CAPITOLO 2

Le schede

2.1 C6713Compact

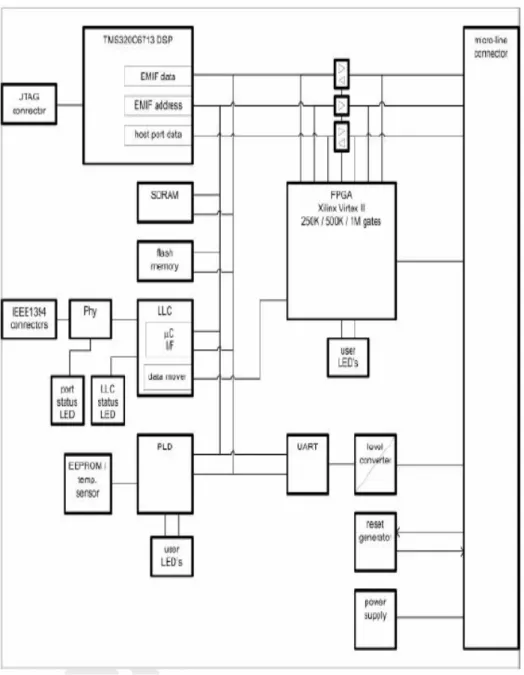

La C6713Compact della Orsys monta un DSP della Texas Instruments TMS320C6713 del tipo floating point che lavora a 225MHz arrivando ad una potenza di calcolo di 1350MFLOPS appoggiato da una RAM interna di 256K. L’FPGA è uno Xilinx VirtexII dalla capacità di 1 Mgate dedicato alla logica programmabile.

Questi due moduli sono appoggiati da un paio di memorie, una Flash EPROM da 32Mbyte organizzata a 16 bit e una SDRAM da 64Mbyte organizzata a 32 bit.

Uno schema a blocchi della scheda è illustrato in figura:

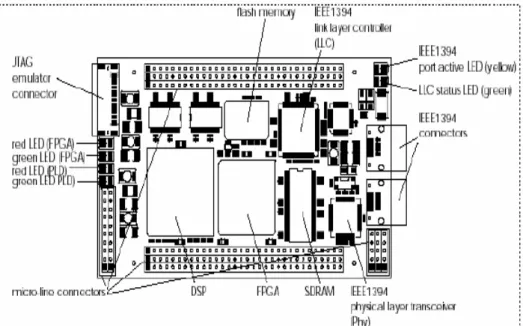

Nelle figure successive si può vedere la scheda in una visione anteriore e posteriore:

Fig 2: Visione anteriore.

Per la programmazione della scheda viene usato come software Code Composer Studio.

2.1.1 Connettore JTAG

Il connettore JTAG viene usato durante lo sviluppo delle applicazioni, ed è associato alle interfacce JTAG di DSP e FPGA; pertanto è usato sia nella fase di debugging, sia per il download di applicazioni nel DSP, sia per il salvataggio nella memoria flash di codice per il DSP o per la programmazione dell’FPGA.

Per quel che riguarda l’FPGA, durante lo sviluppo del progetto è possibile tramite il JTAG scaricare velocemente il codice in esso, per testarlo direttamente.

2.1.2 Connettore IEEE1394

La scheda C6713Compact ha due connettori IEEE1394, che possono essere usati tramite cavi standard a 6 pin. Da notare la presenza di due connettori IEEE1394, questo permette di poter inserire facilmente la scheda in una rete Firewire più complessa del solo nucleo “host computer + Data Processing board”, nel caso ve ne sia l’esigenza.

2.1.3 FPGA

L’FPGA, dalla complessità di 1MGate, permette all’utente di sfruttare una gran quantità di logica programmabile. Esso diventa uno strumento molto versatile grazie alla flessibilità delle connessioni permesse dalla scheda: in particolare esiste la possibilità di legare molti dei pin di ingresso/uscita dell’FPGA a quelli del connettore micro-line e all’interfaccia del DSP.

Più in dettaglio l’FPGA ha accesso a:

• DSP EMIF (External Memory InterFace): bus dati, bus indirizzi, segnali di controllo.

• Pin del connettore micro-line

• Data mover port del Link Layer Controller per l’interfaccia IEEE1394

• Periferiche del DSP: HPI, McASP, GPIO…

• Bus driver control (data, address, HPI data)

• Interfaccia JTAG

• Interrupts del DSP

2.1.4 Memoria esterna SDRAM

La C6713Compact utilizza una memoria esterna SDRAM da 64Mbyte, organizzata a 32 bit. Essa costituisce un valido appoggio per la memorizzazione dei dati. L’accesso alla memoria esterna avviene tramite l’EMIF clock, a 90MHz.

Paragonata alla memoria interna del DSP, questa appare quindi molto più lenta, e la stessa EMIF deve anche essere condivisa con altre risorse, come la UART. Quindi, per quel che riguarda l’utilizzo

del DSP in operazioni che richiedono elevate velocità, è consigliabile l’uso della memoria interna sia come registro d’appoggio per i dati, sia per il salvataggio del codice di programma, almeno finché questo risulta possibile.

2.1.5 Memoria Flash

La C6713Compact utilizza una memoria flash EPROM Am29LV256 a 32Mbyte organizzata a 16 bit, per la memorizzazione non volatile di codice, applicativo per il DSP e di programmazione per l’FPGA.

La memoria flash viene suddivisa in 32 segmenti di 1Mbyte ciascuno. Essi sono accessibili in modo mutuamente esclusivo: i 5 bit più significativi del registro FSR del PLD controllano quale segmento della memoria flash sia correntemente accessibile.

2.1.6 PLD

Il PLD, tramite i suoi registri, permette di accedere alle varie parti hardware della scheda e di configurarne alcune opzioni.

2.1.7 EEPROM seriale

E’ presente sulla scheda anche una memoria EEPROM seriale di 256 byte, integrata col sensore di temperatura della board. Essa può utilmente contenere il serial number e altri parametri.

La EEPROM è connessa al PLD tramite un’interfaccia I²C, e vi si può accedere tramite l’I²C bus control register.

2.1.8 Sensore di temperatura

La scheda C6713Compact contiene un sensore, con interfaccia I²C, che permette di misurare la sua temperatura durante l’utilizzo.

Questo sensore può misurare la temperatura con un range tra -55 e +125 gradi Celsius con la risoluzione di un grado. Se la scheda opera in un ambiente in cui è esposta ad alte temperature, il sensore può divenire indispensabile ad evitare condizioni di rischio. La temperatura interna della CPU è al massimo di circa 15 gradi superiore a quella misurata dal sensore.

Anche il sensore è ovviamente connesso al PLD tramite l’interfaccia I²C, e vi si può accedere tramite l’IC bus control register.

2.1.9 Generatore di reset e Watchdog

Il generatore di reset della C6713Compact genera un impulso di reset nel caso si presentino uno o più dei seguenti casi:

• Accensione

• Reset software (attraverso il module control register)

• Pin /RESETIN attivo

• Discesa di una tensione d’alimentazione sotto il limite minimo

• Azzeramento del Watchdog timer del reset generator, se attivo

• Linea CTS attiva e configurata come reset function.

Durante l’impulso di reset vengono rese attive le uscite RESETOUT e /RESETOUT. Il generatore di reset è dotato, come accennato, di un timer di Watchdog che causa un reset della scheda se non è periodicamente, a sua volta, resettato dal software.

Questo meccanismo può essere utilmente sfruttato nella comunicazione tra la Data-Processing Board e la Detection Board come meccanismo di sicurezza, previsto anche dalle specifiche del progetto. Il Watchdog Timer è di default disabilitato: per attivarlo basterà porre ad 1 il bit numero 4 del registro di configurazione WDG_PHRST del PLD.

2.1.10 External Flags XF signals

La scheda C6713Compact presenta due pin dedicati ad applicazioni generiche, che possono essere impostati come ingressi od uscite. In entrambi i casi, la lettura di tali segnali, o la loro scrittura, avviene tramite il registro XF del PLD.

Esempi di applicazione classici riguardano la gestione di una linea di controllo verso un dispositivo esterno:

- se configurati come uscite daranno ad esso dei segnali di sincronizzazione o controllo,

- se configurati come ingressi ne rileveranno lo stato.

2.1.11 Alimentazione

La scheda C6713Compact, che non sopporta inversioni della tensione d’alimentazione, deve essere alimentata con una tensione tra i 3.3V e i 5V. Internamente sono poi generate tutte le tensioni, minori od uguali a 3.3V, necessarie al funzionamento dei diversi componenti hardware:

• 1.26V per il core del processore DSP

• 3.3V per la maggior parte della circuiteria digitale

• 3.3V, 2.5V e 1.8V per le celle di I/O dell’FPGA connesse al connettore micro-line. Il valore di default è 3.3V, gli altri due sono impostabili tramite una differente hardware configuration della scheda.

2.1.12 LED

Sulla scheda C6713Compact sono montati sei LED, suddivisi in tre gruppi:

•Due LED programmabili dall’utente, controllati dal PLD, che possono essere utilizzati dalle applicazioni software per mostrare determinati eventi o stati.

•Due LED programmabili dall’utente controllati dall’FPGA, con funzioni definite dal design dell’FPGA stesso.

•Due LED di stato legati all’interfaccia IEEE1394: il primo è giallo e si accende se il Phy è correttamente alimentato e connesso ad un'altra periferica IEEE1394; il secondo è verde e di default indica che nel registro FIFO di ricezione, all’interno del LLC, sono presenti dei dati da acquisire.

2.1.13 Periferiche del DSP

Il DSP montato sulla C6713Compact possiede un gran numero di periferiche integrate. Bisogna prestare particolare attenzione, quando si usano contemporaneamente più periferiche perché alcune di esse condividono dei pin.

2.1.14 Multi-channel Audio Serial Ports (McASP)

Le periferiche McASP sono due porte seriali ottimizzate per la gestione di applicazioni audio, anche multicanale. Esse sono contraddistinte dalle sigle McASP0 e McASP1. McASP0 è completamente connessa al bus micro-line, tranne che per la linea AMUTEIN0, connessa all’FPGA. McASP1 è invece connessa all’FPGA.

2.1.15 External Memory Interface (EMIF)

La EMIF è l’interfaccia principale verso le periferiche esterne. Essa ha accesso a:

• Memoria esterna (SDRAM e flash)

• Periferiche on-board: UART, LLC e PLD.

Tramite l’ultima modalità ed un design appropriato dell’FPGA, è possibile accedere a periferiche esterne alla board.

2.1.16 Inter Integrated Circuit (I²C) Interface

Le interfacce I²C del DSP sono due: esse possono essere usate per accedere a periferiche quali il sensore di temperatura, EEPROMS, convertitori D/A e A/D. Sulla C6713 è tuttavia disponibile una sola delle due interfacce I²C.

2.1.17 General Purpose Input/Output Peripheral (GPIO)

Sulla C6713Compact, l’uso di tale interfaccia è sconsigliato, in quanto non direttamente connessa al bus micro-line. Tuttavia possono essere utilizzati, come pin dell’interfaccia GPIO, alcuni pin normalmente dedicati agli External Flags (XF), ai McBSP e alle connessioni con pin liberi dell’FPGA.

2.1.18 Multi-Channel Buffered Serial Ports (McBSP)

Nella scheda sono presenti due McBSP indipendenti: ogni porta può comunicare in full duplex, con un data stream continuo fino a 75Mbps. Esse possono essere usate, ad esempio, per la

comunicazione tra due processori, o per la connessione con altre periferiche, come codec e convertitori A/D e D/A.

Questa porta adotta lo standard delle interfacce seriali sincrone delle famiglie di DSP Texas Instruments TMS320C2000, ‘C3x e ‘C5000, e può essere programmata per divenire compatibile con ogni altra interfaccia sincrona seriale. Essa è costituita dai segnali DRx (data receive), DXx (data transmit), CLKRx (clock receive), CLKXx (clock transmit), FSRx (frame sync receive) e FSXx (frame sync transmit). Di default, i segnali delle porte McBSP sono connessi al bus micro-line.

2.1.19 Timers

Il DSP TMS320C6713 contiene 2 timer indipendenti, a 32 bit. Ognuno di essi ha un pin di ingresso ed uno di uscita. Per maggiore versatilità d’utilizzo essi possono ricevere il clock da una sorgente esterna o da quella interna.

2.1.20 Host Port Interface (HPI)

Il DSP TMS320C6713 è dotato di una host port a 16 bit, che può essere usata da un host processor per avere accesso diretto alla memoria del DSP; in questo caso l’host accede come master ed il DSP viene visto come slave. L’host processor e il DSP possono così

scambiare dati sia attraverso la memoria interna del DSP, sia attraverso la memoria montata sulla board.

L’host avrà inoltre accesso anche ai registri delle periferiche mappati in memoria. La connessione tra l’host e lo spazio di memoria del DSP è assicurata da un meccanismo DMA.

2.1.21 Interrupts

Quattro interrupt non mascherabili ed uno mascherabile permettono ai dispositivi della scheda o ad eventuali periferiche esterne di interrompere il programma corrente del DSP e saltare ad una routine di servizio dedicata all’interruzione.

Sulla C6713Compact, due linee di interrupt (EXT_INT6 e EXT_INT7) sono gestite dal PLD e due (EXT_INT4 e EXT_INT5) dall’FPGA. In tabella 3.2 sono mostrate le possibili fonti degli interrupt provenienti dal PLD.

2.1.22 DMA

Il DSP TMS320C6713 è dotato di un controller enhanced DMA (EDMA).

Il DMA può essere usato per trasferire dati tra due locazioni qualunque nello spazio di memoria della C6713Compact. Tali

trasferimenti dati possono essere sincronizzati dal software o da eventi generati internamente o esternamente alla scheda: gli eventi esterni sono segnalati per mezzo delle linee di interrupt.

Le operazioni DMA possono essere concatenate, cioè la fine di ogni trasferimento di dati può dare inizio al successivo: ciò costituisce un potente e flessibile modo di svolgere operazioni senza l’intervento della CPU.

Il meccanismo DMA è quello che consente le maggiori prestazioni di velocità all’interno della scheda: il massimo throughput è 225Mwords per secondo.

2.1.23 Supporto Software

La ditta Orsys fornisce con la C6713Compact un pacchetto di software, chiamato “board library”. Esso costituisce un insieme di driver a basso livello per i componenti della scheda, permettendone un’immediata inizializzazione e facilitando la fase di programmazione.

2.2 Nallatech Ballynuey2

La scheda Nallatech Ballynuey2 è uno strumento per la progettazione e la verifica di core, chip, e di sistemi di elaborazione digitali ad elevate prestazioni.

L'elemento che più caratterizza la scheda è la flessibilità; infatti la struttura di base della scheda è composta da un insieme di risorse fisse quali bus, sorgenti diverse di clock, memorie RAM (Random Access Memory) e un certo numero di FPGA (Field Programmable Gate Array) di dimensioni medio alte.

A queste risorse fisse vanno aggiunte dei moduli inseribili dall'utente che contengono elementi di elaborazione vari: memorie RAM, FIFO (First-In First-Out), FPGA, DSP (Digital Signal Processor). La capacità complessiva di elaborazione è quindi molto elevata.

Inoltre il sistema risultante è quasi totalmente programmabile dall'utente e capace di adattarsi ad applicazioni molto diverse: codifica di immagini, sistemi di comunicazione wireless ecc…

La flessibilità è resa possibile dal numero elevato di bus che connettono i moduli utente fra di loro e con le altre risorse (fisse) a bordo della scheda. Questi bus nella maggioranza dei casi sono completamente programmabili dall'utente e consentono elevate frequenze di lavoro. Inoltre la Ballynuey è dotata di un certo

numero di sorgenti di clock programmabili in vari modi. Questo fatto consente di realizzare la comunicazione fra chip diversi tramite protocolli sincroni, quindi molto efficienti. La disponibilità di bus ad elevato parallellismo permette la realizzazione di sistemi di elaborazione ad elevate prestazioni.

La scheda comunica con il mondo esterno tramite connettori che consentono di colloquiare con dispositivi di vario tipo.

Il più importante di questi è sicuramente il connettore PCI, con cui è possibile interfacciare la scheda con un personal computer. La Ballynuey2 è corredata di un insieme di utilità software che consentono di configurare la scheda e di gestire in modo semplice ma efficace i trasferimenti di dati fra la scheda e il PC host.

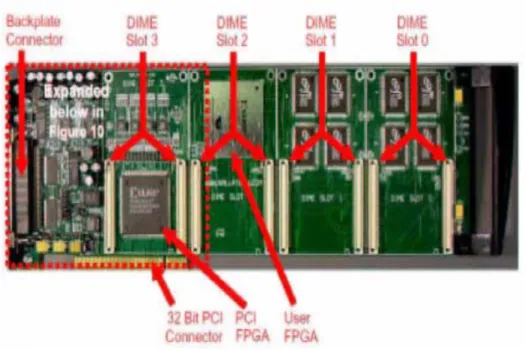

La scheda è mostrata in figura 5:

Fig 5: Nallatech Ballynuey2 .

2.2.1 Le risorse fisse

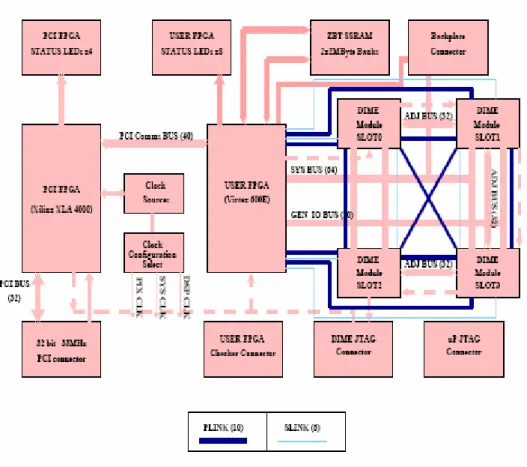

In figura 5 è presentato uno schema a blocchi delle risorse fisse della scheda Ballynuey. In basso a sinistra si può notare il connettore PCI, che collega la scheda al PC host e lavora a 33MHz.

Il connettore PCI si interfaccia dal lato interno della scheda con un FPGA Xilinx 4000XLA, preprogrammato tramite una memoria PROM; questo FPGA, detto PCI FPGA, ha il compito principale di controllore per il connettore PCI.

I dati scambiati con il PC host vengono trasferiti dal PCI FPGA ad un'altro FPGA detto User FPGA o On Board FPGA.

Lo User FPGA presente sulla scheda in dotazione è uno Xilinx Virtex-E XCV600. Esso è la principale risorsa di elaborazione fissa fornita dalla scheda ed è completamente programmabile dall'utente.

L'importanza dello User FPGA deriva soprattutto dalla posizione strategica in cui si trova, infatti è connesso a tutte le altre risorse disponibili sulla scheda.

Proseguendo nella descrizione delle risorse fisse, sono presenti due gruppi di led. Il primo, composto di quattro elementi, è connesso direttamente al PCI FPGA, e può essere usato per verificare il corretto funzionamento del collegamento fra il PCI host e il PCI FPGA; infatti i led possono essere comandati tramite funzioni software dal PC host.

Il secondo gruppo di led, di otto elementi, è connesso esclusivamente allo User FPGA e può risultare molto utile sia per verificare che l’FPGA sia stato configurato correttamente, sia a scopo di debug dell'hardware.

Il Backplate IO connector può essere usato per collegare la scheda ad altri dispositivi hardware esterni; il connettore è del tipo a 68 piedini.

Sempre connessi allo User FPGA vi sono due blocchi di memoria ZBT SSRAM (Zero Byte Turnaround Synchronous Static RAM), ognuno composto da quattro banchi da 128KByte x 32bit.

Il clock della memoria ZBT viene fornito dallo User FPGA, e deriva da uno dei tre clock della scheda entranti nell’ On Board FPGA.

2.2.2 Moduli DIME e struttura dei Bus

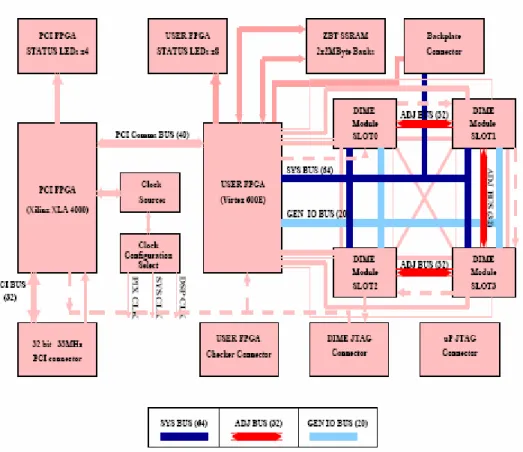

Fig 6: Struttura dei Bus: SYSBUS, GEN IO BUS e ADJBUS.

I moduli DIME (DSP and Image Processing Module for Enhanced FPGA), sono i principali elementi di elaborazione a disposizione della Ballynuey.

I moduli DIME possono essere inseriti nella scheda, a discrezione dell'utente, tramite i quattro slot di espansione rappresentati in figura 6. In questo paragrafo si descrivono le strutture di

connessione che collegano i moduli DIME fra loro e con lo User FPGA.

Riferendosi alla figura 6 si osserva il SYS Bus, ovvero bus di sistema, a cui hanno accesso lo User FPGA, tutti i moduli DIME e il Backplate IO Connector.

Il SYS Bus ha parallelismo 64 ed è un bus per soli dati, completamente programmabile dall'utente; con ciò si intende che ogni linea del bus può lavorare sia in modo unidirezionale che bidirezionale, e la modalità di funzionamento e la funzione logica associata al segnale trasportato è definita in modo completamente arbitrario dall'utente.

Il SYS Bus è adibito al trasporto esclusivo di segnali di dato, non può essere usato ad esempio per portare segnali di clock da un punto all'altro del sistema.

Generalmente questo Bus viene diviso in due bus a 32 bit: Il bus SYSVIN (System Video In) e il bus SYSVOUT (System Video Out).

Volendo far comunicare ad esempio lo User FPGA con un modulo DIME, occorre stabilire se i piedini dello User FPGA mappati sul bus SYSVIN corrispondano, nel modulo DIME, a quelli mappati sul bus SYSVIN oppure a quelli sul bus SYSVOUT.

Il GEN IO Bus (Generic Input Output Bus) ha caratteristiche molto simili al SYS Bus. Dal punto di vista topologico differisce solo in quanto non è connesso al Backplate IO Connector.

Il parallelismo è pari a 20, tuttavia il bus non è sempre completamente programmabile dall'utente, dato che su certi moduli DIME alcuni bit del GEN IO Bus svolgono funzioni particolari.

Il bus ADJ (Adjacent bus) connette ogni modulo DIME con gli altri due moduli DIME adiacenti. Come per il SYS Bus può essere usato per il solo trasporto di segnali di dato. Si divide in due bus, entrambi con parallelismo 32, detti ADJVIN (Adjacent Video In Bus) e ADJVOUT (Adjacent Video Out Bus).

Il Bus ADJVIN di un modulo DIME corrisponde al bus ADJVOUT del modulo DIME precedente; ovviamente il bus ADJVOUT di un modulo DIME corrisponde al bus ADJVIN del modulo DIME successivo.

Oltre i già citati SYS Bus, GEN IO Bus e ADJ Bus la Ballynuey mette a disposizione un certo numero di collegamenti punto-punto, divisi in PLink e SLink di cui i primi hanno parallelismo pari a 10 bit mentre i secondi pari a 6 bit.

Entrambi i tipi di collegamento sono, nella maggioranza dei casi, completamente programmabili dall'utente e servono esclusivamente per il trasporto di segnali di dato.

I PLink possono essere usati per la realizzazione di connessioni di tipo parallelo, mentre gli SLink per connessioni di tipo seriale.

La struttura dei bus è evidenziata in figura:

Fig 7: PLink e SLink.

Si esaminano ora la struttura dei collegamenti PLink e SLink disponibili sulla scheda. Come si può notare dalla figura 7, per quanto concerne i PLink ogni slot DIME ha un collegamento privato con lo User FPGA e uno verso ognuno degli altri slot DIME. Per quanto riguarda gli SLink, ogni slot DIME ha un collegamento

privato con lo User FPGA; i collegamenti fra slot DIME esistono solo fra gli slot 0 e 2, e fra gli slot 1 e 3.

Le corrispondenze fra i segnali componenti il collegamento e la rispettive funzioni logiche associate ai PLink e agli SLink sono riportate nelle seguenti tabelle.

Tabelle PLink, SLink.

I protocolli di comunicazione adottati sono gli stessi usati ad esempio dai DSP della Analog Devices appartenenti alla famiglia 21xxx, per i collegamenti di tipo parallelo e seriale.

La corrispondenza citata fra i segnali e le funzioni logiche associate è da intendere come vincolante solo quando ad un estremo del collegamento è presente un dispositivo hardware che implementa quel tipo di connessione.

Nel caso in cui ad entrambi gli estremi di un PLink o di un SLink si trovino due FPGA, le corrispondenze indicate non sono assolutamente vincolanti, pertanto il programmatore può definire in modo arbitrario la funzione logica associata a ciascun bit del collegamento, esattamente come accade per il SYS Bus.

2.2.3 Reti di clock e Reset

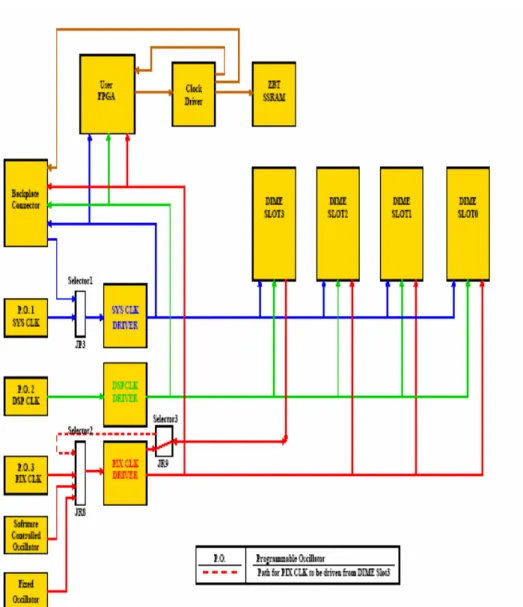

La scheda Ballynuey2 è dotata di tre diverse reti di clock, chiamate SYS CLK, PIX CLK e DSP CLK. Lo schema delle reti di clock è fornito nella figura 1.5. Ogni rete può essere alimentata da diverse sorgenti di clock, le opzioni possibili sono:

• Opzioni per la sorgente del SYS CLK:

Oscillatore programmabile

Sorgente esterna, tramite Backplate Connector

• Opzioni per la sorgente del PIX CLK:

Oscillatore programmabile

Clock derivato dal modulo DIME nello Slot3

Clock comandato via software

• Opzioni per la sorgente del DSP CLK:

Oscillatore programmabile

Gli oscillatori programmabili forniscono segnali con frequenza programmabile nell'intervallo fra 400KHz e 90MHz. La programmazione della frequenza avviene tramite il DIME Configuration Software GUI oppure tramite la funzione DIME Set-Oscillator-Frequency della DIME Software Library.

Figura 8: Reti di distribuzione dei clock.

Sulla rete del SYS CLK è possibile usare come sorgente un segnale proveniente da un dispositivo esterno, tramite il Backplate Connector.

La scheda consente di montare un oscillatore fisso esterno, con package di tipo DIL (Dual In Line) a 8 o 14 piedini.

Questa possibilità può risultare utile per applicazioni particolari, in cui servono sorgenti di clock con caratteristiche diverse da quelli presenti sulla scheda.

Oltre all'oscillatore fisso e a quello programmabile, la rete del PIX CLK può essere alimentata da un segnale di clock comandato tramite software, opzione che può risultare utile in fase di debug del sistema, oppure da un segnale generato dal modulo DIME sullo SLOT3.

In figura 9 è mostrato lo schema della rete di distribuzione dei reset.

Fig 9: Rete di distribuzione dei reset.

Come si può notare si ha una rete principale che fornisce il reset a tutto il sistema, ossia allo User FPGA e ai moduli DIME, e una seconda rete che fornisce il reset al solo User FPGA.

I due reset per lo User FPGA sono mappati su piedini distinti. Questi segnali, entrambi attivi bassi, sono dei comuni reset hardware, non hanno nessun effetto sulla configurazione delle FPGA, ma servono solo per portare il sistema in uno stato noto.

Le reti di reset sono comandate a livello hardware dal PCI FPGA, mentre a livello software dal DIME Configuration Software oppure da funzioni apposite della DIME Software Library. Sempre agendo per via software è possibile comandare un terzo segnale di reset, non indicato in figura, che agisce sul solo PCI FPGA.

2.2.4 Il modulo BallySharc2

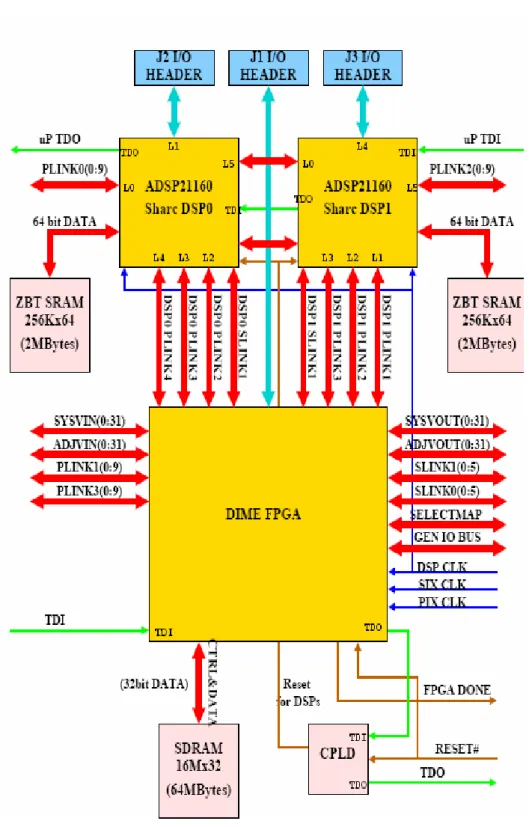

Il modulo BallySharc2 è uno dei tre moduli DIME presenti sulla Ballynuey 2. In figura 10 ne è riportato lo schema a blocchi.

Come si può notare i principali elementi di elaborazione sono due DSP della Analog Devices, modello Sharc21160M, e un FPGA Xilinx Virtex-E, modello XCV2000.

I DSP hanno una frequenza di lavoro massima pari a 80MHz, con una capacità di elaborazione per ogni DSP pari a 1.2GFlops, ovvero 1.2 miliardi di operazioni floating-point al secondo.

La Virtex-E mette a disposizione più di due milioni di porte logiche programmabili. Inoltre sono presenti tre memorie RAM di dimensioni medio-alte, collegate come periferiche ai DSP e all’FPGA. I DSP ricevono il clock dalla rete del DSP CLK, oppure da un oscillatore al quarzo.

I DSP Sharc21160M si interfacciano con il mondo esterno tramite un insieme di porte.

Il collegamento principale è costituito da due bus, uno per i dati a 64 bit e uno per gli indirizzi a 32 bit. Sul modulo BallySharc2 questi sono connessi a due memorie di tipo ZBT SRAM. Le memorie hanno parallelismo dati pari a 64 e una profondità di 256Kword, per una capacità complessiva di 2MByte.

Oltre i due bus sopraccitati gli Sharc hanno ognuno sei canali di comunicazione di tipo parallelo a 10 bit, detti Link Port, e due canali di tipo seriale a 6 bit. I canali sono connessi in vario modo.

Un primo canale parallelo si connette ad un header , consentendo la comunicazione fra gli Sharc e dispositivi hardware esterni alla scheda.

Un altro collegamento parallelo interconnette i DSP fra loro; un terzo Link Port si interfaccia direttamente sui PLink del DIME bus; in questo caso i segnali dei PLink non sono programmabili dall'utente ma devono implementare il protocollo usato dai Link Port. Il Link Port sul DIME bus del DSP0 si connette allo User FPGA, mentre quello del DSP1 ad un altro modulo DIME.

I rimanenti Link Port si interfacciano sulla Virtex-E, detto anche DIME FPGA o Ballysharc FPGA. Dei collegamenti seriali, uno connette i DSP fra loro, mentre l'altro è diretto alla DIME FPGA.

Il reset agli Sharc arriva direttamente dal CPLD presente nello schema di figura 10, e come si può notare è distinto dal segnale di reset della DIME FPGA, collegato al system reset della scheda, e comandabile via software.

Alcuni segnali di controllo dei DSP sono connessi direttamente al BallySharc FPGA. Questi sono i tre segnali di interrupt IRQ1, IRQ2 e IRQ3, i segnali di flag, a 4bit e il segnale Timer Expired.

Quest'ultimo in pratica viene asserito per quattro cicli di clock quando un contatore programmabile interno al DSP raggiunge lo zero.

I segnali di flag e di Timer Expired possono risultare molto utili per la misurazione delle prestazioni effettive dei processori. Infatti queste ultime, devono tenere conto non solo del tempo di elaborazione ma anche dei tempi di input/output, difficilmente stimabili dallo strumento di sviluppo fornito a corredo dei DSP.

Gli Sharc possono essere programmati sia collegando un DSP In Circuit Emulator (ICE), sia caricando i programmi tramite la scheda host. Il primo metodo sfrutta la catena JTAG dei DSP; i segnali µP TDI (Test Data In) e µP TDO (Test Data Out) sono infatti connessi al µP JTAG Connector della scheda Ballynuey2 (vedi figura 10).

Oltre lo svantaggio di richiedere un dispositivo esterno alla scheda e connesso al PC host questo metodo risulta alquanto lento in quanto il programma viene caricato in modo seriale, un bit per volta; tuttavia l'ICE può risultare molto utile in fase di debug.

Il secondo metodo per programmare il DSP sfrutta i collegamenti paralleli fra i DSP e la scheda che, come già detto, sono sei per ogni Sharc.

Ritornando sullo schema a blocchi del modulo BallySharc, si può osservare come la DIME FPGA si interfaccia al resto del sistema: oltre il SYS BUS verso lo User FPGA, i bus ADJVIN e ADJVOUT ad altri moduli DIME si hanno 2 SLink, uno diretto allo User FPGA(SLink0) e uno ad un modulo DIME(SLink1), e altri due PLink, diretti a due moduli DIME diversi.

La DIME FPGA può connettersi ad un dispositivo esterno tramite il J1 I/O Header. Il collegamento è a 36 pin, di cui 12 connessi a massa e i rimanenti 24 a disposizione dell'utente per il trasporto dati.

Per aumentare la memoria RAM a disposizione del programmatore, sul BallySharc è presente una memoria SDRAM con parallelismo 32 e profondità pari a 16Mwords, per una capacità complessiva pari a 64MBytes. La memoria, divisa in due banchi, è comandata esclusivamente dalla DIME FPGA.

Nella parte inferiore della figura 10 è presente un CPLD che serve esclusivamente alla configurazione dei moduli, nello specifico garantisce che i moduli siano di tipo Plug and Play, consente il riconoscimento automatico del modulo e la sua corretta gestione software.

2.2.5 Il modulo BallyBlue

Fig 11: Schema a blocchi del modulo BallyBlue.

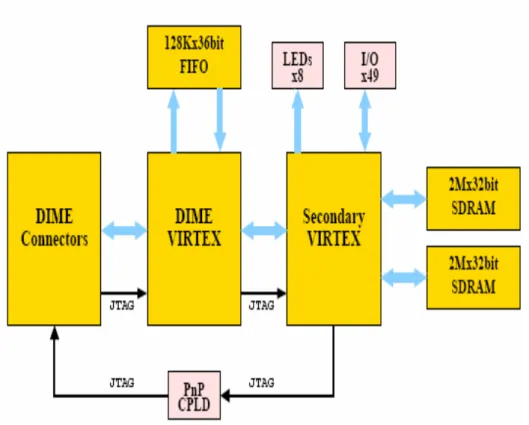

Oltre il modulo BallySharc sulla scheda Ballynuey2 sono presenti due moduli DIME BallyBlue. Il modulo BallyBlue è caratterizzato dalla presenza di due FPGA Virtex-E. Su uno dei moduli le FPGA sono due XCV1000E, mentre sull'altro sono delle XCV2000E.

La figura 11 mostra lo schema a blocchi di un modulo BallyBlue. Come si può notare solo uno degli FPGA ha accesso ai DIME bus,

questo FPGA viene pertanto definito DIME FPGA o primary FPGA, mentre l'altro è detto secondary FPGA.

I bus cui ha accesso il DIME FPGA sono quelli più volte citati : SYS BUS, ADJ BUS, GEN IO BUS, 4 PLink e 2 SLink. Diversamente dal modulo BallySharc, tutti i 20 bit del GEN IO BUS sono disponibili per applicazioni utente.

Oltre le due Virtex-E sono presenti tre memorie RAM. La prima è una FIFO che si connette al DIME FPGA, con dimensioni pari a 128k x 36bit. La FIFO consente il buffering di un grosso numero di dati, ed evita di riservare a tale scopo la RAM a bordo degli FPGA. Il componente è dotato di un numero consistente di parametri programmabili, per cui il comportamento della FIFO è alquanto flessibile.

La FIFO è asincrona, con una frequenza di lavoro massima pari a 100MHz. I clock possono essere forniti sia dalla primary che dal secondary FPGA, anche in modo misto.

I due FPGA sono connessi tramite un bus a 101 bit, completamente programmabile.

Il secondary FPGA comanda due SDRAM (Synchronous Dynamic RAM), indipendenti, da 2Mx32bit e con frequenza di lavoro massima pari a 143MHz. Il modulo BallyBlue fornisce un segnale di clock indipendente ad entrambe le SDRAM, tramite il secondary FPGA, tuttavia non è conveniente usare regimi di clock diversi, soprattutto ad alte frequenze. Infatti il primo requisito da rispettare

per il corretto interfacciamento delle memorie è la sincronia di clock fra le medesime e i registri comunicanti con esse sugli FPGA.

Il sincronismo si ottiene tramite l'uso dei DLL messi a disposizione dalla Virtex-E; questi per funzionare hanno bisogno di un segnale di reazione (feedback), che tenga conto del ritardo del clock che alimenta le memorie.

Il secondary FPGA può scambiare dati con dispositivi esterni alla scheda tramite un connettore a 49 bit; il collegamento è completamente programmabile dall'utente.

La configurazione e la gestione della scheda Ballynuey2 avviene tramite l'uso di pacchetti software eseguiti dal PC host, il quale dialoga con la scheda tramite l'interfaccia PCI.

2.3 ORUGA

Fig 12: Scheda Oruga.

Oruga è una scheda PCI per l’acquisizione ed emissione dati capace di campionare 64 canali di ingresso analogici con una risoluzione di 16 bit a 66 KSamples/s ciascuno e di pilotare 4 canali di uscita analogici fino a 1 MSample/s con avanzate operazioni di trigger che offrono una grande flessibilità.

Il DSP C6713 assicura il controllo di tutte le periferiche e offre un’ampia banda per l’elaborazione matematica con estrema flessibilità e facilità di programmazione.

La scheda possiede un set molto completo di periferiche per una veloce integrazione del sistema compresi ingressi e uscite digitali, porte dati esterne e sincronismi per più schede.

E’ un’applicazione completa per applicazioni industriali e d’ufficio che richiedono un elevato numero di canali, acquisizione e pilotaggio dati ad alta risoluzione e coprocessing opzionale: test e misure, data logging/playback, strumenti OEM, analisi acustiche di vibrazioni, controlli industriali.

Il diagramma a blocchi è illustrato in figura 13:

2.3.1 Descrizione

Il front-end analogico consiste di 64 canali d’ingressi indipendenti e filtri anti aliasing individuabili raggruppati in 2 banchi e multiplexati 32 a 1 in due convertitori A/D da 2,2 MSample/s.

La logica di controllo offre un’ampia selezione di modalità di trigger e di sorgenti per il clock, tutte configurabili via software e che permettono di configurare qualsiasi tipo di schema di acquisizione complesso.

Una modalità di decimazione supporta anche 2 stream concorrenti, uno a bassa velocità e l’altro ad alta velocità per un utilizzo ottimizzato del bus e della banda del CPU così come della CPU host.

Anche i 4 canali indipendenti di uscita con convertitori D/A da 1 MSample/s traggono beneficio da questo controllo avanzato del trigger e offrono alte prestazioni analogiche per la generazione di forme d’onda playback o controllo a ciclo chiuso.

Il TMS320C6713 è il più veloce DSP floating-point della Texas Instruments che utilizza tutta la potenzialità della famiglia C6000. Con una memoria di 256 Kb, un efficiente controllore della cache a 2 livelli e 16 canali DMA, il DSP è riconosciuto dagli sviluppatori come il processore a cui si adatta meglio il linguaggio C.

Le librerie software dell’Oruga fanno un buon uso dei driver delle periferiche del DSP/Bios per facilitare lo sviluppo del codice da

parte dell’utente per le applicazioni multi-thread più complesse attraverso l’ottimizzazione dell’utilizzo della banda.

Oruga è una scheda a 64 bit/33MHz PCI che supporta operazioni burst da 254 Mbyte/s da e per la memoria del PC host, ed è anche compatibile con un bus PCI a 32 bit.

Un canale di comunicazione con messaggi di tipo mail-box per comandare e controllare le funzioni con l’applicazione ospite.

La scheda presenta anche numerose caratteristiche per una facile integrazione del sistema: 64 bit di ingresso e uscita digitale d’uso generale, una porta veloce e bidirezionale FIFO esterna per i dati e una porta SyncLink/ClockLink per una facile sincronizzazione di più schede o hardware esterno.

2.3.2 DSP Processing

La scheda Oruga supporta il DSP TMS320C6713 cloccato a 150 MHz, DSP a 32 bit floating point, il più veloce della famiglia Texas Instruments come già detto, e usa un’efficiente architettura della cache a 2 livelli con la cache del primo livello di 4 Kbyte per i dati e di 4 Kbyte per i programmi e uno spazio di 256 Kbyte che può essere partizionato attraverso un set-up software tra la cache di secondo livello e la RAM.

Il controllore DMA pilota 16 canali indipendenti che alleggeriscono il carico dati della CPU.

L’EMIF è interfacciata attraverso 2 dispositivi logici della Xilinx a 2 canali A/D, agli I/O digitali e all’interfaccia PCI.

Una delle 2 porte seriali multicanale MCBSP controlla e riceve dati dai canali DAC, la seconda MCBSP è portata fuori dall’utente.

La porta HPI da 16 bit è usata per il booting e acceduta attraverso l’interfaccia PCI.

Sul chip sono presenti inoltre 2 timer da 32 bit.

Le risorse sulla scheda includono una Sdram a 32 Mbyte, 3 timer a 24 bit, una DDS base dei tempi da 0 a 25 MHz, un’interfaccia PCI a 33 MHz con buffer FIFO.

Un chip logico della Xilinx controlla i convertitori analogici, i segnali di trigger start-stop e i 32 bit di ingresso-uscita digitali.

Il firmware include il buffering FIFO dei dati A/D, la correzione digitale del guadagno e dell’offset e la decimazione dei canali a bassa velocità.

Un secondo dispositivo Xilinx pilota l’interfaccia PCI, la matrice di selezione della base dei tempi, l’interfaccia della porta FIFO e gli altri 32 bit di I/O digitali.

2.3.3 Canali di input analogici

La scheda presenta 64 canali di input differenziali o singola uscita con un range tra ±10 V raggruppati in 2 banchi da 32 canali ciascuno.

I range di ingresso possono essere variati per ogni canale via software con un massimo di ±10 V. Gli ingressi sono accoppiati alla continua e la massima banda del segnale di ingresso è di 100 KHz.

Ogni canale di ingresso è portato attraverso un filtro di Sallen-Key a 4 poli settati a 100 KHz che può essere bypassato attraverso un jumper e connesso a un amplificatore buffer e portato a un multiplexer 32 a 1.

Ogni uscita dei multiplexer è connessa a un convertitore AD7621 a 16 bit di 2,2 MSample/s con 1 LSB di non linearità e prestazioni in alternata con SFDR di oltre 85 dB.

L’Oruga ha una caratteristica di autocorrelazione che utilizza degli interruttori controllati via software e dei riferimenti di tensione sulla scheda che permettono all’utente di calibrare la scheda senza rimuovere fili esterni.

I 2 convertitori A/D possono usare una base dei tempi separata così l’utente può configurare un mix di canali a alta e bassa velocità.

Per i dati ad alta velocità i segnali di trigger per la base dei tempi possono essere scelti fra molte sorgenti di clock: DDS su scheda, i

timer del DSP, i timer logici, clock esterno, un pin SyncLink/ClockLink o da comando software.

Quando si configura un gruppo di canali per la bassa velocità la base dei tempi può essere scelta fra le seguenti: base dei tempi ad alta velocità divisa per n, clock esterno o software.

La scheda fornisce anche una grande flessibilità per il trigger che è completamente configurabile via software.

Il campionamento dei dati è definito con segnali di start e stop che di base applicano una maschera o una finestra sul segnale di clock della base dei tempi. Il trigger di start può essere scelto tra un’ampia gamma di segnali: timer, interruzioni esterne, il pin SyncLynk/ClockLynk, comandi software o soglie analogiche.

Il tempo di stop è anch’esso flessibile e permette differenti modi di operare: durata specifica usando un timer, lunghezza specifica come definita da un numero di campioni acquisito, o altri segnali esterni come interruzioni esterne, il pin di SyncLynk/ClockLync o comandi software.

Così si può facilmente configurare il sistema per acquisizioni ripetute basate su eventi hardware e software.

2.3.4 Canali di output analogici

La scheda offre 4 canali D/A opzionali con una risoluzione di 16 bit e con una frequenza di campionamento di 0-1MHz ciascuno che utilizzano convertitori Linear Tech LTC1597.

Il range delle uscite è tra ±10 V ma può essere personalizzato cambiando dei resistori, ciascuna uscita del DAC è connessa a un filtro di Sallen-Key a 2 poli settato a 400 KHz, e ogni segnale di uscita è accoppiato in continua.

In modo simile alle operazioni di A/D il trigger D/A è estremamente flessibile sia in termini di sorgenti di clock per la base dei tempi sia per i segnali di stop. La base dei tempi D/A e il trigger di start-stop possono essere differenti dai controlli A/D.

La scheda permette un’autocalibrazione della conversione D/A attraverso la A/D, completamente sotto il controllo software.

I canali D/A sono interfacciati al DSP con un MCBSP, porta a 50 Mbit/s che supporta la modalità a 4 canali a 750 KSample/s per canale.

2.4 MVE

La MVE (Multimedia Video Engine) è una piattaforma embedded per applicazioni di video processing che integra una evoluta interfaccia utente.

Fig 14: Scheda MVE.

L’hardware è basato su un processore DSP ad altissime prestazioni, prodotto da Texas Intruments, che permette l’implementazione di complessi algoritmi d’elaborazione d’immagine.

Il sistema è in grado di acquisire un segnale video nei più comuni standard analogici, elaborarlo in tempo reale, e presentare il risultato dell’elaborazione su un monitor.

Allo stesso tempo, la piattaforma può acquisire, elaborare e generare segnali analogici con una frequenza di campionamento di 133KHz.

Una complessa interfaccia grafica, pilotata tramite mouse e tastiera, permette di interagire con il sistema in modo semplice ed

immediato, disponendo degli strumenti abitualmente utilizzati nei comuni calcolatori.

Il sistema realizzato, comprensivo di scheda embedded e di framework software, costituisce una piattaforma ideale per la rapida prototipazione di algoritmi di elaborazione video in tempo reale.

Fig 15: Schema a blocchi.

L’architettura della scheda è costituita da vari moduli: DSP, FPGA, Memoria, Video input, Video output, I/O analogico, Periferiche.

Il DSP è il componente su cui si basa la scheda. Il dispositivo utilizzato è il TMS320C6415, un processore di nuova generazione

prodotto da Texas Instruments che fornisce ragguardevoli prestazioni in elaborazione video.

L’architettura di tipo VLIW (Very Long Instruction Word) esegue in parallelo 8 istruzioni a 32bit per ciclo ad una frequenza di clock di 600MHz, ovvero fino a 4800MIPS.

Inoltre, ognuna delle sei ALU e dei due moltiplicatori è in grado di eseguire, oltre ad una singola operazione su operandi a 32bit, due operazioni a 16 bit o quattro operazioni ad 8bit. Questa peculiarità può essere largamente sfruttata in elaborazione video in quanto le immagini sono rappresentate da matrici di punti ad 8 o 16 bit.

Oltre ad una ragguardevole potenza di calcolo, il TMS320C6415 possiede anche abbondanti risorse per l’interfacciamento fra cui: un bus a 64 bit, un bus a 16 bit, un bus PCI a 32 bit, tre seriali sincrone multicanale.

Per ultimo, un evoluto controllore DMA a 64 canali permette una complessa gestione del flusso dei dati.

Per quanto riguarda la memoria invece si può subito notare che è suddivisa in tre banchi:

Un banco da 512 KB di memoria flash, tipicamente utilizzata per contenere il firmware del DSP.

Un banco da 512MB, 64-bit, 133MHz, di memoria SDRAM, costituita da un modulo DIMM opzionale.

Il modulo di video input è in grado di acquisire un segnale video in formato Y/C o CVBS, negli standard PAL, NTSC e SECAM.

Il decoder video utilizzato, l’SAA7114 prodotto da Philips, contiene inoltre un video scaler che permette di ridimensionare l’immagine sia in orizzontale che in verticale. Una volta che i dati sono acquisiti, questi vengono trattati da un FPGA che può essere utilizzato per convertire i dati dal formato Y/C ad RGB.

Il dispositivo permette inoltre di interfacciare la scheda ad un modulo di pre-processing.

Il modulo di video output è basato sul processore grafico 69000, prodotto da Asiliant. Il dispositivo integra 2 MB di SDRAM, un acceleratore grafico 2D, una finestra di pop-up ed un cursore grafico. Inoltre, il processore grafico è in grado di implementare una finestra di playback ove viene rappresentato un segnale video, gestendo il meccanismo di double-buffering. Il modulo video è anche in grado di generare un segnale in video standard quando l’uscita VGA non è utilizzata.

Il modulo di I/O analogico è costituito da due convertitori multicanale: un ADC ad 8 canali, 12 bit, frequenza di campionamento di 133KHz; un DAC a 4 canali, 10 bit, 330KHz.

Fra le periferiche presenti nella scheda, è di particolare importanza il controllore USB, dotato di due porte di downstream ed una porta di upstream a velocità full-speed.

Il controllore permette sia di interfacciare la scheda a dispositivi USB, quali ad esempio mouse e tastiera, sia di usare la scheda come dispositivo USB di un apparato master, quale ad esempio un personal computer. Oltre all’USB, il modulo contiene un’interfaccia seriale ed un collegamento JTAG per l’emulazione e la programmazione del firmware.

I dati acquisiti dal decoder video vengono temporaneamente memorizzati in una memoria FIFO. Quando un’intera linea dell’immagine è presente nella FIFO, un trasferimento DMA la trasferisce nel capture-buffer.

La struttura è di tipo double-buffering: un buffer (capture-buffer) è utilizzato per acquisire il frame attuale mentre un secondo buffer (processing-buffer) contiene il frame precedente che è reso disponibile per l’elaborazione. Entrambi i buffer sono collocati nella memoria interna del DSP.

Quando tutte le linee sono state trasferite, ovvero un frame è completo, avviene lo switch dei buffer e il codice viene eseguito sui nuovi dati. Il codice, una volta completata l’esecuzione, rende disponibile i dati per l’output in un buffer che può essere collocato ovunque in memoria (on-chip, SBSRAM, SDRAM).

I dati in uscita vengono quindi convertiti nel formato video opportuno e spostati nel video-buffer tramite un trasferimento DMA. Infine, i dati sono spostati nel buffer di playback sul processore grafico attraverso il bus PCI.

2.5 QUADIA

La Quadia è una scheda compatta PCI che monta quattro DSP, due FPGA e due siti PMC; possiede prestazioni eccellenti con grande flessibilità per il campionamento avanzato dei segnali e applicazioni in tempo reale.

Fig 16 : Scheda Quadia.

I quattro DSP sono TMS320C6416 che lavorano a 1 GHz, sono DSP a virgola fissa a 32 bit arrivando così a 32000 MIPS e ogni DSP è appoggiato da una memoria SDRAM da 64Mb.

Per quanto riguardo gli FPGA se ne possono notare due al centro della scheda; sono due XC2VP40 VIRTEXII pro della XILINX ciascuno avente una SDRAM da 2 Mb e una da 128Mb.

La prima provvede ad un semplice controllo e a un modello lineare di memoria veloce e semplice da usare, spesso utilizzata da appoggio per l’esecuzione della FFT mentre la seconda provvede ad un ampio immagazzinamento di dati e istruzioni.

I due blocchi distinti comprendenti ognuno due DSP, un FPGA e un sito PMC offrono il migliore bilanciamento per le comunicazioni inter-processore, per un facile accesso alle periferiche e un utilizzo ottimo della banda.

Il bus PCI è usato come piano di controllo e condivide una RAM di 64 Mb. I PMC sono mappati sul bus PCI per essere acceduti da un qualsiasi DSP. Esso fornisce anche una connessione diretta a 64 pin con la Virtex II per un’incredibile interfaccia da 800Mb\s configurabile internamente all’FPGA.

Il firmware fornito implementa un potente piano dati per una comunicazione fra i dispositivi e l’hardware esterno a bassa latenza ed ampia banda.

Due porte dati esterne utilizzano connettori SFP implementando un FPDP seriale a 2.5 Gbit\s ognuno.

Due porte Ethernet sono presenti sul PMC 0 e portate sul connettore del backplane attraverso un PICMG2.16. Un ponte PCI-Star Fabric permette una facile integrazione della Quadia nei sistemi più avanzati PICMG 2.17.

La RAM on chip è composta da una cache a due livelli con la L1 di 128 Kbits(data) e 128 kbits(program), e la L2 unificata da 8 Mbits che può essere partizionata attraverso il software.

Tale struttura della cache fa sì che l’utilizzo di memoria esterna sia efficiente all’85% rispetto alla memoria interna. Le altre risorse on chip includono un’interfaccia PCI a 32 bit, due porte McBSP, 64 canali DMA, 3 timer e la porta HPI.

Ogni DSP ha una propria SDRAM da 133 Mhz 64 Mb mappata sul bus a 64 bit EMIF-A. Questo ampio bus è la scelta migliore per l’utilizzo della memoria dedicata e per ottimizzare l’andamento dei task. Il core PCI permette flessibilità, facilità d’uso delle comunicazioni fra i DSP, l’host e ogni altro dispositivo mappato sul bus.

Le interfacce esterne EMIF-B sono da 133 Mhz e sono connesse fortemente alla loro FPGA locale per le comunicazioni inter-processore.

Tutte le porte McBSP sono anch’esse istradate verso la logica.

I due FPGA utente sono gli XC2VP40 Virtex II Pro della Xilinx. Il chip VP40 consiste in 64k di celle logiche, 3.4 k bit di blocchi di RAM, 192 18x18 moltiplicatori dedicati, 8 digital clock managers e oltre 800 I/O per l’utente, così come 2 processori Power PC e 12 transceiver Rocket. Tutto questo lascia ampie risorse per il codice dell’utente finale e per l’integrazione nei più richiesti algoritmi del

signal processing come la conversione down\up, il filtraggio complesso, il ricampionamento, e la ricostruzione del clock.

Gli FPGA sono praticamente disponibili al 100% per il codice dell’utente finale e rappresentano una risorsa enorme. Una VP50 ha i pin compatibili e può essere fornita opzionalmente.

Lo schema a blocchi è il seguente:

2.5.1 Rete di collegamento interna ed esterna

La maggiore innovazione della architettura della Quadia risiede nell’alta connettività fra i DSP, gli FPGA, l’host e l’hardware esterno. In tutte le applicazioni multi processore, l’aspetto cruciale che incide sulle prestazioni globali è l’efficienza della comunicazione intra e inter processore, entrambe in termini di latenza e di carico dei dati trasferiti.

Una particolare attenzione è stata data a questo aspetto e il risultante schema a più percorsi soddisferà le più richieste applicazioni. Una connettività ottima fra i DSP è data da due piani di comunicazione separati:

- Il bus PCI che è il piano di controllo espandibile e facile da utilizzare.

- La matrice di switch logici che è il piano ad alta velocità ed ampia banda con comunicazioni a pacchetti fra i dispositivi e le porte seriali esterne.

2.6 DMDK

Il nuovo DSP DM642 della Texas Instruments appartiene alla famiglia DigitalMedia che è basata sul potente C64.

Dedicato al mercato audio-video integra una interfaccia “glue-less” agli encoder e decoder video e audio.

Questo nuovo SoC (System on Chip) riduce il costo dei sistemi video permettendo di raggiungere prestazioni ineguagliabili e alti livelli di flessibilità.

La scheda DMDK642 trae vantaggio dal DSP DM642 e offre prestazioni avanzate quali: Real Time Clock, interfaccia IDE (hard disk, CDROM, DVDROM drive management), interfacce UART complete su RS232 o RS422, Ethernet e HPI.

Questa scheda è state originariamente progettata per funzionare in stand alone ma a richiesta può essere resa disponibile l’interfaccia PC104.

La DMDK642 ha un reference design completo per lo sviluppo e la prototipazione con FPGA e con una porta per scheda aggiuntiva ad alta velocità.

Fig 18: DMDK.

Lo schema a blocchi della scheda è il seguente:

Si nota al centro della scheda il DSP TMS320DM642 della Texas Instruments con frequenza 600 MHz

Una Sdram da 32 Mb con frequenza di lavoro di 133 MHz affiancata a una flash da 4 Mb.

Capacità di processamento FPGA 50 Kgates con 256 kWords di SRAM locale.

Le interfacce analogiche consentono di collegare un range completo di dispositivi.

2.6.1 Interfacce Video:

BT.601, BT.656, SMPTE nn input e output digitale per accesso diretto alla Video Port del DM642 sul connettore esteso

canali on-board per la cattura del video analogico(NTSC o PAL)

generatore on-board di video analogico (NTSC or PAL)

1 uscita VGA

2.6.2 Interfacce audio:

Un canale on-board per cattura audio analogico (stereo, linea di livello, qualità CD + 1 input microfono)

Un audio on-board analogico per playback (stereo, linea di livello, qualità CD)

2.6.3 Interfacce per uso generale:

Questo ampio numero di interfacce consente parecchie tipologie applicative:

interfaccia Host Port.

Hard Drive Disk su interfaccia IDE.

Interfaccia seriale per i dati: McASP, I2C.

Dual UART con livelli RS232 o RS422.

Ethernet 10/100 Mbps.

Porta di espansione High-speed 32 bits.

Input/Output per uso generale.

2.6.4 Applicazioni

Le applicazioni sono di svariati tipi si passa da applicazioni multimediali a videosicurezza, video entertainment, video conferenza.

2.7 DMCK

La scheda DMCK è una scheda completa che usa sia l’ FPGA che il DSP, per una vasta gamma di applicazioni, incluse, quelle nel campo video e audio, e applicazioni a banda larga, radiodiffusione, video-sicurezza, campo medico, militare,del trasporto, industriale, ecc....

La scheda sfrutta un DSP della Texas Instruments, il DM642, che lavora a 600 MHz, con 32 Mb di Sdram e 4 Mb di memoria Flash.

L’FPGA EP1C20 Cyclone è dell’Altera ed è affiancato da una memoria di 32 Kb.

Il bus asincrono usa delle FIFO per rendere più veloce il trasferimento di dati dal DSP all’FPGA.

In figura 21 si può notare il diagramma a blocchi di questa scheda:

Fig 21: Schema a blocchi.

La piattaforma hardware include delle entrate e uscite audio e video, connesse sia al DSP che all’FPGA, così il trattamento dei dati può essere sviluppato su DSP e successivamente portati su FPGA.

Per quanto riguarda le interfacce, si possono notare l’uscita VGA e canali analogici video NTSC o PAL, mentre in digitale si hanno ingresso e uscita BT.601, BT.656, SMPTE nn, che hanno un accesso diretto al DM642.

Altre interfacce sono:

Interfaccia Host Port.

Interfacce per trattamento dati: McASP (audio digitale ingresso e uscita), I2C.

Dual UART con RS-232 o RS-422.

Ethernet 10/100 Mbps.

Una porta di espansione a 32 bit ad alta velocità.

4 generali di tipo IO.

Per quanto riguarda altre risorse si possono notare un real time Clock RTC, 5 LED programmabili dall’utente, e la porta JTAG, descritta già in altre schede per DSP e FPGA.

2.8 QUIXOTE

Quixote fornisce una notevole integrazione di dispositivi su una piattaforma userfriendly, che può essere impiegata all’interno dei più avanzati sistemi nei campi wireless, radar, video, testing, nel campo dei semiconduttori, dei sistemi fisici ad alta velocità e in altri numerosi settori.

Fig 22:Quixote.

Quixote è una scheda a 64 bit per rilevare, generare e coprocessare segnali; combina un DSP C6416 con un Virtex 2 FPGA, utilizzando il meglio dei due mondi nella tecnologia del processamento del segnale per avere un’estrema flessibilità e efficienza.

Il convertitore A/D duale a 14 bit con canali analogici in ingresso e uscita integra la cattura del segnale e la generazione di forme d’onda sull’interfaccia esterna dell’FPGA.

Un’interfaccia PCI a 64 bit e a 66 MHz, e un PMC facilitano l’integrazione nei sistemi PCI. Infine una PCI a un ponte Star Fabric offre 2 porte a 2,5Gbps al nuovo PICMG2.17 connessa fino a 625 Mbytes al secondo per comunicazioni board to board.

Quixote combina un DSP a 1 GHz a 32 bit in virgola fissa con il più grande FPGA disponibile su un'unica piattaforma hardware.

Lo schema a blocchi della schema è visibile in figura 23:

Una veloce interfaccia digitale esterna è garantita attraverso connettori J4 del PMC site, che presenta 64 pin attaccati direttamente all’FPGA Virtex II o alternativamente configurata come 31 coppie di segnali LVDS.

Questa interfaccia fornisce una flessibile e modulare costruzione dei blocchi per implementare ogni tipo di comunicazione digitale a 800 Mb/sec.

Ci si può connettere direttamente all’FPGA con segnali TTL o LVDS, oppure installare una card mezzanine che implementa il protocollo di comunicazione.

L’interfaccia utente può essere rapidamente implementata in logica FPGA e l’interfaccia mezzanine è realizzata rapidamente con gli specifici connettori con pin di I/O dedicati a ciascuna applicazione. In più , un’altra porta a 32 bit è utilizzabile per general purpose I/O.

Ci sono tre diverse configurazioni per Quixote: Quixote1, Quixote2 e Quixote3.

Quixote 1 è dotato del nuovo DSP TMS320C6416 della Texas Instruments che utilizza l’ultima architettura a virgola fissa a 32 bit nel C6000 series. Lavorando a 1 GHz, questo DSP offre un processamento del segnale a 8000 MIPS. Esso effettua velocemente operazioni in parallelo e l’unità matematica è ottimizzata per applicazioni di processamento del segnale.

Il codice compatibile con gli altri dispositivi C6000 DSP permette la facile inserzione di esistenti programmi dai precedenti dispositivi C62XXX.

Le risorse on chip includono otto unità funzionalmente indipendenti (6 ALU e 2 moltiplicatori), un’ efficiente memoria composta da 16KB di cache L1,16 KB di memoria di programma, 1MB cache L2 mappata RAM, e un turbo decoder. L’interfaccia a 32 bit sul chip PCI è interfacciata all’host bus tramite un ponte PCI e connesso allo SPARTAN 2 e al PMC.

Interfacciate con l’esterno troviamo due memorie: una EMIFA a 64 bit è interfacciata alla VIRTEX II e alla SDRAM, mentre la EMIFB è usata essenzialmente per l’interfaccia con la PCI streaming.

Il chip ha anche due porte seriali sincrone bufferizzate multicanali (MCBSP) connesse alla VIRTEX II e con una capacità di 100 MBPS per canale.

L’FPGA include moltiplicatori hardware 18x18 e contiene più di 12 digital clock, producendo ciascuna 256 suddivisioni di shift di fase e capacità di sintesi di frequenza e mostra un incredibile flessibilità nel gestire il clock on chip e off chip e la sincronizzazione.

I blocchi di memoria on chip in VIRTEX II forniscono un’opportuna memoria ad alta velocità per le FIFO, per la RAM a doppia porta e per la memoria locale, che sono importantissime in un’efficiente progetto logico. E’ semplicemente il dispositivo a più

alte performances per il processamento dei dati e possiede un’avanzata interfaccia esterna.

Ciascuna scheda Quixote ha una SDRAM da 32 Mb che è utilizzata dal DSP: essa è una memoria grande, veloce ed esterna per i dati e per il codice programma.

E’ presente inoltre un front end analogico con due canali in ingresso realizzato con il più recente AD6645 della Analog Devices, dotato di 14 bit e che campiona fino a 105 MHz. Le due uscite analogiche impiegano un AD9764 a 14 bit e 105 MHz,con 5 filtri smoothing di interpolazione a 5 poli, un amplificatore, un buffer single ended di uscita a 50 Ohm.

L’FPGA è caricato con tutte le funzioni che controllano le sue interfacce come il set up della conversione della base dei tempi, la regolazione digitale del guadagno e dell’offset, l’interpolazione dei dati, il controllo delle FIFO, il controllo della base dei tempi PLL, e il controllo del trigger.

La scheda supporta una matrice di base dei tempi configurabile dall’utente che gli consente di selezionare l’ingresso di ciascuna base dei tempi da una serie di sorgenti di clock: timers on e off chip, PLL, e clock esterno. La selezione è effettuata via software con comandi a singola linea.

Il PLL usa un oscillatore a 20 MHz, fornendo la migliore combinazione di un treno di impulsi di clock a alta risoluzione e basse oscillazioni. Il range della frequenza di uscita è 50-105 MHz.

I metodi di triggering START/STOP sono molto flessibili, la scheda può essere configurata secondo un trigger esterno, un trigger analogico a soglia, un trigger analogico pre e post campionamento. Nelle applicazioni multicard alcuni di questi trigger possono essere condivisi fra le card usando la PXI trigger.

IL PMC è collegato con connettori ai pin I/O dell’FPGA, offrendo una velocità altissima, bassa latenza, porta digitale per il movimento dei dati e per la flessibile configurazione e il trattamento dei segnali. Questa porta è capace di trasferire 800 Mb/sec e combinandosi coi blocchi privati della SBSRAM offre innumerevoli possibilità per l’interfaccia digitale.

Il ponte PCI-Star Fabric è integrato sul bus PCI della scheda cosicché ciascun dispositivo sul BUS, PCI, DSP, PMC o memoria può usare Star Fabric come un efficiente connessione dati a tutti gli altri dispositivi connessi a Fabric.

Le seguenti semplici tipologie sono tutte supportate senza aver bisogno di nessuno switch Star Fabric board: sitemi multicard quixote con collegamenti diretti board to board, (sono permesse comunicazioni private DSP-DSP e le porte possono essere settate per avere la massima banda fra board) estensione della PCI a un altro chassis(il DSP del quixote può essere acceduto da altre card su star Fabric.) Topologie più avanzate sono realizzate usando Star Fabric switched card.

I 32 bit di I/O general purpose sono assicurati con un connettore MDR50. Un timer DSP e i pin di start e stop analogici sono

indirizzati tramite questo connettore. La sincronizzazione multiboard è facilitata dall’interfaccia PXI. Non si tratta di un cablaggio complesso solo di una configurazione software.

Clock e interrupt esterni sono presenti e possono essere utilizzati come sorgente di segnale per la configurazioni via software della matrice di timer/trigger. L’interfaccia supporta Compact PCI bus a 64 bit/66MHz.

Gli strumenti di sviluppo per la Quixote sono il TI’s, Code Composer Studio, l’emulatore JTAG debugger e il tool set PISMO. Con obbiettivi specifici DSP e con le librerie periferiche in codice sorgente i singoli comandi di scheda funzionano come applet di utilità, di emulazione, download, esecuzione e debug a alto livello.

2.9 SIGNALWAVE

Fig 24: Signalwave.

La scheda monta un DSP TMS320C6713 che lavora a 225MHz appoggiato da una memoria di 32 Mb a 100Mhz. Il DSP comunica con un FPGA XC2V3000.

2.10 SIGNAL MASTER

Fig 26: Signalmaster.

La scheda monta un DSP della Texas Instruments, il TMS320C6701, che lavora a 150 MHz arrivando a 1 GFlops. Questo DSP è un classico a 32 bit floating point avente il connettore JTAG.

Per quanto riguarda la memoria si trova una Sdram a 16 Mb.

L’FPGA è un VirtexII della Xilinx, con connettore Jtag e 16 Mb di memoria Sdram.

Fig 27: Schema a blocchi.

Una differenza fra queste due schede può essere fatta prendendo in considerazione le interfacce di I/O.

La SignalWave infatti ha un canale stereo a 16 bit a 48 KHz, la seconda invece ne ha due di ingresso e 6 di uscita a 24 bit a 96 KHz.