CAPITOLO 5

Realizzazione del prototipo

5.1 Introduzione

Una volta ottenuta la descrizione a livello di celle standard del controllore di fase attraverso il sintetizzatore Design Analyzer di SYNOPSYS, si è in grado di importare tali descrizioni in formato Verilog all’interno dell’ambiente CADENCE dove si possono utilizzare insieme alla parte fullcustom per creare lo schematico complessivo del chip e utilizzare poi il tool CELLENSEMBLE per effettuare il floorplanning, cioè le operazioni di placement e routing del chip.

Questo strumento CAD assiste il progettista nelle operazioni di floorplanning e consente quindi di ottenere, partendo dal progetto schematico specificato fino a livello delle celle standard, il layout completo del chip tramite il quale si può procedere alla creazione dei file di descrizione delle maschere (GDSII), nonché all’estrazione delle capacità parassite da utilizzare in back-annotation per effettuare la simulazione post-layout del chip.

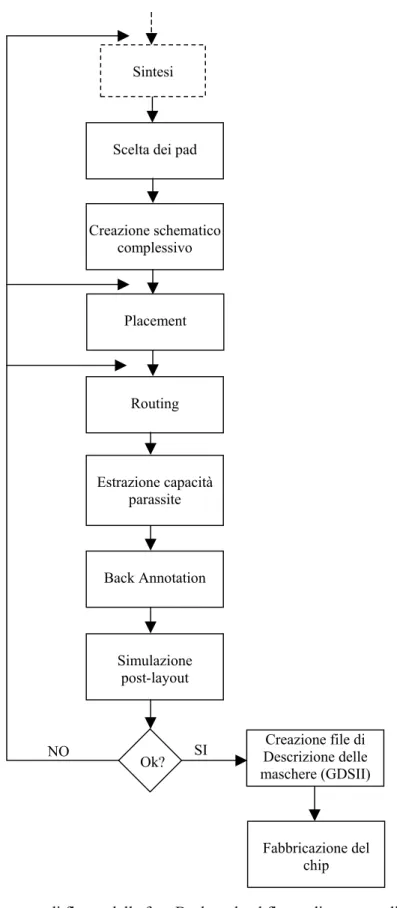

In Figura 5.1 presentiamo un diagramma di flusso che rappresenta i principali passaggi che portano dalla sintesi alla realizzazione del chip, cioè la cosiddetta fase di back-end. Nei prossimi paragrafi approfondiremo ciascuno dei passaggi.

chip NO SI Fabbricazione del Creazione file di Descrizione delle maschere (GDSII) Ok? Simulazione post-layout Back Annotation Estrazione capacità parassite Routing Placement Creazione schematico complessivo Sintesi

Scelta dei pad

Figura 5.1 Diagramma di flusso della fase Back-end nel flusso di progetto di un circuito integrato

5.2 Creazione dello schematico complessivo

Il tool di sintesi e ottimizzazione logica Design Analyzer di SYNOPSYS, ricevuta ingresso la descrizione VHDL di qualsiasi dispositivo ed effettuata la sintesi, permette di creare un file del tipo SDF (Standard Delay Format) il quale contiene le informazioni timing del circuito sintetizzato e ottimizzato a livello di celle standard. Per poter essere letta da CADENCE la netlist del sistema sintetizzato deve essere in formato Verilog in quanto il design-kit 3.30 della AMS comprende la libreria delle descrizioni Verilog di tutte le celle standard e non quella VHDL.

Il primo passo da fare è quello di importare in CADENCE la descrizione Verilog prodotta da SYNOPSYS, operazione che può essere fatta utilizzando l’apposito tool denominato VERILOG-IN. Fatto ciò abbiamo la descrizione schematica del controllore di fase: a questo livello il circuito viene visto come un insieme di celle standard con le loro interconnessioni, e l’organizzazione gerarchica del progetto viene trasformata in una gerarchia fisica. Mettendo insieme anche il simbolo della parte relativa al blocco fullcustom e collegando tra loro i simboli, possiamo costruire lo schematico di tutto il blocco Deskewer. I passi da effettuare sono schematicamente i seguenti:

Floorplanning, ossia l’organizzazione dell’insieme di celle standard in regioni o gruppi in base alla loro gerarchia fisica. Con questo passo vengono così imposti dei vincoli di piazzamento in modo da mantenere ravvicinate standard cell appartenenti allo stesso livello gerarchico e quindi in modo da diminuire la lunghezza dei collegamenti. Viene altresì definita la posizione dei piedini di ingresso/uscita (pad) di cui non ci occuperemo.

Placement, ossia la disposizione nello spazio fisico dell’insieme di standard cell e dei pad.

Routing, ossia il tracciamento dei collegamenti tra le varie celle standard e dei segnali del blocco fullcustom

.

5.3 Report

della

sintesi

del controllore di fase

Realizzata la sintesi del controllore di fase il tool Design-Analyzer di SYNOPSYS permette di generare un file di report in cui vengono restituiti i parametri elettrici, geometrici, temporali e fisici del dispositivo visto come insieme di celle standard. Ricordiamo che a livello gerarchico il controllore di fase è costituito da due blocchi (bisezione e differenziale al nonio). Per il blocco di bisezione il numero di celle calcolato è pari a 155 per un’area totale stimata pari a 18.98 mm2, il numero di flip-flop risulta essere pari a 25 per una capacità di carico complessiva di 0.40 pF per il segnale di clock. Per il blocco differenziale al nonio il numero di celle è risultato 183 per un’area complessiva stimata di 16.59 mm2, il numero di flip-flop relativi a tale blocco è 15 per una capacità di carico totale di 0.24 pF per il segnale di clock. È necessario osservare che la stima dell’area occorrente effettuata da SYNOPSYS comprende anche l’area relativa alle interconnessioni ed è una stima piuttosto grossolana e sicuramente per eccesso.

In fase di sintesi non è stata prevista la bufferizzazione automatica del segnale di clock che deve andare in ingresso a tutti i flip-flop presenti nella rete. Visto il limitato numero di flip-flop presenti nel nostro controllore la distribuzione del segnale di clock non ha richiesto particolari attenzioni. Infatti è stato sufficiente utilizzare un unico buffer per fornire il clock a tutti i flip-flop presenti nei due blocchi, come mostrato nella rappresentazione schematica in Figura 5.2.

Clk_blocco bisezione INV 2 INV 1 Clk Clk_blocco differenziale

I due inverter sono stati istanziati direttamente nello schematico complessivo. Complessivamente per il controllore di fase l’area stimata è pari a 35.57 mm2 con un numero di celle standard pari a 238, un numero totale di flip-flop pari a 40 per una capacità di carico pari a 0.64 pF del segnale di clock.

5.4 Floorplanning del controllore di fase

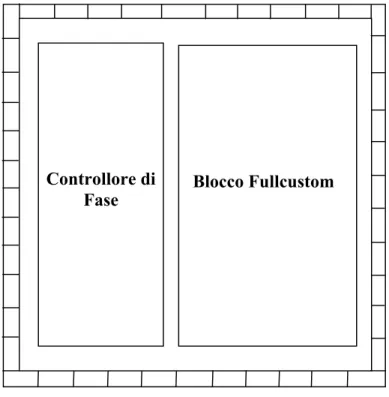

Prima di procedere con il placement e il routing del chip nel suo complesso, è necessario (approccio bottom-up) organizzare il floorplannig posizionando i macroblocchi che si intendono utilizzare. Il controllore di fase è stato posizionato opportunamente a sinistra della parte fullcustom in modo da facilitare il compito del router, infatti tutti i segnali di controllo del blocco fullcustom sono stati previsti, in fase di layout, nel lato sinistro.

Il floorplanning di questo macroblocco non ha presentato particolari problemi in quanto è costituito da solo 238 celle standard che abbiamo organizzato in quattro righe. I pin relativi alla comunicazione con la parte fullcustom sono stati posizionati sul lato destro, il pin del clock e del reset sul lato sinistro, mentre i pin dell’alimentazione e di ground sono stati posizionati rispettivamente sul lato superiore e inferiore.

Una volta posizionati i pin, effettuati il placement e il routing in maniera automatica e controllato il rispetto delle regole di layout (DRC), si è in grado di creare una vista abstract del blocco che potrà essere utilizzata a livello gerarchico più alto nel floorplanning complessivo di un chip.

5.5 Placement

Una volta che abbiamo a disposizione lo schematico complessivo del nostro chip e dopo che abbiamo deciso il posizionamento dei macroblocchi, possiamo procedere nel flusso di progetto passando alla fase del piazzamento. Questa fase è caratterizzata da quattro passi da eseguire in successione:

Piazzamento dei pad.

Piazzamento dei macro-blocchi. Piazzamento delle celle standard. Piazzamento delle power-cell.

Per quanto riguarda il primo punto i pad possono essere piazzati a nostro piacimento scrivendo un apposito file in cui è descritta la posizione di ciascuno di essi. La procedura più agevole per ottenere questo risultato è quella di utilizzare il tool CELLENSEMBLE per piazzare automaticamente i pad, generare successivamente sempre in modo automatico il file di descrizione, modificarlo in base alle nostre esigenze e infine farlo rileggere al programma il quale posizionerà i pad secondo la nuova descrizione. Possiamo osservare che se stiamo eseguendo il floorplanning di un intero chip, in questa fase si posizionano i pad di ingresso e uscita veri e propri. Se invece stiamo realizzando un macroblocco si scelgono più semplicemente i punti i cui i segnali di ingresso e uscita si affacciano sul perimetro del nostro blocco. Sottolineiamo che è diverso realizzare il placement a seconda del caso in cui consideriamo celle elementari o macroblocchi; nel primo caso è più semplice dato che sono disponibili librerie di celle realizzate in modo tale da avere tutte la stessa altezza, mentre i macroblocchi hanno dimensione casuale. É per questo che il piazzamento delle celle standard è effettuato in modo automatico mentre quello dei macroblocchi deve essere effettuato in modo manuale. I criteri di ottimizzazione nel piazzamento possono essere:

Minimizzazione dell’area.

Minimizzazione delle interconnessioni.

Minimizzazione dei ritardi e quindi massimizzazione della velocità.

In Figura 5.3 possiamo osservare la disposizione nell’area del chip del controllore di fase rispetto al blocco fullcustom dove a sinistra troviamo il macroblocco corrispondente al controllore di fase e a destra quello relativo alla parte fullcustom. Il blocco semicustom è stato posizionato manualmente. Durante il piazzamento è stata inserita anche una certa quantità di particolari celle di collegamento, dette feed-trough, che consentono in fase di routing di attraversare una riga di celle standard con una pista di metal.

Blocco Fullcustom Controllore di

Fase

Figura 5.3 Placement

A questo punto, per completare la fase di piazzamento, è necessario inserire e posizionare opportunamente le power cell. A questa tipologia di celle appartengono le cap cell e le power feed cell. Le prime sono sempre necessarie in quanto poste agli estremi destro e sinistro di ogni riga consentono un corretto

collegamento delle righe di celle standard con le metal esterne di alimentazione. Per spiegare la funzione delle power feed cell bisogna premettere che tutte le celle standard possiedono piste di alimentazione di ampiezza prefissata dalla tecnologia, le quali possono sopportare una certa corrente massima. Tali piste si collegano automaticamente tra loro per contatto quando le celle sono posizionate una accanto all’altra in una riga. Quindi esiste un limite superiore al numero di celle che compongono una riga, sempre che non si provveda a far arrivare l’alimentazione non solo agli estremi ma anche nei punti intermedi attraverso l’inserimento di colonne di power feed cell. Il numero massimo di celle che costituisce una riga senza interruzioni dipende dalla potenza massima sopportabile dalle metal di alimentazione per ogni riga, dalla frequenza di clock, da un fattore di switching activity e dal consumo di potenza media per unità di frequenza di una cella.

5.6 Routing

Il routing è quella fase di progetto in cui si realizzano, in parte in modo automatico e in parte in modo interattivo, i collegamenti necessari tra le celle standard, i macroblocchi e i pad per ottenere il layout conclusivo. Si tratta di un problema di notevole importanza che diventa sempre più serio con il progredire della tecnologia in relazione al fatto che si realizzano transistori sempre più piccoli mentre le connessioni, soprattutto per quanto riguarda la lunghezza, non scalano con la stessa velocità, con tutte le conseguenze che questo, sia in termini di ritardo che di ingombro d’area, comporta. A questo proposito è stato osservato che, in media oggi, in un chip solo circa metà della sua area è occupata da celle di elaborazione, mentre il resto dello spazio serve tutto per le connessioni.

Il primo passo della fase di routing è la creazione dei canali; infatti una volta piazzate le celle, CELLENSEMBLE può individuare gli spazi orizzontali e verticali nei quali potrà far passare le metal necessarie per effettuare i

collegamenti. Questi canali, durante le successive operazioni di global e detailed routing, saranno opportunamente ristretti o allargati in funzione del numero e delle dimensioni dei collegamenti che dovranno contenere. Prima di procedere al routing vero e proprio bisogna definire caratteristiche particolari da assegnare a net speciali, tipo ampiezza delle metal di VDD e GND, minimizzazione dello skew tra i clock, assegnando a ciascuno di essi una priorità maggiore rispetto alle altre reti. Il passo successivo è quello del global routing durante il quale non viene realizzato il routing fisico ma vengono solo determinati i canali in cui ogni net dovrà passare e stabilite le connessioni logiche tra i pin delle celle e i canali. Per avere un certo grado di libertà nel global routing delle alimentazioni e per tener conto della presenza delle barre di power cell, il routing deve essere svolto in maniera manuale utilizzando i comandi del router interattivo. Il router, dopo aver effettuato l’operazione una prima volta, procede ad una ottimizzazione durante la quale la disposizione delle celle standard viene cambiata per ridurre la congestione del routing e si tenta di distribuire i collegamenti in modo uniforme in tutto il chip. In questa fase le celle possono quindi essere scambiate tra loro e per alcuni nodi può, se necessario, essere rieseguito il routing.

L’ottimizzatore lavora con un algoritmo di annealing simulato nel quale si fissa una funzione di costo (basata sulla lunghezza dei collegamenti) e si considera il costo di ogni spostamento che viene eseguito solo se provoca una diminuzione del valore attuale della funzione. Questi spostamenti avvengono sotto il controllo di una variabile temperatura fittizia: la quantità degli spostamenti permessi e la distanza tra le celle scambiabili sono funzioni crescenti della temperatura. Essa viene fatta partire da un valore alto per consentire nella fase iniziale molti spostamenti, poi il layout viene progressivamente “raffreddato” fino alla sua stabilizzazione.

Per ottenere migliori risultati è consigliabile effettuare più volte l’operazione di ottimizzazione anche se essa necessita di un tempo di elaborazione molto elevato.

Una volta terminato il global routing resta da fare il detailed routing che consiste nel routing fisico vero e proprio. Il flusso di progetto relativo alla tecnologia AMS a 0.35 µm consente l’uso di tutte e tre le metal per il routing.

Nonostante il routing venga effettuato in modo automatico, ci possono essere comunque geometrie che violano le regole di layout, quindi è necessario effettuare una verifica DRC.

In Figura 5.4 viene rappresentata la struttura tipica di chip semicustom in cui sono messe in evidenza le righe di celle elementari, i canali di routing e le celle di I/O (pad più circuiti di I/O).

CELLE DI I/O (pad + circuiti I/O)

Righe di celle standard

Canali di routing

Figura 5.4 Struttura di una standard cell

5.7 Simulazione

post-layout

La simulazione post-layout è simile alla simulazione pre-layout eccetto che le connessioni tra le porte e le celle logiche in questo caso sono sostituite con

circuiti RC, come mostrato in Figura 5.5. Per effettuare una verifica della correttezza delle operazioni di floorplanning viste finora, e per evidenziare eventuali effetti dannosi sulla funzionalità del sistema causati dalle capacità parassite dovute alle interconnessioni, è necessaria la simulazione post-layout dell’intero chip. Ci permette, ad esempio, di verificare che non ci siano problemi di violazione dei tempi di setup e di hold per i flip-flop utilizzati.

La parte fullcustom del nostro sistema è già stata ampiamente testata con le simulazioni analogiche SPECTRE descritte nel capitolo 3. In termini di tempo e di memoria disponibile sulle normali workstation è impensabile effettuare una simulazione analogica dell’intero chip in quanto il numero dei transistori risulta troppo elevato. Metal 2 Metal 1 AND OR C R (a) (b)

Figura 5.5 (a) Layout; (b) Equivalente elettrico

Per ridurre i tempi di simulazione e l’occupazione di memoria pur tenedo conto delle capacità parassite introdotte dalle interconnessioni di routing, si può ricorrere o ad una simulazione VERILOG SWITCH-XL in ambiente CADENCE o ad una simulazione Design-Analyzer in ambiente SYNOPSYS. Queste simulazioni vengono fatte considerando per le celle standard solo la funzione logica e il ritardo introdotto, quindi sono di gran lunga più veloci rispetto a quelle analogiche.

Il primo passo per arrivare alla simulazione Verilog è costituito dall’estrazione delle capacità parassite dal layout conclusivo del chip. In ambiente

SYNOPSYS è stata creata una descrizione del controllore di fase detta SDF (Standard Delay Format) che serve per effettuare la back-annotation prima della simulazione vera e propria. Dopo essere stata effettuata la sintesi, nella Command Window del Design Analyzer di SYNOPSYS viene passato manualmente il comando:

write_sdf -version 2.1 Controller_GL.sdf

che genera il file SDF del controllore semicustom.

L’operazione successiva è la creazione della netlist Verilog che viene costruita partendo dalla descrizione schematica del chip di tutti i blocchi in esso utilizzati, ad eccezione di quello relativo alla parte fullcustom per il quale bisogna usare la vista estratta dal layout. A questo punto dobbiamo osservare che VERILOG-XL prevede due primitive che modellano il comportamento dei transistori NMOS e PMOS con tre terminali, mentre i transistori estratti da CADENCE sono quelli a quattro terminali. Dunque è stato necessario, una volta ottenuta la netlist, introdurre in essa i modelli Verilog dei transistori PMOS4 e NMOS4 che sono i seguenti:

module nmos4 (B,D,S,G); input B,D,S,G; tranif1 # (0.1) (D,S,G); endmodule module pmos4 (B,D,S,G); input B,D,S,G; tranif0 # (0.1) (D,S,G); endmodule

dove i modelli tranif simulano un interruttore: tranif0 inizia condurre dopo 0.1 ns dal momento in cui il segnale di controllo G diventa 0, tranif1 si comporta in

maniera complementare cioè conduce quando G vale 1. L’inserimento di questi modelli consente di far riconoscere al simulatore Verilog i transistori della parte fullcustom.

Una volta prodotta la netlist si può procedere alla preparazione di un file Verilog contenete la descrizione degli stimoli esterni e infine si può lanciare la simulazione che consta di tre fasi. La prima è quella della compilazione, in cui si ottiene la struttura dati necessaria utilizzando anche i file Verilog di libreria forniti da AMS, che contengono, oltre alla descrizione funzionale di ogni cella, i ritardi nominali ad essa corrispondenti (nei casi di funzionamento worst, typical e fast) nonché gli eventuali dati relativi ai controlli temporali.

La seconda fase è quella detta back-annotation, in cui si usa il file SDF prodotto precedentemente per annotare nella netlist Verilog i ritardi dovuti alle capacità parassite delle interconnessioni. E per finire, la terza fase consiste nella simulazione vera e propria prima di effettuare la quale è possibile scegliere quali segnali monitorare, inserire break-point, e effettuare altre funzioni di debugging. Questi passi ci permettono di verificare le funzionalità del chip.