1 Contributi di potenza in tecnologia CMOS.

Negli ultimi anni, è aumentata notevolmente la domanda di dispositivi elettronici portatili da parte dei consumatori (telefonia mobile, computer portatili, applicazioni avioniche, spaziali, automotive ecc.). Per far sì che la batteria di tali dispositivi sia piccola e leggera, la riduzione della potenza dissipata è diventata un fattore di progetto di primo ordine. Tale fattore deve essere considerato anche per i dispositivi non-portatili: infatti con un basso consumo di potenza, saranno minori le spese per l’alimentazione e il raffreddamento. A questo scopo bisognerà focalizzarsi non tanto sulle prestazioni e sull’area dei dispositivi, bensì su opportuni metodi di riduzione della potenza. Prima di far ciò si analizzeranno le varie cause di dissipazione di potenza. In un circuito CMOS progettato con approccio sincrono, la potenza media può essere così calcolata:

leakage circuit short switching avg P P P P = + − +

1.1 Potenza di switching.

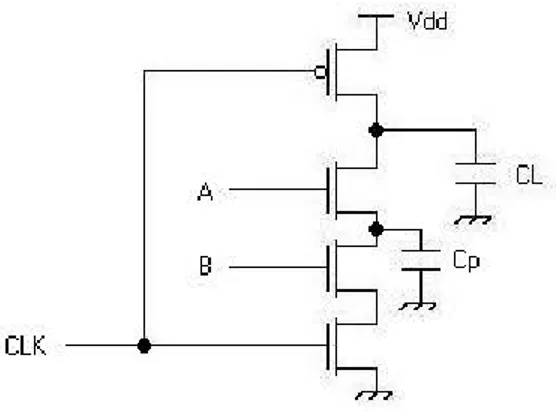

E’ la componente della potenza necessaria per caricare le capacità inevitabilmente presenti nel circuito e dovute ai gate dei transitori e alle interconnessioni. Essa rappresenta la più larga percentuale della potenza totale dissipata in un circuito (può costituirne il 70 % - 90 %). Supponiamo di avere una generica porta CMOS come quella rappresentata in Figura 1-1:

Figura 1-1 Modello per il calcolo della potenza di switching.

Se nell’intervallo di tempo [to,t1], si ha una transizione dal livello basso a livello alto dell’uscita, allora l’energia erogata dall’alimentazione è pari a:

∫

∫

=∫

= = = → dd V L dd out L t t t t dd out L dd dd dd dt V C dV V C dt dV C V dt t I V E 0 2 1 0 1 0 1 0 ) (Si sa che che l’energia immaga zzinata nel condensatore dopo che si è caricato, è pari a: L dd C V C E 2 2 1 =

Quindi, di tutta l’energia E0→1, solo metà è stata immagazzinata nel condensatore, l’altra metà è stata dissipata nella pull-up network (PUN). Supponiamo ora che Vout ritorni al livello logico basso: l’alimentazione né consuma né assorbe energia (la pull-up network è interdetta) e il condensatore

Si consideri ora un progetto sincrono in cui ogni nodo può commutare solo dopo un fronte in salita del clock. Supponiamo che un generico nodo commuti dal livello logico basso al livello logico alto, n volte nel tempo NTclk, allora la potenza media dissipata dall’alimentazione per caricare e scaricare quel nodo vale: = = = →∞ →∞ clk dd L N clk N avg NT N n V C NT N E P lim ( ) lim ( ) 2 clk dd L clk dd L N C V f C V f N N n 2 1 0 2 ] ) ( [lim →∞ ≡ → = α

Dove si è definito il fattore di switching activity (α0→1) del nodo, cioè il numero medio di commutazioni del nodo (dal livello logico basso al livello logico alto) in un ciclo di clock. Ovviamente per calcolare la potenza di switching totale di un circuito bisogna fare la somma, su tutti i nodi del circuito, dei singoli contributi, cioè: clk dd eff clk dd i L i clk dd L avg iC iV f i C i V f C V f P =

∑

[α0→1() () 2 ]=[∑

α0→1( ) ( )] 2 ≡ 2Dove Ceff è la capacità efficace: cioè il circuito si comporta, in termini di potenza, come se avessimo un’unica capacità di valore Ceff che commuta dal livello logico basso al livello logico alto una volta ogni ciclo di clock.

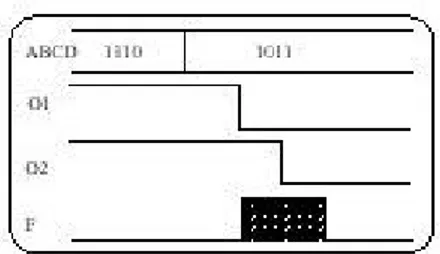

Nei circuiti a logica dinamica si può presentare il fenomeno detto “charge sharing” che contribuisce ad aumentare la potenza di switching. Consideriamo ad esempio una porta NAND con albero logico ad NMOS (quindi il transistore di precarica sarà di tipo PMOS):

Figura 1-2 NAND dinamica.

Supponiamo che l’ingresso A sia al livello logico alto e l’ingresso B sia al livello logico basso. Nella fase di precarica l’uscita viene caricata alla tensione Vdd. Nella fase di elaborazione, l’uscita deve mantenersi alla tensione Vdd, ma

poiché il transistore NMOS connesso all’ingresso A è acceso, la carica presente sulla capacità di uscita si distribuisce in parte sulla capacità parassita Cp. Quindi la

tensione di uscita diminuisce della quantità:

dd p L p dd p L L dd out V C C C V C C C V V + = + − = ∆

Nella fase successiva di precarica, l’alimentazione eroga la seguente energia: 2 dd p L p L out L dd V C C C C V C V E + = ∆ =

Ciò non va bene perché in queste condizioni la tensione su CL dovrebbe

rimanere costantemente al valore logico alto, e quindi l’alimentazione dovrebbe dissipare una potenza nulla. Invece la potenza dissipata dall’alimentazione sarà:

clk dd p L p L f V C C C C P 2 + =

1.1.1 Influenza della funzione logica sulla potenza di switching.

Il tipo di funzione logica svolta darà origine a risultati diversi per quanto riguarda la probabilità statica di transizione. Consideriamo l’esempio di una semplice porta NOR in cui gli ingressi possono cambiare al massimo una volta ogni ciclo di clock, e inoltre le 4 possibili coppie in ingresso (00, 01, 10, 11) sono equiprobabili. Allora la probabilità che l’uscita commuti dal livello logico basso al livello logico alto in un ciclo di clock è data dalla probabilità che essa sia, in un certo istante, allo stato 0 e che al ciclo successivo sia allo stato 1; quindi supponendo che i 2 eventi siano indipendenti avremo:

16 3 4 1 4 3 ) 1 ( 0 0 1 0 1 0→ = p p = p − p = × = p

Se invece si considera una porta XOR, sotto le stesse ipotesi avremo:

4 1 2 1 2 1 ) 1 ( 0 0 1 0 1 0→ = p p =p −p = × = p

Ne segue che, sotto le ipotesi di sopra, una porta XOR a due ingressi avrà un’attività di commutazione superiore rispetto ad una porta NOR a due ingressi

1.1.2 Influenza della famiglia logica sulla potenza di switching.

Bisogna scegliere tra una logica CMOS di tipo statica o dinamica. Con un’implementazione dinamica di una porta NOR, la potenza viene consumata durante la fase di precarica ogni volta che la capacità si è scaricata nel precedente

ciclo. Nel caso in cui gli ingressi siano ancora equiprobabili avremo che la probabilità di transizione sarà data da:

75 . 0 0 1 0→ = p = p

Mentre per una porta NAND dinamica avremo:

25 . 0 0 1 0→ = p = p

Da questi casi si può vedere che la probabilità di transizione è più grande per un’impleme ntazione dinamica. Infatti, usando una logica dinamica, l’attività di commutazione non dipende dallo stato precedente come invece accade in una logica statica. Se gli ingressi di una porta statica rimangono costanti allora anche l’uscita rimane costante; ciò può non avvenire per una porta dinamica: ad esempio durante la fase di elaborazione, la configurazione degli ingressi può imporre costantemente un valore logico basso in uscita, mentre nella fase di precarica l’uscita deve commutare sempre al valore Vdd.

1.1.3 Influenza della statistica dei segnali sulla potenza di

switching.

In genere gli ingressi di una porta logica non sono sempre equiprobabili come si è supposto precedentemente. Ciò può avere un forte impatto sull’attività di commutazione. Si consideri ancora una porta NOR, in cui i 2 ingressi A e B hanno rispettivamente una probabilità P e a P di essere al livello logico alto; b

allora si ha: ) 1 )( 1 )]( 1 )( 1 ( 1 [ ) 1 ( 1 1 1 0 1 0 p p p p Pa Pb Pa Pb p → = = − = − − − − −

1.1.4 Influenza della correlazione fra i segnali sulla potenza di

switching.

Fino ad ora si è fatta l’ipotesi dell’indipendenza fra i segnali in ingresso alle porte logiche in esame. Anche questo non è sempre vero. Per calcolare la probabilità di transizione dell’uscita bisogna perciò applicare delle formule più generali che tengano conto delle probabilità condizionate. Ad esempio, per la solita porta NOR con gli ingressi A e B si avrà:

)) 0 0 ( ) 0 ( ))] 0 0 ( ) 0 ( ( 1 [ ) 1 ( 1 1 1 0 1 0 = = = = = = − = = − = = → B A P B P B A P B P p p p p p

1.1.5 Influenza della topologia del circuito sulla potenza di

switching.

Per valutare l’attività di commutazione di una rete, non bisogna soffermarsi solo sulla funzione logica svolta e sulle statistiche dei segnali in ingresso, ma bisogna considerare anche la temporizzazione del circuito. Infatti a causa dei ritardi diversi tra ciascun ingresso e l’uscita, si possono osservare delle commutazioni spurie sull’uscita prima che essa si stabilizzi al suo valore di regime. Se ad esempio si considera una rete sequenziale sincrona, proprio per questo motivo si possono avere dei nodi con α0→1>1, cioè un nodo può

commutare dal livello logico basso al livello logico alto, più di una volta ogni ciclo di clock. Se invece si considera un modello ideale delle porte senza ritardi (zero-delay model), chiamando N la variabile aleatoria : “numero di commutazioni

1

0→ di un generico nodo della rete all’interno di un periodo di clock”, allora N è una variabile aleatoria discreta che può assumere solo i valori 0 e 1. In questa ipotesi, si ha che il coefficiente α0→1 può anche essere definito in modo statistico e non più deterministico, quindi si può definire come valor medio della variabile aleatoria N:

1 0 1 0 1 0→ ≡ E[N]=1P(N =1)+0P(N =0)= P(N=1)= p p = p → α

Per scegliere fra due implementazioni diverse della stessa funzione, bisogna tener conto non solo della probabilità statica dei nodi ma anche del loro comportamento “dinamico”.

Si consideri ad esempio la funzione F = ABCD che può essere implementata nei seguenti modi:

Figura 1-3 Chain structure vs Tree structure.

Supponiamo che i 4 ingressi siano incorrelati ed equiprobabili. Dal punto di vista della probabilità statica, tra le due soluzioni cambia solo la probabilità di transizione del nodo O2 che è minore nell’implementazione a catena, infatti:

64 7 8 1 8 7 ) 2 ( ) ( 1 0→ O = × = p chain 16 3 4 1 4 3 ) 2 ( ) ( 1 0→ O = × = p tree

Per quanto riguarda invece il comportamento dinamico, se si considera ad esempio una commutazione 1110→1011 degli ingressi ABCD, e si suppone un ritardo unitario per ogni porta AND, avremo per la struttura a catena una temporizzazione del tipo:

Figura 1-4 Presenza di transizioni spurie.

Quindi anche se il nodo F non dovrebbe commutare, esso sta alto per 2 unità di tempo a causa dei cammini non bilanciati. Nella soluzione ad albero invece O1 e O2 vanno a 0 contemporaneamente e il nodo F rimane sempre al livello basso.

L’effetto delle transizioni spurie si può notare soprattutto nei circuiti sommatori in cui all’aumentare del numero di bit, aumenta il ritardo nella catena di propagazione del carry.

Sebbene sia possibile eliminare questo problema (ad esempio utilizzando dei cammini bilanciati), sotto questo punto di vista è meglio usare una logica dinamica perché nella fase di elaborazione non sono permesse transizioni spurie (in questa fase, se la tensione va al livello basso, non può più ritornare al livello alto) e perciò se il progetto è ben fatto ogni nodo non può commutare dal livello logico basso al livello logico alto più di una volta ogni ciclo di clock.

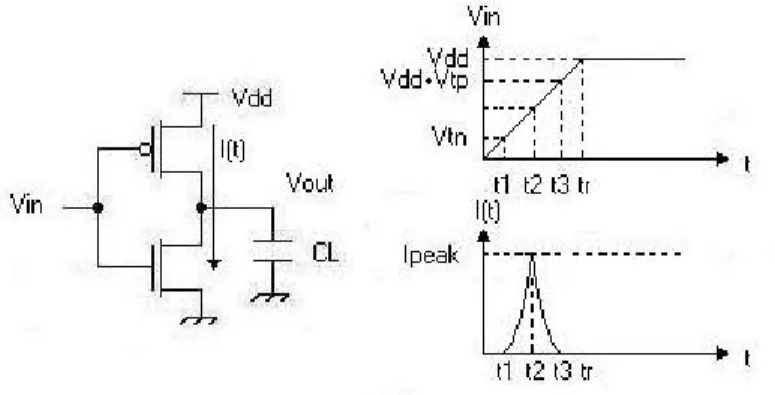

1.2 Potenza di cortocircuito.

I tempi di salita e discesa non nulli dei segnali in ingresso alle diverse porte logiche provocano un percorso di corrente tra V e dd GND (da qui deriva il termine “potenza di cortocircuito”). Anche se ciò avviene per brevi periodi di tempo, la potenza di cortocircuito può essere significativa e può raggiungere il 30% della potenza totale dissipata in un circuito. C onsideriamo l’esempio dell’inverter CMOS statico rappresentato in Figura 1-5:

Figura 1 -5 Corrente di cortocircuito in un inverter CMOS statico.

Nel periodo di tempo in cui

p n in dd t

t V V V

V < < + entrambi i transistori sono accesi, quindi si ha una corrente tra alimentazione e massa diversa da zero. Ricordiamo che in un MOS vale la relazione

L W Co x µ β = . Supponiamo per ipotesi: p n t t V

V = e βn =βp allora si ha che quando Vtn <Vin <Vdd /2 il transistore NMOS è in saturazione (infatti VDSn >VGSn −Vtn). Quindi in questo intervallo di tempo, la corrente I(t) è data da:

2 2 ) ( 2 ) ( 2 ) ( n n n t r dd n t GS n t V t V V V t I = β − = β −

Se si ha una commutazione ogni ciclo di clock (dal basso all’alto oppure viceversa) della tensione Vin, la potenza di cortocircuito è data da:

∫

∫

= − = = − 2 1 2 0 ) ( 2 2 ) ( 1 t t t r dd n clk dd dd clk circuit short t V dt t V T V dt t I V T P n clk T β clk r t dd clk r n V V clk r n V V t f T t dx x T t n n t dd ∝ − = =∫

− 3 2 / 0 2 ) 2 ( 3 β βdimostrare che le correnti di cortocircuito diventano più significative quando i tempi di salita/discesa degli ingressi sono più lunghi dei tempi di discesa/salita dell’uscita. Supponiamo che l’ingresso Vin commuti da 0 V a Vdd e che in uscita sia presente una capacità molto elevata in modo che la tensione d’uscita vari più lentamente dell’ingresso: durante il tempo di salita di Vin, la tensione tra drain e source del transistore PMOS rimane nulla e quindi in questo intervallo di tempo la corrente Ip sarà sempre nulla. In seguito, quando comincia a calare la tensione d’uscita, il segnale di ingresso è già a 5 V e quindi il PMOS risulterà interdetto. Se invece la capacità d’uscita è piccola in modo che la tensione d’uscita varia più velocemente di quella di ingresso si ha l’effetto opposto: ora la tensione tra drain e source del PMOS va subito a −Vdd e poi durante la transizione del segnale in ingresso la corrente di cortocircuito può essere notevole (pari alla corrente di saturazione del PMOS).

Se si hanno delle reti a più livelli di logica bisogna fare in modo che per ogni stadio, i tempi di salita/discesa degli ingressi siano maggiori di quelli delle uscite: ciò si può realizzare usando delle capacità che aumentano passando dai primi stadi a quelli successivi (cioè usando dei transistori con larghezza di canale che aumenta passando da uno stadio al successivo). In questo modo si può ottenere che la potenza di cortocircuito contribuisce meno del 10% alla potenza dinamica complessiva.

Un’altra soluzione per ridurre o addirittura eliminare la potenza di cortocircuito può essere quella di ridurre la tensione di alimentazione in modo che:

p n t

t

dd V V

V < + . Così non si avranno mai degli intervalli di tempo in cui condurranno contemporaneamente i transistori PMOS e NMOS. Spesso, però, quest’ultima soluzione non è accettabile in quanto, come si vedrà nel Paragrafo 2.1, al tendere di Vdd a Vtn aumentano in modo eccessivo i ritardi di propagazione

1.3 Potenza di leakage.

Ci sono principalmente tre tipi di contributi alla potenza di leakage: quello dovuto alle correnti inverse delle giunzioni pn in interdizione relative ai pozzetti di drain/source, quello dovuto alle correnti sottosoglia che attraversano il canale anche quando il transistore è spento, quello dovuto alla corrente di gate-tunnel tra gate e substrato.

1. In genere il potenziale del substrato di un transistore PMOS è a Vdd

e per un NMOS è a 0 V, allora le giunzioni pn tra i pozzetti di drain/source e il substrato saranno sempre interdette, quindi la corrente di leakage sarà: IL =AJS, dove A è l’area del pozzetto di drain/source e Js è la densità di corrente di leakage.

2. Quando la tensione tra gate e substrato supera il punto di debole inversione ma ancora non raggiunge la tensione di soglia, allora scorre una corrente di diffusione tra source e drain che dipende esponenzialmente dalla tensione VGS [1]: / (1 KT/q)

V q nKT V V DS DS t GS e Ae I − − − = .

Dove A è una costante che dipende dalla tecnologia, n è un parametro di merito del transistore detto coefficiente di subthreshold swing. Dalla formula si nota che per

mV q KT VD S >> / ≈26 (a 25°C) allora vale: (1 ) 1 / ≈ − − q KT VDS e ;

quindi la corrente ID S diventa indipendente dalla tensione VD S. 3. In seguito allo scaling dei dispositivi CMOS, si tende

continuamente a ridurre lo spessore dell’ossido di gate per evitare effetti di canale corto e per aumentare la transconduttanza dei transistor. Ciò provoca il passaggio di una certa corrente per effetto tunnel tra gate e substrato. Se ad esempio si considera un NMOS

effetto tunnel, una corrente di portatori maggioritari (lacune) che dal gate raggiungono il substrato per effetto tunnel. Da risultati sperimentali si può osservare che con spessori dell’ossido di 2.5 nm la corrente di gate tunnel è nove ordini di grandezza più bassa della corrente di drain [20].

In genere per circuiti che sono attivi (non in standby) la potenza totale di leakage è minore dell’1% della potenza totale. Essa però potrebbe essere significativa in sistemi che restano in standby per lunghi periodi di tempo e in cui si può avere: Pleakage >>Pdinamica .

Per una NAND a 2 ingressi appartenente alla tecnologia che si è usata in questo lavoro di tesi (vedi Paragrafo 4.2) CORELIB8DLL_HCMOS8D a 0.18 µm ad una temperatura pari a -40 °C la potenza totale di leakage vale circa 138 pW. Quindi se ad esempio si considera un progetto fatto da 10000 gate, la potenza di leakage sarà circa uguale a 1.4 µW.