4 Scelta delle soluzioni tecniche

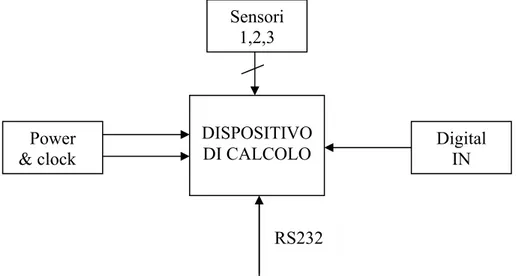

L’architettura del sistema che ci proponiamo di realizzare è la seguente:

RS232 Digital IN Power & clock Sensori 1,2,3 DISPOSITIVO DI CALCOLO

Fig. 4.1: Schema architetturale

Nei paragrafi successivi andremo pertanto a discutere la scelta dei sensori e del dispositivo di calcolo, dobbiamo però anzitutto chiarire in termini tecnici i risultati trovati nei capitoli precedenti.

Nel capitolo precedente abbiamo trovato lo schema di controllo finale, per avere una stima della grandezza che tale codice andrà ad occupare nella memoria di programma del dispositivo di calcolo che andremo a scegliere, basterà lanciare il real-time workshop di Matlab (si veda il capitolo 5 per maggiori dettagli), fare quindi il build dello schema, prendere i file così prodotti e compilarli con un qualsiasi compilatore C (nel nostro caso si è ad esempio usato il Microsoft Visual Studio 6.0), controllando infine la grandezza del file oggetto prodotto dal compilatore.

Andando a fare questo tipo di operazione abbiamo riscontrato una grandezza di codice pari a circa 40 kbyte. Ovviamente tale dimensione dipende dal tipo di compilatore usato, ma è lecito aspettarsi che la grandezza non vari tantissimo da compilatore a compilatore (sicuramente non varierà di un ordine di grandezza), e basterà pertanto aumentare un po’ la dimensione trovata per avere una buona stima della grandezza del codice.

Possiamo anche valutare l’occupazione di spazio della memoria dati, andando a contare il numero di variabili presenti nel codice C generato dal builder, e considerando il tipo di ciascuna: char (1 byte), intero (2 byte ), double (4 byte). A tal proposito anticipiamo che, nella scelta del dispositivo di calcolo, andremo a considerare soltanto i dispositivi lavoranti in virgola fissa, dando solo qualche accenno ai virgola mobile; sfruttando una procedura automatizzata per la scrittura del codice di programma (tecnica discussa di cui parleremo in dettaglio più avanti) infatti, non dovremo preoccuparci delle difficoltà nell’approssimare i numeri in doppia precisione, usati in tutti i nostri esperimenti, in numeri interi, che sarà fatta interamente dai compilatori; potremo pertanto scegliere un dispositivo di costo più basso, rispettando le specifiche che c’eravamo imposti.

Per quanto concerne la velocità d’esecuzione, può essere fatta una stima facendo eseguire al PC, un numero predeterminato di cicli in cui viene lanciata la funzione generata, ed andando a misurare il tempo impiegato. Avremo pertanto che :

C f N T f f rich cicli m proc micro ⋅ ⋅ ⋅ =

Dove indica la frequenza minima necessaria del microcontrollore, indica la frequenza del processore su cui si è fatta la prova in questione, indica la frequenza minima con cui si intende eseguire il codice (nel nostro caso 4 volte la banda del sistema, ovvero 80 Hz) , T indica il tempo misurato, ed è il numero di cicli impostato. Nella formula compare inoltre una costante C, che tiene di conto del fatto che il microprocessore del PC, diversamente dal microcontrollore, effettua conti in virgola mobile (tale costante non è nota a priori ed andrà largamente sovrastimata). micro f fproc rich f cicli N m

Una stima di massima dei requisiti del nostro dispositivo di calcolo può quindi essere questa:

• 50-60 kbyte di memoria ROM • 2-4 kbyte di memoria RAM

nei paragrafi successivi analizzeremo pertanto una serie di dispositivi di calcolo che soddisfino sia tali caratteristiche sia altre che andremo ad introdurre.

4.1 Gli accelerometri

4.1.1 Analisi dei requisitiPer quanto abbiamo visto finora, e per quello che andremo a chiarire ora, gli accelerometri dovranno soddisfare le seguenti specifiche:

Ingombro : risulta abbastanza chiara l’esigenza di avere degli accelerometri poco ingombranti, visto che dovranno essere montati su degli occhiali, dove lo spazio utilizzabile è estremamente ridotto

Multiassialità: un sensore multiasse minimizza il numero dei sensori usati riducendo lo spazio occupato, inoltre vengono minimizzati gli inevitabili errori d’allineamento tra gli assi dovuti al non perfetto montaggio. L’ideale sarebbero degli accelerometri triassiali ma al momento d’inizio di questa tesi, l’unico prodotto di ricerca di questo tipo non è risultato disponibile; ci siamo pertanto accontentati di un dispositivo biassiale.

Alimentazione/potenza: la portabilità del dispositivo ci obbliga ad un’alimentazione a batterie, dovremo pertanto avere un dispositivo che basso consumo di potenza, inoltre non disporremo d’alimentazioni superiori ai 5 V. (TTL/Lpower)

Accuratezza e precisione : il fondoscala del dispositivo deve essere di 2g (dove con g s’intende l’accelerazione gravitazionale terrestre), dato che le accelerazioni massime con cui avremo a che fare saranno al massimo di 1g in modulo, ma sarà sempre presente anche il vettore di gravità ( dunque avremo al massimo 1g+1g ). Sarà inoltre necessario avere almeno 10 bit di risoluzione (2mg).

Banda: per le analisi fatte nel primo capitolo dovremo avere una banda di almeno 50 Hz., ma è bene in fase di sperimentazione avere un certo margine ed avere a disposizione 100 Hz.

Costo : non dovrà essere elevato, visto che faremo uso di tre accelerometri e che il costo totale dell’interfaccia dovrà essere contenuto come discusso nei capitoli precedenti.

4.1.2 Gli ADXL202

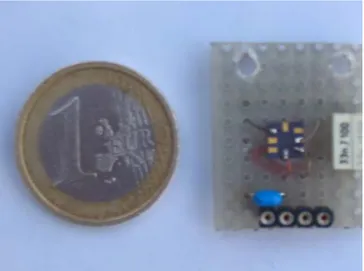

Tale dispositivo, prodotto dalla Analog Devices, risulta essere particolarmente adatto alle nostre esigenze: si tratta di un accelerometro biassiale di tipo MEMS (Micro Electro-Mechanic System), estremamente piccolo, disponibile in un package di 5mm x 5mm x 2mm.

Fig. 4.1.1: Dimensioni ADXL202

Il dispositivo inoltre può essere alimentato da una tensione pari a 5V o anche inferiore, e presenta un consumo piuttosto basso in termini di corrente (inferiore agli 0.6 mA); la banda arriva fino ad un massimo di 5 kHz, e soddisfa ampiamente le nostre necessità.

Il fondoscala è di 2g, proprio come da noi richiesto, e la risoluzione di targa alla frequenza di 60 Hz, è di 2mg (ovvero 0.01962 m/ ). s2

Il dispositivo presenta due tipi d’uscita: una analogica, in cui il valore della tensione letta è direttamente proporzionale al valore dell’accelerazione, ed una digitale modulata in PWM, dove il valore di quest’ultima è invece proporzionale al valore del duty cycle dell’onda rettangolare in uscita.

L’uscita digitale può essere estremamente utile,nel caso in cui non si disponga di un convertitore analogico digitale, in quanto tale uscita può essere direttamente letta dal DSP, o dal microcontrollore, tramite un contatore.

Il costo di ciascun accelerometro, è inferiore ai 10 $, pertanto non troppo elevato (avremo circa 30 $ di costo degli accelerometri) ed adattabile alle nostre specifiche. Lo schema interno a blocchi dell’accelerometro è il seguente

Fig. 4.1.2 : Schema interno dell’ADXL202

I sensori danno un’uscita che, una volta demodulata, arriva in ingresso ad un filtro passa basso di tipo RC, con capacità esterna. Il prelievo del segnale analogico viene pertanto fatto sull’uscita del filtro RC, che a sua volta funge da ingresso per il modulatore DCM, che va a creare l’uscita in PWM; tale modulatore può essere disattivato semplicemente non inserendo la resistenza Rset.

Le misure che abbiamo fatto su tali accelerometri sono: • Misura della caratteristica d’ingresso/uscita • Stima della non linearità

• Misura del fondo di rumore in presenza e assenza del modulatore DCM • Stima della risoluzione

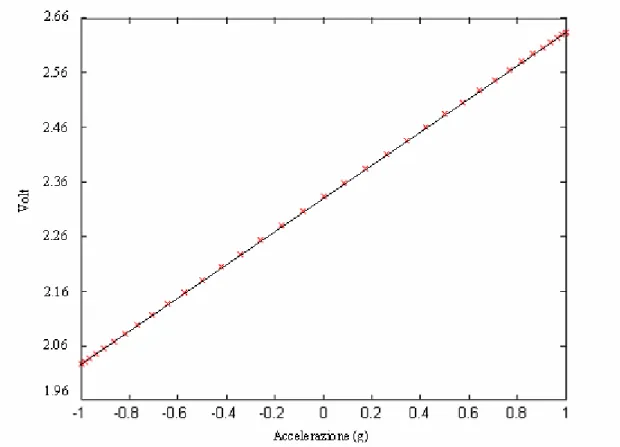

La prima misura è stata eseguita con due esperimenti di tipo differente: una misura di tipo statico, ed una di tipo quasi-statico. Il primo tipo di misura è stato effettuato posizionando la basetta dell’accelerometro su di un goniometro rotante, e misurando l’uscita, con uno step angolare di 5° gradi, alla frequenza di 1 kHz. Per

ogni posizione è stato pertanto effettuata una media sui campioni acquisiti, ed abbiamo calcolato i coefficienti della retta di regressione, ovvero la retta che minimizza lo scarto quadratico medio, ottenendo una caratteristica di questo tipo:

Fig. 4.1.3 : Caratteristica statica accelerometro 1, asse x

Con questo tipo d’esperimento è stato possibile anche ottenere una stima della non linearità del dispositivo, andando a calcolare lo scarto quadratico medio dei campioni, rispetto alla retta di regressione; prendendo la media dei campioni acquisiti su ciascun angolo ( ) e calcolando lo scarto quadratico medio rispetto al valore corrispettivo della retta di regressione ( ) si è trovato per l’accelerometro preso in esame che:

i x r x

(

)

N x x N i i r∑

= − = 1 2 2 σ =4.34⋅10−7 V 2ovvero una deviazione standard di circa 1.6 mg; tale valore ci fa pertanto capire che è ragionevole usare una caratteristica d’ingresso-uscita di tipo lineare, visto che l’errore commesso sarà inferiore agli errori dovuti al non corretto allineamento degli accelerometri, e come vedremo anche all’errore di quantizzazione.

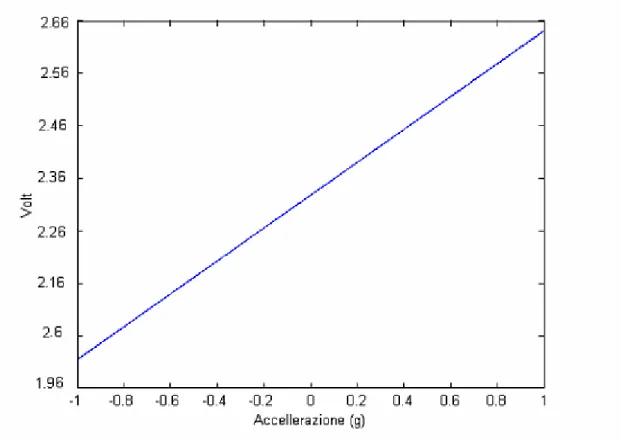

Il secondo tipo d’esperimento è stato eseguito posizionando la basetta dell’accelerometro sul albero di un motore, girando manualmente ed in maniera piuttosto lenta il rotore, e leggendo la posizione angolare grazie all’encoder di cui il motore era dotato. In tal modo è stato possibile ottenere una misura con uno step angolare molto più basso, pari a 0.1 gradi, ed ottenuta su una quantità di campioni più alta. Una volta rilevati i dati si sono poi calcolati i coefficienti della retta di regressione ottenendo una caratteristica di questo tipo:

Fig. 4.1.4: Caratteristica quasi-statica accelerometro 1, asse x

Si veda l’appendice A, per le caratteristiche di tutti gli assi di ciascun accelerometro.

Abbiamo infine stimato le eventuali variazioni del fondo di rumore, causate dall’attivazione o disattivazione del modulatore DCM. Parlando sempre del solito accelerometro e del solito canale, si è notato che in presenza del modulatore il rumore presenta una deviazione standard pari a 31*10 , mentre in assenza di tale, la deviazione standard scende ad un valore pari a 15*10 , ovvero meno della metà del valore precedente. Tale rapporto è stato riscontrato in ciascun asse dei tre accelerometri sotto misura, e pertanto è stato scelto di usare il canale analogico,

3 −

compatibilmente con la scelta del dispositivo di calcolo che andremo ad analizzare nel paragrafo successivo.

I valori delle capacità esterne sono stati scelti in maniera da realizzare un filtro a 100 Hz, che rappresenta un valore di guardia soddisfacente per eliminare i disturbi e diminuire la potenza di rumore, ma al tempo stesso non eliminare nessun tipo di frequenza di segnale (ulteriori filtraggi potranno essere poi fatti via software). La risoluzione reale che si è riscontrato lavorando con tale montaggio è superiore a quella di targa ed è di quasi 3 mg, che su di un fondoscala di 4g ci danno circa 10,5 bit; tale misura è stata fatta ruotando il rotore e leggendo dall’encoder l’angolo minimo che causava una variazione apprezzabile dell’uscita. Tale peggioramento della risoluzione rispetto ai dati di targa è spiegabile considerato che i dati forniti dal costruttore sono da considerarsi sempre nel caso migliore possibile.

4.2 Il microcontrollore e possibili soluzioni sul mercato

Andiamo adesso ad analizzare la scelta del dispositivo di calcolo della nostra interfaccia. Possiamo anzitutto scegliere tra due diverse soluzioni architetturali:

• Dispositivo di calcolo semplice e driver da computer remoto complesso • Dispositivo di calcolo più complesso e driver più semplice

Mentre la prima soluzione comporta un vantaggio in termini di costo, e nei tempi di sviluppo del firmware, la seconda comporta una maggiore flessibilità d’utilizzo; un driver più semplice comporta infatti una possibile indipendenza dal sistema operativo utilizzato, ed un minore carico computazionale da parte del sistema remoto. In questo modo la nostra interfaccia diventa a tutti gli effetti, un dispositivo HCI (Human Computer Interface), in grado di interfacciarsi con un elevato numero d’elaboratori elettronici, da quelli più recenti a quelli piuttosto antiquati; inoltre il driver potrà essere estremamente semplice e pertanto indipendente dalla piattaforma utilizzata dal computer remoto.

Si è scelta pertanto la seconda soluzione, considerando anche il fatto che ad oggigiorno esistono sul mercato un elevato numero di dispositivi di calcolo (microprocessori, DSP, microcontrollori) anche piuttosto complessi,a costi tutto sommato ragionevoli.

Nei prossimi paragrafi faremo una breve carrellata delle possibilità presenti sul mercato, tenendo comunque sempre presenti le specifiche in termini di dimensioni di memoria,velocità e costo, citate alla fine del precedente capitolo.

4.2.1 Microprocessori

Numerosi sono oggigiorno i microprocessori presenti sul mercato, tra le principali case produttrici vanno ricordate la Intel e la Amd produttrici rispettivamente dei famosi Pentium e degli Athlon, entrambi in gran voga su i PC sia moderni che datati.

Le potenze di calcolo raggiunte dai dispositivi odierni sono notevoli, alcuni superano i 3 GHz di frequenza, e senz’altro superiori ai nostri scopi, in compenso tali dispositivi per poter funzionare necessitano di componentistica esterna quali ROM dove scrivere il programma, e RAM dove scrivere i dati. L’interfaccia di tipo proposto, si deve comportare come un dispositivo HCI, e si deve interfacciare con un numero ampio di dispositivi d’elaborazione, ma al tempo stesso risultare semplice per tutto ciò che concerne la sua elettronica in modo da limitare al massimo la componentistica, sia per una minimizzazione dello spazio occupato, sia per limitare il costo del sistema (anche in termini di sviluppo). Inoltre i microprocessori non sono dotati di IO per la gestione delle periferiche come ad esempio gli input analogici, e richiedono di allestire della logica su bus per il completamento delle funzionalità desiderate.

Pertanto tale soluzione non è adatta ai nostri scopi.

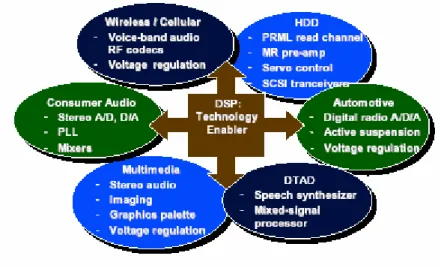

4.2.2 DSP

I DSP (Digital Signal Processing) sono microprocessori progettati ed ottimizzati per l’elaborazione di dati in tempo reale, essi rappresentano una soluzione già più integrata della precedente. Alcuni di essi, presentano inoltre memoria integrata sul chip, ed anch’essi hanno tipicamente una notevole capacità di calcolo.

Ciò nonostante la maggior parte, non ha integrata della logica complessa per l’acquisizione di dati, tuttavia esistono delle famiglie particolari, orientate verso il controllo industriale, ben fornite di periferiche di I/O come convertitori A/D o ingressi PWM. La famiglia TMS320C6000 della Texas Instruments, ad esempio,

presenta una notevole quantità d’ingressi IO, ed una velocità di calcolo anche pari a 1350 MFLOPS (Mega Floating Operations Per Second).

Tipiche applicazioni dei DSP sono: sistemi di controllo avanzati, sistemi legati all’automotive, all’elaborazione digitale di video, immagini statiche, audio.

Fig. 4.2.1: Campi d’applicazione dei DSP

Tali dispositivi vanno comunque ben aldilà delle nostre esigenze, ed hanno un costo che va oltre i target prefissati (si parte tipicamente da un minimo di 10$, per dispositivi di bassa fascia, non adatti alle nostre esigenze, fino ad arrivare a cifre anche di molto superiori ai 200$) sono stati pertanto scartati dalla nostra scelta architetturale.

Il futuro comunque potrebbe presentare delle sorprese, facendo notevolmente scendere il costo di tali dispositivi, grazie allo sviluppo del mobile computing, e dei DSP per telefoni cellulari.

4.2.3 Microcontrollori

Il termine Microcontrollore o MCU (Microcontroller Unit) identifica un particolare circuito integrato che riassume in se le funzionalità di un’unità di calcolo con quelle di un dispositivo in grado di gestire input output sia analogici che digitali.

Giusto per citarne alcuni tra quelli riportati nelle statistiche mondiali aggiornati al 1997, ecco le principali applicazioni di sistemi controllati tramite MCU.

HOME OFFICE AUTOMOBILE

APPLIANCES TELEPHONES TRIP CPU

INTERCOM COMPUTERS ENGINE CONTROL

TELEPHONES SECURITY SYST. AIR BAG SECURUTY SYSTEMS FAX MACHINE ABS

GARAGE OPEN MICROVAWE INSTRUMENTATION

ANSWERING MACHINE COPIER SECURITY SYSTEM DISHWASHER LASER PRINTER TRANSMISSION CONT. HOME COMPUTER COLOR PRINTER ENTERTAINMENT

TV BATTERY CHARGER CLIMATE CONTROL CABLE TV ACCESS CONTROL CELLULAR PHONE DECODER REMOTE CONTROL KEYLESS ENTRY

VCR PAGING CRUISE CONTROL

CAMCORDER NETWORK SYSTEM RADIO

DIGITAL CAMERA CELLULAR PHONES MUSICAL INSTRUM LIGHTING CONTROL PAGING CAMERA PINBALL MACHINE

Fig. 4.2.2 : campi d’applicazioni dei microcontrollori

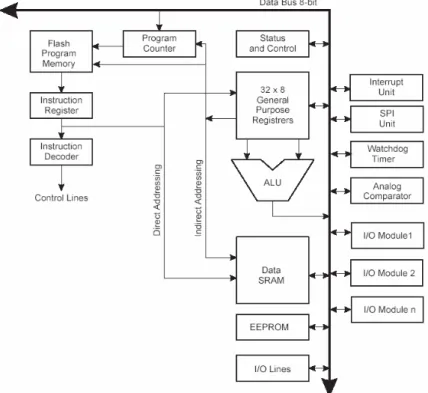

All’interno di un microcontrollore possiamo distinguere almeno quattro blocchi funzionali:

1) Una serie d’interfacce d’input, ad uno o più ingressi designate ad acquisire dati e informazioni dal mondo esterno. A seconda della tipologia di microcontrollore considerato gli ingressi possono essere limitati a segnali digitali semplici (livelli logici), oppure essere più estesi come ingressi seriali (RS232, USB, IEEE802.X, SSP) o ancora come segnali analogici semplici o complessi come, ad esempio, quelli video.

2) Una serie di dispositivi di output, in grado di controllare i dispositivi remoti a cui il microcontrollore viene connesso. Anche in questo caso le uscite possono essere digitali semplici o complesse per consentire al microcontrollore di pilotare diversi generi di dispositivi: motori, display, antenne, monitor.

3) Uno o più blocchi di memoria (generalmente EEPROM o FLASH) nella quale vengono memorizzati i programmi da eseguire, i parametri di funzionamento e le variabili che in corso di lavoro sono di utilizzo per il microcontrollore. L’uso di memorie permanenti consente di preservare il valore di questi dati anche quando il dispositivo è disalimentato

4) Un’unità di calcolo (Central processing unit: CPU, denominata CORE). Ad essa sono assegnati i compiti di sviluppare i conti necessari per leggere gli input e trasformarli in opportuni outputs. Le architetture dei microcontrollori si differenziano ampiamente in base alle potenzialità di quest’unità (larghezza della parola e dell’architettura di bus, numero di istruzioni, velocità di esecuzione, disponibilità di compilatori di diverso tipo e di ambienti di sviluppo)

Oltre a questi blocchi funzionali, indispensabili per poter definire microcontrollore un determinato chip, solitamente vengono anche implementate altre funzioni legate alla complessità del dispositivo; tra le più comuni segnaliamo:

• Timer; • Porte seriali; • Porte IO per BUS; • Convertitori A/D e D/A; • Generatori PWM; • Comparatori; • Driver per display;

• Sistemi di autoscillazione interna; • Altro

Il cuore dell’unità di calcolo di una MCU è costituito da: • Registri

• Unità logico aritmetica • Contatore di programma • Unità di fetch

• Decodificatore d’istruzioni • Memorie

In figura è rappresentata una possibile organizzazione generale di un microcontrollore (sebbene molte poi siano quelle reali) da cui s’intravede come queste componenti siano interconnesse.

Le unità principali comunicano mediante un BUS (4,8,16,32 bit) le cui dimensioni definiscono l’architettura del microcontrollore. Questo bus, essendo l’unità di trasferimento base per tutti i dati, è collegato alla capacità di manipolare le informazioni all’interno del microcontrollore, e quindi alle sue prestazioni.

Quando ci riferiremo a microcontrollori a 8 bit, intenderemo che la capacità di gestione dati del microcontrollore è organizzata su strutture delle stesse dimensioni e quindi anche il BUS interno dovrà possedere le medesime linee.

Fig. 4.2.3: organizzazione di un microcontrollore

Le componenti in figura sono divise in due gruppi: alla destra del BUS tutte le componenti I/O modulari che offrono le funzionalità di controllo, alla sinistra la parte dedicata all’elaborazione delle informazioni.

La divisione non è solo grafica ma anche funzionale nel senso che ogni periferica comunica con la parte di calcolo tramite una porzione di memoria accessibile sul BUS e visibile nello spazio di memoria del processore.

Programmare un dispositivo di IO diventa pertanto accedere in forma, modi e tempi particolari a determinate zone di memoria.

Il funzionamento dei moduli d’elaborazione è invece analogo a quello di un microprocessore, con la differenza che le memorie necessarie al funzionamento sono già incluse nell’architettura base (sebbene memorie aggiuntive possono essere connesse dall’esterno). In questo modo il microcontrollore può divenire un elemento indipendente che funziona quando alimentato e connesso ad un oscillatore che ne genera il clock (talvolta incluso nel chip stesso).

Numerosissime sono le case produttrici presenti sul mercato, tra le più famose ricordiamo: Microchip, Atmel, Motorola, Renesas, Intel, Analog Devices, Texas Instruments, STMicroelettronics, SGS Thomson. Nel nostro studio sullo stato dell’arte, ci siamo soffermati principalmente sulle prime cinque citate, e di seguito riportiamo una breve panoramica sui principali dispositivi da esse prodotti.

• Microchip

La Microchip è particolarmente rinomata per la famiglia PIC, in gran voga tra gli hobbisty, per il bassissimo costo, e la semplicità del set d’istruzioni.

Attualmente lo sviluppo dei prodotti della famiglia Microchip si dirige verso due linee principali di produzione: la famiglia PIC18 e i dsPIC.

I primi ovviamente sono la naturale evoluzione delle famiglie precedenti, con un’estensione delle caratteristiche ed in particolare: una ALU più complessa che consente la manipolazione di variabili a 16 bit, più memoria e registri, la possibilità di avere dei PLL interni per ridurre la frequenza di clock esterna ed il consumo. I secondi invece sono dedicati ad un mercato più esigente, (lo stesso nome ricorda infatti i DSP) e sono prodotti che integrano funzionalità più complesse al loro interno: ad esempio la lettura degli encoder di motori, usati in automazione industriale.

• Intel

La famiglia classica dei prodotti per il microcontrollo della intel, si appoggia su due linee di architetture fondamentali: il gruppo MCS (R) 51/251 ed il gruppo MCS (R) 96/296 [12].

Le due famiglie di differenziano più per “dialetto” di programmazione che per prestazioni. Il primo gruppo infatti, iniziato con il capostipite “8051” è stato un caposaldo delle tecnologie embedded per un lungo periodo. La facilità di

programmazione e la politica di hardware-licensing del sistema hanno fatto sì che decine di produttori diversi si affidassero a questa architettura per produrre i loro controllori (Philips, Atmel, ST solo per citarne alcuni).

Con il tempo (in maniera analoga a quanto è successo per i processori della famiglia x86), questa linea di produzione si è evoluta passando dagli 8 ai sedici bit, arricchendosi di funzionalità in termini di periferiche e migliorando le prestazioni di sistema. Circa 15 anni dopo l’esordio del capostipite (1981-1996), Intel ha cominciato a vendere infatti la versione a 16 bit dello stesso processore (sottofamiglia 251, così come successe per l’80286). Tra i vari vantaggi di questa soluzione la compatibilità pin to pin con i modelli precedenti che consentiva di sostituire i vecchi microcontrollori, negli schemi già collaudati con i nuovi più potenti e generosi. La versione 251 già dai primi prototipi, a detta della Intel risulta essere circa 15 volte più efficiente (in termini di troughput) rispetto alla versione precedente a 8 bit. Inoltre la struttura interna della CPU, dotata di più registri che il solo accumulatore (come per la versione 8051) consente la realizzazione di programmi C molto più rapida ed efficiente.

• Atmel

La famiglia Atmel AT89x è pienamente compatibile con quella intel 80c52 e contiene 2K di EEPROM e 8K di flash.

Nel 1996 la Atmel [11] ha dato in produzione una nuova linea di prodotti MCU con architettura RISC, denominata AVR. Questa architettura più flessibile dello standard 8051 è basata su un core di istruzioni a lunghezza fissa (16 bit) e 32 registri (piuttosto che il solo accumulatore come nell’8051). Inoltre l’architettura RISC più performance consente di effettuare una istruzione ogni ciclo di clock (piuttosto che una ogni dodici). La filosofia di progettazione degli AVR ricalca l’architettura HARWARD in cui e può indirizzare fino 8MB di dati o di istruzioni. La Atmel sostiene che questa linea di prodotti è in grado di operare circa 10 volte più veloce degli 8051.

Dal 1998 la linea standard degli AVR è stata suddivisa in tre linee di produzione: tinyAVR, standardAVR, megaAVR. Ovviamente le tre linee variano per costi/prestazioni e mercato a cui sono riferite. Ad esempio la linea megaAVR ha fino a 256KM di flash su chip il che elimina la necessità di provvedere memoria esterna e fino a 4Kb di EEPROM o SRAM oltre naturalmente a tutte le periferiche

previste nei micro (ADC, RTC, I2C, USART,...), il costo medio si aggira dai 5 ai 20 euro in grosse quantità. Tutti i modelli delle nuove linee sono anche disponibili nella versione L che operano a 3 volt (e quindi salvano consumo di energia), oppure (ma solo per alcuni di questi) nella versione V che opera a circa 1.8 volt.

Al livello TOP della gamma di processori della famiglia Atmel, vi è la famiglia AT91, in realtà questi non sono già più microcontrollori, ma veri e propri microprocessori dotati di una ampia gamma di piedini di IO (come per i DSP, diversi produttori ormai si stanno orientando verso questo tipo di dispositivi in quanto sono richiestissimi da una ampia gamma di prodotti: palmari, telefonia mobile, navigatori satellitari,...).

Questi processori impiegano tutti la tecnologia ARM701. ARM è uno standard di architettura di calcolo organizzato a 32 bit e sviluppato nell’ottica di realizzare dispositivi portabili, basso consumo, scalabilità...

Lo sviluppo di software per questo tipo di sistemi richiede la conoscenza della architettura ARM (utilizzo delle istruzioni del processore insieme alle specifiche relative delle periferiche: organizzazione della memoria, uso delle periferiche). Nella fattispecie, la famiglia AT91, si basa sulla versione 7/9 del processore ARM e quindi lo sviluppo software per questo tipo di processori può essere effettuato con compilatori adeguati per la versione ARM7/9.

• Motorola

Motorola [14] è un pezzo di storia nello standard dei microcontrollori tanto è che molti produttori a tutt’oggi usano i prodotti Motorola come riferimento per i propri prodotti. Nel settore dei microcontrollori a 4 bit Motorola è tuttoggi il leader mondiale. Nel 1993 la Motorola introdusse una nuova linea di microcontrollori 68HC08 ed anno per anno produce innovazioni significanti alle proprie linee di prodotti a 16 e 32 bit.

Tra le famiglie a 16 bit prodotte vi sono la HCS12,68HC12,68HC16,56800

La sua nuova struttura denominata MCORE ha lo scopo di rivaleggiare con il processore di tipo ARM-THUMB di riferimento nella linea di prodotti a 32 bit (ST, ATMEL e altri).

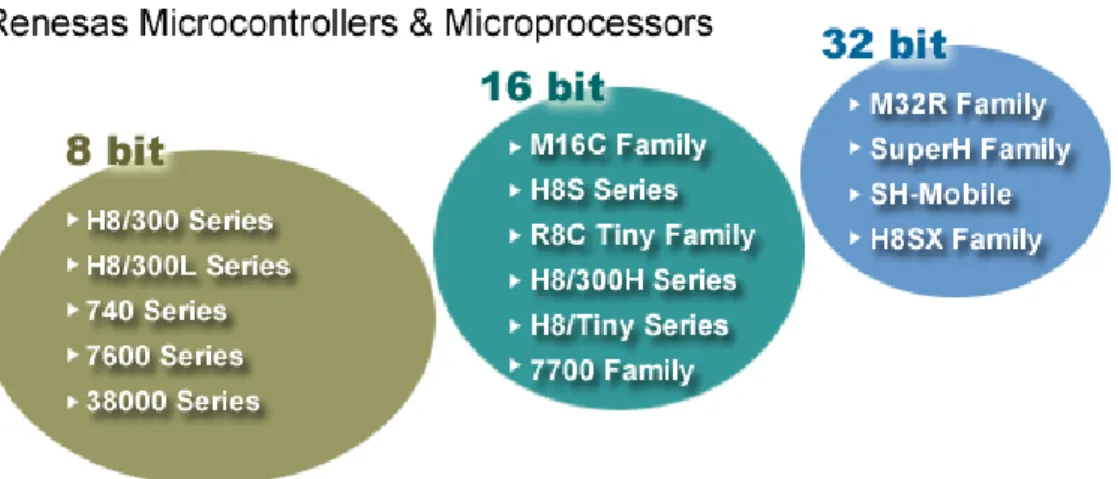

La RENESAS corporation [13] è una azienda fondata il primo aprile 2003 con capitale partecipato dalla Hitachi (55%) e dalla Mitsubishi (45%). Lo scopo dell’azienda è appunto quello di concentrare gli sforzi nella direzione di prodotti LSI quali microcontrollori, logica, sistemi analogici, memorie flash e SRAM.

Attualmente la Renesas proclama di essere il primo produttore al mondo nel campo dei microcontrollori.

La linea dei prodotti nel campo di microcontrollori è illustrata nella seguente figura:

fig. 4.2.4 : Linea di prodotti Renesas

I prodotti più interessanti a 32 bit sono quelli della famiglia H8SX, attualmente disponibile in due tipologie: la classe 1650 (riportata in figura a sinistra) e la classe 1657, che rispetto alla precedente presenta un considerevole sviluppo sia intermini di FLASH interna che di controllo DMA. Entrambi i processori sono dei CISC a 32 bit capaci di circa 48Mflop (per i sistemi quarzati a 48MHz). Prossimi sviluppi del dispositivo includeranno periferiche quali CAN2.0B, USB fino alla versione 2.0, PCI2.1, Fast Ethernet e altri ancora.

Di seguito riportiamo una tabella comparativa tra vari dispositivi esaminati per il nostro scopo, tutti quanti presentano almeno 6 ingressi A/D oppure 6 ingressi PWM, focalizzeremo però l’attenzione sugli ingressi con ADC e con risoluzioni di 10 e 12 bit,per i motivi citati nel paragrafo precedente.

Altra caratteristica comune a tutti, è quella di avere una ROM integrata di tipo flash, in modo da consentire un facile sviluppo della prototipazione del firmware.

A tm eg a6 4 (A V R /Atmel ) AT91FR4042 (AT91/Atmel ) 68 H C 91 2D T 12 8 (68HC12/Motor ) 56F8345 (56800/Motor) MC 9S 12 A 12 8 (HCS12/Motor ) M C 9S 12 A 25 6 (HCS12/Motor ) MMC2114 (Mcore /Motor) MPC534 (MPC500/Motor) SH7042 (Su perH/Renesas ) P IC 18 F 66 21 (Pic18/Microchip) SH71 44 (SuperH/Re nesas) ROM 64 K 512 K 128 K 128 K 128 K 256 K 256 K 512 K 128 K 64 K 256 K RAM 4K 256 K 8K 8K 8K 12K 32K 32K 4K 4K 8K ADC 8 ch. 10 bit No 8 ch. 10 bit 16 ch. 12 bit 8 ch. 10 bit 16 ch. 10 bit 8ch. 10bit 16 ch. 10 bit 8 ch. 10 bit 12 ch. 10 bit 8 ch. 10 bit MIPS 16 63 8 60 25 25 31 61 43 10 65 costo indic ativo 10$ 13$ 16$ 15$ 10$ 23$ 15$ 25$ 15$ 7$ 20$

Il dispositivo da noi scelto è il PIC18F6621, in quanto particolarmente adattato alle nostre esigenze in termini sia di dimensioni di ROM e RAM sia di potenza di calcolo, ed in particolare disponibile ad un costo estremamente contenuto, oltre che in un package di piccole dimensioni (già visto in fig. 2.1.6), nonostante in tale tabella si evidenzino prodotti con un rapporto qualità prezzo superiore (ma ad un prezzo complessivamente superiore).

Il costo dei dispositivi è puramente indicativo: esso è infatti fortemente variabile nel tempo oltre che alle condizioni d’acquisto.

4.3 IL PIC18F6621

4.3.1 ArchitetturaIl PIC 18F6621 è un microcontrollore a 64 piedini della famiglia 18 della Microchip. A differenza di altri modelli questo dispositivo non incorpora un oscillatore interno e necessita pertanto di un sistema esterno di oscillazione da collegarsi ai suoi terminali per la generazione del clock. Ciononostante il dispositivo implementa la quasi totalità dei periferiche di I/O attualmente offerti dai microcontrollori.

Il dispositivo ha le seguenti caratteristiche principali:

• Frequenza di lavoro: 10MHz con moltiplicatore x4 interno a PLL; • Memoria di programma interna: 64Kbyte;

• RAM (esclusi IO bytes): 3840 bytes;

• Memoria dati di tipo EEPROM : 1024 bytes

• Set istruzioni standard della Microchip famiglia 18 compatibile con le famiglie precedenti

La piedinatura del dispositivo è riportata nella figura seguente e dettagliata in tabella.

Fig. 4.3.1 : piedinatura del PIC18F6621

OSC1/CLKIN Ingresso OSC o clock esterno OSC2/CLKOUT Uscita per oscillatore al quarzo MCLR RESET

RAx 7 ingressi/uscite digitali

RGx 5 ingressi/uscite + 1 ingresso opzionale

Anx Ingressi analogici

Vref Voltaggio di riferimento per la conversione analogica RBx....RFx Ciascuna porta ha 8 ingressi/uscite digitali

TOCKl,T1CKl Timer O/1 input eventuale SS Slave Select (modulo SSP)

INTx Linee di eventuale Interrupt esterno PGM Voltaggio per la programmazione PGC Usati dal debugger e dal programmatore PGD Usati dal debugger e dal programmatore T1OSI/T1OSO Ingresso/Uscita timer 1

CCPx Porte di ingresso, cattura e confronto (o PWM) SCK/SCL Ingresso clock seriale per SSP

SDO Linea dati di uscita per SSP TX,RX Linee per la USART

CK/DT Clock sincrono e dati per SSP

PSP Porte parallele slave (per connessione BUS pc) RE 3 Linee controllo per PSP oppure IO digitale

Vss Massa

Vdd Alimentazione

Le connessioni in grassetto sono necessarie, le altre dipendono da come si vuole impiegare il microcontrollore.

Vi sono 3 blocchi di memoria distinti ovvero: • Program memory

• Data RAM • Data EEPROM

La program memory e la data memory usano dei bus separati, in modo da consentire l’accesso simultaneo (architettura di tipo Harward).

L’organizzazione della memoria di programma del dispositivo è significativamente diversa dai suoi predecessori della famiglia 18; in aggiunta alla memoria flash disponibile sul chip, è possibile indirizzare anche della memoria esterna fino ad un totale di 2Mbytes;

La memoria dati del dispositivo è paginata in 16 banchi da 256 bytes ciascuno, secondo il seguente schema

Fig. 4.3.2: organizzazione della memoria dati

Tale suddivisione sarà da tener presente al momento della programmazione (si veda il capitolo cinque).

Il microcontrollore mette a disposizione due meccanismi per il controllo d’esecuzione: a controllo di programma e a controllo di esecuzione.

• Controllo a flusso di programma

All’accensione il microcontrollore eseguirà le istruzioni di codice contenute a partire dal primo indirizzo di memoria (0x0000). Essendo le istruzioni a partire dall’indirizzo 0x0004 dedicate al controllo di interruzione è opportuno che tali istruzioni contengano un operazione di salto al codice di esecuzione.

• Controllo ad interruzione

Un unico indirizzo viene messo a disposizione per la gestione di tutte le interruzioni. Ogni qualvolta una interruzione viene generata, il microcontrollore interrompe l’esecuzione del programma corrente (o delle interruzione corrente), salva il valore del PC nello stack e salta all’indirizzo di gestione (0x0004). Sarà compito della routine di servizio determinare da quale dispositivo l’interruzione è

I prerequisiti fondamentali perché un dispositivo possa interrompere il flusso di programma è che le relative maschere siano state abilitate. Vi sono tre tipi di maschere: abilitazione globale (GIE), abilitazione delle periferiche (PIE) e abilitazione per componente (xxxE).

Il metodo di rilevamento dell’interruzione consiste nel esaminare i FLAG delle interruzioni consultando gli appositi registri. Ogni qual volta una interruzione è abilitata, quando un dispositivo la genera mette a uno il flag del dispositivo. Sarà poi cura del programmatore ripristinare a zero tale flag per confermare il termine della esecuzione.

Fig. 4.3.3: schema interno del PIC18F6621

A parte l’aumento del numero di periferiche per la gestione IO, e qualche blocco per l’aumento delle prestazioni, quale il moltiplicatore hardware 8X8, lo schema rientra in quello generale di fig. 3.5, già discusso in precedenza,nei prossimi paragrafi analizzeremo pertanto solo i blocchi d’interesse principale.

La frequenza d’oscillazione può essere presa direttamente dall’esterno senza modifiche, oppure moltiplicata per quattro tramite un apposito moltiplicatore a PLL.

La scelta viene effettuata configurando in maniera adeguata il registro CONFIG1H: il bit /OBSCEN permette di selezionare il clock principale oppure il secondario, mentre tramite i bit Fosc3:Fosc0 si può selezionare la modalità d’oscillazione, tra cui l’eventuale inserzione del moltiplicatore per quattro.

Altri registri utili per la programmazione, anche per linguaggi di programmazione ad alto livello come il C, sono:

• INTCON: registro di controllo delle interruzioni, i suoi bit hanno i seguenti significati

GIE: Abilitazione globale degli interrupt (1=Abilitati) PEIE: Abilitazione interrupt di periferica

TMR0IE: abilita l’interruzione al traboccamento del Timer0 INT0IE: abilita l’interruzione sul piedino esterno RB0 RBIE: RB port change interrupt bit

TMR0IF: se 1 indica il traboccamento del Timero0 INT0IF: se 1 indica interruzione esterna

RBIF: se 1 indica che uno tra RB7:RB4 è cambiato

• INTCON2,INTCON3: registri secondari delle interruzioni, con cui è possibile selezionare le priorità, scegliere il tipo di fronte (in salita o in discesa) per le interruzioni esterne, selezionare un eventuale pull-up resistivo.

• PIE1,2,3: Registro di abilitazione delle interruzioni per periferica, un 1 al corrispettivo bit abilita l’interruzione, uno zero invece la maschera. Tra le possibilità segnaliamo: PSPIE, ADIE, RCIE, TXIE, CCP1IE, TMR2IE, TMR1IE, EEIE, BCLIE, CCP2IE;

• PIR1,2,3: Registri di identificazione degli interrupt (1 indica che la periferica ha sollevato un interrupt). Tra le possibilità citiamo: PSPIF, ADIF, RCIF, TXIF, SSPIF, CCP1IF, TMR2IF, TMR1IF, EEIF, BCLIF (I2C bus collision), CCP2IF;

4.3.2 Uso del convertitore AD

Il PIC18F6621 ha integrato un convertitore AD a 10 bit. Il modulo di conversione sfrutta un unico convertitore analogico digitale insieme ad un multiplexer analogico a 16 bit che consente il rilevamento (non simultaneo) di 16 input analogici:

Fig. 4.3.4: lo schema d’ingresso al convertitore AD

Il meccanismo di conversione AD è quello che sfrutta le approssimazioni successive e termina quando tutte e dieci le cifre di conversione sono note. Il modulo di conversione consente inoltre di utilizzare come tensioni di riferimento per i valori logici di Vmax e Vmin due tensioni esterne Vref+ e Vref- consentendo in questo modo conversioni su una gamma di tensioni anche più ampia di quella 0-5 V di alimentazione del dispositivo.

Il modulo viene controllato tramite l’accesso a 5 registri: • Byte alto di conversione, ADRESH

• Byte basso di conversione ADRESL • Primo byte di controllo ADCON0 • Secondo byte di controllo ADCON1 • Terzo byte di controllo ADCON2

1) assicurarsi che il piedino sia libero dagli altri utilizzi (ovvero che il TRISTATE della porta digitale sia assicurato come bit di ingresso) 2) Configurare i bit dei registri di configurazione in accordo con le seguenti

caratteristiche ADCS1:ADCS0:

CHS2:CHS0 Bit di selezione del canale da convertire GO-/DONE bit di test per fine conversione

ADON: Abilitazione del convertitore AD

ADFM: Formato del risultato 1==Right shifted, 0==Left shifted PCFG3:PCFG0 Tabella di selezione piedini usati per conversione 3) Eventualmente programmare i bit di interruzione se desiderato 4) Aspettare il necessario tempo di acquisizione

5) Far partire la conversione settando a 1 il bit GO/DONE

6) Aspettare che la conversione sia completa monitorando il bit GO/DONE o aspettando il segnale di interrupt

7) Leggere il registro a 16 bit (ADRESH:ADRESL) contenente il risultato della conversione, e mettere a 0 il bit ADIF in caso di funzionamento ad interrupt

Il tempo di conversione di un bit viene definito nel manuale come Tad, e può essere programmato tramite i bit ADCS[2:0], sono possibili 8 opzioni variabili da un Tosc*2 a Tosc*64, fino all’uso di un oscillatore RC interno. Inoltre, in funzione della frequenza di eccitazione del microcontrollore, bisogna porre attenzione che Tad sia sempre maggiore o uguale a 1.6 µs. La conversione di un dato a 10 bit richiederà un tempo complessivo pari a 11.5 Tad. Per un sistema eccitato con un quarzo a 20MHz, con ADCS1,0=10 Tad=1.6 µs.

Come è mostrato in figura l’ingresso analogico carica un condensatore a campionamento e mantenimento (sample and hold) il quale viene connesso con il convertitore. Al fine di assicurarsi che la conversione sia corretta bisogna consentire al convertitore un tempo di precarica sufficiente a che la carica nel condensatore sia regimata. Tale tempo varia ovviamente in funzione dell’impedenza di ingresso del piedino. Il tempo richiesto per la carica del condensatore sarà quindi pari alla somma di tre valori: il tempo dovuto allo switch di canale, il tempo effettivo di carica del condensatore ed il tempo dovuto al coefficiente di temperatura (necessario solo per temperature maggiori di 25 gradi). Nel microcontrollore non vi sono meccanismi per effettuare questa attesa prima di effettuare la conversione. Per effettuare una conversione deve quindi essere cura del programmatore di inserire una attesa opportuna prima di iniziare il ciclo di conversione.

Nel nostro caso siamo di fronte ad un’impedenza d’ingresso al convertitore piuttosto elevata, pari a 32 kΩ , ovvero l’impedenza d’uscita dell’accelerometro. Il tempo di attesa tra una conversione e l’altra sarà pertanto calcolabile nel seguente modo: ) 2047 / 1 ln( ) ( 0 2 S SS IC HOLD C COFF AMP COFF C AMP ACQ R R R C T T s T T T T T + + − = = = + + = µ

dove , , C sono date nel manuale e valgono rispettivamente al massimo 1K , 7KΩ , e 120 pF. Di conseguenza avremo: IC R RSS HOLD Ω s T s T ACQ C µ µ 40 38 ≅ ≅

Tale tempo è sicuramente troppo alto per effettuare un’attesa attiva, pertanto si è scelto di operare tramite l’impiego di un timer che, al completamento di un ciclo programmabile, generi il segnale di interruzione che faccia partire una primitiva di questo tipo

Variabile Incremento

variabile controllo pari Seleziono il canale contatore

Variabile

Leggo il canale dispari

Fig. 4.3.6: diagramma di lettura degli ADC.

Il tempo di acquisizione potrebbe essere diminuito inserendo un buffer, in modo da minimizzare l’impedenza d’uscita dell’accelerometro e quindi quella in ingresso al convertitore, tale soluzione è stata però scartata visto che con l’inserzione di un buffer su ciascun canale d’ingresso, saremmo andati incontro ad un aumento dello spazio occupato, del costo totale, e sopratutto del consumo dell’interfaccia.

Inoltre le specifiche di segnale (100 Hz) non richiedono tempi di lettura estremamente rapidi. L’avere un tempo d’acquisizione elevato darà infatti, un limite alla frequenza massima del segnale d’ingresso che risulterà pertanto pari a circa 25 kHz, ma come abbiamo già avuto modo di vedere tale frequenza è già di per sé nettamente superiore alle nostre esigenze.

Il tempo tra una lettura e l’altra verrà in realtà ulteriormente incrementato, come è spiegato nel capitolo 5.

4.3.3 Uso del modulo seriale USART

Il microcontrollore 18F6621 mette a disposizione due porte seriali, che possono implementare un Full-duplex, ovvero in grado di trasmettere e ricevere contemporaneamente (con linee ed elettroniche separate). La gestione di queste porte permette di trasmettere o ricevere dati di 8 o 9 bit, in maniera sincrona o asincrona, senza particolari tipi di controlli esterni.

Le porte seriali vengono programmate tramite l’uso dei registri: PIR1, PIE1, BAUDCONx, RCSTAx, TXSTAx, RXREG, TXREG, SPBRGH,SPBRG.

L’uso di PIR1 e PIE1 serve ad abilitare e controllare l’avvenuta interruzione da parte di questo dispositivo, ed il loro impiego è già stato descritto. RXREG e TXREG sono due buffer temporanei di memoria e servono a contenere il valore da trasmettere e ricevere con la seriale. Ogni dato ricevuto viene memorizzato in RXREG, ogni dato da trasmettere deve essere scritto in TXREG (Bisogna notare che questi due buffer sono solo temporanei nel senso che non contengono il valore del dato effettivamente in ricezione e/o trasmissione, ma che essi sono solo di passaggio, ovvero vengono ricopiati in altri due registri di dispositivo nascosti). In entrambi i casi la trasmissione e la ricezione può essere effettuata sia a controllo di programma che con il metodo delle interruzioni. L’utente può monitorare TXIF, RCIF per sapere come sta andando il processo di trasmissione oppure tramite gli interrupt ricevere un’interruzione ogni volta che un dato è stata letto o completamente trasmesso. Il metodo per trasmettere o ricevere dati è il seguente

Trasmetto Ricevo Inizializzo la frequenza di

trasmissione/ricezione con l’uso del registro SPBRGH,SPBRG e del bit BRGH

Inizializzo la frequenza di trasmissione/ricezione con l’uso del registro SPBRGH,SPBRG e del bit BRGH.

Abilito la porta serale (SYNC=0, SPEN=1)

Abilito la porta serale (SYNC=0, SPEN=1)

Eventualmente abilito gli interrupt (TXIE=1)

Eventualmente abilito gli interrupt (RCIE=1)

Se voglio trasmettere 9 bit programmo (TX9=1)

Se voglio ricevere 9 bit setto RX9=1

Abilito la trasmissione (TXEN=1) Abilito la ricezione (CREN=1)

Controllo RCIF per sapere quando è avvenuta una ricezione

Eventualmente programmo il nono bit (TX9D=1/0)

Eventualmente leggo il nono bit (RX9D)

Scrivo TXREG (che avvia la trasmissione)

Leggo RCREG

Eventualmente pulisco gli errori con (CREN=0)

Il contenuto dei FLAG di interruzione è il seguente:

• TXIF: viene messo a uno quando viene abilitato TXEN, va a zero durante la trasmissione (quando si carica TXREGx), e torna a uno appena TXREG si svuota. Nota che utilizzano un registro di supporto nascosto alla trasmissione, la prima trasmissione svuota subito TXREG. Ogni volta che TXREG si svuota TXIF viene rimesso a uno indicano disponibilità per un nuovo dato. Il controllo di TXIF è automatico (non necessita programmazione/azzeramento da parte dell’utente) e funziona che siano attive o meno le interruzioni (per poterlo utilizzare anche a controllo di programma).

• RCIF è analogo per la ricezione a TXIF, è un registro controllato automaticamente dall’hardware e fa riscontro a due registri di ricezione nascosto (uno in cui viene effettivamente ricevuto il byte) più una coda di un bit. Questa soluzione permette di tollerare anche delle piccole latenze nelle ISR.

La velocità di trasmissione si regola programmando opportunamente: SYNC, BRGH e SPBRGH,SPBRG. Essa sarà pari a

Nel nostro caso si è scelto di trasmettere ad una frequenza pari 2400 b/s, ovvero di circa 4 kB/s, più che sufficiente per i nostri scopi, con controllo ad interruzione, ed implementando un protocollo asincrono a 8 bit. Pertanto nel registro SPBRG (di cui si è trascurata la parte alta che non è necessaria) è stato caricato il valore 64.

4.3.4 Uso dell’IO digitale

Il PIC mette a disposizione un numero massimo di 54 porte digitali singolarmente configurabili come porte di ingresso uscita digitali (7 PORTA, 8 PORTB, 8 PORTC, 8 PORTD, 8 PORTE, 8 PORTF, 7 PORTG). Lo schema generale di funzionamento di queste porte digitali è riportato in figura:

Figura 4.3.6 : Organizzazione di una porta di uscita

Ovviamente esistono delle differenze tra una porta ed un’altra in funzione delle periferiche associabili a tali porte e delle caratteristiche specifiche della porta, ma il principio di funzionamento generale è spiegabile tramite il modello di cui sopra, ed in particolare:

• WR port e WR tris sono associati alla scrittura nei bit TRISTATE e DATA della porta associata,

• RD port e RD tris sono associati alle relative letture.

• Una scrittura di un 1 nella porta TRISA mette a uno e zero rispettivamente le uscite delle porte OR e AND disabilitando in questo modo lo stadio di uscita della porta e rendendo possibile l’utilizzo della porta come piedino di ingresso (TRIS==1 ==> port==input)

• Una scrittura di uno zero fa sì che le porte siano “trasparenti” ovvero inoltrino il valore negato del bit scritto nel piedino. Tale opzione rende le porte come porta di uscita (TRIS=1 Î porta = OUTPUT).

• Bisogna ricordarsi che il bit del TRISTATE va pulito non solo quando c’interessa leggere il valore della porta di ingresso ma anche quando è necessario utilizzare il piedino per qualche altra funzionalità prevista dal microcontrollore (USART, SSP,...).

Tutte le porte (A,B,C,D,E,F,G) hanno questa funzionalità minima, tutte si distinguono per ospitare anche qualche altra funzionalità, ma inoltre, anche all’interno della semplice funzionalità di IO digitale vi è una distinzione tra le varie porte ed in particolare:

• La porta A4 ha un trigger di schmidt in ingresso e uno stadio di output di tipo open drain (open collector per MOS).

• Le porte B sono connesse con delle resistenze deboli di pull-up verso Vdd, il bit RBPU ne controlla l’attivazione

• Le porte B,C,D,E,F,G hanno tutte un trigger di schmidt in ingresso che ne limita le oscillazioni e il rumore.

• Le porte D e E hanno logica di uscita più semplice per essere più veloci, ma un fanout minore.

L’utilizzo delle porte è alquanto semplice:

1) Accertarsi che le periferiche condivise con la porta non siano abilitate 2) Configurare i piedini della porta come di ingresso e/o uscita a seconda

delle proprie esigenze

3) Scrivere/ leggere i piedini della porta

Nel nostro caso abbiamo usato come ingressi digitali, le porte B in modo da poter usare i deboli pull-up presenti e collegando direttamente gli interruttori delle pulsantiere alla massa del sistema.

4.3.5 Uso dei timer

I moduli di timer possono essere impiegati per una vasta gamma di funzionalità. Dal semplice conteggio del tempo al controllo sul funzionamento del programma, alle temporizzazioni per IO di tipo particolare al controllo delle tempistiche necessarie per le periferiche. Il 6621 mette a disposizione del programmatore 5 moduli timer per un ampia gamma di funzionalità.

Ci limitiamo all’esame dei Timer0-1, da noi utilizzati, elencandone le caratteristiche principali in tabella

TIMER0 TIMER 1

8 bit o 16 bit 16 bit

Leggibile e scrivibile Leggibile e scrivibile Prescaler a 8 bit Prescaler a 4 bit Interrupt su riporto Interrupt su riporto Sorgente anche esterna Sorgente anche esterna

Possibilità di un oscillatore proprio

Il Timer0 è un contatore a 8 16 bit selezionabile via software tramite il bit T08BIT, del registro T0CON; è accessibile tramite i registro TMR0L e TMR0H (o solamente TMR0L se si sceglie la configurazione a 8 bit) sia in lettura che in scrittura. Ogni lettura dai registri riporta il valore del timer mentre ogni scrittura negli stessi registri ha l’effetto di azzerare il valore del timer. Il funzionamento del Timero0 si controlla tramite alcuni bit del registro T0CON in accordo con le seguenti regole:

T0CS : definisce quale sia la sorgente di questo timer. 0== in clock delle istruzioni,

1== le

transizioni sul pin T0CKl

T0SE :definisce quale sia la transizione di controllo su T0CKl: 0 = LH, 1 = HL PSA: abilita il prescaler (0)

T0PS2:T1PS0 frequenza di divisione del prescaler, utilizzabile per il WDT oppure

per il timer zero, il significato dei valori dipende dall’impiego e viene definito nella seguente tabella: Value Timer 0 WDT 000 1:2 1:1 001 1:4 1:2 010 1:8 1:4 011 1:16 1:8 100 1:32 1:16 101 1:64 1:32 110 1:128 1:64 111 1:256 1:128

Il modulo del TIMER1 si accede tramite due registri (TMR1H:TMR1L) entrambi leggibili e scrivibili. Come per il timer0 una interruzione può essere abilitata ogni volta che il timer genera un overflow. Il timer può essere utilizzato sia come timer che come contatore. In ogni caso il suo funzionamento viene regolato da un registro T1CON in accordo con la seguente tabella:

T1CKPS1,0 : Prescaler bits: 00 = 1:1, 01 = 1:2, 10=1:4, 11=1:8

T1OSCEN : quando 1 informa il modulo di usare un oscillatore al quarzo tra i

piedini T1OSI,

T1OSO, i relativi valore della porta tristate sono ignorati dal sistema

T1SYNC : Quando 0 sincronizza il clock interno con la sorgente esterna. TMR1CS : selezione quale sia la sorgente da usare per il timer 1=Ext, 0=Fosc/4 TMR1ON : 1=Start timer, 0=Stop timer

particolare attenzione va effettuata nella lettura del timer a 16 bit in quanto il byte basso può generare un riporto tra le due letture.

Nella nostra applicazione il Timer0 è stato usato per generare un delay di 50 µ s, necessari per la stabilizzazione del condensatore sample and hold dell’ADC. Il Timer1 è stato invece usato per girare la funzione rt_OneStep creata da Matlab, ad una frequenza nota pari a 100 Hz.

4.4 Considerazioni sull’architettura di controllo digitale

4.4.1 Lo schema circuitale

Fig. 4.4.1: Schema circuitale completo

Come si vede, i tre pulsanti sono stati collegati rispettivamente agli ingressi RB0,RB1 ed RB2 del microcontrollore, che presentano un debole pull-up resistivo, che ci consente di non usare uno schema che a pulsante aperto consumi corrente dall’alimentazione.

I piedini RB6,RB7,/MCLR sono stati resi disponibili in uscita insieme all’alimentazione, per poter essere collegati al programmatore (nel nostro caso un GALEP 4 prodotto dalla Conitec [16]).

Si noti che tale configurazione permette una programmazione ICSP (In Circuit Serial Programming) che consente un aggiornamento del firmware, senza dover effettuare alcuna modifica circuitale: basterà infatti collegare l’uscita al programmatore, e scollegare l’alimentazione, per poter riprogrammare ed aggiornare l’interfaccia.

L’uscita del trasmettitore seriale del microcontrollore, è stata collegata all’ingresso di un max232 che provvede ad adattare i ± 5V dell’uscita TTL, ai 10V d’ingresso della porta seriale del PC.

±

4.4.2 La scelta dei componenti

Come si è già accennato il valore delle capacità degli accelerometri di 33 nF, è stato scelto per implementare un filtro passa basso a 100 Hz, mentre le capacità di valore 0.1 µF è inserita ai capi dell’accelerometro per stabilizzare l’alimentazione .

Un quarzo da 10 MHz, è stato inserito tra i piedini 39 e 40,in modo da poter far lavorare il PIC al massimo della sua velocità (40 MHz), che viene raggiunta utilizzando il moltiplicatore X4 interno al microcontrollore; inoltre il manuale del 18F6621 [1] consiglia l’inserzione di due capacità (C1 e C2) di valore 33pF, per stabilizzare la frequenza d’oscillazione seguendo il seguente schema:

Fig. 4.4.2: generazione della frequenza d’oscillazione

Il manuale del max232 [4] consiglia infine per il corretto funzionamento del dispositivo l’inserimento di cinque condensatori esterni dal valore di 1µF.

4.4.3 Possibili sviluppi futuri

Un possibile sviluppo hardware di grande utilità consiste nel implementare una trasmissione wireless. L’ideale sarebbe costruire un trasmettitore di piccole dimensioni, implementabile quindi direttamente sugli occhiali, di basso consumo, e con una portata di almeno 5m.

Nel nostro progetto si è considerata la possibilità d’inserimento di un trasmettitore a led infrarossi, in quanto implementabile a basso costo e facilmente integrabile sugli occhiali. Tale tipo di trasmettitore necessita di poca elettronica aggiuntiva: sono

necessari solamente un encoder/decoder, quale l’MCP2120 [2] prodotto dalla microchip, ed uno o più led IR, pilotati da tale encoder.

Fig 4.4.3: inserzione di un MPC2120

Tale soluzione seppur implementabile con pochi dollari, presenta il notevole svantaggio di avere un consumo di corrente molto elevato, variabile ovviamente dal tipo di led utilizzato,e dalla portata che si vuole ottenere. Tanto per fare un esempio seguendo gli standard IrDA [15], per raggiungere una portata di 2m si dovrebbero consumare più di 40 mA medi di corrente, che limiterebbero in maniera notevole la durata del nostro dispositivo. Le batterie utilizzate sono infatti di tipo standard con una carica di 700 mA*h, e far salire il consumo totale dell’oggetto sopra i 100 mA, comporterebbe una autonomia di pochissime ore.

Pertanto tale soluzione non è stata realizzata, ma ciò non toglie che con uno studio più approfondito non si possa implementare tale soluzione, o anche altre più complesse quali la trasmissione di tipo Bluetooth.

Altro possibile sviluppo consiste nell’inserzione di giroscopi MEMS, ed è già stata discussa nel paragrafo 3.1.2 .

4.5 Il sistema di comunicazione

4.5.1 Descrizione dell’utilizzo da computer remoto

Il protocollo di comunicazione da noi implementato è strutturato in pacchetti: ciascun pacchetto è composto da :

• 2 byte di avvio protocollo pari a -1 • Posizione X (2 byte)

• Posizione Y (2 byte)

• 1 byte di fine protocollo pari a –2 • 1 byte di fine protocollo pari a 0

L’uso di 3 byte di controllo nel protocollo, ci aiuta a ridurre le possibilità di disallineamento di pacchetto. Inoltre i byte di start (0xFF 0xFF) e quello di end hanno tutti i bit differenti, facilitando in questo modo il riallineamento in ricezione. Il computer remoto dovrà pertanto leggere la porta seriale alla frequenza di 38400 b/s, e verificare che il pacchetto venga correttamente inviato, a quel punto inviare la posizione al software di visualizzazione o in caso di errore nella lettura di protocollo, non aggiornare la posizione (o eventualmente in caso di errori ripetuti interrompere il software di visualizzazione).

Start Ricez. Ricez. Ricez. F =-1? F =-2? V V Ricez. Ricez. F =-1? F =0? V V Ricez. Stop

Fig 4.5.1: diagramma di flusso del driver di ricezione

A parte qualche piccola variazione nella modalità di lettura dalla porta seriale, tale driver può essere utilizzato su qualsiasi tipo di computer remoto, utilizzante qualsiasi tipo di piattaforma.

Nel nostro caso abbiamo usato un semplice driver scritto in linguaggio C, sotto sistema operativo Windows.