CAPITOLO I

INTRODUZIONE

Oggi le memorie non volatili a gate flottante rappresentano uno dei principali prodotti dell’industria microelettronica e la possibilità di ridurne le dimensioni ha contribuito enormemente allo sviluppo dei sistemi elettronici portatili, come lettori di musica, fotocamere digitali, palmari, ecc. Tali memorie, infatti, sono molto versatili ed adatte sia in applicazioni che richiedono integrabilità, sia per immagazzinare codici o un grande volume di dati. In questo settore le memorie Flash occupano un ruolo di primo piano. La Samsung, una delle aziende di spicco nel settore, ha confermato che la memoria Flash di tipo NAND è stata adottata come tecnologia pilota nella compagnia, prendendo il posto che per anni è stato occupato dalle DRAM. Le NAND, il prodotto di maggior successo delle memorie Flash, che si distingue per la presenza di una cella compatta a singolo transistore, ha raggiunto la dimensione per bit di 5.5 F2 (F rappresenta la dimensione minima litografica). Lo scopo è quello di cercare di continuare a ridurre le dimensioni ed aumentare la capacità della memoria. Guidata dalle industrie di circuiti integrati, la ITRS o Interational Thecnology Road Map, ha previsto che la tecnologia a 32 nm entrerà a partire dal 2013 in produzione industriale. Tuttavia, è ormai chiaro che significative modifiche nella struttura dei MOSFET a FG saranno necessarie per garantire le prestazioni di ritenzione dell’informazione per tecnologie con dimensione caratteristica inferiore a 50 nm. Ciò ha indotto la comunità scientifica ed industriale ad intensificare la ricerca promuovendo l’introduzione di nuovi materiali e strutture per la cella di memoria.

In questo contesto si inserisce il seguente lavoro di tesi, che ha come obiettivo lo studio di una cella di memoria avente al suo interno un nuovo dispositivo, il FinFET, e la sua relativa operazione di programmazione.

1.1 Stato dell’arte

Le attuali memorie Flash presentano come elemento base della cella elementare un dispositivo MOSFET a gate flottante.

In un dispositivo a gate flottante, FG, la carica è immagazzinata all’interno del gate flottante, costituito da uno strato di polisilicio completamente circondato da dielettrico, da cui appunto deriva il nome, situato fra il canale e l’accessibile gate del FET. La zona centrale è costituita dal canale in silicio del MOSFET, da un sottile strato di ossido di silicio dello spessore di circa 10 nm, chiamato tunnel oxide, dal gate flottante, da un triplo strato di dielettrico (Ossido-Nitruro-Ossido o ONO) dello spessore di circa 20 nm, detto interpoly dielectric, ed infine dal gate di controllo.

Fig.1: Sezione schamatica di un dispositivo MOSFET a gate flottante.

L’informazione è immagazzinata sotto forma di carica all’interno del FG; il cui valore è proporzionale alla variazione della tensione di soglia del FET. Il dato “1 logico” corrisponde, da un punto di vista microscopico, all’assenza di cariche (elettroni) nel gate flottante e, da un punto di vista macroscopico, alla presenza di un ‘alta corrente di lettura (decine di μA); viceversa lo “0 logico” è caratterizzato dalla presenza di carica all’interno del gatte flottante e da una corrente di

lettura nulla. La presenza dei due strati isolanti che circondano il gate flottante assicurano che la carica vi rimanga confinata, rispondendo al requisito di non volatilità della memoria.

Come già accennato, le memorie Flash a FG vanno incontro a dei seri vincoli riguardanti la possibilità di continuare a ridurne le dimensioni. La causa è di natura elettrica, legate ai meccanismi fisici che contraddistinguono le operazioni di scrittura e di cancellazione della memoria, più che a problemi riguardanti le fasi di processo dell’attuale tecnologia CMOS. L’elemento critico è costituito dall’ossido di tunnel, che deve assicurare un veloce trasferimento della carica attraverso il gate flottante, preferibilmente in condizioni di campo elettrico non molto intenso, in modo da garantire che le operazioni di scrittura e di cancellazione siano veloci, a bassa tesione e con un minore consumo di potenza. Inoltre è necessario preservarne le proprietà di isolamento allo scopo di garantire l’integrità dell’informazione memorizzata nel tempo per almeno ai dieci anni. I campi molto elevati, che si generano durante le operazioni caratteristiche svolte dalla memoria, sottopongono l’ossido di tunnel ad un forte stress e ne minano le qualità isolanti. Inoltre ci sono altri aspetti di cui bisogna tenere conto, come la riduzione delle tensione applicata all’elettrodo di drain, senza che si interferisca con i meccanismi fisici legati al funzionamento della memoria. Infatti, in una memoria Flash, i meccanismi di trasporto, che contraddistinguono le operazioni di scrittura e di cancellazione, sono caratterizzati da parametri che difficilmente possono essere ridotti, come l’altezza di barriera che si alza all’interfaccia fra ossido di tunnel e silicio, che gli elettroni, accelerati dal campo elettrico, devono superare per essere iniettati nel FG.

1.2 Architettura delle memorie Flash

Fig. 2: Tipi di architetture per le memorie di tipo Flash.

Nello scenario delle memorie Flash sono state individuate diverse soluzioni, ognuna delle quali adatta ad un particolare tipo di applicazione. Una prima classificazione prevede che esse vengano distinte in base al tipo di architettura interna della memoria, ossia secondo il modo in cui l’array è organizzato. L’architettura della memoria dipende da una serie di fattori, fra cui:

• il modo in cui le celle sono disposte;

• le tensioni applicate durante le fasi di lettura, programmazione e cancellazione; • i collegamenti fra le celle.

Una seconda classificazione riguarda i campi di applicazione: • archiviazione di codici;

• memorizzazione di un grande volume di dati.

Ogni tipo di utilizzo prevede un’architettura particolare, che consenta di rispondere ai requisiti necessari per quella applicazione. A livello industriale standard, si sono imposte le seguenti architetture:

• NOR, che consente di memorizzare sia codici che dati;

• NAND, ottimizzata per la memorizzazione di grandi volumi di dati.

1.2.1 Architettura NOR

In questo tipo di architettura le celle sono connesse in parallelo fra la source line e la bit line. L’array è costituito da celle che sono selezionate attraverso le word line e le bit line.

Nell’architettura di tipo NOR le word line collegano fra loro i gate dei dispositivi presenti nelle celle elementari, mentre le bit line connettono fra loro i drain dei singoli transistori. In questo tipo di organizzazione l’elettrodo di source è comune a tutte le celle. Essa è anche nota come architettura common ground. La peculiarità risiede nel fatto che ogni due celle è presente un contatto di bit line ed una diffusione di source line. La diffusione di source è posta a massa attraverso un contatto metallico condiviso da tutte le bit line.

Fig.3: Circuito equivalente di un array NOR.

L’operazione di lettura è la più frequente ed anche la più semplice.Una volta fornito l’indirizzo della cella da leggere, il decoder di riga attiva la word line selezionata alzandone la tensione ai suoi

capi, mentre la tensione delle altre word line è mantenuta a massa. La bit line selezionata è collegata ad un sense amplifier. Se la cella selezionata contiene il dato logico “0”, essa presenta una tensione di soglia alta e non scorre corrente attraverso la cella e la bit line. Nel caso in cui essa contenga il dato logico “1”, allora il transistore è acceso e scorre una corrente che arriva al sense amplifier. L’uscita è abilitata ed il dato è portato all’esterno attraverso il bus dei dati, in questo modo l’operazione di lettura termina.

Fig.4: Operazioni di lettura del MOSFET a floating gate.

L’operazione di scrittura è più complessa; essa comprende la programmazione della cella e la cancellazione del suo contenuto.

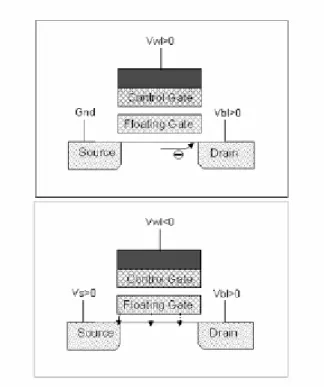

Durante la fase di programmazione, si alza la tensione ai capi della word line selezionata. Nel caso il dato in ingresso sia lo “0” logico, si alza la tensione ai capi della bit line scelta in modo da innescare l’iniezione di elettroni caldi (CHE) e consentire l’innalzamento della tensione di soglia del transistore. A questo punto è necessario verificare che l’operazione sia stata eseguita correttamente andando a controllare che la tensione di soglia sia maggiore di un valore minimo VTem. La cella va dunque letta, ma applicando una tensione di gate più alta rispetto a quella utilizzata nella tipica lettura, e il dato letto va confrontato con quello che si desiderava programmare. Nel caso i due valori coincidano, durante una normale fase di lettura, si ottiene, in

uscita, lo stesso dato scritto. Viceversa, bisogna procedere con una nuova fase di programmazione applicando di nuovo una tensione sia al gate che al drain.

La fase di cancellazione sotto certi aspetti è più complessa. Essa coinvolge un intero settore della memoria; inoltre durante la fase di verifica è necessario che tutte le celle appartenenti a tale zona vengano lette in sequenza. Bisogna poi controllare se siano presenti nelle celle transistori con una tensione di soglia troppo bassa, ed in tal caso portarla ad un valore maggiore. La cancellazione avviene applicando fra source e gate di tutte le celle appartenenti al settore un intenso campo elettrico. In questo modo la corrente tunnel Fowler-Nordheim scarica il floating gate di tutte le celle. Per generare un campo elettrico molto alto si può procedere in due modi: applicando una tensione molto alta al source di tutte le celle da cancellare (tipicamente intorno ai 12V), e lasciando i loro gate a massa; o applicando al source una tensione fra i 5V ai 7V, ed al gate una tensione compresa fra -8V ed i -10V ( procedura che prende il nome di negative gate erase). Anche in questo caso è necessario verificare la correttezza della procedura andando a leggere l’intero settore, ma applicando al gate una tensione più bassa di quelle stabilita durante una tipica fase di lettura. Se il dato letto è l’ “1” logico, allora la tensione di soglia dei transistori presenti nelle celle elementari si è abbassata e, dal momento che la lettura ha dato un risultato corretto anche con una tensione più bassa del consueto, allora durante la normale lettura il valore corretto sarà portato in uscita. Nel caso la verifica non andasse a buon fine anche solo per una cella, bisogna procedere ad una nuova cancellazione finché tutte le celle non sono portate al valore adeguato della tensione di soglia. Dopo la fase di verifica, è necessario procedere ad un ulteriore fase, detta depletion verify, che consiste nel controllare se siano presenti celle del settore che abbiano una tensione di soglia minore di un valore minimo VTem; in tal caso la loro tensione di soglia dovrà essere portata nel range di valori consentiti ( si parla della cosiddetta soft programming) . Con la prima operazione si cerca di individuare la presenza di celle con una tensione di soglia troppo bassa, che potrebbero condurre anche con tensione di gate nulla. Con la seconda fase, le celle individuate sono programmate con una tensione sul gate e sul drain, più bassa rispetto a quelle che caratterizza una normale fase di

scrittura, in modo da alzare solo leggermente la tensione di soglia. La tensione di soglia finale sarà compresa fra VTem<VT<VTeM.

Fig.5: Operazioni di scrittura del MOSFET a floating gate. La figura superiore rappresenta la fase di programmazione, mentre quella inferiore indica la fase di cancellazione.

Operazione BL WL SL COMMON

Lettura 1V Vcc GND

Programmazione 6V 10V GND

Cancellazione Float -10V Vcc Block

Tabella 1: Tensioni di lavoro applicate all’array di un’architettura standard NOR.

La dimensione della cella elementare, per un processo con dimensione minima litografica F, è pari a 10F2 .

1.2.2 Architettura NAND

Essa è utilizzata nella memorizzazione di grandi volumi di dati, ma il suo punto di forza riguarda la possibilità di scaling.

Nell’array sono presenti sedici celle elementari disposte in serie e due transistori di selezione, quello che impone la massa o grounded select transistor ( GSL) e quello che collega le bit line o bit line select transistor (SSL).

Le sedici celle sono connesse ad un’unica bit line a cui sono collegati i transistori di selezione.

Fig.6: Circuito equivalente di un array NAND.

La lettura della cella si svolge basandosi sul concetto del Read Throught, nel senso che le quindici celle vicine a quella indirizzata per la lettura si comportano come dei pass gate. Quindi ogni cella può svolgere due funzioni: memorizzare i dati e, allo stesso tempo, agire da pass gate quando si legge una cella adiacente. Nella fase di lettura la word line della cella selezionata si trova a massa, mentre le celle che agiscono da pass gate presentano una tensione più alta pari a 4.5 Volt.

I due stati logici si distinguono a seconda della tensione di soglia, VT: allo “0” logico corrisponde un VT maggiore di 0V ( cella programmata), mentre per lo stato logico “1” la VT è negativa (cella cancellata) .La tensione in fase di programmazione deve essere più bassa rispetto ai pass gate per

rendere possibile la lettura della cella vicina. Infine, tramite un sense amplifier collegato alla bit line, è possibile distinguere quale stato è memorizzato nella cella. La lettura è più lenta, perchè la corrente deve attraversare le diverse celle ed i transistori di selezione, con tempi tipici attorno ai 10μs. Questo rende l’architettura NAND adatta alla memorizzazione di grandi volumi di dati.

Per programmare una cella è necessario alzare la tensione del gate del transistore in essa contenuto (valori tipici sono fra i 15V ed i 20V) e lasciando a massa la relativa bit line. Le tensione delle word line non selezionate sono intorno ai 10V.

La cancellazione della memoria richiede la polarizzazione del substrato di tipo n e dei pozzetti di tipo p con tensioni molto elevate, tipicamente intorno ai 20V.

Operazione Sel. WL Pass WL SSL GSL “0” BL “1” BL Bulk

Lettura GND 4.5V 4.5V 4.5V 1.8V 0.7V GND

Programmazione 15.5-20V 10V Vcc GND GND Vcc GND

Cancellazione GND GND Float Float Float Float 21V

Tabella 2: Tensioni di lavoro applicate all’array di un’architettura standard NAND.

Entrambi le fasi sono affidate al fenomeno del tunnel Fowler-Nordheim. I vantaggi che presenta questo modo di operare sono i seguenti :

• non è utilizzata l’iniezione di elettroni caldi nella fase di programmazione, perché le tensioni applicate al drain sono molto basse;

• gli elettroni che passano per effetto tunnel provengono dal canale consentendo di utilizzare drogaggi più bassi per le giunzioni di source e di drain;

• poiché sia la fase di programmazione sia la fase di cancellazione avvengono tramite lo stesso fenomeno fisico, l’effetto tunnel, sono richieste basse correnti e alte tensioni, che vengono generate tramite circuiti di pompaggio di carica.

Il meccanismo Read Through alla base dell’architettura NAND rende queste memorie non adatte per le applicazioni che richiedono alta velocità.

A contraddistinguere questo tipo di architettura rispetto alla common ground e' la possibilità di rendere più piccole le dimensioni della cella elementare, complicando però l’operazione di lettura. Le fasi di processo sono più semplici rispetto a quelle che contraddistinguono l’architettura NOR. La dimensione minima della cella è pari a 6F2, che è ridotta rispetto ad un tipico processo NOR.

1.3 Meccanismi di trasporto che intervengono nella programmazaione di una

memoria Flash

Il principio di funzionamento di una memoria Flash si basa sull’intrappolamento di elettroni in una buca di potenziale, in modo tale da non consentirne la fuga per agitazione termica. La memoria svolge tre operazioni: la lettura, la programmazione ed infine la cancellazione. La fase di programmazione prevede il caricamento di elettroni nel gate flottante, mentre la fase di cancellazione la loro rimozione.

I due principali tipi di architettura NOR e NAND si distinguono anche per il tipo di meccanismo che interviene nelle fasi di programmazione e di cancellazione.

L’architettura NOR prevede:

• l’iniezione di elettroni caldi ( Channel Hot Electron, CHE) per la fase di programmazione; • il passaggio di elettroni per effetto tunnel Fowler-Nordheim per la fase di cancellazione .

Fig. 7: Rappresentazione schematica delle fasi di programmazione e di cancellazione di una cella di memoria Flash NOR.

L’architettura di tipo NAND, invece, presenta la stesso meccanismo di trasporto sia per la fase di programmazione che di cancellazione, ossia il tunnel Fowler-Nordheim.

1.3.1 Iniezione di elettroni caldi (CHE)

Applicando agli elettrodi di source, drain e gate una tensione adeguata, tale da rendere conduttivo il canale fra source e drain, gli elettroni presenti al suo interno, accelerati dal campo elettrico longitudinale all’interfaccia, acquistano un’energia cinetica tale da consentire loro di superare la barriera di potenziale, che sia alza all’interfaccia fra silicio ed ossido di silicio, e raggiungere il gate flottante. Tensioni tipiche applicate agli elettrodi durante tale fase sono le seguenti: 12 V sul gate, sul drain 5 V, mentre sia il substrato che il source sono lasciati a massa. A lungo andare, i portatori, che presentano un’alta energia cinetica, possono causare danni all’interfaccia fra silicio e ossido di silicio ed alterare le proprietà isolanti di questo ultimo. Ciò riduce le prestazioni della memoria e ne diminuisce l’affidabilità.

L’iniezione di lacune ed elettroni, sebbene con diversa intensità ed in differenti regioni, avviene simultaneamente. L’effetto principale riguarda i parametri che caratterizzano i dispositivi, come la transconduttanza, la corrente di drain, la tensione di soglia, ecc, i cui valori vengono modificati.

Bisogna sottolineare, comunque, che queste quantità risentono degli effetti dovute alle cariche intrappolate, alla concentrazione di trappole presenti all’interfaccia. Quindi riuscire a distinguere e separare i vari effetti non è semplice.

Tuttavia, fissato il valore di polarizzazione sull’elettrodo di drain e stabilito un certo tempo di sollecitazione, la variazione dei parametri elettrici dipende dalla tensione applicata al gate,VGS. A seconda del valore di VGS possiamo allora distinguere tre casi, partendo da valori bassi della tensione sull’elettrodo di gate fino ad arrivare a valori più alti e confrontabili con quella sull’elettrodo di drain:

• a basse VGS corrisponde uno spostamento della tensione di soglia verso valori negativi e della transconduttanza verso valori positivi (∆VT < 0, ∆gm > 0)

La carica positiva formatasi nel canale, dovuta all’intrappolamento delle lacune, ha come effetto un aumento della concentrazione di elettroni nella sezione del canale dalla parte del drain. In questo modo è come se il drain si estendesse vicino al source, comportando un’effettiva riduzione del canale ed aumentando il valore della transconduttanza verso valori positivi più alti;

• per VGS ≈ VDS/2 ci troviamo nella situazione apposta al caso precedente, cioè abbiamo ∆VT>0 , ∆gm<0 a cui corrisponde il massimo livello di deterioramento;

• per VGS≈VDS prevale l’iniezione di elettroni e gli effetti che si manifestano sui termini VT e gm sono più piccoli che nel secondo caso.

1.3.2 Effetto tunnel

Il campo elettrico, molto alto, creatosi in seguito ad una corretta polarizzazione degli elettrodi di gate e di source, promuove il passaggio di elettroni, attraverso l’ossido, dal floating gate al source. Ecco perché lo strato di ossido, che separa il floating gate dal silicio, è detto di tunnel. In particolare il meccanismo di trasporto è noto come tunnel Fowler-Nordheim. Superata la barriera di potenziale

all’interfaccia fra silicio ed ossido di silicio, di circa 3.15 eV, gli elettroni entrano in banda di conduzione dell’ossido e da qui sono accelerati verso il source. In condizioni tipiche, la differenza di potenziale fra gate e source è di 10 V.

La tensione positiva applicata al gate permette di modulare l’altezza di barriera dell’ossido.

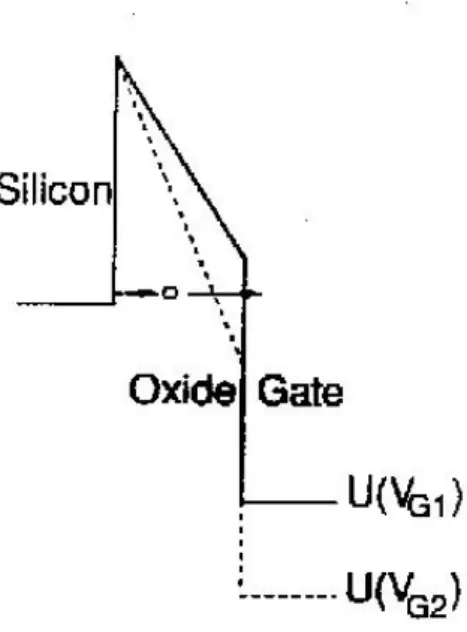

Fig. 8: Rappresentazione schematica delle condizioni di tunnel diretto e di Fowler Nordheim.

Alzando la polarizzazione sul gate da VG1 a VG2 , aumenta il campo elettrico nell’ossido e l’altezza

di barriera tto tunnel

ttraverso una barriera trapezoidale è nota come corrente per tunnel diretto o Direct Tunneling

ensione VG da trapezoidale si evolve in triangolare. La corrente che si genera per effe

a

current, perché gli elettroni vengono iniettati direttamente nell’elettrodo di gate. Mentre la corrente che fluisce attraverso una barriera triangolare è detta corrente tunnel Fowler Nordheim.

Nel caso in cui sia presente un ossido sottile, nella corrente di tunnel, che è funzione della tensione di polarizzazione applicata agli elettrodi, un contributo dominante è dato dal coefficiente di trasmissione, che a sua volta dipende dal campo elettrico dell’ossido. Agendo sulla t

all’elettrodo di gate si può controllare tale effetto. Il meccanismo di trasporto è il tunnel diretto ed il coefficiente di trasmissione, anche in presenza di campi elettrici bassi, aumenta, così come l’effetto delle correnti di perdita. Per poter garantire un tempo di ritenzione adeguato, il coefficiente di

trasmissione deve essere piccolo in presenza di campi elettrici non intensi e ciò rappresenta un vincolo alla riduzione dello spessore dell’ossido di tunnel, che non può andare al di sotto dei 7-8 nm. Correnti di tunnel che consentono una veloce cancellazione della memoria presentano un coefficiente di trasmissione pari a 10-10 a cui corrisponde un campo elettrico pari a 10 MV/cm, tipico valore usato nelle applicazioni.

Le densità di corrente tunnel di gate, in presenza di spessori sottili dell’ossido tunnel, assume la seguente espressione, a seconda dell’intensità del campo elettrico applicato si cade nel regime di tunnel Fowler Nordheim o in tunnel diretto[1]:

⎥ ⎦ ⎤ ⎣ ⎡ − = ox E B 2 ⎢ ox FN AE J exp ; S φ π q h 2 3 16 ; = A

(

2m)

1/2 32 3 4 S ox φ q = B h ;(

)

⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ − − − ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − 3/2 3/2 3/2 2 1/2 exp 1 S ox s S OX S ox S 2 ox DT φ qV φ φ F B φ qV + φ AF = J ;dove Fox è il campo elettrico nell’ossido di silicio;

ΦS è l’altezza della barriera di energia potenziale all’interfaccia silicio-ossido di silicio, misurata

rispetto al livello di Fermi nel silicio;

silicio; mox è la massa effettiva dell’elettrone nell’ossido di

Fig. 9: Rappresentazione del diagramma a bande di energia di una struttura in polisilicio n+/SiO

2/Si nel caso

rispettivamente di tunnel Fowler-Nordheim e di tunnel diretto di elettroni.

La presenza di un campo elettrico molto elevato nello strato d’ossido, indispensabile per innescare il fenomeno del tunnel di portatori attraverso la barriera di energia potenziale, rischia, in seguito a numerosi cicli di programmazione e di cancellazione, di alterare le proprietà isolanti dello strato di ossido. Inoltre si può creare localmente un percorso conduttivo tramite cui la carica accumulata si scarica repentinamente attraverso una forte corrente.

La prima fase è nota come wear out , mentre la seconda come breakdown.

Il primo tipo di stress si manifesta nella generazione di una corrente di perdita che limita fortemente la funzionalità della memoria stessa, perché altera la ritenzione della carica nel floating gate.

Se lo spessore dell’ossido tunnel viene ridotto al di sotto dei 10 nm, interviene un altro meccanismo di degrado. Esso è dovuto alla formazione di difetti elettronici, responsabili di correnti di perdita, noto anche come SILC ( Stress Induced Leakage Current), e rappresenta il principale fattore limitante il processo di scaling delle dimensioni dei transistori. Esso comporta una significativa deviazione della caratteristica di uscita I-V, compromettendo la ritenzione della carica nel gate flottante e ,quindi, l’affidabilità della memoria. La velocità di generazione dei difetti SILC dipende molto pesantemente dalla tensione applicata all’elettrodo di gate. Se l’ossido di tunnel raggiunge

spessori molto sottili, consentendo un’adeguata riduzione delle tensioni di lavoro e dei campi elettrici, è possibile limitare, a parità di corrente tunnel, l’entità di tale stress sullo strato di dielettrico.

Il secondo tipo di stress conduce alla rottura, per effetto Zener, della giunzione pn source-substrato, che è sottoposta ad un intenso campo elettrico causato dall’applicazione di alte tensioni, circa 10V, al gate e al source. Questo effetto porta ad un aumento dei consumi di potenza delle memorie e crea problemi di affidabilità dell’ossido tunnel, alterandone irreversibilmente le proprietà isolanti. Rotture improvvise si manifestano in presenza di ossidi molto spessi in cui, a causa di una forte caduta di potenziale sull’elettrodo di gate, sono presenti campi elettrici molto elevati. In presenza di ossidi sottili si manifesta un fenomeno noto soft-breakdown.

Entrambi sono legati alla riduzione dello spessore dello strato di ossido, ciò pone un serio vincolo alla possibilità di ridurre le dimensioni dei dispositivi e dunque della cella elementare.

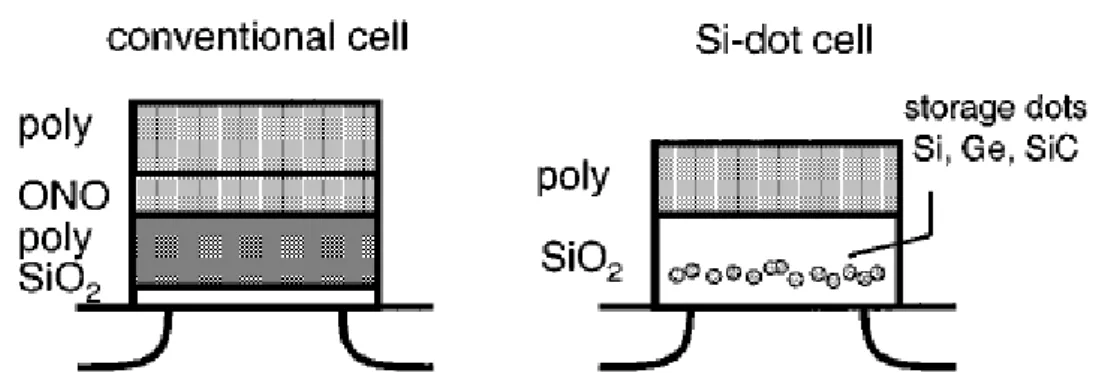

1.4 Memorie Flash a siti di intrappolamento discreto

Questo tipo di tecnologia ha come punto di partenza l’architettura attuale. L’idea di base delle memorie a trappole discrete è quella di fabbricare celle elementari i cui dispositivi abbiano l’ossido di tunnel ultra-sottile e lo strato continuo in polisilicio, che costituisce il gate flottante, sia sostituito da un insieme di nodi discreti, che possono essere presenti in materiali isolanti, come nel nitruro, oppure essere creati artificialmente, come i nanocristalli di silicio. Alla prima categoria appartengono le memorie SONOS, NROM e TANOS, mentre al secondo gruppo appartengono le memorie a nanocristalli di silicio. I vantaggi, che tale struttura offre, sono molteplice, in particolare:

• la presenza di un ossido tunnel molto sottile consente di lavorare con tensioni non molto elevate, sia durante la fase di programmazione che di cancellazione, rispetto a quelle tipiche standard adoperate. Questo consente di ridurre la potenza dissipata e migliorare l’affidabilità del dielettrico rispetto alla degradazione da percorsi SILC.

• la presenza di trappole discrete fa in modo che quando lo strato di ossido tunnel inizia a degradarsi da SILC, l’effetto sulla ritenzione della carica sia più graduale. Infatti inizialmente solo pochi grani, collegati elettricamente con il substrato da percorsi SILC, perdono elettroni. La cella, e dunque la memoria, continua a funzionare. Aumentando il numero di cicli di scrittura-cancellazione, la degradazione dello strato di ossido aumenta ed altri grani perderanno la ritenzione della carica e la cella perderà la propria funzionalità. Questa gradualità non è consentita in una memoria MOSFET a gate flottante, perché la presenza di un cammino SILC scarica il gate flottante della carica in esso contenuta e la memoria perde immediatamente la propria funzionalità.

• partendo dall’attuale tecnologia, i costi di produzione sono contenuti.

Fig. 10: Confronto fra la sezione di un dispositivo in cui è presente lo strato di nitruro e quella di un transistore a FG.

Il primo dispositivo che utilizza il nitruro di silicio per intrappolare la carica è il SONOS. Tuttavia, per diversi anni, tale classe di dispositivi ha ricoperto un ruolo di nicchia, adoperati prettamente in ambito militare e marginalmente per applicazioni commerciali per memoria non volatili di alta densità. Oggi, la struttura SONOS rappresenta un buona base di partenza per le diverse applicazioni delle memorie Flash. In una dispositivo SONOS, acronimo di Silicon Oxide Nitride Oxide Silicon, lo strato di nitruro è interposto fra due strati di ossido di silicio, di cui quello inferiore è più sottile (circa 2.5 nm), mentre quello superiore è più spesso. La fase di programmazione e di cancellazione

della cella di memoria è regolata dal tunnel diretto (DT) di elettroni, che attraversano l’ossido tunnel fino a raggiungere lo strato di nitruro. Le proprietà isolanti del nitruro rendono possibile la riduzione dell’ossido di tunnel, permettendo di lavorare con tensioni più basse, principale vantaggio soprattutto per applicazioni di tipo integrato. Il rinnovato interesse per questo tipo di struttura deriva dai miglioramenti introdotti nella fabbricazione dei dispositivi a semiconduttore. Lo sviluppo di un dispositivo SONOS è simile a quello di un transistore CMOS standard, in cui in luogo del dielettrico di gate è presente uno stack ONO (Oxide Nitide Oxide). Le fasi di processo che portano alla formazione dello stack ONO sono molto importanti perché dalla sua qualità dipende la performance del dispositivo. Le proprietà di ritenere la carica dello strato di nitruro possono essere influenzate cambiando la stechiometria; abbassando il contenuto di silicio dello strato di nitruro il numero di siti in cui la carica viene intrappolata viene ridotto e l’efficienza della memoria cala, anche se si guadagna in termini di affidabilità, viceversa si migliora l'efficienza delle operazioni di programmazione-cancellazione. Nel corso degli esperimenti l’influenza dei rapporti stechiometrici sulle operazioni svolte dalla memoria risulta chiaro, il suo legame riguardo l’affidabilità della memoria e' oggetto di studio. Inoltre, dal momento che la carica è localizzata, è possibile memorizzare due bit di informazione e raddoppiare la densità di integrazione. La struttura NROM risponde a questo requisito; la fase di programmazione è regolata dall’iniezione di elettroni caldi (CHE), mentre l’operazione di cancellazione avviene per iniezione di lacune calde. I due strati di ossido che delimitano il nitruro hanno uno spessore di circa 50 Å, in modo da evitare che si instauri il meccanismo del tunnel diretto. La lettura del dato nella bit line 1 è consentita applicandovi una tensione di 1.5 V, mentre la bit line 2 adiacente è lasciata a massa e la tensione della word line è portata a 3 V. Questo meccanismo prende il nome di “reverse read” perché le tensioni applicate ai terminali di source e di drain nella fase di programmazione e di lettura vengono poi invertiti. Il secondo bit di informazione viene letto e scritto invertendo le tensioni ai terminali durante entrambe le operazioni. La cosa importante è distinguere il bit destro dal sinistro nel momento in cui soltanto un bit è presente. Questo si può fare leggendo il dispositivo in entrambi i modi. Quando la carica è

presente in entrambe le parti, la tensione di soglia è più alta rispetto al caso in cui sia presenta solo una carica. Quindi anche nel caso in cui le cariche si uniscano è possibile distinguere i quattro stati logici (2 bit) corrispondenti alle seguenti situazioni: assenza di carica, carica presente nella parte sinistra, carica presente nella parte destra, carica presente in entrambe le parti. Se solo due stati logici (1 e 0) sono memorizzati nello strato di nitruro è possibile ridurre le dimensioni sotto i 35 nm. I principali svantaggi legati ad una soluziuone di questo tipo riguardano i circuiti periferici che consentano il meccanismo di “reverse reading” e la necessità di alte tensioni all’elettrodo di drain per innescare l’iniezione di elettroni caldi, che limitano la riduzione della lunghezza di canale per evitare il fenomeno del punch-through.

Fig. 11:Sezione di un dispositivo TANOS.

Nelle strutture TANOS la particolarità risiede nella presenza di materiali ad alta costante dielettrica, nel caso Al2O3, in luogo dello stato superiore o inferiore dell’ossido di silicio. Il gate è in TaN che si distingue per avere una funzione lavoro più alta di quella del polisilicio di tipo n+, che diminuisce l’iniezione di elettroni dal gate durante la fase di cancellazione per effetto tunnel FN. Il meccanismo di programmazione è regolato dal tunnel FN di elettroni dal canale, e la carica è memorizzata nello strato di nitruro. La presenza di materiali ad alta costante dielettrica, come ad esempio HfO2, Al2O3, HfAlO, ecc, consente di ridurre il fenomeno parassita del passaggio di elettroni per effetto tunnel dal control gate, permenttendo di aumentare la velocità delle operazioni di programmazione e di

cancellazione, e di poter ridurre le tensioni di lavoro. Tuttavia, l’introduzione di tali materiali comporta una certa complessità nelle fasi di processo convenzionali.

Fig. 12: Confronto fra la sezione di un dispositivo a FG e di un dispositivo a nanocristalli di silicio.

Le memorie a nanocristalli di silicio si distinguono per la presenza di grani di silicio in cui viene memorizzata la carica. Oltre a presentare una notevole robustezza ai difetti da SILC, la struttura consente una buona riduzione delle dimensioni e rappresenta un promettente candidato per applicazioni che richiedono grande capacità di memoria. Il meccanismo fisico che interviene è diverso rispetto a quello di un MOSFET a gate flottante. Esso è legato alle piccole dimensioni dei nanocristalli. Il grano di silicio equivale ad un punto quantico (quantum dot ) collocato vicino a due serbatoi di carica, questo sistema è soggetto ad un regime di trasporto noto come Coulomb blockade. L’informazione contenuta nel dot consiste in una carica pari ad un singolo o pochi elettroni, rendendo piccola la quantità di energia dissipata per bit. Fissati gli stati di carica del dot corrispondenti ad un bit ( lo stato logico “0” corrisponde alla carica –q, mentre lo stato logico “1” a carica nulla), la programmazione o la cancellazione di una cella si otterranno portando la tensione di lavoro a valori distanti fra loro ΔV. Questo sistema risulta adatto a memorizzare più bit di informazione perché il dot presenta molti stati discreti. Tuttavia, il principale svantaggio riguarda la dispersione nell’andamento delle caratteristiche elettriche da un dispositivo all’altro, aspetto che diventa critico in strutture dalle dimensioni molto ridotte.