Capitolo 4

La scheda di interfaccia

4.1 Descrizione della scheda di interfaccia

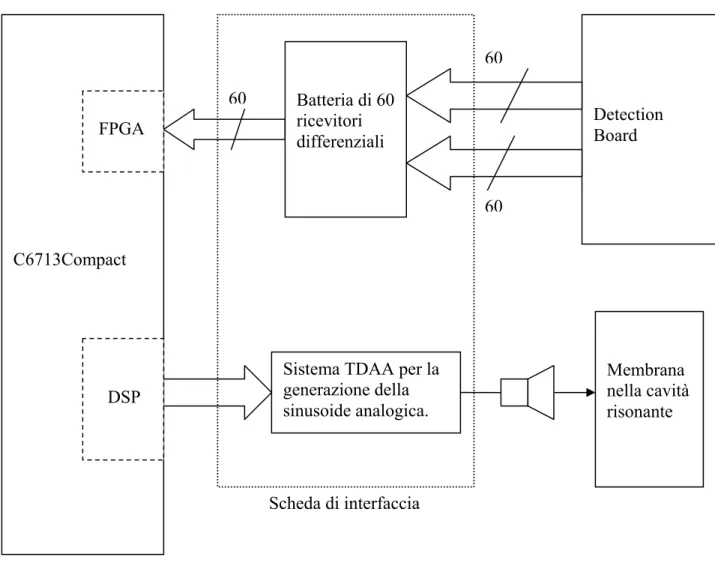

La scheda di interfaccia si colloca, nello schema logico del progetto, tra la C6713Compact da una parte e la Detection Board e la membrana mobile dall’altra.

Figura 4.1: Schema a blocchi che descrive le funzionalità della scheda di interfaccia. 60 Batteria di 60 ricevitori differenziali C6713Compact Detection Board 60 60

Sistema TDAA per la generazione della sinusoide analogica. Membrana nella cavità risonante Scheda di interfaccia FPGA DSP

Essa deve svolgere essenzialmente due funzioni principali:

• Trasformare i 60 segnali differenziali a 5V, provenienti dagli iAQC della Detection Board, che segnalano i rilevamenti fotonici, in segnali unipolari a 3.3V, compatibili con la tecnologia della C6713Compact.

• Generare la sinusoide analogica capace di pilotare lo speaker affacciato alla membrana mobile, partendo da campioni digitali di essa, forniti dal DSP.

4.2 Progettazione della barriera di ricevitori differenziali

Per questa sezione della scheda, la fase progettuale si limita sostanzialmente alla scelta dei dispositivi più adatti allo scopo che si vuole perseguire. Le operazioni che devono essere compiute sui segnali in ingresso sono due: la trasformazione del segnale da differenziale a unipolare e l’abbassamento del livello di tensione massimo da 5V a 3.3V. Si sono quindi cercati dei dispositivi integrati che potessero svolgere entrambe le funzioni contemporaneamente, evitando l’utilizzo di due distinte barriere di dispositivi (la prima costituita da ricevitori RS-422 standard e la seconda dai limitatori di tensione), soluzione che avrebbe portato ad ingombri e consumi maggiori.

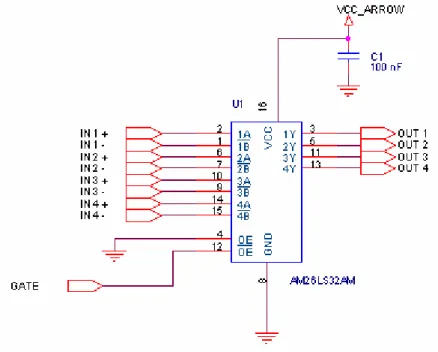

Dispositivi integrati adatti allo scopo si sono rivelati quelli della famiglia 26LV32, come i Texas Instruments AM26LV32: essi sono costituiti da ricevitori differenziali alimentati a 3.3V, e quindi con uscite legate a tale tensione; tuttavia possono sopportare in ingresso tensioni differenziali superiori a 5V. Ogni integrato è costituito da quattro ricevitori differenziali: serviranno quindi 15 dispositivi per formare l’intera barriera di 60 ricevitori.

E’ possibile l’uso di due abilitazioni, una attiva alta ed una attiva bassa, comuni ai quattro ricevitori di ogni integrato, poste in And tra loro.

La massima frequenza di utilizzo garantita è di 32MHz, sufficiente al caso in esame, in cui il massimo data rate dei segnali provenienti dagli iAQC risulta essere circa 20MHz.

Figura 4.2, a e b: Schema logico e package del dispositivo AM26LV32.

L’utilizzo di tali integrati è immediato: agli ingressi si portano direttamente i segnali differenziali forniti dalla Detection Board tramite i due connettori SCSI a 68 pin, mentre le uscite possono essere indirizzate al connettore micro-line della scheda Orsys tramite un innesto adeguato. Delle due abilitazioni se ne userà una sola, eventualmente controllata dallo stesso segnale di Gate indirizzato anche ai dispositivi della Detection Board. L’alimentazione, come già rilevato, avviene a 3.3V; tale tensione può essere stabilizzata tramite un piccolo condensatore (ad esempio 100nF) posto vicino al pin Vcc.

4.3 Progettazione della sezione per la generazione della sinusoide

4.3.1 Il sistema TDAA

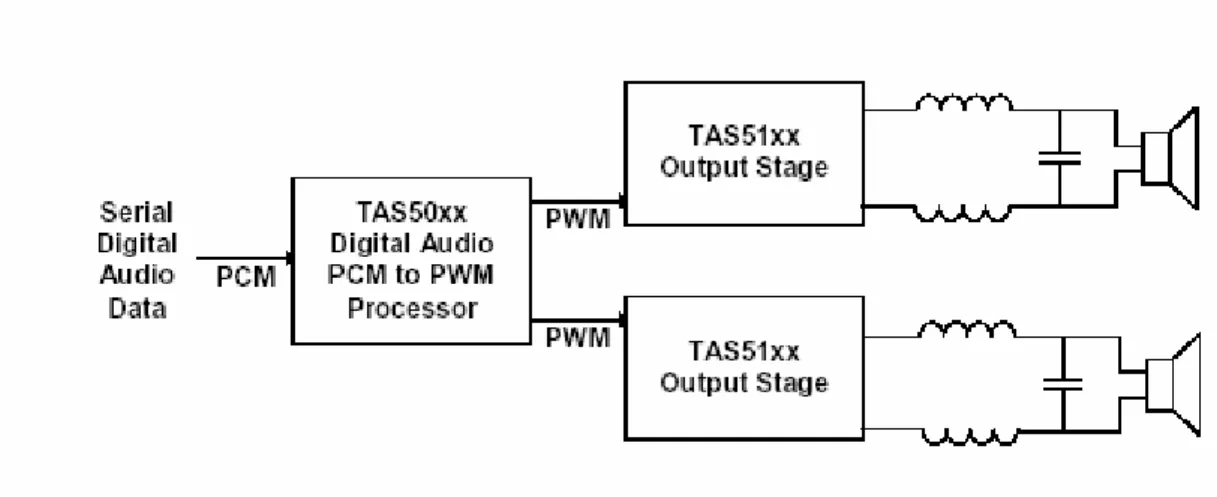

Per la generazione della sinusoide analogica si è scelto di utilizzare un sistema TDAA (True Digital Audio Amplifier), cioè un chip set totalmente digitale dedicato all’amplificazione audio. Esso può consistere semplicemente in un modulatore PCM-PWM, come il TAS50xx della Texas Instruments, e in un certo numero di amplificatori in classe D, adatti al segnale PWM, come i TAS51xx. Il cuore di questa tecnologia brevettata consiste proprio nella conversione del segnale dal formato PCM, Pulse-Code Modulated, a quello PWM, Pulse-Width Modulated: in questo modo il segnale audio può essere mantenuto nel dominio digitale fino al filtro finale, appena prima della connessione agli speaker. Non viene quindi applicata nessuna amplificazione a segnali analogici, e il segnale PWM è mandato direttamente agli speaker, attraverso un solo filtro passa-basso passivo. Questo permette di passare agli speaker il segnale audio in alta fedeltà, senza le inevitabili distorsioni introdotte dagli amplificatori analogici.

Il costo economico di tali dispositivi è alquanto ridotto, poiché a causa della loro versatilità essi sono prodotti in larga scala.

Figura 4.4: Il sistema TDAA proposto da Texas Instruments.

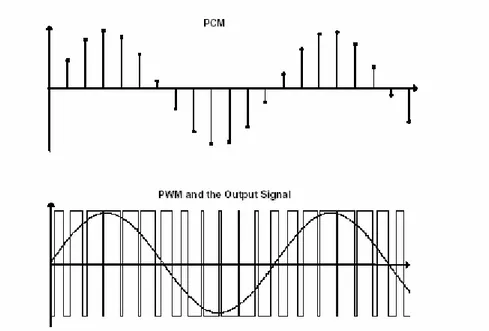

Nella parte superiore della figura 4.5 una forma d’onda sinusoidale è mostrata in termini di segnale PCM; il corrispondente segnale modulato PWM con lo stesso sampling rate è mostrato nella sezione sottostante. Il valore discreto di ogni campione è descritto dalla codifica PWM in termini di larghezza dell’impulso, mentre nel PCM la descrizione avveniva tramite l’altezza dello stesso. In figura 4.6 questo concetto viene ulteriormente chiarificato. La funzione dell’integrato modulatore TAS50xx è proprio quella di effettuare la conversione PCM-PWM del segnale.

Figura 4.5: Esempi di una sinusoide campionata e modulata PCM e PWM.

Figura 4.6: Il segnale PCM è modulato nell’altezza dell’impulso, il PWM nella larghezza. Il segnale audio PCM a 24 bit è mandato al chip modulatore. Internamente c’è un preliminare filtro digitale interpolatore, dove lo stream di dati è sovracampionato di 2, 4 o 8 volte (secondo il sampling rate) fino tipicamente a 352.8 o 384 kHz, che sono i sampling rate interni del sistema TDAA. Il modulatore Equibit trasforma a questo punto il segnale sovracampionato in un PWM avente la stessa frequenza. Questa operazione è non-lineare ed il modulatore TAS50xx utilizza raffinati algoritmi di correzione per migliorare la prestazione globale del sistema.

Figura 4.7: Schema interno del modulatore PWM TAS50xx.

Il segnale PWM, per ogni canale, è quindi mandato agli stadi di uscita di potenza TAS51xx, dove è traslato di livello e portato a due set di transistori di potenza DMOS a canale N connessi in forma “H-bridge”. Infine i segnali d’uscita PWM giungono ai rispettivi speaker, passando attraverso un filtro passa-basso, tipicamente di secondo ordine.

4.3.2 Adattamento del sistema TDAA al caso in esame

La banda che può venire spazzata dalla sinusoide che si deve generare è compresa tra 1.5kHz e 3kHz: essa rientra quindi ampiamente nella banda audio standard, trattata dai normali dispositivi commerciali di amplificazione audio, proprio come i TAS50xx e i TAS51xx

Come si evince dalla descrizione del sistema TDAA, i motivi principali che hanno portato alla scelta di utilizzare proprio tale procedimento d’amplificazione nella generazione della sinusoide sono: la mancanza di distorsioni del segnale dovute ad eventuali amplificazioni analogiche; il basso costo degli integrati necessari. A queste motivazioni si aggiunga poi la possibilità di avere in uscita dal DSP direttamente un segnale modulato PCM, proprio come quello desiderato in ingresso dal TAS50xx.

In particolare il TAS50xx può essere interfacciato direttamente alla periferica McASP0 del DSP, tramite alcuni pin dedicati del connettore micro-line. Il protocollo di comunicazione seriale che può essere utilizzato è il IIS1.

La potenza che deve essere sviluppata per pilotare la membrana non è particolarmente elevata (4W), ed il TAS51xx è progettato in modo da poter fornire in uscita, in un carico di 4Ω, fino a 2 x 15W RMS. Il segnale d’uscita prodotto dai dispositivi TAS51xx è di tipo differenziale. Quindi, se il carico di 4Ω accetta ingressi differenziali, può essere connesso direttamente ai connettori d’uscita. Nel caso invece che lo speaker accetti ingressi di tipo unipolare, si potrà adottare una rete resistiva di adattamento2, che non distorca il segnale in uscita.

Gli integrati utilizzati nei sistemi audio, così come le interfacce audio dei DSP, sono pensati per essere utilizzati in sistemi stereo (se non addirittura multicanale). Nel progetto SPADA, invece, una sola membrana deve essere fatta vibrare attraverso una sinusoide, ed è quindi necessario un solo canale audio, dei due disponibili: l’altro canale rimane inutilizzato. Si potrebbe tuttavia pensare ad implementare in hardware anche la linea di amplificazione e di filtraggio d’uscita del secondo canale audio, per rendere il sistema più versatile per applicazioni future.

Verrà ora discusso più in dettaglio il sistema TDAA usato nella scheda di interfaccia, basato sui dispositivi integrati TAS5001PFB e TAS5101DAP, facilmente reperibili anche sul catalogo RS.

4.3.3 Interfacciamento del TAS5001 al DSP

Come già evidenziato, esistono due periferiche del DSP TMS320C6713, McASP0 e McASP1, destinate alla comunicazione seriale di dati audio.

1 Vedere paragrafo 4.3.3. 2 Vedere paragrafo 4.3.10.

Figura 4.8: Diagramma a blocchi di un’interfaccia McASP.

McASP0, in particolare, ha i pin di ingresso/uscita connessi direttamente al connettore micro-line (a parte un pin di mute in ingresso, non strettamente necessario all’applicazione da implementare). Essa può quindi risultare utile nella trasmissione dei campioni della sinusoide al chip TAS5001.

Affinché ciò sia possibile senza troppi artifizi, sono necessarie tre condizioni: • La possibilità di gestire il clock in modo semplice.

• Un’effettiva corrispondenza pin a pin delle due interfacce. • L’esistenza di un protocollo di comunicazione comune.

Per quel che riguarda la gestione del clock si ha possibilità di scelta, essendo possibile impostare sia DSP sia TAS5001 come master o slave. Si è deciso di far lavorare il DSP come master, ed il TAS5001 come slave, lasciando al DSP il compito di generare il master clock alla frequenza desiderata per la comunicazione audio PCM standard. Questa decisione rientra nell’ottica di rendere

il DSP logicamente master dell’intero sistema. Dovendo esso stesso generare i campioni della sinusoide, appare naturale che il DSP gestisca anche la temporizzazione della loro comunicazione seriale al TAS5001.

La corrispondenza pin a pin dei principali segnali necessari alla comunicazione è verificata, come illustrato nella tabella 4.1.

Pin di comunicazione dell’integrato TAS5001 Pin corrispondente dell’interfaccia McASP0 MCLK_IN AHCLKX MCLK_OUT - SCLK ACLKX LRCLK AFSX SDIN AXR[n] /MUTE AMUTE Tabella 4.1: corrispondenza pin a pin delle interfacce di TAS 5001 e McASP0.

Si è fatta l’assunzione di considerare il TAS5001 come slave: in tal caso il master clock è da esso ricevuto sul pin di ingresso MCLK_IN, mentre il pin MCLK_OUT rimane inutilizzato.

SCLK e LRCLK sono altri due segnali di clock: il primo è sincronizzato con i bit del flusso seriale di dati, il secondo fornisce la scansione dei frame, intesi come gruppi di due campioni, uno destinato al canale sinistro ed uno al canale destro. Il periodo di SCLK è 4MCLK, quello di LRCLK è 256MCLK, cioè 64SCLK, equivalenti a 32 periodi di SCLK per ogni canale.

SDIN è la linea su cui arrivano i dati veri e propri. Si può evidenziare come per ogni interfaccia McASP del DSP siano disponibili n = 8 linee dati bidirezionali AXR[n], pensate per poter gestire sistemi audio anche molto complessi. Nel caso in esame sarà sufficiente l’utilizzo di una sola linea, che potrà essere scelta nel modo più conveniente, in funzione della posizione dei pin AXR[n] sul connettore micro-line e delle condivisioni di tali pin con altre interfacce del DSP.

/MUTE è ovviamente un segnale attivo basso per rendere “silenzioso” il TAS5001. In particolare, con /MUTE logicamente a 0, il segnale PWM in uscita dal TAS5001 diventa un’onda quadra, con duty cycle costante e pari al 50%.

I protocolli di comunicazione che possono essere gestiti dal DSP e dall’integrato TAS5001 sono parecchi. Tra essi ve ne sono alcuni comuni. In particolare è possibile utilizzare il protocollo IIS (I2S) Compatible Serial Format, nelle sue versioni a 16, 20, o 24 bit.

Figura 4.9: IIS Compatible Serial Format. Caratteristiche principali di tale protocollo sono le seguenti:

• Il canale sinistro è ricevuto quando LRCLK è basso. • Il canale destro è ricevuto quando LRCLK è alto. • SDIN è campionato col fronte in salita di SCLK.

• I bit dei campioni del segnale devono essere trasmessi a partire da quello più significativo.

• Nel primo ciclo di SCLK, dopo il cambiamento di stato di LRCLK, non viene trasmesso alcun bit del segnale. La trasmissione dei dati inizia dal ciclo di SCLK successivo. Questo implica che la trasmissione non possa essere a 32 bit, ma solamente a 16, 20 o 24 bit, che sono comunque più che sufficienti, come risoluzione, agli scopi di un sistema TDAA.

4.3.4 Utilizzo del TAS5001

Nel paragrafo precedente, si è visto come i pin del TAS5001 strettamente legati alla comunicazione seriale possano essere connessi, semplicemente, ai corrispondenti pin dell’interfaccia McASP0 del DSP.

L’integrato TAS5001 ha però anche molti altri pin di ingresso/uscita utilizzati, dedicati alle alimentazioni, a particolari impostazioni del modo di utilizzo e all’inserimento di componenti discreti esterni necessari al suo corretto funzionamento.

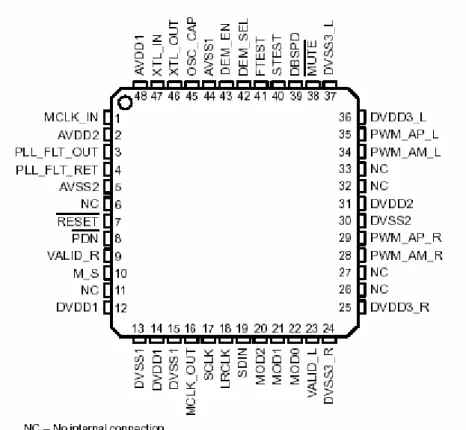

Figura 4.10: TAS5001: terminal assignments.

AVDD1 ed AVDD2 sono ingressi per l’alimentazione delle sezioni analogiche del chip, mentre DVDD1, DVDD2, DVDD3_L e DVDD3_R sono di alimentazione per le sezioni digitali. Tutti questi ingressi possono essere posti alla tensione di 3.3V, eventualmente stabilizzata tramite piccoli condensatori da 100nF.

Analogamente AVSS1, AVSS2, DVSS1, DVSS2, DVSS3_L e DVSS3_R devono essere posti a ground.

I pin FTEST e STEST, utilizzabili in fase di test, nelle normali operazioni devono essere connessi a DVSS3_L.

Il pin di /RESET in ingresso al TAS5001 può essere utilmente controllato tramite la FPGA, attraverso un design dedicato. Quindi esso può venire connesso per questo scopo con un pin adeguato del connettore micro-line.

M_S è il pin tramite il quale si può impostare il dispositivo come master o slave. Ponendo M_S a ground si seleziona il funzionamento in modo slave.

I pin di “mode”, MOD0, MOD1 e MOD2, servono ad impostare il protocollo di funzionamento, secondo la tabella 4.2.

MODE MOD2 MOD1 MOD0 SERIAL INTERFACE SDIN

0 0 0 0 16 bit, MSB first; right justified 1 0 0 1 20 bit, MSB first; right justified 2 0 1 0 24 bit, MSB first; right justified

3 0 1 1 16 bit IIS

4 1 0 0 20 bit IIS

5 1 0 1 24 bit IIS

6 1 1 0 16 bit MSB first; left justified

7 1 1 1 16 bit DSP frame

Tabella 4.2: Selezione Hardware del protocollo seriale di ricezione dati.

Per selezionare il protocollo IIS a 16, 20 o 24 bit è quindi necessario impostare i pin MOD2, MOD1 e MOD0 rispettivamente a 011, 100 o 101. Si può decidere a priori l’utilizzo di uno di questi tre protocolli, tutti adeguati dal punto di vista delle specifiche di risoluzione della sinusoide. In alternativa, per dare maggior flessibilità all’hardware, si possono rendere i pin MOD2, MOD1 e MOD0 disponibili alla modifica dell’operatore, tramite ponticelli.

Esiste un pin di Double-speed mode, DBSPD, utilizzato per impostare il supporto di sampling rate doppi in ingresso, a 88.2 kHz e 96 kHz. Nel caso in esame esso può essere posto a 0.

Per sorgenti audio che siano state oggetto di pre-enfasi a monte della comunicazione seriale, è previsto un filtro di de-enfasi, attivabile tramite il pin DEM_EN e di risposta in frequenza dipendente dal pin DEM_SEL. Nel caso in esame, il filtraggio di de-enfasi non è necessario, quindi tali pin possono essere posti a 0.

I pin PLL_FLT_OUT e PLL_FLT_RET sono terminali ai quali collegare il filtro di componenti discreti, due condensatori ed una resistenza, necessario al corretto funzionamento del PLL interno al TAS50013.

Il pin /PDN, attivo basso, di power down, può nel caso in esame essere posto ad 1 in maniera costante.

Poiché il clock viene fornito attraverso MCLK dal DSP, il pin XTL_IN (Crystal or clock input) viene posto a ground, mentre XTL_OUT e OSC_CAP (Crystal output e Oscillator cap return) vengono lasciati flottanti.

I pin PWM_AP_L, PWM_AM_L, PWM_AP_R e PWM_AM_R costituiscono il segnale d’uscita modulato PWM, per i due canali sinistro e destro, nello standard di tensioni adatto ad essere accettato dai dispositivi di amplificazione TAS5101.

I pin VALID_L e VALID_R, attivi alti, indicano invece l’effettiva validità dei dati PWM in uscita. Essi possono andare direttamente agli ingressi attivi bassi /RESET dei dispositivi TAS5101.

Figura 4.11: utilizzo del TAS5001. E’ stato qui imposto l’utilizzo del protocollo di comunicazione IIS a 24bit (MOD=5).

4.3.5 Utilizzo del TAS5101

Per ogni canale audio che si voglia utilizzare nel sistema TDAA analizzato, è necessario un dispositivo TAS5101, seguito dal corrispondente filtro in uscita.

Anche in questo caso vi sono molti pin da gestire, alcuni a discrezione dell’utente, altri in modo coerente con l’utilizzo riportato nei datasheet dell’oggetto4.

Figura 4.12: TAS5101: terminal assignments.

PWM_AP, PWM_AM, PWM_BP, PWM_BM sono i pin di ingresso per il segnale modulato PWM proveniente dal TAS5001. Da tale dispositivo, a monte, arriva anche il segnale di /RESET.

Il pin /RESET, assieme a /ERR0, /ERR1, HiZ e /SHUTDOWN, appartiene alla logica di control/sense a 3.3V.

I pin d’uscita /ERR1 ed /ERR0, che indicano la condizione di malfunzionamento del dispositivo TAS5101, possono essere lasciati, nel caso in esame, flottanti.

Invece, il pin /SHUTDOWN indica che il dispositivo è finito in condizione di shutdown: esso può essere usato per resettare il TAS5001, a monte, nel caso che ciò accada.

/HiZ è un ingresso, tramite il quale è possibile costringere l’uscita del TAS5101 in condizione di alta impedenza. Se tale funzionalità non è necessaria, si pone /HiZ a 1 (+3.3V).

Alimentazione e massa per la sezione digitale dell’integrato sono costituite da DVDD e DVSS. DVDD deve essere posto a +3.3V.

Le alimentazioni, elevate, per le sezioni analogiche di uscita sono invece PVDDA1, PVDDA2, PVDDB1 e PVDDB2, cui corrisponde la massa PVSS. I massimi valori previsti per tali alimentazioni si aggirano attorno ai 26V, con valori minimi di PVDDA2 e PVDDB2 posti dal costruttore a 10.5V. Poiché il carico che si deve guidare non richiede l’utilizzo di potenze elevate, si sceglierà un valore relativamente basso dell’alimentazione della sezione analogica, attorno a 12V. In tal caso (per valori di PVDD inferiori a 16.5V), i datasheet prescrivono di connettere assieme LDROUTA con PVDDA2, e LDROUTB con PVDDB2.

Per il valore delle capacità che devono essere inserite esternamente, tra i pin BOOTSTRAPA e BOOTSTAPB e le uscite, si rimanda ai datasheet [28] e [30].

Analogamente, si rimanda a [28] e [30], anche a proposito dei componenti discreti che devono essere connessi ai pin BIASA, BIASB e VRFILT.

OUTPUTA ed OUTPUTB sono le uscite del TAS5101, segnali modulati PWM a tensione elevata. Tali uscite sono guidate da transistori DMOS in configurazione “H-bridge”: questi transistori sono alternativamente spenti o completamente accesi, cosa che riduce la loro resistenza parassita durante la conduzione e la potenza dissipata nel dispositivo, aumentandone l’efficienza. Il risultato è un segnale d’uscita ad onda rettangolare, con un duty cycle proporzionale all’ampiezza del segnale audio.

Figura 4.14: utilizzo del TAS5101: canale sinistro.

4.3.6 Filtro di ricostruzione della sinusoide in uscita.

Figura 4.15: Filtro di uscita del sistema TDAA.

Lo scopo principale del filtro d’uscita è attenuare la componente di switching ad alta frequenza dell’amplificatore TDAA mantenendo i segnali nella banda audio.

Questo filtro passa-basso è caratterizzato dalla sua frequenza di cut-off (a -3dB), dal suo guadagno, dal ripple nella pass-band e dall’attenuazione nella stop-band. L’ordine del filtro determina quanti poli esistono alla stessa frequenza, ognuno dei quali accresce la pendenza dell’attenuazione di -20dB per decade. La frequenza di switching dell’amplificatore può influenzare la scelta dell’ordine del filtro: più alta è tale frequenza, meno alto è l’ordine del filtro richiesto per ottenere una data attenuazione nell’intorno di essa. Questo suggerisce di usare la più alta frequenza di switching possibile, altro valido motivo per cui il segnale viene sovracampionato.

Il filtro di uscita utilizzato nel caso in esame è un semplice filtro passivo LC di Butterworth di second’ordine, la cui risposta in frequenza risulta sufficientemente piatta nella banda audio e che richiede un piccolo numero di componenti discreti.

La funzione di trasferimento per un filtro di Butterworth del secondo ordine è:

1 2 s 1 H(s) 2+ + = s

Per studiare più agevolmente la risposta in frequenza del filtro, se ne può dapprima considerare una versione semplificata, con un ingresso unipolare rispetto ad un riferimento di massa, ed una sola induttanza.

Figura 4.16: Circuito semplificato usato per lo studio del filtro d’uscita. La funzione di trasferimento per il circuito semplificato è:

C' L' 1 C' R' s s C' L' 1 H(s) 2+ + =

da cui risultano i valori dei componenti discreti:

R' f π 2 2 1 C' co ⋅ = e co f π 2 R' L' ⋅ =

essendo fco la frequenza di cut-off del filtro. Si può passare facilmente ora al circuito definitivo.

R = R’ C = C’ co f 4π R 2 2 L' L ⋅ = =

La frequenza di cut-off del filtro risulta essere:

2LC 2π

1 fco =

Le capacità denominate C1A e C1B in figura 4.15 servono come bypass per le alte frequenze; il loro valore, scelto empiricamente, è circa il 10% di 2C.

La scelta dei singoli componenti discreti è ora essenzialmente legata solo al valore della resistenza di carico e alla frequenza di switching del segnale PWM.

Una consueta frequenza di switching utilizzata da un sistema TDAA è di 352.8kHz, mentre la banda audio che si vuole preservare è tipicamente quella da 20Hz a 20kHz (anche se nel caso specifico si potrebbe limitare a quella compresa tra 1.5kHz e 3kHz). Si può quindi pensare di utilizzare una frequenza di cut-off attorno ai 35kHz, sufficientemente maggiore del limite massimo della banda audio, ma comunque una decade sotto la frequenza di switching, alla quale si avrà quindi un’attenuazione di circa 40dB. Considerando la resistenza di carico del caso in esame (4Ω), si ottiene:

C = 786nF L = 12.6µH

Tali valori sono quelli che si ottengono tramite il calcolo matematico preciso. Si sceglieranno poi, nella pratica, elementi discreti con valori prossimi a quelli appena ottenuti, tra quelli effettivamente disponibili in commercio. Un possibile filtro di uscita coerente con quanto appena esposto è mostrato in figura 4.18.

Figura 4.18: Filtro di ricostruzione della sinusoide, per il solo canale sinistro.

Per quel che riguarda la scelta dei componenti, le due induttanze sono elementi chiave che determinano le effettive performance del sistema. In particolare sono importanti per esse le specifiche di resistenza e di corrente, continua e di picco, sopportabile. La resistenza delle induttanze, in particolare, ha diretta influenza sull’efficienza del sistema TDAA, che può essere calcolata con la formula approssimata:

(load) (ind) (DMOSon) (in) (out) R R R 2 1 1 P P η + ⋅ + = =

fornita dal costruttore dei dispositivi TAS51xx (Texas Instruments), in cui R(load) è la resistenza dc del carico, R(DMOSon) quella dei transistori di potenza DMOS dello stadio di uscita del TAS51xx nello stato di completa conduzione, e R(ind) quella degli induttori. Si sceglieranno quindi induttori con basso valore di resistenza, per non diminuire troppo il rendimento del sistema.

Dal punto di vista delle correnti sopportate, per evitare la saturazione magnetica, che può condurre ad una forte distorsione del segnale audio o addirittura al danneggiamento dello speaker, si preferiranno induttori con rating di corrente sufficientemente elevati, anche al prezzo di aumentare costi ed ingombri.

I condensatori, invece, dovranno ovviamente essere in grado di sopportare le tensioni ad essi applicate. In particolare C2 deve essere capace di gestire la tensione RMS di uscita

dall’amplificatore, C1A e C1B la somma tra le tensioni dc e ac, cioè la quantità /2

R P

Vss/2+ max∗ (load) , dove Vss è la tensione di alimentazione in ingresso e Pmax la massima

potenza di uscita RMS dall’amplificatore.

4.3.7 Controllo delle oscillazioni indesiderate.

Quando si progetta un circuito stampato, bisogna tener presente il fatto che le stesse tracce del circuito possono dar luogo a capacità ed induttanze parassite, anche piuttosto consistenti. Esistono per questo alcune accortezze da utilizzare a livello di layout, come, ad esempio, almeno in punti critici, disporre gli elementi discreti in modo da minimizzare la lunghezza delle piste stampate. In questo modo viene minimizzata anche l’induttanza parassita, fornita dall’equazione:

+ + ⋅ + + ⋅ ⋅ ⋅ = − 0.2235 w h 0.5 h w 2.1 ln 10 2 L 7 l l

E’ inoltre utile evitare di creare layout che diano luogo ad elevate capacità parassite. Si prenda l’esempio di una linea di alimentazione con un condensatore ceramico di decoupling: se vi è, vicino, un piano a tensione di alimentazione affacciato ad un sottostante piano di ground, si può creare una capacità parassita elevata, collegata ad un condensatore effettivo tramite un tratto di linea, corrispondente ad un’induttanza. Ciò potrebbe portare ad un’oscillazione indesiderata.

Per evitare interferenze di tipo elettro-magnetico (le tracce dello stampato rischiano in molti casi di comportarsi come “antenne”), spesso si usano circuiti RC. Ad esempio, come si osserva in figura 4.14, sono state usate semplici reti di condensatori e resistenze per evitare oscillazioni indesiderate agli ingressi delle alimentazioni elevate del TAS5101, PVDDA1 e PVDDB1.

Analogamente, è utile l’inserimento di filtri contro le interferenze elettro-magnetiche in prossimità degli speaker, a valle del filtro di ricostruzione della sinusoide (Figura 4.18).

Esistono delle formule empiriche che permettono di calcolare i valori di R e C per tali filtri, in funzione delle capacità (Cs) e delle induttanze (Ls) parassite:

s s C L 2 1 R = s C 3 C= ⋅

4.3.8 Dissipazione termica

Tradizionalmente “surface-mount” e “potenza” sono stati termini mutamente esclusivi. Infatti l’elevata quantità di calore generata nei dispositivi di potenza difficilmente riesce ad essere dispersa nell’ambiente dai piccoli package tradizionali dei dispositivi surface-mount. Questi involucri sono normalmente di dimensioni ridotte e non prevedono particolari sistemi di dissipazione.

Al contrario, il package PowerPAD utilizzato per il TAS5101, pur essendo di molto ridotte dimensioni, prevede un efficace sistema di dissipazione del calore, tramite un Thermal Pad posto sotto il dispositivo, che deve venire a contatto con il circuito stampato sottostante. In questo modo si riescono a combinare i vantaggi della tecnologia SMD con le performance termiche proprie dei dispositivi tradizionali, dotati di package più grandi.

Figura 4.19: Package PowerPAD con Thermal pad.

4.3.9 Sistema di “Closed-Loop Reset” consigliato.

E’ consigliato dal produttore del chipset TDAA (Texas Instrument) un sistema tramite il quale si possa effettuare il reset del dispositivo TAS50xx, in seguito ad un avvenuto shutdown di uno dei due TAS5101 a valle. Ciò può avvenire in seguito a parecchie condizioni critiche, come una temperatura del chip eccessiva, od una corrente in uscita troppo elevata (in questo caso il meccanismo costituisce anche una protezione contro eventuali cortocircuiti).

Figura 4.20: Configurazione di “Closed-Loop Reset” raccomandata.

4.3.10 Eventuale rete di adattamento in uscita

Tutte le considerazioni circuitali svolte fino ad ora riguardano l’ipotesi di uno speaker in uscita che possa ricevere ingressi differenziali, e dalla resistenza di carico prestabilita di 4Ω. Se tuttavia una delle due condizioni non si verificasse, dovrebbero essere previste reti di adattamento fra l’uscita del filtro e lo speaker.

Ad esempio, poiché lo speaker audio si trova a lavorare in condizioni meccaniche particolari (all’interno di una cavità risonante), potrebbe non essere assicurata la costanza della sua resistenza d’ingresso. In particolare essa potrebbe risultare minore di 4Ω, caso che potrebbe influire molto sulla risposta in frequenza del filtro di ricostruzione della sinusoide, progettato per un carico di 4Ω.

Si ricorda inoltre che lo stesso dispositivo TAS5101 non è ottimizzato per carichi inferiori a 4Ω. Per ovviare al problema, si può pensare di utilizzare una semplice rete di adattamento resistiva, del tipo mostrato in figura 4.21.

TAS50xx /RESET VALID TAS51xx /RESET /SHUTDOWN TAS51xx /RESET /SHUTDOWN 2.2 kΩ 2.2 kΩ 3.3V 10 nF

System /Reset 22 µs delay

Figura 4.21: Rete di adattamento resistiva in uscita.

All’ingresso di tale rete si vedranno sempre almeno 2Ω. Alcuni valori di riferimento, per le fluttuazioni della resistenza d’ingresso alla rete, sono mostrati in tabella 4.3.

R speaker R in 6Ω 4.40Ω 5Ω 4.22Ω 4Ω 4Ω 3Ω 3.71Ω 2Ω 3.33Ω 1Ω 2.80Ω

Tabella 4.3: Stabilizzazione della resistenza vista in uscita tramite la rete d’adattamento resistiva di figura 4.21.

La rete d’adattamento di figura 4.21 presenta purtroppo l’inconveniente di richiedere molta più potenza in uscita: se si vogliono disponibili allo speaker 4W di potenza, all’ingresso della rete dovranno essere forniti 16W. Se si alimenta il TAS5101 a 12V, come precedentemente ipotizzato, si riusciranno comunque ad ottenere i 16W richiesti.

Nel caso si debba invece presentare il caso di uno speaker unipolare, la rete di adattamento che si potrebbe utilizzare è quella di figura 4.22.

1Ω 4Ω 4Ω? 1Ω R in R speaker

Figura 4.22: rete di adattamento per speaker unipolare.

La rete appena mostrata risolve anche il problema di stabilizzazione della resistenza vista, ma, come la precedente, comporta un grande spreco di potenza.

R speaker R in 6Ω 4.44Ω 5Ω 4.23Ω 4Ω 4Ω 3Ω 3.73Ω 2Ω 3.42Ω 1Ω 3.08Ω

Tabella 4.4: Stabilizzazione della resistenza vista in uscita tramite la rete d’adattamento resistiva di figura 4.22.

4.4 Alimentazione della scheda di interfaccia

Per poter decidere come alimentare la scheda di interfaccia, bisogna innanzi tutto ricapitolare le tensioni necessarie ai vari dispositivi, e le correnti massime che essi possono assorbire.

Si ha bisogno di due tensioni di alimentazione principali: una, bassa, 3.3V, per i ricevitori differenziali, il TAS5001 e la sezione digitale del TAS5101; una, più alta, 12V, per la sezione analogica del TAS5101.

Nella tabella seguente sono indicati gli assorbimenti di corrente per gli integrati che sfruttano la tensione più bassa.

8Ω

4Ω 4Ω

Dispositivo integrato TYP MAX UNIT

AM26LV32 8 17 mA

TAS5001 – Digital 22 - mA

TAS5001 – Analog 8 - mA

TAS5101 – Digital 2 - mA

Tabella 4.5: correnti assorbite dai dispositivi sulle alimentazioni a 3.3V.

In totale quindi, considerando anche la necessità di 15 dispositivi AM26LV32, si avrà un assorbimento massimo di corrente, dall’alimentazione a 3.3V, di circa 300mA. Tale valore non è molto elevato: in questo caso si può sfruttare la tensione fornita sul bus micro-line dalla Power Supply Board. Come già osservato in precedenza, essa è infatti stata ideata per alimentare più schede (dotate di connettori di tipo micro-line) sovrapposte, fornendo, tramite la tensione 5V, correnti fino a 2.5A. Poiché l’assorbimento della C6713Compact si aggira sui 500mA, senz’altro la tensione di alimentazione per la sezione digitale della scheda di interfaccia può essere ricavata da quella fornita dalla Power Board.

Sarà sufficiente un semplice regolatore dc/dc integrato, che produca la tensione 3.3V partendo dai 5V. Si può ad esempio utilizzare il “Low Dropout Regulator” LM3940 prodotto da National Semiconductor, che può erogare fino a 1A di corrente.

Figura 4.23: LM3940IT-33, 3-lead TO-220 package, disponibile su catalogo RS.

L’utilizzo del dispositivo è molto semplice, e tipico di questo tipo d’oggetti: saranno esternamente necessari solamente due condensatori, uno all’ingresso ed uno all’uscita.

Il condensatore d’uscita è critico in rapporto alla stabilità del sistema: esso dovrà essere necessariamente di valore uguale o superiore a 33µF, e con una resistenza serie equivalente nel range mostrato dal grafico di figura 4.25. Se tali condizioni non venissero verificate, il sistema potrebbe entrare in oscillazione.

Figura 4.25: Regione di stabilità per la resistenza serie equivalente del condensatore.

Bisogna far attenzione al fatto che generalmente i costruttori indicano solamente la resistenza a temperatura ambiente, mentre in realtà questa varia molto con la temperatura. Ad esempio, la resistenza di un condensatore elettrolitico alluminico può aumentare di un fattore 30, se la temperatura scende da +25°C a -40°C. Condensatori al tantalio solido hanno invece un comportamento più costante con la temperatura, ma sono anche molto più costosi. Una scelta intermedia, giustificata anche dal fatto che la Data-Processing Board non sarà utilizzata in condizioni ambientali particolarmente severe, consiste nell’utilizzare due condensatori in parallelo: un elettrolitico di elevata capacità, per ottenere senza troppo costo i 33µF desiderati, ed un “solid Tantalum” più modesto, e quindi meno costoso, per stabilizzare la resistenza serie equivalente.

Al contrario di ciò che accade con l’alimentazione a +5V, quella a +12V non può essere fornita dalla Power Board. Quest’ultima potrebbe infatti procurare al massimo una tensione di +15V, destinata anche al Physical Layer Transceiver IEEE1394, ma con massima corrente erogabile attorno ai 200mA, in gran parte assorbiti proprio dal Phy. La richiesta di corrente erogabile dalla sorgente a +12V è invece abbastanza elevata, dell’ordine di grandezza di un paio d’Ampere. Ne consegue che i +12V dovranno essere forniti da un alimentatore stabilizzato separato, capace di erogare qualche Ampere.

Come consigliato dal costruttore, è bene prevedere degli “snubber circuit” in corrispondenza delle alimentazioni per le sezioni analogiche. In figura 4.26 sono mostrati i filtri per i due canali, destro e sinistro; notare che le induttanze L3, L4, L5, L6, possono essere create su PCB tramite piste metalliche larghe 0.5mm e lunghe circa 40mm.

Figura 4.26: Snubber circuit sull’alimentazione della sezione analogica del TAS5101.

4.5 Chassis e alimentatori richiesti

Una volta stabilite le dimensioni totali della Data-Processing Board e le richieste d’alimentazione delle varie parti del sistema, è possibile fornire al committente (ESO) tali dati, di modo che questi possa predisporre uno chassis di dimensioni adeguate, con all’interno anche gli alimentatori necessari sia alla Data-Processing Board sia alla Detection Board.

Le dimensioni totali della Data-Processing Board appaiono delimitate principalmente, in larghezza e lunghezza, da quelle della Power Supply Board: 160mm x 120mm.

In altezza le dimensioni saranno limitate invece dall’altezza delle tre schede (Power, C6713Compact, Interfaccia) montate l’una sovrapposta all’altra.

Considerando anche lo spazio necessario per inserire i connettori ed i cavi per collegare le schede con i connettori da pannello montati sullo chassis, si possono considerare accettabili come dimensioni minime dell’involucro le seguenti: 230mm x 180mm x 100mm, cui poi andrà aggiunta la sezione contenente gli alimentatori.

Per quel che riguarda i connettori da pannello che devono essere montati sullo chassis, essi saranno:

• Un connettore LEMO 1B a 7 poli, che porta l’alimentazione alla Detection Board

• Una serie di 8 connettori SMC, per I/O di tipo generico • 4 connettori LEMO a 2 poli per le uscite Audio

• Il connettore a 9 pin per la seriale RS-232

Inoltre è da prevedere uno sportellino laterale con due asole, fissato da 4 viti, per l’ingresso e l’uscita dei cavi Firewire.

(a)

(b)

2 connettori SCSI Lemo 7

I/O: SMC RS 232 Audio: LEMO2 Minimo: circa 180mm Mimino: circa 230mm

(sezione Data processing board)

Dipende dalle dimensioni degli alimentatori (sezione alimentatori)

Sezione alimentatori Sezione Data Processing board

Sportellino per la Firewire: vedi particolare. Minimo: circa 100mm

(c)

Figura 4.27: Chassis. In (a) è visibile il retro, con i connettori da pannello, in (b) il fronte, in (c) la proiezione laterale con le dimensioni previste per lo “sportellino Firewire”. Notare che le dimensioni non sono perfettamente in scala e che la disposizione dei connettori è puramente

indicativa e non vincolante.

L’alimentazione che deve essere fornita alla Data-Processing Board, è molto semplicemente costituita da una tensione stabilizzata a +12V (common ground) capace di erogare fino a 5A. Le altre tensioni necessarie al funzionamento dei vari componenti delle schede (+5V, +3.3V…) vengono generate internamente alle schede stesse.

Per completezza si riportano, in tabella 4.6, anche le tensioni necessarie alla Detection Board, che saranno fornite ad essa dagli alimentatori, tramite il connettore LEMO a 7 poli citato poco sopra.

Tensione richiesta Corrente corrispondente richiesta

-24V d.c. floating 120mA rms, 1A suggested

+12V d.c. common ground 600mA rms, 2A suggested

+5V d.c. common ground 1.5A, 3A suggested

+12V, for Peltier, d.c. separated ground 4A, 5A suggested

Tabella 4.6: Alimentazioni richieste dalla Detection Board. Circa 100mm

Circa 75mm

Asole per il passaggio dei cavi Firewire.

Minimo: circa 100mm

Minimo: circa 180mm