Capitolo 3

La piattaforma di sviluppo ed il

partizionamento del progetto

3.1 Scelta della piattaforma di sviluppo

Come già esposto precedentemente, al gruppo di lavoro dell’università di Pisa compete la sezione del progetto costituita dalla realizzazione della Data-Processing Board e del software su computer remoto, secondo le specifiche enunciate.

In particolare la scheda di Data-Processing deve avere tra le sue caratteristiche:

• Una grande disponibilità di logica programmabile, per implementare soprattutto contatori e registri di ausilio.

• Una buona capacità di elaborazione aritmetica, utile alla generazione della sinusoide e al calcolo del segnale di curvatura. Altre elaborazioni, richieste da un eventuale post-processing, statistico e diagnostico, potranno essere effettuate dal software del computer remoto.

• La possibilità di gestire la risorsa di comunicazione IEEE1394 (Firewire).

• Una discreta quantità di memoria, in cui creare strutture di tipo FIFO nelle quali inserire i dati da comunicare al computer remoto, in modo da poter garantire che nessun dato vada perso in eventuali intervalli di tempo in cui il computer non riesca ad acquisire in tempo reale.

Queste necessità hanno portato alla scelta di utilizzare, come cuore della Data-Processing board, una scheda assemblata e venduta dalla ditta tedesca Orsys, la C6713Compact. Essa monta, in particolare:

• Una FPGA Xilinx Virtex-II dalla complessità di 1Mgate, sulla quale implementare la sezione di logica programmabile.

• Un DSP floating point Texas Instruments TMS320C6713, a 225MHz, con grande potenza di calcolo (1800MIPS o 1350MFLOPS), e 256k di RAM interna.

• La possibilità di gestire la comunicazione via Firewire IEEE1394, attraverso un chipset dedicato, su due porte.

• Una gran quantità di memoria, sotto forma di Flash EPROM (32Mbyte, organizzata a 16 bit) e SDRAM (64Mbyte, organizzata a 32 bit).

Inoltre la scheda può vantare dimensioni contenute, che ne agevolano l’inserimento nei diversi sistemi di osservazione astronomica.

Alla C6713 vanno affiancate almeno altre due schede. La prima è di esclusivo supporto alla C6713, per quel che concerne l’alimentazione e la comunicazione seriale; fornita anch’essa dalla Orsys, è la Power Supply (PS) Board. La seconda costituisce l’interfaccia con la Detection Board e la membrana di focalizzazione del fronte luminoso incidente.

L’unione delle tre schede, montate l’una sovrapposta all’altra, costituirà l’intera Data-Processing Board.

3.2 La scheda Orsys Micro-Line

®C6713Compact

Come già rilevato, la scheda micro-line® C6713Compact è una board di processazione dati, basata su DSP, ad elevate prestazioni.

Figura 3.1: la scheda Orsys C6713Compact.

Per lo sviluppo, il debug e la programmazione della scheda sono necessari come minimi tool aggiuntivi:

• Un PC per lo sviluppo.

• Un emulatore JTAG, come lo XDS560.

• Il software Code Composer Studio, per la programmazione del software del DSP.

3.2.1 Struttura hardware

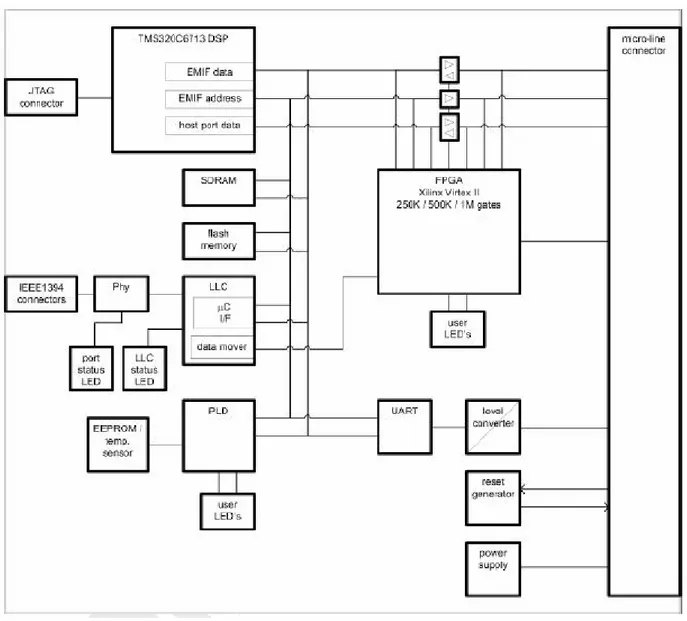

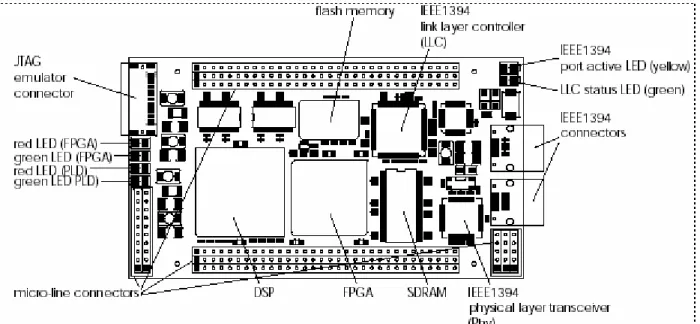

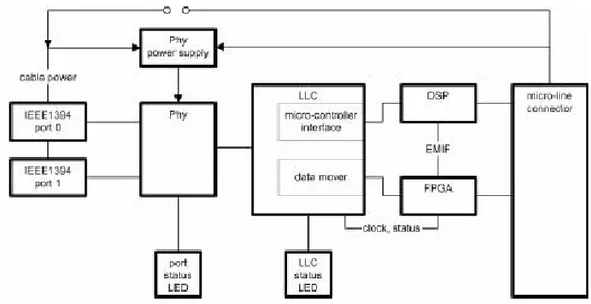

Un diagramma a blocchi della struttura complessiva della scheda è mostrato in figura 3.2, mentre nelle successive immagini, 3.3 e 3.4, sono mostrate le proiezioni schematiche delle due facce della board.

Figura 3.3: Component side della scheda Orsys C6713Compact.

Figura 3.4: Bottom side della scheda Orsys C6713Compact.

3.2.2 Connettori

3.2.2.1 Connettore micro-line®

Il connettore principale della board è il micro-line®, diviso a sua volta in 6 gruppi di 32 pin, 2 di 8 pin e 3 di 4 pin. Esso è realizzato in modo da poter impilare l’una sull’altra, molto facilmente, schede dotate dello stesso standard: è il caso, ad esempio, della power supply board utilizzata, che

viene posta immediatamente al di sotto della C6713, alla quale è connessa tramite il connettore micro-line.

In generale i segnali legati al connettore micro-line possono essere suddivisi in tre gruppi principali:

• Power supply

• Segnali di interfaccia col DSP o con la board. • Segnali direttamente legati all’FPGA.

Esiste uno standard micro-line che attribuisce ad ogni pin del connettore un compito ed un collegamento specifico, tuttavia queste connessioni possono essere quasi completamente riconfigurate dall’utente, secondo le esigenze specifiche. Ad esempio, nel collegamento standard la maggior parte dei pin vengono riservati all’accesso al DSP, mentre nell’utilizzo che si farà di questa scheda per scopi astronomici gran parte dei pin dovranno essere utilizzati come ingressi diretti all’FPGA, per il conteggio dei fotoni.

3.2.2.2 Connettore JTAG

Il connettore JTAG viene usato durante lo sviluppo delle applicazioni, ed è associato alle interfacce JTAG di DSP e FPGA; pertanto è usato sia nella fase di debugging, sia per il download di applicazioni nel DSP, sia per il salvataggio nella memoria flash di codice per il DSP o per la programmazione dell’FPGA.

L’interfaccia JTAG del DSP è utilizzabile assieme ad un emulatore JTAG e al software Code Composer Studio.

Per quel che riguarda l’FPGA, durante lo sviluppo del progetto è possibile tramite il JTAG scaricare velocemente il codice in essa, per testarlo direttamente. Nell’utilizzo finale dell’applicazione il codice sarà invece salvato nella memoria flash, e caricato sull’FPGA tramite il DSP.

3.2.2.3 Connettore IEEE1394

La scheda C6713Compact ha due connettori IEEE1394, che possono essere usati tramite cavi standard a 6 pin. Nell’applicazione legata al progetto SPADA tale interfaccia permetterà la comunicazione con l’host computer, sia in upload sia in download.

Appare importante anche il fatto che vi siano due connettori IEEE1394, e non uno solo. Ciò permetterà infatti, in futuro, di poter inserire facilmente la scheda in una rete Firewire più complessa del solo nucleo “host computer + Data Processing board”, nel caso ve ne sia l’esigenza.

3.2.3 Componenti Hardware e Interfacce 3.2.3.1 FPGA

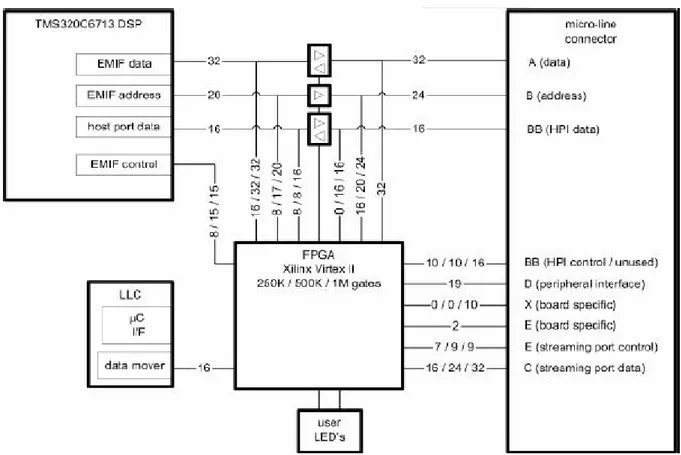

L’FPGA, dalla complessità di 1MGate, permette all’utente di sfruttare una gran quantità di logica programmabile. Essa diventa uno strumento molto versatile grazie alla flessibilità delle connessioni permesse dalla scheda: in particolare esiste la possibilità di legare molti dei pin di ingresso/uscita dell’FPGA a quelli del connettore micro-line e all’interfaccia del DSP.

Più in dettaglio l’FPGA ha accesso a:

• DSP EMIF (External Memory InterFace): bus dati, bus indirizzi, segnali di controllo. • Pin del connettore micro-line

• Data mover port del Link Layer Controller per l’interfaccia IEEE1394 • Periferiche del DSP: HPI, McASP, GPIO…

• Bus driver control (data, address, HPI data) • Interfaccia JTAG

• Interrupts del DSP

La figura 3.5 mostra uno schema di alcune possibili connessioni per l’FPGA; si noti che sono in commercio anche schede C6713Compact con FPGA di complessità minore di 1MGate, e in figura sono evidenziate le possibilità di connessione per ciascuna versione della board: naturalmente, la maggiore versatilità si ottiene con le schede che montano FPGA più complesse. Proprio questa alta flessibilità, assieme alla possibilità di avere più logica programmabile disponibile, ha portato alla scelta della versione della C6713Compact con FPGA più complessa.

Gli utilizzi indicati in parentesi accanto ai gruppi di pin del connettore micro-line sono quelli definiti dallo standard, ma completamente riconfigurabili.

Figura 3.5: possibilità principali di connessione per l’FPGA

3.2.3.2 Interfaccia IEEE1394

La C6713Compact utilizza come chipset per l’interfaccia IEEE1394 il Link Layer Controller (LLC) Texas Instruments TSB12LV32, ed il Physical layer transceiver (Phy) TSB41AB2.

Il chipset contempla:

• Una comunicazione ad un massimo di 400Mbit/s, in accordo col protocollo IEEE1394. • Un trasferimento dati isocrono continuo a 32768000 bytes/s.

• Due vie indipendenti all’interno dell’LLC: la “micro-controller interface”, collegata al DSP, e la “data mover port”, collegata all’FPGA.

• Due connettori di uscita distinti, previsti anche nella possibilità di connessione all’interno di reti senza l’utilizzo di hub.

Figura 3.6: il chipset per la comunicazione IEEE1394.

Per le operazioni IEEE1394, un software per la transazione dati gira sul DSP e accede all’LLC attraverso la micro-controller interface, in modo da permettere una transazione asincrona in ingresso o in uscita, comprendente fino a 2048 bytes per ogni pacchetto dati.

Il trasferimento di dati isocrono è invece di solito implementato tramite la via “data mover”, connessa alla sola FPGA: da questa lo stream di dati può essere diretto verso il DSP o il connettore micro-line usando i board support package forniti con la scheda, o attraverso un design dedicato effettuato dall’utente. Il ciclo di clock del trasferimento sincrono può essere ricevuto o controllato dall’FPGA.

Il Link Layer Controller può generare interrupt, che sono portati a destinazione attraverso il PLD.

L’alimentazione del Physical layer transceiver, diversa da quella del resto della scheda, è fornita dalla power supply board. Alternativamente è possibile configurare la scheda in modo che la stessa connessione IEEE1394 provveda a tale alimentazione.

3.2.3.3 Memoria esterna (SDRAM)

La C6713Compact utilizza una memoria esterna SDRAM da 64Mbyte, organizzata a 32 bit. Essa costituisce un valido appoggio per la memorizzazione dei dati, soprattutto in applicazioni di imaging, come quelle di carattere astronomico che si vogliono realizzare.

L’accesso alla memoria esterna avviene tramite l’EMIF clock, a 90MHz. Paragonata alla memoria interna del DSP, questa appare quindi molto più lenta, e la stessa EMIF deve anche essere condivisa con altre risorse, come la UART. Quindi, per quel che riguarda l’utilizzo del DSP in operazioni che richiedono elevate velocità, è consigliabile l’uso della memoria interna sia come

registro d’appoggio per i dati, sia per il salvataggio del codice di programma, almeno finché questo risulta possibile.

3.2.3.4 Memoria Flash

La C6713Compact utilizza una memoria flash EEPROM Am29LV256 a 32Mbyte (organizzata a 16 bit), per la memorizzazione non volatile di codice, applicativo per il DSP e di programmazione per l’FPGA.

Al reset o all’accensione, il boot loader interno del DSP carica il primo Kbyte contenuto in memoria flash, partendo dall’indirizzo 0, e lo esegue. Normalmente in questo segmento di codice è contenuta la direttiva di effettuare un secondary boot loader, per caricare il resto dell’applicazione, solitamente molto più grande di 1 Kbyte.

La memoria flash viene logicamente suddivisa in 32 segmenti di 1Mbyte ciascuno. Essi sono accessibili in modo mutuamente esclusivo: i 5 bit più significativi del registro FSR del PLD controllano quale segmento della memoria flash sia correntemente accessibile.

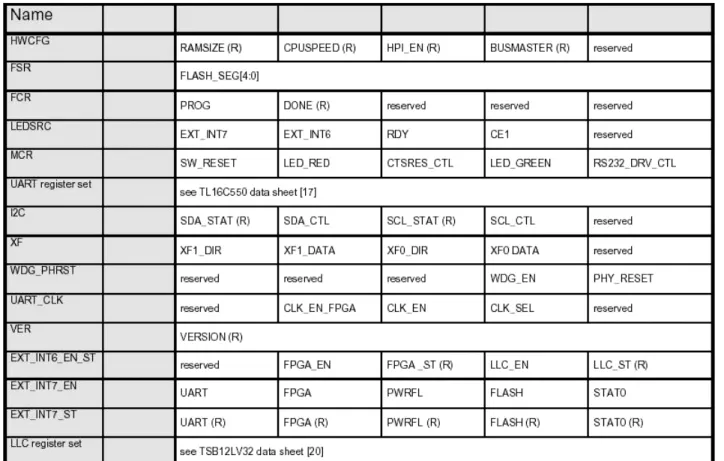

3.2.3.5 PLD

Il PLD costituisce la “glue logic” della board: esso permette infatti, tramite i suoi registri, di accedere alle varie parti hardware della scheda e di configurarne alcune opzioni.

Fra i registri più importanti, oltre al già citato FSR, è utile evidenziare anche i seguenti:

• HardWare ConFiGuration register (HWCFG): contiene informazioni sui settaggi hardware della board: dimensioni della memoria RAM, velocità massima della CPU, abilitazione dell’interfaccia HPI del DSP, funzionamento della C6713Compact in modo master o slave.

• FPGA Control Register (FCR): viene usato dalle applicazioni per caricare codice nell’FPGA.

• Module Control Register (MCR): contiene, fra gli altri, un bit per il reset software della board, uno per il controllo dello stato del LED rosso ed uno per quello del LED verde. • WatchDoG enable and Phy ReSeT register (WDG_PHRST): il bit numero 4, posto ad 1,

abilita il meccanismo di watchdog. Il bit numero 3 è usato per resettare il Physical layer transceiver.

• Version Register (VERSION): contiene il codice identificativo della versione della board.

Altri registri controllano varie altre impostazioni possibili per la scheda, come ad esempio quelle riguardanti il routing dei segnali di interrupt per il DSP, la gestione degli external flags, alcuni controlli sull’interfaccia UART…

3.2.3.6 Interfaccia UART / RS-232

L’interfaccia RS-232 è realizzata tramite il dispositivo UART Texas Instruments TL16C550, connesso al line driver RS-232. Tale interfaccia è comunemente usata come forma generica di comunicazione, ad esempio per trasmettere ad un host computer risultati di misurazioni, oppure come connessione a periferiche remote. Nel caso del progetto SPADA, la RS-232 sarà un’interfaccia per la comunicazione con la Detection Board, mentre in fase di testing può risultare utile come output per le informazioni di debug.

L’interfaccia consiste nei segnali TxD (Transmit Data), RxD (Receive Data), RTS (Request To Send) e CTS (Clear To Send). Questi segnali sono disponibili anche su pin dedicati del connettore micro-line.

3.2.3.7 EEPROM seriale

E’ presente sulla scheda anche una memoria EEPROM seriale di 256 byte, integrata col sensore di temperatura della board: essa può utilmente contenere il serial number e altri parametri. I driver software per questa memoria sono forniti con la documentazione della C6713Compact.

La EEPROM è connessa al PLD tramite un’interfaccia I2C, e vi si può accedere tramite l’I2C bus

control register.

3.2.3.8 Sensore di temperatura

La scheda C6713Compact contiene un sensore, con interfaccia I2C, che permette di misurare la

sua temperatura durante l’utilizzo, con un range tra -55 e +125 gradi Celsius e la risoluzione di un grado. Se la board opera in un ambiente in cui è esposta ad alte temperature, il sensore può divenire indispensabile ad evitare condizioni di rischio. La temperatura interna della CPU è al massimo di circa 15 gradi superiore a quella misurata dal sensore. I driver software per il sensore sono forniti con la documentazione della C6713Compact.

Anche il sensore è ovviamente connesso al PLD tramite l’interfaccia I2C, e vi si può accedere

tramite l’I2C bus control register.

3.2.3.9 Generatore di reset e Watchdog

Il generatore di reset della C6713Compact genera un impulso di reset nel caso si presentino uno o più dei seguenti casi:

• Accensione

• Reset software (attraverso il module control register) • Pin /RESETIN attivo

• Discesa di una tensione d’alimentazione sotto il limite minimo • Azzeramento del Watchdog timer del reset generator, se attivo • Linea CTS attiva e configurata come reset function.

Durante l’impulso di reset vengono rese attive le uscite RESETOUT e /RESETOUT.

Il generatore di reset è dotato, come accennato, di un timer di Watchdog che causa un reset della scheda se non è periodicamente, a sua volta, resettato dal software. Questo meccanismo può essere utilmente sfruttato nella comunicazione tra la Data-Processing Board e la Detection Board come meccanismo di sicurezza, previsto anche dalle specifiche del progetto.

Il Watchdog Timer è di default disabilitato: per attivarlo basterà porre ad 1 il bit numero 4 del registro di configurazione WDG_PHRST del PLD.

3.2.3.10 External Flags (XF signals)

La scheda C6713Compact presenta due pin dedicati ad applicazioni generiche, che possono essere impostati come ingressi od uscite.

In entrambi i casi, la lettura di tali segnali, o la loro scrittura, avviene tramite il registro XF del PLD.

Esempi di applicazione classici riguardano la gestione di una linea di controllo verso un dispositivo esterno: se configurati come uscite daranno ad esso dei segnali di sincronizzazione o controllo, se configurati come ingressi ne rileveranno lo stato.

3.2.3.11 Alimentazione

La scheda C6713Compact, che non sopporta inversioni della tensione d’alimentazione, deve essere alimentata con una tensione tra i 3.3V e i 5V. Internamente sono poi generate tutte le tensioni, minori od uguali a 3.3V, necessarie al funzionamento dei diversi componenti hardware:

• 1.26V per il core del processore DSP

• 3.3V per la maggior parte della circuiteria digitale • 1.5V per il core dell’FPGA

• 3.3V, 2.5V e 1.8V per le celle di I/O dell’FPGA connesse al connettore micro-line. Il valore di default è 3.3V, gli altri due sono impostabili tramite una differente hardware configuration della board.

3.2.4 LED

Sulla scheda C6713Compact sono montati sei LED, suddivisi in tre gruppi:

• Due LED programmabili dall’utente, controllati dal PLD, che possono essere utilizzati dalle applicazioni software per mostrare determinati eventi o stati.

• Due LED programmabili dall’utente controllati dall’FPGA, con funzioni definite dal design dell’FPGA stessa.

• Due LED di stato legati all’interfaccia IEEE1394: il primo è giallo e si accende se il Phy è correttamente alimentato e connesso ad un'altra periferica IEEE1394; il secondo è verde e di default indica che nel registro FIFO di ricezione, all’interno del LLC, sono presenti dei dati da acquisire.

3.2.5 Periferiche del DSP

Il DSP montato sulla C6713Compact possiede un gran numero di periferiche integrate, alcune delle quali possono essere utilmente impiegate nel “progetto SPADA”. Le principali verranno ora descritte brevemente: approfondimenti sul loro funzionamento si possono reperire nella documentazione Texas Instruments ([22] e [23]).

Bisogna fare particolare attenzione, quando si usano contemporaneamente più periferiche, al fatto che alcune di esse condividono dei pin.

3.2.5.1 Multi-channel Audio Serial Ports (McASP)

Le periferiche McASP sono due porte seriali ottimizzate per la gestione di applicazioni audio, anche multicanale. Esse sono contraddistinte dalle sigle McASP0 e McASP1.

McASP0 è completamente connessa al bus micro-line, tranne che per la linea AMUTEIN0, connessa all’FPGA. McASP1 è invece connessa all’FPGA.

Notare come la porta McASP0 potrà essere utile in fase di generazione della sinusoide in banda audio, nell’ambito del progetto SPADA.

3.2.5.2 External Memory Interface (EMIF)

La EMIF è l’interfaccia principale verso le periferiche esterne. Essa ha accesso a: • Memoria esterna (SDRAM e flash)

• Periferiche on-board: UART, LLC e PLD. • Connettore micro-line attraverso bus driver.

Tramite l’ultima modalità ed un design appropriato dell’FPGA, è possibile accedere a periferiche esterne alla board.

3.2.5.3 Inter Integrated Circuit (I2C) Interface

Le interfacce I2C del DSP sono due: esse possono essere usate per accedere a periferiche quali il

sensore di temperatura, EEPROMS, convertitori D/A e A/D. Sulla C6713 è tuttavia disponibile una sola delle due interfacce I2C.

3.2.5.4 General Purpose Input/Output Peripheral (GPIO)

Sulla C6713Compact, l’uso di tale interfaccia è sconsigliato, in quanto non direttamente connessa al bus micro-line. Tuttavia possono essere utilizzati, come pin dell’interfaccia GPIO, alcuni pin normalmente dedicati agli External Flags (XF), ai McBSP e alle connessioni con pin liberi dell’FPGA.

3.2.5.5 Multi-Channel Buffered Serial Ports (McBSP)

Vi sono due McBSP indipendenti: ogni porta può comunicare in full duplex, con un data stream continuo fino a 75Mbps. Esse possono essere usate, ad esempio, per la comunicazione tra due processori, o per la connessione con altre periferiche, come codec e convertitori A/D e D/A.

Questa porta adotta lo standard delle interfacce seriali sincrone delle famiglie di DSP Texas Instruments TMS320C2000, ‘C3x e ‘C5000, e può essere programmata per divenire compatibile con ogni altra interfaccia sincrona seriale. Essa è costituita dai segnali DRx (data receive), DXx (data transmit), CLKRx (clock receive), CLKXx (clock transmit), FSRx (frame sync receive) e FSXx (frame sync transmit).

Di default, i segnali delle porte McBSP sono connessi al bus micro-line.

3.2.5.6 Timers

Il DSP TMS320C6713 contiene 2 timer indipendenti, a 32 bit. Ognuno di essi ha un pin di ingresso ed uno di uscita. Per maggiore versatilità d’utilizzo essi possono ricevere il clock da una sorgente esterna o da quella interna.

3.2.5.7 Host Port Interface (HPI)

Il DSP TMS320C6713 è dotato di una host port a 16 bit, che può essere usata da un host processor per avere accesso diretto alla memoria del DSP: in questo caso l’host accede come master ed il DSP viene visto come slave. L’host processor ed il DSP possono così scambiare dati sia attraverso la memoria interna del DSP, sia attraverso la memoria montata sulla board; l’host avrà inoltre accesso anche ai registri delle periferiche mappati in memoria. La connessione tra l’host e lo spazio di memoria del DSP è assicurata da un meccanismo DMA.

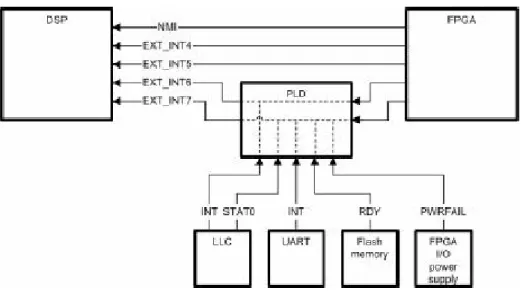

3.2.5.8 Interrupts

Quattro interrupt non mascherabili ed uno mascherabile permettono ai dispositivi della scheda o ad eventuali periferiche esterne di interrompere il programma corrente del DSP e saltare ad una routine di servizio dedicata all’interruzione.

Sulla C6713Compact, due linee di interrupt (EXT_INT6 e EXT_INT7) sono gestite dal PLD e due (EXT_INT4 e EXT_INT5) dall’FPGA. In tabella 3.2 sono mostrate le possibili fonti degli interrupt provenienti dal PLD.

source DSP interrupt line

LLC interrupt EXT_INT6

LLC STAT0 line EXT_INT7

UART interrupts EXT_INT7

Flash memory ready condition EXT_INT7 FPGA I/O power fail condition EXT_INT7

FPGA EXT_INT6, EXT_INT7

Tabella 3.2: sorgenti delle interruzioni gestite dal PLD.

Figura 3.7: routing delle interruzioni sulla C6713Compact.

3.2.5.9 DMA

Il DSP TMS320C6713 è dotato di un controller enhanced DMA (EDMA). Esso può essere usato per trasferire dati tra due locazioni qualunque nello spazio di memoria della C6713Compact. Tali trasferimenti dati possono essere sincronizzati dal software o da eventi generati internamente o esternamente alla scheda: gli eventi esterni sono segnalati per mezzo delle linee di interrupt. Le operazioni DMA possono essere concatenate, cioè la fine di ogni trasferimento di dati può dare inizio al successivo: ciò costituisce un potente e flessibile modo di svolgere operazioni senza l’intervento della CPU.

Il meccanismo DMA è quello che consente le maggiori prestazioni di velocità all’interno della scheda: il massimo throughput è 225Mwords per secondo.

3.2.6 Supporto Software.

La ditta Orsys fornisce con la C6713Compact un pacchetto di software, chiamato “board library”. Esso costituisce un insieme di driver a basso livello per i componenti della scheda, permettendone un’immediata inizializzazione e facilitando la fase di programmazione.

Sono forniti anche alcuni progetti d’esempio, pronti ad essere utilizzati tramite Code Composer Studio.

Tutte le definizioni necessarie per l’hardware della board sono fornite sotto forma di files C-header.

3.3 Schede di supporto

Come si era già notato in precedenza, la scheda C6713Compact non può da sola costituire l’intera Data-Processing Board. Essa ha bisogno, infatti, di almeno due schede ausiliarie: la Power Supply Board, ed una scheda di interfaccia verso la Detection Board e la membrana mobile.

Si vedrà ora una descrizione della Power Supply Board, mentre la scheda di interfaccia sarà illustrata ampiamente nel capitolo seguente.

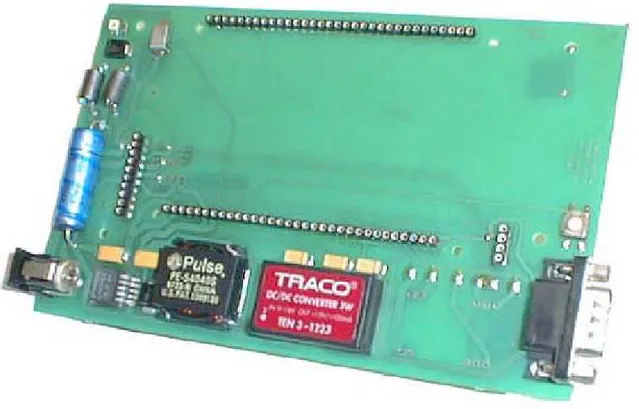

3.3.1 Power Supply Board

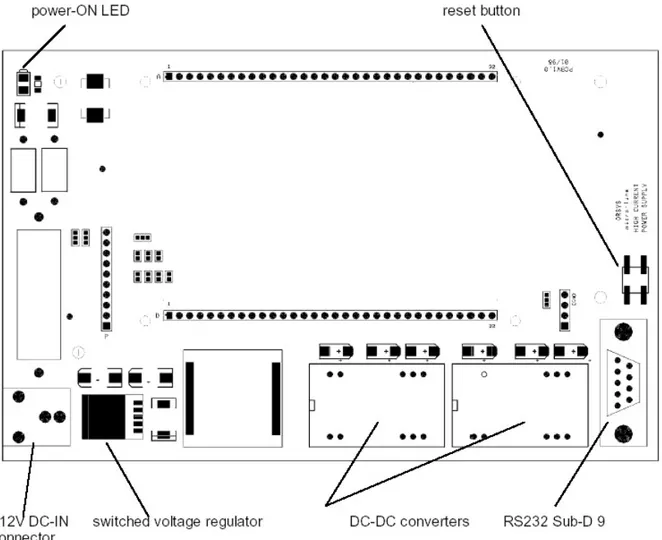

Figura 3.8: Power Supply Board

La Power Supply Board, sempre prodotta dalla ditta Orsys, è costruita in modo da potersi adattare, in maniera modulare, allo standard dei connettori micro-line, come quelli presenti sulla C6713Compact.

Essa deve provvedere a fornire alla scheda di elaborazione tutte le tensioni d’alimentazione necessarie al suo corretto funzionamento.

L’alimentazione della Power Supply Board avviene partendo dalla normale tensione di rete (230V, 50Hz), attraverso un adattatore AC/DC universale con al massimo, in uscita, 12V DC e 9.6VA. A partire da tale tensione continua vengono poi prodotti, tramite un regolatore di tensione switching, i +5V necessari alla C6713Compact. La corrente massima erogabile dall’uscita a 5V è 2.5A, molto superiore a quella richiesta dalla sola C6713Compact; del resto la Power Supply è stata pensata proprio come scheda di alimentazione per più board impilate modularmente, tramite il connettore standard micro-line. Nel caso della Data-Processing Board del progetto SPADA, tale sovrabbondanza di corrente disponibile potrà essere usata per alimentare gran parte dei dispositivi della scheda di interfaccia.

Vi è poi, a valle del regolatore che fornisce i +5V, un convertitore DC/DC che fornisce le tensioni +15V e -15V, necessarie agli integrati Physical Layer Transceiver per la comunicazione IEEE1394.

Come funzioni aggiuntive, sulla Power Supply Board sono previste: • Un bottone di reset

• Un LED di power-on

• Un connettore RS-232 SUB-D 9, collegato ad adeguati pin del connettore micro-line, che permette la comunicazione seriale con la scheda C6713Compact.

• Componenti per la protezione da interferenze elettro-magnetiche.

Le dimensioni della Power Supply Board, maggiori di quelle della C6713Compact, sono 160mm x 120mm.

3.4 Schemi a blocchi delle applicazioni e Partizionamento

Avendo a questo punto scelto la piattaforma di sviluppo del sistema, si può procedere alla fase di partizionamento del progetto della Data-Processing board tra le varie risorse a disposizione.

Per fare questo, è conveniente innanzi tutto analizzare le tre applicazioni che devono essere realizzate, suddividendo ognuna di esse in una serie di blocchi elementari funzionali, che individuano ben precise operazioni da compiere. A questo punto si potranno individuare più agevolmente, ad esempio, le operazioni comuni alle tre applicazioni.

3.4.1 Schema a blocchi dell’applicazione FTI

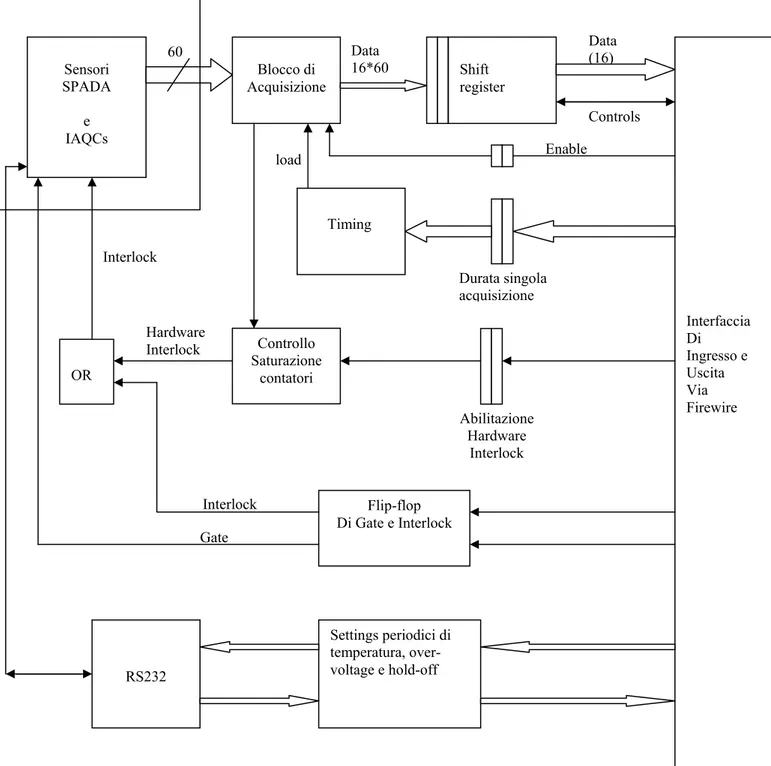

Figura 3.10: Schema a blocchi dell’applicazione FTI.

Sensori SPADA e IAQCs Blocco di Acquisizione 60 Data 16*60 Interfaccia Di Ingresso e Uscita Via Firewire Durata singola acquisizione Timing load Shift register Data (16) Controls Controllo Saturazione contatori Abilitazione Hardware Interlock Hardware Interlock Flip-flop Di Gate e Interlock Interlock OR Interlock Gate Settings periodici di temperatura, over-voltage e hold-off RS232 Enable

3.4.2 Schema a blocchi dell’applicazione AO

Figura 3.11: Schema a blocchi dell’applicazione AO.

Sensori SPADA e IAQCs Blocco di acquisizione 60 Data 16*60 Interfaccia Di Ingresso e Uscita Via Firewire Acquisizioni da integrare Shift register Controllo Saturazione contatori Abilitazione Hardware Interlock Hardware Interlock Flip-flop Di Gate e Interlock Interlock OR Interlock Gate Settings periodici di temperatura, over-voltage e hold-off RS232 Enable Elaborazione del segnale di curvatura C A, B Settings per la sinusoide (A,f,φ) Generazione dei campioni della sinusoide Parallelo Æ seriale T A S Audio Sincronizzazione Eventuale Gate-in

3.4.3 Schema a blocchi dell’applicazione LS

Figura 3.12: Schema a blocchi dell’applicazione LS.

Eventuale impostazione del numero di slot Sensori SPADA e IACQs Blocco per le 10 acquisizioni consecutive 60 Data 16*60 Interfaccia Di Ingresso e Uscita Via Firewire Timing per l’applicazione LS load Shift register Data (16) Controls Controllo Saturazione contatori Abilitazione Hardware Interlock Hardware Interlock Flip-flop Di Gate e Interlock Interlock OR Interlock Gate Settings periodici di temperatura, over-voltage e hold-off RS232 Enable Generazione dei campioni della sinusoide Parallelo Æ seriale T A S Trigger di start

3.4.4 Analisi degli schemi a blocchi

Dall’analisi degli schemi a blocchi mostrati si possono ricavare alcune informazioni utili. Si noti, ad esempio, che vi sono alcune funzionalità di base che devono essere implementate nelle tre diverse applicazioni.

Esse sono, in primo luogo, quelle riguardanti le impostazioni dirette alla Detection Board, che devono essere comunicate attraverso la porta seriale. Ovviamente, infatti, i parametri di over-voltage e hold-off time degli iAQC vanno impostati indipendentemente dallo scopo della rilevazione fotonica. Analogamente vi deve sempre essere la possibilità di controllare la temperatura del sensore SPADA.

Presente nelle tre applicazioni è naturalmente anche la batteria di 60 contatori che devono contare gli impulsi corrispondenti alle incidenze dei fotoni sui 60 rivelatori SPADA. Differente è invece il modo di sincronizzazione del conteggio: in FTI esso dipende esclusivamente dalla durata della finestra temporale impostata via software, in AO vi deve essere sincronizzazione tra la sinusoide generata e le finestre di conteggio, in LS è importante la sincronizzazione del momento partenza del conteggio con un impulso di trigger proveniente dal laser.

Anche la gestione dei segnali di Interlock e Gate software, ed il meccanismo di generazione dell’Interlock Hardware, sono comuni alle tre applicazioni.

3.4.5 Partizionamento Hardware-Software

Un primo partizionamento da effettuare è quello tra hardware - cioè scheda vera e propria - e software del computer remoto.

In effetti, negli schemi precedenti, tale ripartizione è stata implicitamente già compiuta, avendo deciso a quale livello posizionare il blocco di interfaccia Firewire, e omettendo in essi le funzionalità che saranno effettuate dal software.

Poiché si vuole poter considerare la Data-Processing board come uno strumento di misura (ad esempio, in ottica adattiva, come un sensore di curvatura), parecchie elaborazioni devono essere svolte necessariamente sulla C6713Compact. In questo modo si possono ottenere ottime prestazioni anche dal punto di vista della velocità, parametro critico del progetto; infatti, tramite FPGA o DSP, si ottengono elaborazioni in tempi molto ristretti e controllabili, a differenza di quelli che si possono avere in un host computer con un sistema operativo costretto a gestire più processi che lavorano in concorrenza.

• Controllo delle impostazioni dell’hardware • Salvataggio e visualizzazione dei dati acquisiti • Post-elaborazioni di carattere statistico o diagnostico.

3.4.6 Partizionamento C6713Compact – Scheda d’interfaccia

A costituire ciò che è stato considerato precedentemente “hardware” vi sono in realtà, come mostrato nei paragrafi precedenti, tre schede distinte. Di queste, la Power Supply board ha solo una funzione di supporto a livello di alimentazione, e di alloggio del pulsante di reset e del connettore RS-232. Quindi essa non interviene in realtà nel flusso di dati ora considerato.

Ovviamente la maggior parte delle funzioni vengono svolte dalla scheda C6713Compact, in quanto essa è facilmente programmabile via software. Tuttavia vi sono alcune funzioni, legate al mondo “analogico”, che essa non può materialmente svolgere, e che devono quindi essere implementate tramite la scheda di interfaccia. Esse sono:

• La generazione della sinusoide analogica a partire da campioni generati dalla C6713Compact

• La conversione degli impulsi di ingresso da differenziali, a +5V, ad unipolari, a 3.3V.

3.4.7 Partizionamento tra i vari dispositivi della C6713Compact

Come evidenziato nel paragrafo 3.2, sulla scheda C6713Compact sono montati numerosi dispositivi. Ve ne sono alcuni, che saranno in ogni caso utilizzati, come il sensore di temperatura della scheda, o il chipset per la comunicazione Firewire, la cui funzione è ben definita ed univoca. Altri, invece, sono strumenti più versatili, per cui vanno definite le funzioni che tramite essi saranno implementate. Essi sono: il DSP, l’FPGA e la memoria on-board.

Poiché vi sono tre differenti applicazioni da implementare, la cosa che appare più conveniente è dedicare l’FPGA a quelle funzioni, soprattutto legate all’acquisizione e al conteggio degli impulsi in arrivo, comuni alle tre applicazioni:

• Acquisizione degli impulsi in arrivo dalla Detection Board e loro conteggio • Gestione dell’Interlock hardware in modalità “safety”

• Gestione della comunicazione seriale RS-232, per le impostazioni e le letture di Temperatura, Over-Voltage e Hold-Off Time degli iAQC.

Alcune di tali funzioni non potrebbero comunque essere eseguite da altro dispositivo.

Appare al contrario più semplice e conveniente, in termini di utilizzo di risorse, lasciare al DSP le elaborazioni di carattere più matematico, variabili da caso a caso, ma che devono comunque essere eseguite “real-time”:

• Generazione dei campioni della sinusoide

• Serializzazione di tali campioni, tramite l’interfaccia McASP0 • Elaborazione del segnale di curvatura

La memoria esterna, SDRAM o Flash, sarà utile invece come coda d’uscita dei dati verso il computer remoto. Infatti quest’ultimo, in linea di principio, essendo gestito da un sistema operativo con più processi concorrenti in esecuzione, non può assicurare troppa costanza nella velocità di acquisizione dei dati. E’ quindi utile la disponibilità di una memoria in cui creare una coda FIFO d’uscita, capace di riempirsi nei momenti in cui l’host non sia disponibile a ricevere i dati, in modo che questi non vadano perduti. Una memoria in cui salvare i dati è anzi strettamente necessaria nell’applicazione di Layer Sensing, in cui l’accumulo di dati avviene molto velocemente e poi è successivamente scaricato sul computer remoto. In tale applicazione non vi è, infatti, la necessità (né a volte la possibilità) di comunicare real-time i dati acquisiti.