INDICE

INTRODUZIONE III CAPITOLO 1 1 LE TECNICHE DI TRASMISSIONE 1 1.1CARATTERISTICHEGENERALI 1 1.2TRASMISSIONESERIALE 2 1.2.1 EIA-RS232 4 1.2.2 EIA-RS422 / EIA-RS485 6 CAPITOLO 2 7PROGETTO DELLA SCHEDA DI CONTROLLO E PCB 7

2.1SPECIFICHEDIPROGETTO 7

2.2BREVEDESCRIZIONEDELLASCHEDADICONTROLLO 8

2.3FASIDIPROGETTO 11 2.4SCHEMATICIDIPROGETTO 13 2.5PCBDELLASCHEDA 21 CAPITOLO 3 29 PROGRAMMAZIONE IN VHDL DELL’FPGA 29 3.1 INTRODUZIONE 29

3.2FASEDIMONITORAGGIOEACCESSOALLAMEMORIARAM 32

3.3.ACCESSOALLAMEMORIAFLASH 38

3.4SCRITTURA,LETTURACANCELLAZIONEDELLAFLASH 38

3.5FASEDISETTING 49

CAPITOLO 4 98

SIMULAZIONE VHDL 98

4.1INTRODUZIONE 98

4.2 CICLODISCRITTURANELLAFLASH 98

4.3 CICLODILETTURADELLAFLASH 100

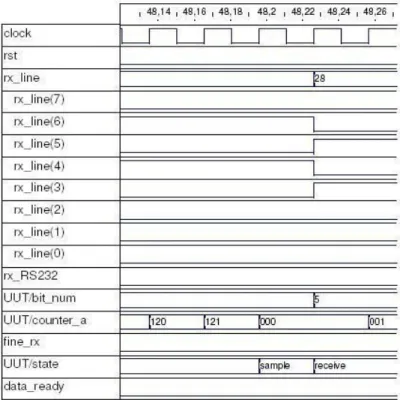

4.4 FUNZIONAMENTODELL’INTERFACCIACONL’RS232 102

4.4.1 RICEZIONE 102

4.4.2 TRASMISSIONE 104

CAPITOLO 5 107

5.2 SCELTADIPROGETTO 114

5.3PROGRAMMAZIONEDELL’UART 116

CONCLUSIONI 123

INTRODUZIONE

La tesi è stata realizzata con la collaborazione tra il Dipartimento dell’Informazione dell’Università degli Studi di Pisa e la Caen Aerospace s.r.l. di Viareggio.

Relatore interno è il professore Luca Fanucci, relatore esterno è l’ingegnere Lorenzo Fontani.

Gli obiettivi che ci si propone sono : programmare la Cyclone FPGA (in linguaggio VHDL) ed il processore 80C52 (in linguaggio C) presenti nella scheda di controllo per propulsore ionico ad effetto Hall progettata nel mio precedente lavoro di tesi per la laurea triennale e progettare il PCB della scheda stessa.

La scheda trasmette e riceve i comandi via seriale RS422/485 e fornisce il controllo delle correnti e tensioni che andranno ad alimentare il propulsore SPT.

Lo spazio sarà il luogo dove la scheda troverà il suo impiego e quindi, come si spiegherà in dettaglio all’interno della tesi, è necessario l’uso di componenti rad-hard nel progetto.

I suddetti componenti hanno la caratteristica di essere robusti alla esposizione alle radiazioni presenti nello spazio, ma a causa dei costi elevati dei componenti rad-hard, in via prototipale si realizza una scheda con componenti ad uso commerciale.

Ciascun componente commerciale viene scelto a partire dal componente rad-hard corrispondente in modo che abbia caratteristiche confrontabili rispetto a quest’ultimo.

Il lavoro è strutturato in cinque capitoli :

il primo analizza le tecniche di trasmissione tra dispositivi digitali;

il secondo presenta il progetto del PCB della scheda, mostrando i suoi 6 layer e la serigrafia, a partire da un riassunto degli obiettivi e di alcune caratteristiche principali del progetto della scheda di controllo già trattati nella tesi triennale;

il terzo descrive la programmazione in VHDL della Cyclone FPGA;

il quarto simula il comportamento dell’FPGA in risposta agli stimoli provenienti dai componenti della scheda con i quali si interfaccia;

il quinto descrive la struttura interna dei registri e delle memorie dell’80C52 ed il programma in linguaggio C.

A ciò segue la bibliografia che riporta le fonti usate per la stesura del lavoro di tesi. Si riportano di seguito dei brevi riassunti di ciascun capitolo.

CAPITOLO 1 : LE TECNICHE DI TRASMISSIONE

Si descrivono brevemente le principali caratteristiche della trasmissione parallela e di quella seriale.

Riguardo alla trasmissione seriale si introduce il caso sincrono e quello asincrono e, di seguito, si descrivono gli standard di trasmissione RS232, l’RS422, l’RS485 ed i rispettivi connettori di interfaccia.

CAPITOLO 2 : PROGETTO DELLA SCHEDA DI CONTROLLO E PCB

Si parte col riassumere le caratteristiche principali del progetto della scheda di controllo per propulsore ad effetto Hall e col presentare gli schemi elettrici del progetto realizzati con lo schematic entry Innoveda, già esposti nel precedente lavoro di tesi triennale.

A ciò segue il progetto del PCB della scheda realizzato con P-CAD 2006.

CAPITOLO 3 : PROGRAMMAZIONE IN VHDL DELL’FPGA

In questo capitolo si affronta la programmazione in VHDL del componente programmabile Cyclone FPGA.

Si parte da una breve descrizione della struttura di un programma VHDL e da un’analisi dei compiti che deve eseguire l’FPGA.

A ciò seguono il programma fpga_top e i suoi sottoprogrammi.

Il primo è il programma madre, che contiene nell’entity tutti i segnali di ingresso e di uscita con i quali l’FPGA si interfaccia al resto della circuiteria della scheda e che ha il compito di chiamare e di collegare tra loro dei componenti, ovvero dei sottoprogrammi che eseguono ciascuno singole azioni che, nella totalità, costituiscono la programmazione dell’intero FPGA.

CAPITOLO 4 : SIMULAZIONE DELL’FPGA

base delle scelte di programmazione fatte nel capitolo 3.

Attraverso il programma Active-HDL dell’ALDEC sono state effettuate simulazioni sulla risposta dell’FPGA agli stimoli di ingresso.

Si è scelto di simulare il ciclo di scrittura e quello di lettura della FLASH e poi la ricezione e la trasmissione dell’interfaccia con l’RS232.

CAPITOLO 5 : PROCESSORE 80C52 E UART

Si parte da una descrizione della struttura interna del processore 80C52 usato nel progetto, con maggiore attenzione all’UART integrato, che permette la lettura e la scrittura dei dati sulla porta seriale.

Si passa, quindi, alla programmazione dell’80C52, usando il compilatore ‘C’ READS51 specifico per processori della famiglia dell’8051.

Si programma il processore in modo che la scheda di controllo esegua : • la scrittura e la lettura dei “DAC”;

• la lettura dell’ADC;

• la lettura dello status di ciascun alimentatore;

Capitolo 1 : Le tecniche di trasmissione

CAPITOLO 1

LE TECNICHE DI TRASMISSIONE

1.1 CARATTERISTICHE GENERALI

La trasmissione seriale è un tipo di comunicazione tra dispositivi digitali nella quale le informazioni sono inviate una di seguito all’altra e giungono sequenzialmente al ricevente nello stesso ordine in cui le ha trasmesse il mittente.

Altro tipo di trasmissione usata è quella parallela; rispetto alla trasmissione seriale quella parallela da una parte richiede un maggior numero di fili e quindi un maggior costo e ha una minor tolleranza alle interferenze e agli errori di trasmissione, ma dall’altra ha prestazioni più alte a parità di frequenza.

Infatti nella trasmissione parallela si usano più conduttori per trasmettere simultaneamente informazioni, quindi se si vuole fare una trasmissione a n bit il cavo usato contiene almeno n conduttori separati, contro il solo conduttore necessario per la trasmissione seriale.

Accanto a questi n conduttori ci sono un cavo per la massa e cavi di controllo come quello per il clock (nel caso di trasmissione sincrona).

Normalmente, per comunicazioni a lunga distanza, si preferisce usare la trasmissione seriale, lasciando l’uso della trasmissione parallela per i casi di comunicazione locale o per la trasmissione di dati da elaboratore (es. un PC) a periferiche (es. una stampante), dato che i cavi necessari alla trasmissione parallela renderebbero non economicamente conveniente il progetto.

Capitolo 1 : Le tecniche di trasmissione

Figura 2 : trasmissione parallela di 8 bit

1.2 TRASMISSIONE SERIALE

Ci sono due tipi di trasmissione seriale : sincrona e asincrona.

Nel caso asincrono il trasmettitore ed il ricevitore sincronizzano i loro clock prima della trasmissione e li mantengono sincronizzati per tutta la durata dello scambio di informazioni.

Nessun segnale di clock viene inviato con i dati.

Ogni dato (ogni byte) è sincronizzato usando un bit di start che precede la trasmissione dell’informazione (si parte dal bit meno significativo); il clock interno al ricevitore scandisce gli istanti di campionamento (in base al bit rate impostato, la cui definizione sarà data nel seguito), a partire dall’istante di ricezione del bit di start.

La comunicazione si chiude con l’invio del bit di stop e resta in attesa fino al prossimo dato.

Il trasmettitore deve avere un clock uguale a quello del ricevitore in modo da poter comunicare tra loro.

I dati sono inviati a gruppi con cadenza regolare, secondo la precedente sincronizzazione tra trasmettitore e ricevitore.

Nel caso sincrono l’informazione viene trasmessa in modo continuo su una base di tempi condivisa dal trasmettitore e dal ricevitore, ovvero sulla base di un clock.

Capitolo 1 : Le tecniche di trasmissione

Figura 3 : trasmissione seriale sincrona

Figura 4 : trasmissione seriale asincrona

Tra i due tipi di trasmissione seriale la più vantaggiosa è quella sincrona, nel senso che tutti i bit inviati sono di informazione, mentre nel caso di trasmissine asincrona ogni byte trasmesso ha bisogno di un bit di start e di uno di stop oltre ai bit di informazione.

D’altro canto lo svantaggio della comunicazione sincrona sta nell’esigenza di inviare il clock.

Gli standard di trasmissione seriale si differenziano in base alle caratteristiche elettriche ed in base al protocollo di trasmissione dei dati.

Un protocollo è un insieme di regole che l’elemento trasmittente e quello ricevente devono rispettare per comunicare tra loro correttamente.

L’EIA (Electronics Industry Associations) ha creato degli standard di trasmissione seriale quali l’ RS232, l’RS422, l’RS485 che verranno ora analizzati.

Capitolo 1 : Le tecniche di trasmissione

1.2.1 EIA-RS232

Il link fisico dell’RS232 è di tipo single-ended o sbilanciato : la tensione dei segnali è misurata rispetto ad un riferimento comune, la massa.

La velocità della comunicazione seriale dell’RS232 va da 300 b/sec fino a 115 kb/sec. Il protocollo fisico dell’RS232 è studiato per interfacciare un terminale detto DTE (Data Terminal Equipment) quale è un Personal Computer, con un DCE (Data Comunication Equipment), quale è un modem.

Figura 5 : rappresentazione schematica di trasmissione

Si usano due segnali digitali in modalità full-duplex più altri segnali di controllo, oltre al segnale comune, la massa.

Si definisce “trasmissione full-duplex” quella trasmissione che suddivide il canale di comunicazione in due parti : il DTE e il DCE ne useranno per ciascuno una per ricevere l’altra per trasmettere.

La modalità full-duplex si contrappone a quella half-duplex, nella quale la trasmissione avviene alternativamente in un senso o nell’altro, condividendo lo stesso canale trasmissivo da parte delle due stazioni collegate.

Di conseguenza quella full-duplex permette di fatto di raddoppiare la banda passante aggregata del mezzo trasmissivo.

Il protocollo dell’ RS232 indica che si possono usare tensioni che vanno da ±5V a V

15

± , ma la tensione classica è di ±12V .

Per minimizzare la presenza di disturbi elettrici l’interfaccia elettrica ha una soglia di ±

Capitolo 1 : Le tecniche di trasmissione

Nello standard RS232 un segnale alto (+12V) rappresenta lo 0 logico ed uno basso(-12V) rappresenta l’1 logico.

Le unità di misura della velocità di trasmissione sono essenzialmente due :

1. il BAUD RATE : indica il numero di valori che vengono trasmessi in un secondo; 2. il BIT PER SECONDO (bps o b/sec) : indica quanti bit al secondo sono trasmessi lungo la linea.

Nel caso di trasmissione di simboli binari, le due cose coincidono numericamente.

Si consideri l’esempio in cui si voglia inviare un unico valore di tensione tra 0V e 7V (che costituisce l’informazione) su 3 bit (0V =000, 1V=001, 2V=010, …).

In tal caso una trasmissione a 1000 baud equivale ad una a 3000 bps.

Il connettore dell’interfaccia RS232 è costituito da vari segnali, tra i quali si hanno : • RXD (RECEIVED DATA) : il dato ricevuto è spedito su questa linea dal DCE al DTE;

• TXD (TRANSMITTED DATA) : il dato trasmesso è spedito su questa linea dal DTE al DCE;

• RTS (REQUEST TO SEND) : segnale pilotato dal DTE per chiedere al DCE di spedire dati o di non spedirne;

• CTS (CLEAR TO SEND) : segnale pilotato dal DCE per comunicare al DTE se è pronta a trasmettere dati o meno;

• GND (GROUND) : comune dell’alimentazione.

Capitolo 1 : Le tecniche di trasmissione

1.2.2 EIA-RS422 / EIA-RS485

Nel caso di RS422 il link fisico invece usa due conduttori per i dati ed è di tipo differenziale bilanciata.

Ciò vuol dire che la variazione di stato del dato è determinata dalla differenza delle tensioni sui due fili in modo bilanciato (da 0 a +5V e -5V sui due conduttori

rispettivamente).

Entrambi i fili sono arrotolati tra di loro con un passo ben preciso e devono seguire lo stesso percorso, quindi un rumore elettrico o disturbo, ripercuotendosi su entrambi i conduttori, non altera la tensione relativa tra loro.

Conseguenza di ciò è un’alta immunità ai disturbi, non presente nel caso dello standard RS232, e la possibilità di trasmissione su una maggiore distanza.

L’esigenza di connettere più apparecchiature in cascata con minimo rumore ha generato lo standard EIA-RS485 in cui la parte trasmittente, se non sollecitata a trasmettere, si presenta sul supporto trasmissivo in alta impedenza.

Il connettore dell’interfaccia RS422 è costituito da vari pin di segnale, tra i quali si hanno:

• RXD+,- (DIFFERENTIAL RECEIVED DATA) : il dato ricevuto (differenziale) è spedito su questa linea dal DCE al DTE;

• TXD+,- (DIFFERENTIAL TRANSMITTED DATA) : il dato trasmesso (differenziale) è spedito su questa linea dal DTE al DCE;

• RTS+,- (DIFFERENTIAL REQUEST TO SEND) : segnale pilotato dal DTE per richiedere al DcE di spedire dati o di non spedirne;

• CTS+,- (DIFFERENTIAL CLEAR TO SEND) : segnale differenziale pilotato dal DCE per comunicare al DTE se è pronta a trasmettere dati o meno;

• GND (GROUND) : comune dell’alimentazione.

Il connettore dell’interfaccia RS485 è costituito da vari pin di segnale, tra i quali si hanno:

• A+,B- (DIFFERENTIAL RECEIVE-TRASMIT DATA) : segnale differenziale di ricezione e trasmissione (half-duplex);

Capitolo 2 : Progetto della scheda di controllo e PCB

CAPITOLO 2

PROGETTO DELLA SCHEDA DI CONTROLLO E PCB

2.1 SPECIFICHE DI PROGETTO

La tesi parte da un lavoro di progetto, realizzato per la tesi triennale, il cui oggetto è la progettazione di una scheda di controllo delle grandezze elettriche (corrente e tensione) caratteristiche di un propulsore ionico ad effetto Hall SPT (Stationary Plasma Thruster).

La scheda di controllo è realizzata per applicazioni spaziali, quindi al suo interno devono essere usati componenti rad-hard, caratterizzati da una massima total dose dell’ordine di 100krad, in modo da essere robusti alle radiazioni e da specifiche adatte al progetto.

La ricerca dei componenti rad-hard è stata realizzata tra i dispositivi forniti da MIL-STD-975 NASA e da ESA-PSS-01-603.

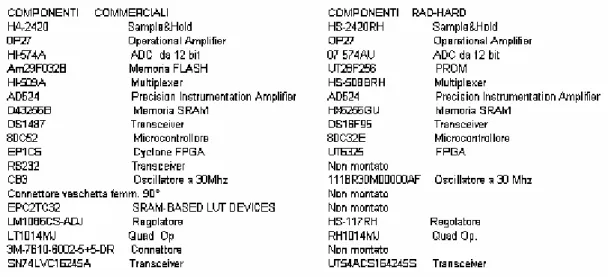

Tabella 1 : componenti rad-hard e corrispettivi componenti commerciali

A causa degli alti costi di tali componenti si usano, per il prototipo, componenti commerciali che abbiano caratteristiche simili a quelli rad-hard.

Capitolo 2 : Progetto della scheda di controllo e PCB

Infatti l’ordine di grandezza del costo di un componente rad-hard si ottiene moltiplicando il prezzo del relativo componente commerciale per un fattore di 10 per resistenze e 2 condensatori, di 10 per memorie e di 3 10 per integrati quali FPGA e microcontrollori. 4

In tabella 1 vengono riportati i componenti rad-hard e a fianco i corrispettivi componenti commerciali usati nel progetto.

La scheda riceve in ingresso le tensioni, generate da degli alimentatori, proporzionali alle grandezze elettriche che alimentano il motore del propulsore.

Il propulsore ha una struttura interna costituita da quattro elementi essenziali : un acceleratore, due elettromagneti ed un riscaldatore e le grandezze che la scheda riceve dagli alimentatori sono la corrente e la tensione relative all’acceleratore e la sola corrente degli elettromagneti e del riscaldatore.

Le specifiche di progetto sono un acceleratore configurabile tra 200 V e 300 V e controllato in corrente fino a 1.1 A, un riscaldatore controllato in corrente fino a 6 A e due elettromagneti controllati fino ad una corrente di 1 A.

La scelta dei componenti di progetto è stata fatta sulla base della specifica di usare un’alimentazione di tipo digitale di 5 V e 1.5 A ed una di tipo analogico di +12 V e 400 mA e -12 V e 200 mA.

Ulteriore specifica di progetto è quella di mantenere un range di 10V per i segnali analogici in uscita alla scheda che vanno a settare gli alimentatori.

Tali grandezze analogiche costituiscono l’uscita di filtri LP che ricevono in ingresso i segnali PWM posti in uscita dell’FPGA.

I pin di I/O dell’FPGA sono alimentati con 3.3V, quindi per ottenere segnali analogici nel range detto si è fatto in modo da realizzare un’amplificazione pari a 3 attraverso i filtri LP stessi.

2.2 BREVE DESCRIZIONE DELLA SCHEDA DI CONTROLLO

La scheda è costituita da due componenti principali : il microprocessore e l’FPGA. Il processore appartiene alla famiglia dell’8051 ed è costituito da quattro porte I/O a 8 bit, da una RAM interna di 256 bytes, da uno spazio di memoria per il programma di 64

Capitolo 2 : Progetto della scheda di controllo e PCB

Lo spazio di memoria per i dati del processore è costituito, per i primi 32 kbytes dalla RAM e per gli altri 32 kbytes dai dati da convertire in analogico per la fase di setting di cui si parlerà nel paragrafo successivo (i DAC in figura 1) e per gli status e i command degli alimentatori.

Il microcontrollore si occupa della trasmissione e ricezione di comandi con l’esterno via seriale per mezzo del transceiver posto tra l’ RS422/RS485 ed il microcontrollore in modo da adattare l’uscita differenziale della seriale all’ingresso di tipo single ended del processore.

Inoltre invia all’FPGA un bus dati ed un bus di indirizzi ciascuno da 8 bit, oltre ai comandi di lettura e di scrittura rispettivamente /RD e /WR e ad altri segnali di cui parleremo nel capitolo 3.

Attraverso un oscillatore si fornisce un clock da 30Mhz sia al microcontrollore che all’FPGA.

Le memorie usate, rispettivamente, per immagazzinare i dati e per la memorizzazione del programma del processore e dell’FPGA sono, rispettivamente, una RAM e una FLASH.

In particolare si usa una FLASH da 32 Megabit (4M x 8-bit) ed una SRAM da 256 kbit (32k-word da 8 bit).

Nel progetto finale si usa una PROM al posto di una FLASH.

Tale scelta dipende dal fatto che una PROM è una memoria programmabile una sola volta e quindi non è adatta per essere usata su un prototipo che sarà, in quanto tale, oggetto di cambiamenti e test.

Capitolo 2 : Progetto della scheda di controllo e PCB 0000h SRAM (32kbytes) 7FFFh 8000h DAC1L 8001h DAC1H 8002h DAC2L 8003h DAC2H 8004h DAC3L 8005h DAC3H 8006h DAC4L 8007h DAC4H 8008h DAC5L 8009h DAC5H 800Ah status 800Bh command 800Ch FFFFh

Figura 1 : spazio di memoria per i dati del microcontrollore

L’FPGA è un dispositivo a matrice di porte programmabili sul campo (Field Programmable Gate Array) con logica interna programmabile e con connessioni programmabili.

L’FPGA usato appartiene alla famiglia delle Altera Ciclone ed in particolare è un EP1C6 PQFP (plastic quad flat pack) costituito da 240 pin, di cui 185 sono pin di I/O, da 5,980 LE, da 92,160 bit di RAM, da 2 PLL.

Capitolo 2 : Progetto della scheda di controllo e PCB

L’FPGA ha il compito di colloquiare, oltre che con il microcontrollore, con la circuiteria della scheda.

Questa è costituita :

1. dai due multiplexer che ricevono le cinque grandezze analogiche dagli alimentatori, 2. dall’amplificatore per strumentazione che abbatte l’eventuale rumore presente,

3. dal sample & hold e dal convertitore ADC, che si occupano della digitalizzazione delle grandezze analogiche da analizzare,

4. dalla memoria FLASH che contiene il programma del microcontrollore insieme a quello dell’FPGA,

5. dalla memoria SRAM, che contiene i dati.

Per il debug dell’FPGA, si usa il JTAG, che invia il programma nell’FPGA ed è lo strumento che consente di verificare il corretto funzionamento di tutti i registri dell’FPGA.

Le apparecchiature che effettuano il JTAG possono pilotare ed osservare i livelli logici dei pin di I/O dell’FPGA utilizzando un’interfaccia a 4 pin, la Test Access Port (TAP).

I tre pin TMS (Test Mode Select), TCK (Test Clock) e TDI (Test Data Input) sono gli ingressi del TAP, mentre TDO (Test Data Output) è un suo pin di uscita.

TCK è il clock che sincronizza le operazioni del TAP; TMS è il segnale che determina le transizioni di stato e viene campionato sul fronte in salita di TCK; TDI e TDO rappresentano rispettivamente l’ingresso e l’uscita seriale dei dati.

I dati in ingresso al TDI sono campionati dal fronte in salita di TCK, mentre quelli in uscita dal TDO risultano validi sul fronte in discesa di TCK.

Attraverso la linea TDI si immette il programma nell’FPGA.

2.3 FASI DI PROGETTO

Il progetto della scheda si compone di due fasi principali, quella di monitoraggio e quella di setting delle grandezze elettriche delle parti interne al propulsore.

La fase di monitoraggio consiste nella selezione di una delle cinque grandezze da controllare.

Il monitoraggio viene fatto attraverso un sistema a due multiplexer differenziali a quattro canali, di cui il primo ha in ingresso quattro delle grandezze ed il secondo ha su un ingresso la restante grandezza da controllare mentre gli altri tre ingressi sono connessi a massa in

Capitolo 2 : Progetto della scheda di controllo e PCB

modo che non siano flottanti.

La scelta di un sistema differenziale mira ad abbattere il rumore additivo.

Il comando di abilitazione di ciascun multiplexer ed i due bit che selezionano una delle grandezze di ingresso sono gestiti attraverso l’FPGA.

La grandezza selezionata, uscente dal multiplexer abilitato tramite FPGA, viene convertita in digitale dopo essere passata attraverso un amplificatore per strumentazione, che ha lo scopo di trasformare il segnale differenziale di ingresso in un unico segnale di uscita, senza amplificarlo.

La grandezza viene convertita su 12 bit e va in ingresso all’FPGA, che la memorizza in RAM.

Inoltre l’FPGA fa un controllo EDAC (Error Detection And Correction) di ciò che viene memorizzato in memoria.

Tale necessità deriva dalla possibile presenza di errori nell’informazione registrata nella memoria, causata dalla presenza di radiazioni, trovandosi nello spazio.

Quindi si affianca alla memoria una RAM EDAC con un bus dati da 5 bit, a differenza del bus dati da 8 bit dell’altra RAM.

I cinque bit detti sono quelli del codice Hamming che vengono usati per effettuare un controllo DDE-SCE (Double Detection Error – Single Correction Error)dei dati presenti in RAM in modo quindi da rivelare da uno a due errori e da poterne correggere uno.

La fase di setting consiste nella conversione da digitale ad analogico di ciascuna delle cinque grandezze lette dal microcontrollore.

Tale conversione viene fatta attraverso una modulazione PWM della grandezza; dal segnale PWM così ottenuto si preleva il valor medio, essendo quest’ultimo proporzionale al duty cycle del segnale stesso.

Il valor medio si ottiene attraverso l’uso di un filtro di Butterworth del secondo ordine tale da ottenere un’attenuazione di 70 db del segnale PWM rispetto al suo valore medio, in modo da avere un rumore inferiore a 1 mV alla frequenza del segnale PWM, che è pari a :

kHz T f PWM PWM 7.41 1 = = , dove ms T TPWM CLOCK 4095 0.135 10 30 1 ) 1 2 ( 12 6 ∗ = ∗ = − ∗ = e

n=12 è il numero di bit del segnale digitale da convertire e (212 −1)=4095 è il valore del segnale PWM con duty cycle pari al 100%.

Capitolo 2 : Progetto della scheda di controllo e PCB pari a : 1 ) ( 4 0 0 + = f f H jf

H , dove f è la pulsazione di taglio e 0

2 ) (jf0 H0 H = , ed imponendo che 70 ) ( log 20 0 = PWM jf H H

, si ottiene f0 =131.78Hz del filtro di

Butterworth utile al progetto.

A partire dagli schemi elettrici della scheda realizzati con lo schematic entry Innoveda, si è passati alla programmazione in VHDL dell’FPGA e a quella in C del processore.

Seguono gli schematici di progetto.

Capitolo 2 : Progetto della scheda di controllo e PCB

2.5 PCB DELLA SCHEDA

Il PCB è stato realizzato su 6 strati : 4 strati interni per alimentazioni e masse (pagine 18, 19, 20, 21), uno strato di top nel quale sono stati piazzati tutti i componenti della scheda (pagina 17) ed infine uno strato di bottom (pagina 22).

Le dimensioni della scheda sono 9175 mils (233,68 mm) di altezza e 6250 mils (158,75 mm) di larghezza.

Sul perimetro della scheda viene lasciata una zona di rispetto, che deve essere lasciata libera da componenti e collegamenti, il cui scopo è quello di permettere il fissaggio meccanico della scheda di controllo su elementi dissipativi del calore prodotto dalla scheda stessa.

E’ stato scelto, per il piazzamento dei componenti, di separare in due zone diverse la parte analogica e la parte digitale della scheda.

La parte analogica e la relativa zona diffusa di rame per la massa (AGND) sono state posizionate nella parte superiore destra della scheda, mentre la parte digitale e la relativa zona diffusa di rame per la massa (DGND) occupano l’area restante della scheda (si veda la pagina 18).

Il PCB è stato fatto seguendo le seguenti scelte :

via di larghezza pari a 30 mils, piste di larghezza minima pari a 8 mils, un isolamento minimo tra pad e piste pari a 8 mils ed un isolamento, negli strati interni, tra griglia di diffusione in rame e pad non collegati alla griglia di 12 mils.

Capitolo 3 : Programmazione in VHDL dell’FPGA

CAPITOLO 3

PROGRAMMAZIONE IN VHDL DELL’FPGA

3.1 INTRODUZIONE

Questo capitolo si occupa della programmazione dell’FPGA in modo che quest’ultimo interagisca con vari componenti presenti nella scheda di controllo, oggetto della tesi, analizzando in dettaglio gli obiettivi della programmazione e le sue fasi.

Il linguaggio di programmazione usato è il VHDL, che è l’acronimo di VHSIC (Very High Speed Integrated Circuits) Hardware Description Language.

Esso serve a descrivere il funzionamento e la struttura di componenti hardware e, come tale, ha alcune caratteristiche distintive rispetto ai linguaggi software.

La principale differenza è la concorrenzialità; con questo termine si indica il fatto che diverse parti di un codice scritto in VHDL devono funzionare contemporaneamente, così come circuiti fisici possono operare in parallelo.

In genere, al contrario, in un linguaggio software, le funzioni descritte dal codice sono eseguite dall’alto verso il basso, riga dopo riga.

Un programma VHDL può essere visto, a livello schematico, come un blocco con dei segnali di ingresso e di uscita; questi ultimi variano a seconda del valore degli ingressi, seguendo la struttura funzionale del programma stesso.

Il simulatore del linguaggio VHDL lavora event-driven, nel senso che ogni volta che cambia un valore di un segnale interno del codice vengono attivati tutti i blocchi (in cui opera tale segnale) in modo concorrente.

La struttura di un file VHDL è la seguente:

Capitolo 3 : Programmazione in VHDL dell’FPGA

library ieee;

use ieee.std_logic_1164.all

2. entity : dove viene dichiarato il nome del programma con ingressi, uscite ed eventuali inout (ingresso/uscita);

3. architecture : dove viene dichiarata l’architettura del programma con i segnali usati e con la descrizione funzionale del programma e la sua temporizzazione.

La libreria IEEE con il package std_logic_1164 dà accesso al tipo std_logic, il quale descrive tutti i possibili valori di un segnale digitale a 1 bit (0, 1, Z) ed al tipo std_logic_vector (nbit-1 downto 0) che definisce un bus di segnali da nbit.

Gli ingressi, le uscite e gli inout dell’FPGA sono rappresentati in fig. 1 (dove non si è considerata la presenza dei transceiver per semplicità di disegno) .

Figura 1 : schema dell’interfaccia dell’FPGA verso gli altri componenti della scheda

Capitolo 3 : Programmazione in VHDL dell’FPGA

1. eseguire la fase di monitoraggio delle grandezze analogiche, in ingresso alla scheda, provenienti da alimentatori;

2. convertire tramite ADC le grandezze analogiche; 3. leggere e scrivere la RAM;

4. fare un controllo EDAC dei dati memorizzati nella RAM;

5. trasmettere dati verso una porta seriale, per la lettura della FLASH e riceverne, per la scrittura nella FLASH

6. eseguire la fase di setting della grandezza di controllo

Sfruttando l’alto livello di astrazione del VHDL è possibile affidare ad un programma “madre” il compito di chiamare e di collegare tra loro dei componenti, ovvero dei sottoprogrammi che eseguono ciascuno singole azioni che, nella totalità, costituiscono la programmazione dell’intero FPGA.

Il programma madre è stato dichiarato come fpga_top ed esso contiene nell’entity tutti i segnali di ingresso e di uscita con i quali l’FPGA si interfaccia al resto della circuiteria della scheda.

Nell’architecture vengono istanziati i component ed all’interno del begin dell’architecture stessa si definiscono le interconnessioni con i blocchi di programma “vicini” nel cosiddetto “port map”.

I sottoprogrammi descrivono il comportamento di circuiti combinatori quali porte logiche and, or, not o descrivono la funzione di circuiti sequenziali sincroni quali flip flop e latch o costituiscono macchine a stati sincrone con determinati compiti.

Si mostreranno, man mano che si analizzano tutte le fasi della programmazione dell’FPGA, dei diagrammi nei quali si raffigureranno i blocchi dei sottoprogrammi usati e le loro reciproche interconnessioni.

In realtà si tratta di un unico diagramma a blocchi spezzettato in più diagrammi per motivi di spazio.

Capitolo 3 : Programmazione in VHDL dell’FPGA

3.2 FASE DI MONITORAGGIO E ACCESSO ALLA MEMORIA RAM

Figura 2 : pin di ingresso/uscita della memoria RAM

La memoria RAM (si veda figura 2) effettua operazioni di lettura e di scrittura secondo la tabella di verità di figura 3.

CS# OE# WE# MODO I/O

H X X non attivo Hi-Z

L H H uscite non attive Hi-Z

L X L scrittura Din

L L H lettura Dout

Figura 3 : tabella di verità della RAM (X=don’t care)

L’accesso alla RAM viene dal microcontrollore per scrivere e leggere i dati, ma anche dall’ADC per memorizzare i suoi 12 bit in cui è contenuta la conversione in digitale delle grandezze di controllo provenienti, a monte, dagli alimentatori.

L’abilitazione della RAM avviene attraverso il livello ‘0’ di una delle sei uscite (O_int0) del programma decoder (che implementa un decoder fisico) del quale si parlerà nel paragrafo 3.5).

Si decide di dare priorità all’ADC in caso di una contemporanea richiesta di accesso da parte del microcontrollore e dell’ADC.

A tale scopo si scrive il programma “arb” che fa appunto da arbitro per i due accessi.

Esso ha in ingresso le richieste di accesso dell’ADC (req_adc_arb a ‘1’) e del microcontrollore (req_micro a ‘1’) e acconsente all’accesso del processore (ack_micro a ‘1’)

Capitolo 3 : Programmazione in VHDL dell’FPGA

(altrimenti si avrebbe in uscita ack_adc_arb a ‘1’).

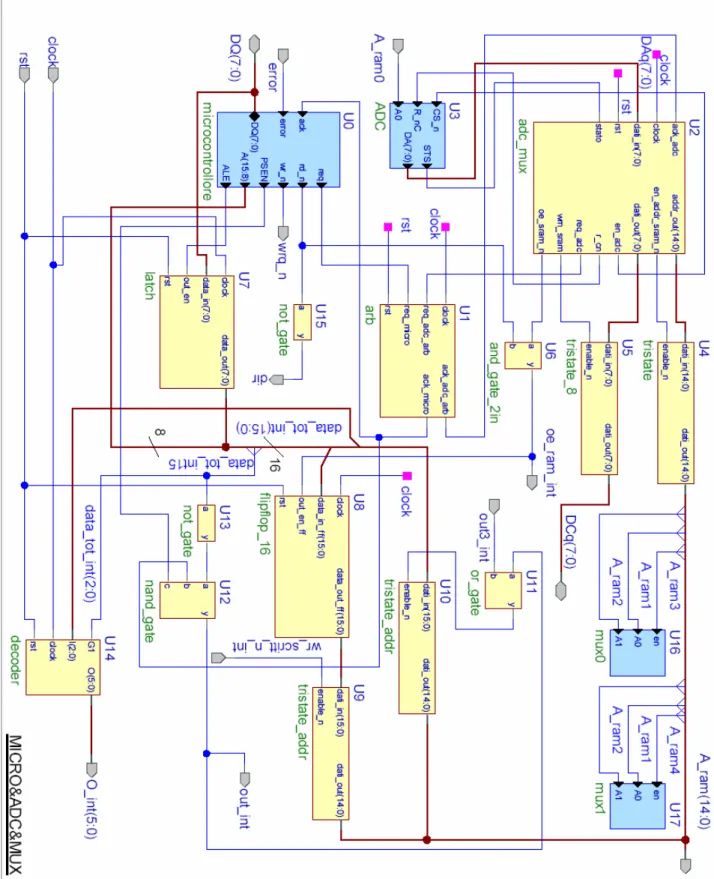

Il programma che si occupa della conversione dell’ADC delle grandezze analogiche provenienti dal suo ingresso e poi della scrittura delle grandezze convertite in memoria è adc_mux.

Quest’ultimo riceve in ingresso i dati provenienti dall’ADC, l’ack_adc_arb proveniente dall’arbitro e il pin stsq col quale l’ADC comunica se sta convertendo (stsq a ‘0’) oppure no. Le sue uscite sono i dati da scrivere nella memoria, gli indirizzi ai quali scrivere i dati nella RAM, il segnale che abilita l’ADC mettendo a ‘0’ il suo CS#, i comandi di scrittura della RAM (wrn_sram a ‘0’ e oe_sram_n a ‘0’) o di lettura della stessa (wrn_sram a ‘1’ e oe_sram_n a ‘0’).

Infine serve un tristate (tristate_addr(ADC)) che mandi gli indirizzi dell’ADC alla RAM solo quando è l’ADC a scrivere nella RAM, altrimenti ci sarebbe un conflitto tra gli indirizzi provenienti dall’ADC e quelli provenienti dal processore (si veda figura 4).

Il microcontrollore, per scrivere e leggere i dati nella RAM, deve comunicare anche i 15 bit di indirizzo delle locazioni dei dati nella memoria.

Essendo appartenente alla famiglia dell’8051, il processore ha la caratteristica di fornire gli otto bit più significativi di indirizzo e di “latchare” altri otto indirizzi attraverso un latch esterno.

Quest’ultimo riceve in ingresso il bus dati da otto bit dal microcontrollore insieme ad un latch enable, che è il piedino ale del processore stesso, e fornisce in uscita un bus di otto bit che costituisce gli otto bit meno significativi di indirizzo .

Allora si implementa, attraverso il VHDL, un latch fisico ed il programma usato per fare ciò è chiamato “latch” anche se più propriamente esso agisce come un flip flop, essendo sincrono.

I dati del microcontrollore vanno verso la memoria per la scrittura e vanno in direzione opposta durante la lettura della RAM.

Per evitare conflitti, durante la scrittura si mette in alta impedenza il bus dati del processore nella direzione in cui i dati sono degli ingressi del microcontrollore, mentre nel caso di lettura si mettono in alta impedenza nella direzione in cui sono ingressi della memoria. La schematizzazione di quanto è stato detto è in figura 4.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Figura 4 : tristate per evitare conflitti sui dati del microcontrollore

Come si vede da figura 4, il tristate che manda in uscita i dati nel caso di scrittura da parte del processore (tristate_scr) è abilitato (il suo enable è attivo basso) dal comando di scrittura (wrq_n a ‘0’) del microcontrollore.

Invece il tristate che manda in uscita i dati nel caso di lettura (tristate_lett) è abilitato dall’uscita della porta logica NAND (realizzata tramite VHDL) che ha come ingressi il negato dell’indirizzo più significativo del processore, l’uscita da arb, ack_micro, e il pin psen del microcontrollore.

Infatti psen è a ‘1’ quando il processore legge la RAM, mentre è a ‘0’ quando legge la FLASH; ack_micro è a ‘1’ quando l’arb concede al processore l’accesso alla RAM mentre a(15) è a ‘0’ quando si vuole accedere alla RAM (si veda figura 1 del capitolo 2) occupando quest’ultima i primi 32kbytes dello spazio di memoria dati del microcontrollore.

Analizziamo ora il blocco di programma corrector visto in figura 4.

Esso, insieme al programma hencoder, ha l’obiettivo di fare un controllo sui dati memorizzati nella memoria RAM attraverso un meccanismo di tipo EDAC (Error Detection And Correction); in particolare si fa in modo da rivelare fino a due errori nei dati e da correggerne uno solo ed in tal caso si parla di SCE-DDE (Single Correction Error-Double

Capitolo 3 : Programmazione in VHDL dell’FPGA

Detection Error), come è stato già visto nel capitolo 2).

Il corrector viene usato nella fase di lettura della RAM; esso riceve in ingresso sia i dati della RAM, sia quelli dell’EDAC e dà in uscita i dati corretti dell’EDAC e della RAM ed un segnale di errore che mette a ‘1’ per comunicare al processore la presenza di più di un errore che non è in grado di correggere, o a ‘0’ per comunicargli l’assenza di errore.

I dati in uscita dal corrector vengono memorizzati ciascuno in due registri da 8 e da 5 bit. La fase successiva è quella di scrittura dei dati, contenuti nei flip flop, all’interno della RAM e dell’EDAC.

Tale scrittura è abilitata dal blocco scrittura.

Questi dati o sono già in partenza corretti o sono stati corretti dal corrector nella fase di lettura.

Nella fase di scrittura, inoltre, il blocco hencoder produce, a partire dal bus dati del processore, i 5 bit del codice Hamming che saranno scritti nell’EDAC.

Per evitare conflitti sul bus dati essendo questo bidirezionale si mette un tristate tra i dati da scrivere nelle RAM e l’ingresso delle memorie; tale tristate viene attivato nel caso di scrittura da parte del microcontrollore o da parte dell’ADC.

Il programma le cui uscite comandano direttamente la scrittura o la lettura delle due RAM (comandano OE#, WE# e CS#) è “scrittura” rispettando la tabella di verità di figura 3.

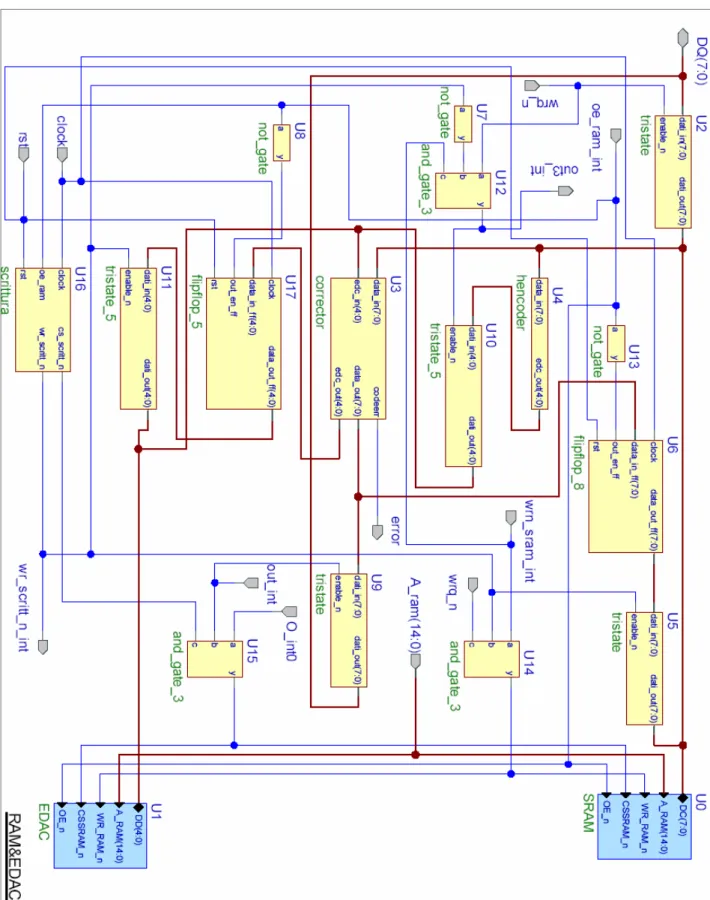

Vengono riportati in figura 5 e 6 due diagrammi in cui sono raffigurati in blocchi i programmi VHDL finora nominati.

Si passa a descrivere come viene gestito il monitoraggio, caratterizzata dal controllo della selezione di una delle cinque grandezze, fornite in uscita dagli alimentatori e caratteristiche delle parti interne del propulsore.

In tale fase due multiplexer differenziali ricevono in ingresso un comando di abilitazione (“en” di figura 6) che attiva o meno il componente a seconda che detto comando abbia un valore logico alto o basso; inoltre ricevono due bit (A0 e A1 di figura 6) che selezionano una delle grandezze di ingresso e la mandano in uscita.

L’abilitazione dei multiplexer e la gestione della scelta della grandezza da controllare vengono eseguite attraverso gli indirizzi meno significativi provenienti dall’FPGA e destinati alle RAM.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Capitolo 3 : Programmazione in VHDL dell’FPGA

Figura 6 : accesso alla RAM dal processore e dall’ADC e selezione della grandezza di controllo tramite multiplexer

Capitolo 3 : Programmazione in VHDL dell’FPGA

3.3. ACCESSO ALLA MEMORIA FLASH

Obiettivi di questa fase di programmazione sono : 1. scrivere il programma del micro nella FLASH; 2. leggere dalla FLASH;

3. cancellare la FLASH.

3.4 SCRITTURA, LETTURA CANCELLAZIONE DELLA FLASH

Il blocco contr_seriale manda all’FPGA un byte; quest’ultimo arriva alla FLASH per essere in essa scritto.

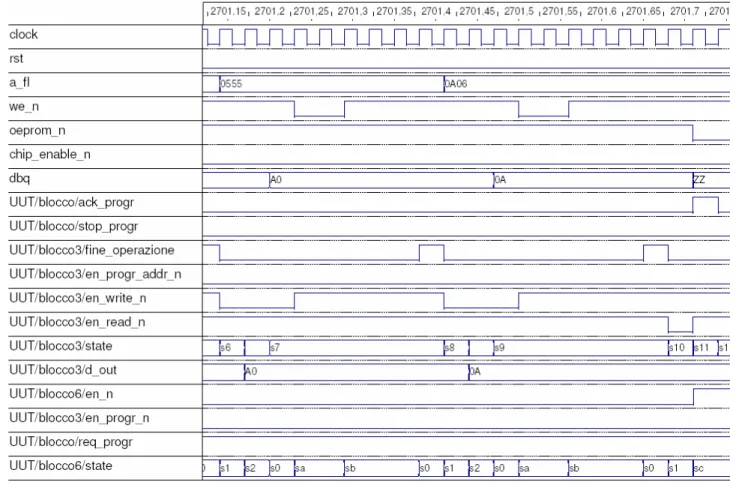

Il protocollo di trasmissione della seriale usato è il seguente : il primo byte trasmesso comunica alla memoria il comando di scrittura o quello di lettura o quello di chip-erase, a seconda che le venga trasmesso, rispettivamente, il numero 10, 20 o 30.

Nel caso in cui si voglia scrivere nella memoria si mandano, in due byte consecutivi, 16 bit in cui è contenuto il numero di byte di programma che si decide di memorizzare nella FLASH e a questi seguono i byte del programma effettivo.

Se si vuole leggere dalla FLASH si manda il numero di byte che si intende leggere, mentre se si vuole cancellare l’intera memoria è sufficiente mandare il comando 30 di chip-erase.

Per interfacciarsi alla RS232 si usano due programmi VHDL : uno, dichiarato come contr_seriale, usato per ricevere dati dalla porta seriale da inviare verso l’FPGA, e un altro, detto seriale_tx, che invia all’RS232 i dati proveniente dall’FPGA.

Seriale_tx è una macchina a stati sincrona; essa riceve in ingresso dall’FPGA il byte dei dati da trasmettere (tx_line) e un bit (tx_start) che comanda, al blocco seriale_tx, di iniziare la trasmissione.

Le sue uscite sono il bit (tx_rs232) da trasmettere all’RS232 ed un bit (tx_end) con il quale comunica, al blocco di programma chiamato blocco_a al quale è collegato (del quale si parlerà in seguito), la fine della trasmissione del dato.

Contr_seriale è anche essa una macchina a stati sincrona.

Il suo unico ingresso è il bit rx_rs232 di dato scambiato tra l’RS232 e l’FPGA, mentre le sue uscite sono il byte di dato rx_line che va in ingresso al suddetto blocco_a e che deve

Capitolo 3 : Programmazione in VHDL dell’FPGA

raggiungere la FLASH, il bit data_ready che comunica all’RS232 sel’FPGA è pronto a ricevere o meno ed infine il bit fine_rx che comunica al blocco_a la fine o meno della ricezione del dato.

In figura 7 viene riportato un diagramma in cui sono raffigurati in blocchi i programmi VHDL finora nominati.

Sono indicati in giallo i blocchi raffiguranti gli ingressi e le uscite dei programmi VHDL contr_seriale, seriale_tx e blocco_a e in blu è rappresentata la porta seriale RS232 fisica.

Il protocollo di comunicazione seriale vede l’inizio della trasmissione con un bit di start (0 logico), seguito dall’invio dell’informazione, ovvero degli 8 bit, dal meno significativo fino a più significativo; poi viene trasmesso un bit di stop (1 logico), che indica la fine della comunicazione.

Si lavora con un baud rate della porta seriale pari a 115,2 kbit/s; di conseguenza il tempo che ci vuole per trasmettere ogni bit è pari a 8,7 µsec, ovvero all’inverso del baud rate.

E’ importante garantire il rigoroso rispetto della durata dei singoli bit; infatti non è presente alcun segnale di clock comune a trasmettitore e ricevitore e l’unico elemento di sincronizzazione è dato dal fronte in salita del bit di start.

Il campionamento in ricezione è effettuato al centro di ciascun bit, come si è già detto nel capitolo riguardante la comunicazione seriale.

Quindi se 8,7 µsec è il tempo per ogni bit, si campiona il bit di start dopo 4,35 µsec e tale ritardo si protrae per ciascun bit fino al bit di stop.

Si usa allora un contatore che ritardi l’inizio della ricezione del byte di 4,35 µsec ed un altro che conti fino a 8 in modo che gli otto bit ricevuti siano accorpati in un unico byte.

Quindi il primo conta fino a 4,35µsec/30MHz=145, dove 30MHz è la frequenza di clock dell’FPGA, mentre il secondo conta fino a 8,7 µsec/30MHz= 290, per porsi a metà del primo bit e poi dei bit successivi.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Figura 7 : trasmissione e ricezione della porta seriale RS232 con l’FPGA.

Si nota che, per la ricezione dei dati da RS232 a FPGA, l’evento che permette il passaggio da uno stato di idle agli stati successivi è l’invio di un bit di start, dello 0 logico, mentre il comando effettivo di ricezione del byte è :

Capitolo 3 : Programmazione in VHDL dell’FPGA

“rx_line_i<= rx_RS232 & rx_line_i(6 downto 0);”

dove “&” fa un’unione del bit rx_RS232, che viene dalla porta seriale, con altri 7 bit. Il blocco contr_seriale ha in ingresso rx_RS232 che, volta per volta, è un bit del byte che costituirà l’uscita rx_line di contr_seriale stesso.

In particolare su rx_RS232 arriva da LSB a MSB del dato che deve essere scritto nella FLASH.

Finito l’invio dell’intero byte si pone il data_ready e il fine_rx a 1.

Nel programma seriale_tx si esce dallo stato di idle se seriale_tx riceve in ingresso tx_start a 1; quindi l’RS232 riceve il bit di start e dopo un ritardo di 8,7 µsec, trasmette dal bit LSB al bit MSB, per poi concludere col bit di stop.

La trasmissione del bit LSB avviene attraverso il comando: “tx_rs232_i<=tx_line(0);”

mentre quella dei restanti 7 bit attraverso: “tx_line_i<=’0’&tx_line_i(7 downto 1);” e poi successivamente con:

“tx_rs232_i<=tx_line_i(0);”

ovvero aggiungendo uno 0 in testa a tx_line facendo scorrere verso destra il bit che si vuole inviare all’RS232, analogamente ad un registro a scorrimento.

Quando seriale_tx ha finito la trasmissione del dato, lo comunica al blocco_a, mettendo tx_end a ‘1’.

Il blocco_a, a seconda che sia stato ricevuto, attraverso il blocco contr_seriale, il comando di scrittura, lettura o cancellazione della FLASH, fa un handshake rispettivamente con i blocchi flash_progr, flash_lett e flash_erase per verificare se sia possibile iniziare l’azione dettata dal comando stesso (si veda figura 13).

Infatti il blocco_a fa a tutti e tre i blocchi detti una richiesta di scrittura o di lettura o di cancellazione accertandosi che i blocchi di programma ad esso collegati siano pronti per abilitare l’azione di competenza.

Nel particolare al blocco flash_progr manda in ingresso i dati da scrivere in memoria, gli indirizzi (inviati in due volte essendo a 16 bit) ai quali scrivere, e il comando di fine scrittura attraverso il bit stop_progr a livello alto; al blocco flash_lett manda il bit stop_lett che, quando è a livello alto, comunica la volontà di far finire la lettura della memoria.

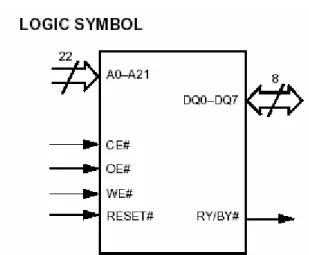

Prima di descrivere in dettaglio i vari blocchi di programma usati per accedere alla memoria FLASH, si fa una descrizione della struttura interna della memoria e dei comandi che permettono la scrittura, la lettura e la cancellazione della stessa.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Gli ingressi/uscite della FLASH sono raffigurate in fig.8 :

Figura 8 : simbolo della memoria FLASH

Le operazioni del bus del dispositivo sono inizializzate attraverso il command register interno alla memoria; questo registro ha al suo interno dei latch che immagazzinano i comandi insieme all’informazione sull’indirizzo e sul dato necessaria ad eseguire il comando.

I contenuti del registro servono come input per la macchina a stati interna alla memoria; le uscite della macchina a stati determinano la funzione del dispositivo.

Si riportano, in tabella 1, gli ingressi, i livelli richiesti e le uscite risultanti che permettono le operazioni di scrittura e di lettura della memoria :

Tabella 1 : valori degli ingressi e delle uscite per le operazioni di lettura e scrittura

CE# è il chip-enable del dispositivo, mentre OE# è il controllo dell’uscita e porta i dati ai pin di uscita; WE# è il write-enable.

L’operazione di cancellazione della memoria vede CE#, OE#, WE# allo stesso livello del caso della scrittura.

La macchina a stati interna è settata per leggere i dati all’accensione del dispositivo; ciò garantisce che nessuna alterazione spuria del contenuto della memoria si abbia durante il transitorio di accensione.

Nessun comando è necessario in tale modalità per leggere i dati e la memoria resta abilitata per l’accesso alla lettura finchè i contenuti del command register non sono cambiati.

Operazione CE# OE# WE# A0-A21 DQ0-DQ7 Lettura L L H AIN DOUT

Capitolo 3 : Programmazione in VHDL dell’FPGA

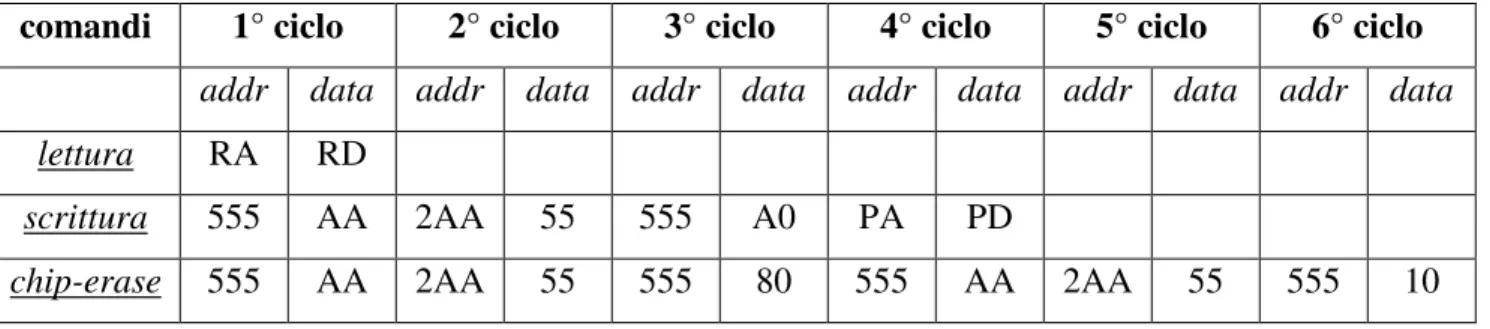

cancellazione dell’intera memoria sono riportate nella tabella 2, dove : RA=indirizzo della memoria che si vuole leggere;

RD=il dato da leggere all’indirizzo RA; PA=l’indirizzo di memoria in cui scrivere;

PD=il dato da dover essere scritto alla locazione PA.

comandi 1° ciclo 2° ciclo 3° ciclo 4° ciclo 5° ciclo 6° ciclo

addr data addr data addr data addr data addr data addr data lettura RA RD

scrittura 555 AA 2AA 55 555 A0 PA PD

chip-erase 555 AA 2AA 55 555 80 555 AA 2AA 55 555 10

Tabella 2: sequenza di comandi per lettura, scrittura e cancellazione della memoria

Se si scrive un indirizzo o il valore di un dato non corretti o scrivendoli in una sequenza non corretta la memoria ritorna in modalità di lettura.

La programmazione consiste in un’operazione di 4 cicli.

La sequenza del comando di scrittura è inizializzata scrivendo due cicli di scrittura in apertura, seguiti da un comando di set-up del programma.

A ciò seguono l’indirizzo a cui scrivere ed il dato da scrivere.

Il diagramma di flusso dell’operazione di scrittura è raffigurato in figura 9a e la sua temporizzazione in figura 9b, dove twp=50ns (WE# a ‘0’), twph=20ns (WE# a ‘1’), twc=150ns (tempo di scrittura).

Il blocco di programma che si occupa della sequenza di programmazione e delle fasi contenute nel diagramma di flusso di figura 9a è il flash_progr, mentre la temporizzazione della scrittura viene trattata nel programma VHDL blocco_a.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Figura 9a : operazione di programmazione

Figura 9b:temporizzazione dell’operazione di programmazione

Il sistema determina lo stato dell’operazione di scrittura (e si vedrà in seguito che ciò vale anche nel caso di chip-erase) usando DQ7 all’interno dell’ algoritmo del Data Polling il cui

Capitolo 3 : Programmazione in VHDL dell’FPGA

Il Data Polling è valido dopo il fronte in salita dell’ultimo impulso di WE# nella sequenza di programma (e lo stesso vale, come si vedrà in seguito, per il caso di cancellazione).

Figura 10 : Data Polling

Infatti, durante l’algoritmo di programmazione, la memoria fa uscire su DQ7 il complemento (DQ7 negato) del dato programmato per DQ7.

Quando l’algoritmo di scrittura è completo il dispositivo fa uscire il dato programmato per DQ7.

Quanto ora detto è raffigurato in fig. 11 :

Figura 11 : temporizzazione del Data Polling.

Il data polling è trattato nel blocco flash_progr (che è attivato dal blocco_a) e consiste in una lettura di durata trc=150ns con OE# e CE# a ‘0’, WE# a ‘1’.

Capitolo 3 : Programmazione in VHDL dell’FPGA

La cancellazione è analoga alla scrittura per quanto riguarda i livelli assunti dagli ingressi della FLASH, volendo CE# e WE# a ‘0’ e OE# a ‘1’, ma è diversa dalla scrittura per quanto riguarda la sequenza di comandi (si veda la tabella 2).

Infatti la cancellazione prevede 6 cicli di comandi; il chip-erase è inizializzato attraverso la scrittura di due cicli in apertura, seguiti da un comando di set-up.

Due cicli di scrittura in apertura aggiuntivi sono poi seguiti da un comando di chip erase che invoca l’algoritmo di cancellazione.

L’algoritmo di cancellazione automaticamente preprogramma e verifica la memoria interna in modo che si abbia un pattern di tutti ‘0’.

La rappresentazione in diagramma di flusso dell’operazione di cancellazione dell’intera memoria è riportata in figura 12.

Figura 12: diagramma di flusso dell’operazione di cancellazione della FLASH

La temporizzazione del chip-erase è analoga a quella della scrittura.

Come nel caso di scrittura, anche nella cancellazione si ha il data polling, successivo alla sequenza di comandi .

L’unica differenza sta nel tipo di controllo fatto su DQ7; infatti durante l’algoritmo di cancellazione la FLASH produce uno 0 su DQ7, mentre quando l’algoritmo è finito produce un 1 su DQ7.

Capitolo 3 : Programmazione in VHDL dell’FPGA

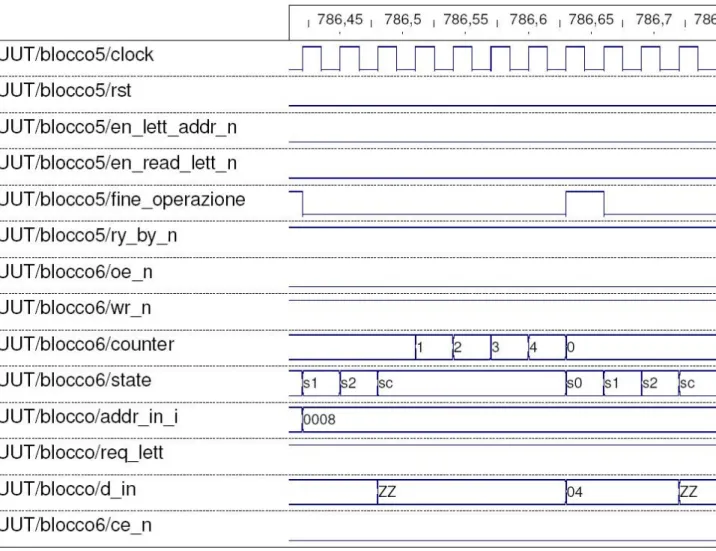

Nel caso della lettura basta dare agli ingressi i valori indicati nella tabella 1 .

Il programma lett_scritt è quello che effettivamente comanda con le sue uscite gli ingressi WE#, CE# OE# della FLASH e abilita alla lettura o alla scrittura a seconda che sia comandato da flash_lett o da flash_progr.

Il programma mux_dati serve a mettere in Hi-Z i dati in uscita da flash_progr quando è flash_erase ad essere stato attivato dal blocco_a (e quindi sono di interesse i dati in uscita da flash_erase) e viceversa.

In uscita dalla memoria FLASH si ha il segnale ry/by (ready/busy); quando assume il valore 0 indica che la memoria sta cancellando o programmando in modo attivo, altrimenti è pronta a leggere i dati.

Quindi si manda tale segnale in ingresso ai blocchi flash_progr, flash_erase e flash_lett in modo che sappiano quando attivare o meno l’operazione specifica che viene loro richiesta dal blocco_a.

La struttura dei blocchi ora nominati e dei reciproci collegamenti è riportata in figura 13. Si nota la presenza di blocchi tristate; questi, una volta abilitati, mettono in uscita il bus dati che trovano in ingresso.

In assenza dei tristate i dati e gli indirizzi della FLASH sarebbero condivisi da più blocchi di programma creando delle situazioni di conflitto.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Capitolo 3 : Programmazione in VHDL dell’FPGA

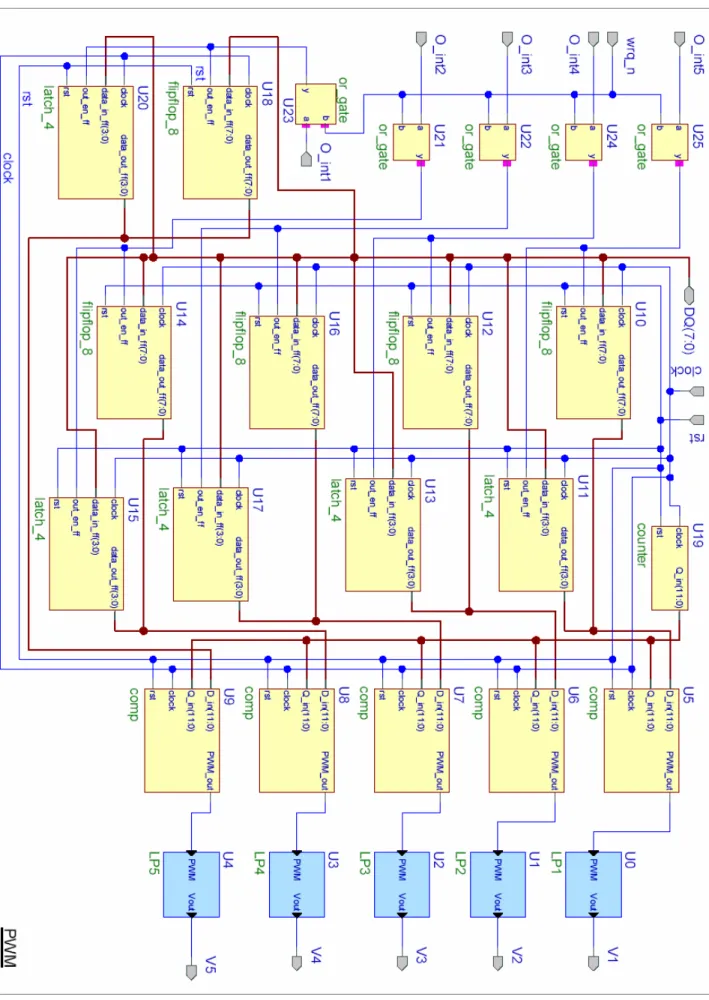

3.5 FASE DI SETTING

Il fine è quello di produrre in uscita dalla scheda di controllo delle tensioni proporzionali alle cinque grandezze analogiche caratteristiche del motore del propulsore; tali tensioni saranno portate all’ingresso degli alimentatori per il set delle loro tensioni e correnti di uscita.

A tale scopo si fa una conversione da digitale ad analogico delle cinque grandezze elettriche di interesse, prelevandole dal bus dati del microcontrollore.

Ciascuna delle sei grandezze digitali viene scritta su 12 bit.

Per prelevare ognuna di esse si fa una doppia lettura dei dati del microcontrollore, memorizzando i primi 8 bit e successivamente gli ultimi 4 bit in due registri e poi unendo in 12 bit i dati memorizzati.

Quindi si passa a fare una conversione da digitale ad analogico, modulando i 12 bit per avere un segnale PWM (pulse width modulation).

Dal PWM si preleva facilmente il valore medio, essendo quest’ultimo proporzionale al duty cycle secondo la relazione:

δ

K VM =

dove VM è il valore medio del segnale PWM, k è l’ampiezza massima del segnale PWM

e δ è il duty cycle del segnale stesso.

Il valor medio costituisce la tensione che va a settare ciascun alimentatore.

Per poter scegliere in quale DAC scrivere il dato si usa il programma decoder già nominato per l’abilitazione della RAM (si veda paragrafo 3.2).

Come già detto esso ha, in corrispondenza del suo segnale di enable, l’indirizzo più significativo del microcontrollore che è a ‘1’ quando si vuole accedere nella seconda metà dei 64kbytes dello spazio di memoria dei dati del processore, ovvero nella zona destinata ai “DAC” (si veda figura 1 del capitolo 2).

Il decoder è programmato in modo che quando A15 è a ‘0’ abilita, indipendentemente dagli altri ingressi, l’uscita O_int(0), mentre quando è a ‘1’ abilita una delle altre cinque uscite, O_int(1), O_int(2), O_int(3), O_int(4), O_int(5), a seconda del valore dei tre indirizzi meno significativi del microcontrollore.

Queste ultime 5 uscite vanno ciascuna in ingresso ad un or logico il cui secondo ingresso è il comando di scrittura del microcontrollore, wrq_n.

Capitolo 3 : Programmazione in VHDL dell’FPGA

L’uscita di questo or logico costituisce l’abilitazione dei due registri in cui abbiamo detto vengono memorizzati i 12 bit della grandezza da convertire.

Il segnale PWM viene realizzato mandando i 12 bit ad un programma “comparatore” che confronta i 12 bit con l’uscita di un programma “contatore” che implementa un contatore fisico a 12 bit.

Il contatore ed il comparatore sono sincroni .

Il comparatore è strutturato in modo che, finchè il valore contato dal contatore è minore o uguale rispetto al valore dei 12 bit derivanti dall’unione dei valori memorizzati nei flip flop, la sua uscita dia ‘1’ altrimenti dia ‘0’.

Quindi quanto più prevale il tratto in cui l’uscita del comparatore è a livello alto, tanto maggiore è il duty cycle del segnale e tanto maggiore è il suo valore medio, ovvero il valore della grandezza convertita.

La struttura a blocchi che realizza il segnale PWM e quindi la conversione di una grandezza in analogico è mostrata in figura 14.

Capitolo 3 : Programmazione in VHDL dell’FPGA

Capitolo 3 : Programmazione in VHDL dell’FPGA

Di seguito vengono riportati i programmi in VHDL dei vari blocchi visti finora in questo capitolo.

Programma fpga_top

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity fpga_top is port(clock:in std_logic; rst_n:in std_logic;dcq:inout std_logic_vector(7 downto 0); ddq:inout std_logic_vector(4 downto 0); dbq:inout std_logic_vector(7 downto 0); dq:inout std_logic_vector(7 downto 0); daq:in std_logic_vector(7 downto 0); stsq:in std_logic; ry_byq:in std_logic; req_q:in std_logic; aleq:in std_logic; rdq_n:in std_logic; wrq_n:in std_logic; psen_q:in std_logic;

a:in std_logic_vector(15 downto 8); rxd232q:in std_logic;

a_ram:out std_logic_vector(14 downto 0); read_convertn:out std_logic; oe_n:out std_logic; wr_ram_n:out std_logic; cssram_n:out std_logic; pwm_out1:out std_logic; pwm_out2:out std_logic; pwm_out3:out std_logic; pwm_out4:out std_logic; pwm_out5:out std_logic; error:out std_logic; chip_enable_n:out std_logic; we_n:out std_logic;

a_fl:out std_logic_vector(15 downto 0); cs_n:out std_logic; oeprom_n:out std_logic; ack:out std_logic; rts232:out std_logic; txd232:out std_logic; dir:out std_logic ); end fpga_top;

architecture arch of fpga_top is signal rst;

signal ack_progr_int:std_logic; signal ack_erase_int:std_logic;

Capitolo 3 : Programmazione in VHDL dell’FPGA

signal rx_line_int:std_logic_vector(7 downto 0); signal fine_rx_int:std_logic;

signal tx_end_int:std_logic;

signal tx_line_int:std_logic_vector(7 downto 0); signal tx_start_int:std_logic;

signal req_progr_int:std_logic; signal req_erase_int:std_logic; signal req_lett_int:std_logic;

signal addr_in_int:std_logic_vector(15 downto 0); signal stop_progr_int:std_logic;

signal dati_in_int:std_logic_vector(7 downto 0); signal stop_lett_int:std_logic;

signal en_progr_addr_n_int:std_logic; signal en_read_n_int:std_logic; signal en_write_n_int:std_logic; signal fine_operazione_int:std_logic;

signal d_out_int:std_logic_vector(7 downto 0); signal d_out_erase_int:std_logic_vector(7 downto 0); signal en_erase_addr_n_int:std_logic;

signal addr_out_erase_int:std_logic_vector(15 downto 0); signal en_read_erase_n_int:std_logic; signal en_write_erase_n_int:std_logic; signal en_lett_addr_n_int:std_logic; signal en_read_lett_n_int:std_logic; signal en_n_int:std_logic; signal en_progr_n_int:std_logic;

signal d_out_in_int:std_logic_vector(7 downto 0); signal D_in1a_int:std_logic_vector(7 downto 0); signal D_in2a_int:std_logic_vector(3 downto 0);

signal D_in3a_int:std_logic_vector(11 downto 0); signal Q_ina_int:std_logic_vector(11 downto 0); signal out_en_ffa_int:std_logic;

signal D_in1b_int:std_logic_vector(7 downto 0); signal D_in2b_int:std_logic_vector(3 downto 0); signal D_in3b_int:std_logic_vector(11 downto 0); signal Q_inb_int:std_logic_vector(11 downto 0); signal out_en_ffb_int:std_logic;

signal D_in1c_int:std_logic_vector(7 downto 0); signal D_in2c_int:std_logic_vector(3 downto 0); signal D_in3c_int:std_logic_vector(11 downto 0); signal Q_inc_int:std_logic_vector(11 downto 0); signal out_en_ffc_int:std_logic;

signal D_in1d_int:std_logic_vector(7 downto 0); signal D_in2d_int:std_logic_vector(3 downto 0); signal D_in3d_int:std_logic_vector(11 downto 0); signal Q_ind_int:std_logic_vector(11 downto 0); signal out_en_ffd_int:std_logic;

signal D_in1e_int:std_logic_vector(7 downto 0); signal D_in2e_int:std_logic_vector(3 downto 0); signal D_in3e_int:std_logic_vector(11 downto 0); signal Q_ine_int:std_logic_vector(11 downto 0); signal out_en_ffe_int:std_logic;

signal req_adc_int:std_logic; signal ack_adc_int:std_logic;

signal edc_int:std_logic_vector(4 downto 0); signal O_int:std_logic_vector(5 downto 0);

Capitolo 3 : Programmazione in VHDL dell’FPGA

signal data_tot_int:std_logic_vector(15 downto 0); signal data_out_latch_int:std_logic_vector(7 downto 0); signal data_latch_int:std_logic_vector(7 downto 0); signal oe_ram_int:std_logic;

signal wr_scritt_n_int:std_logic; signal cs_scritt_n_int:std_logic;

signal addr_out_int:std_logic_vector(14 downto 0); signal addr_out_progr_int:std_logic_vector(15 downto 0); signal dati_out_int:std_logic_vector(7 downto 0);

signal cen_sram_int:std_logic; signal wrn_sram_int:std_logic; signal en_addr_sram_n_int:std_logic; signal oe_sram_n_int:std_logic;

signal out_latch1_int:std_logic_vector(7 downto 0); signal out_latch2_int:std_logic_vector(4 downto 0); signal out_latch3_int:std_logic_vector(15 downto 0); signal or_out_int:std_logic;

signal out3_int:std_logic;

signal edc_tristate_int:std_logic_vector(4 downto 0); signal out_int:std_logic; signal oe_ram_neg_int:std_logic; signal data_tot_neg_int:std_logic; signal wr_scritt_n_neg_int:std_logic; signal enable_a_int:std_logic; signal enable_b_int:std_logic; signal enable_c_int:std_logic; signal enable_d_int:std_logic; signal enable_e_int:std_logic; signal ack_micro_int:std_logic;

signal Q_in_int:std_logic_vector(11 downto 0);

component blocco_a port(clock:in std_logic; rst:in std_logic;

ack_progr:in std_logic; --progr ack_erase:in std_logic; --erase ack_lett:in std_logic; --lett

rx_line_a:in std_logic_vector(7 downto 0); --progr,erase,lett fine_rx_a:in std_logic; --progr,erase,lett tx_end_a:in std_logic; --lett

d_in:in std_logic_vector(7 downto 0); --lett tx_line_a:out std_logic_vector(7 downto 0); --lett tx_start_a:out std_logic; --lett req_progr:out std_logic; --progr req_erase:out std_logic; --erase req_lett:out std_logic; --lett addr_in:out std_logic_vector(15 downto 0); --progr,lett stop_progr:out std_logic; --progr dati_in:out std_logic_vector(7 downto 0); --progr stop_lett:out std_logic --lett );

end component;

component flipflop_5 port ( clock : in std_logic;

Capitolo 3 : Programmazione in VHDL dell’FPGA

data_in_ff : in std_logic_vector (4 downto 0); out_en_ff : in std_logic;

data_out_ff : out std_logic_vector(4 downto 0) );

end component;

component contr_seriale is port( clock : in std_logic; rst : in std_logic;

rx_RS232 : in std_logic; --ricezione bit a bit rx_line : out std_logic_vector (7 downto 0); data_ready: out std_logic;

fine_rx:out std_logic );

end component;

component seriale_tx port( clock : in std_logic; rst : in std_logic;

tx_start:in std_logic; tx_line : in std_logic_vector (7 downto 0); tx_RS232 : out std_logic;

tx_end: out std_logic );

end component;

component flash_progr port(clock:in std_logic; rst:in std_logic;

addr_in_wr:in std_logic_vector(15 downto 0); dati_in_wr:in std_logic_vector(7 downto 0); req_progr_wr:in std_logic;

ry_by_n:in std_logic; stop_progr_wr:in std_logic;

fine_operazione:in std_logic; d_contr:in std_logic_vector(7 downto 0); addr_out:out std_logic_vector(15 downto 0); d_out:out std_logic_vector(7 downto 0); ack_progr_wr:out std_logic; en_read_n:out std_logic; en_write_n:out std_logic; en_progr_addr_n:out std_logic; en_progr_n:out std_logic ); end component; component flash_erase port(clock:in std_logic; rst:in std_logic; req_erase_c:in std_logic; ry_by_n:in std_logic; fine_operazione:in std_logic;

d_contr_erase:in std_logic_vector(7 downto 0); addr_out_erase:out std_logic_vector(15 downto 0); d_out_erase:out std_logic_vector(7 downto 0); ack_erase_c:out std_logic;

Capitolo 3 : Programmazione in VHDL dell’FPGA en_erase_addr_n:out std_logic; en_read_erase_n:out std_logic; en_write_erase_n:out std_logic ); end component; component flash_lett port(clock:in std_logic; rst:in std_logic; req_lett_l:in std_logic; ry_by_n:in std_logic; stop_lett_l:in std_logic; fine_operazione:in std_logic; en_lett_addr_n:out std_logic; en_read_lett_n:out std_logic; ack_lett_l:out std_logic ); end component; component lett_scritt port(clock:in std_logic; rst:in std_logic; en_read_n_ls:in std_logic; en_write_n_ls:in std_logic; en_read_erase_n_ls:in std_logic; en_write_erase_n_ls:in std_logic; en_read_lett_n_ls:in std_logic; wr_n:out std_logic; oe_n:out std_logic; ce_n:out std_logic; fine_operazione_ls:out std_logic; en_n:out std_logic ); end component; component mux_dati port(clock:in std_logic; rst:in std_logic; en_progr_n_mux:in std_logic;

d_out_mux:in std_logic_vector(7 downto 0); d_out_erase_mux:in std_logic_vector(7 downto 0); d_out_in:out std_logic_vector(7 downto 0)

);

end component;

component comp port ( clock: in std_logic; rst : in std_logic;

Q_in : in std_logic_vector(11 downto 0); D_in : in std_logic_vector(11 downto 0); PWM_out: out std_logic

);

end component;