CAPITOLO 5

Progetto e realizzazione del sistema di controllo

elettronico

Prima di procedere con l’esposizione dettagliata del progetto realizzato, è necessario analizzare in maggior dettaglio i sistemi di accensione implementabili sui motori a combustione interna, al fine di giustificare alcune scelte relative alle configurazioni circuitali selezionate.

5.1 Classificazione ed analisi dei sistemi di accensione per i motori a combustione interna

5.1.1 Sistemi convenzionali di accensione induttiva

Premesso che i motori a combustione interna necessitano, in condizioni di bassa temperatura ed umidità, di una tensione di 25 kV ai capi degli elettrodi delle candele affinché abbia luogo la scarica, si può pensare ad uno schema del tipo riportato in figura 5.1:

Figura 5.1 – Schema di un sistema convenzionale di accensione induttiva

se effettuiamo l’equivalente elettrico, otteniamo lo schema di figura 5.2, dove Cs

rappresenta la capacità totale sul secondario della bobina (circa 100 pF) imputabile alla somma delle capacità dovute al distributore, alle candele, ai fili di collegamento con quelle parassite relative al secondario della bobina.

Visto che l’energia necessaria a provocare l’accensione della miscela aria-combustibile è stimabile intorno a 1mJ e dato che è necessario caricare la Cs ai succitati 25 kV, i

sistemi di accensione tradizionali operano nel seguente modo: con le puntine chiuse circola corrente nel primario, permettendo l’immagazzinamento di energia in forma magnetica, mentre con le puntine aperte si ha una variazione molto veloce del campo magnetico che comporta una tensione sul secondario. Al fine pertanto di ottenere la massima tensione di uscita, è necessario immagazzinare la massima energia magnetica sul primario della bobina, durante il periodo in cui i contatti sono chiusi; tale energia è esprimibile nella forma

Ep =

2 1

Lp (ip)2 (5.1)

con Ep energia immagazzinata nel primario, Lp induttanza del primario e ip corrente nel

primario.

Risulta chiaro come per aumentare tale energia, sia necessario aumentare sia la corrente circolante che l’induttanza dell’avvolgimento. Nei sistemi convenzionali rappresentati, la corrente non può superare i 3,5 A, pena una drastica riduzione di vita delle puntine a causa del manifestarsi di archi elettrici e conseguenti ossidazioni dei materiali. D’altronde l’induttanza del primario non può essere arbitrariamente grande, vista la sua diretta influenza sulla costante di tempo del primario che comporterebbe una diminuzione di energia immagazzinata alle alte velocità. Per un corretto dimensionamento dei parametri circuitali è quindi opportuno valutare l’energia da immagazzinare nel primario, nel seguente modo:

Ep = 2 1 Cp 2 ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ s p N N Vs2 + 2 1 Cs Vs2 (5.2)

con Cp capacità posta tra un capo del primario e massa, Np/Ns rapporto spire e Vs

tensione ai capi del secondario all’atto della scarica. Le bobine dei sistemi tradizionali sono tipicamente caratterizzate da un rapporto spire 1:100; in questo modo sulle puntine si genera una tensione di 250 V (per avere i 250 kV sul secondario) che comporta la presenza di una capacità di circa 0,22 µF, al fine di evitare la presenza di archi. Sostituendo nell’ultima espressione tutti i valori numerici precedentemente citati, si ottiene un valore di Ep pari a 38,12 mJ che rappresenta un valido riferimento teorico,

visto che nella pratica si è poi soliti assumere un valore doppio per i dimensionamenti effettivi. Un ulteriore parametro di merito di un sistema di accensione è il tempo di

salita della forma d’onda della tensione agli elettrodi della candele; in particolare, per bassi tempi di salita, si hanno sistemi in grado di accendere la miscela, anche nel caso di elettrodi imbrattati da olio o da sostanze carboniose. La motivazione di tale fatto può essere spiegata tenendo conto dell’effetto pelle dei conduttori ed osservando che le componenti ad alta frequenza sono quelle con il maggior peso, in una scomposizione secondo Fourier di una forma d’onda avente un breve tempo di salita. Per avere una stima del tempo di salita, possiamo trascurare gli elementi dissipativi ed utilizzare la pulsazione naturale:

ω =

LC

1

(5.3) da cui possiamo calcolare ts come:

ts = ω 02 . 1 = 72,1 µs (5.4) dove abbiamo sostituito i valori tipici di induttanza (L = 50 H) e capacità (C = 100 pF) di una bobina tradizionale. Evidentemente per abbassare ts risulta essere necessario

diminuire il prodotto LC; tale accorgimento risulta essere difficile da attuarsi in questa tipologia di sistemi di accensione, vista l’esigenza di avere un certo valore di induttanza primaria e del rapporto spire, con un conseguente incremento della capacità dispersa.

5.1.2 Sistemi elettronici di accensione a transistori

La disponibilità di transistori al silicio con tensioni di breakdown superiori ai 500V, correnti di collettore di 10 A e temperatura massima di giunzione pari a 150°C, permette la realizzazione di sistemi di accensione con basse correnti sui contatti ed elevate correnti sul primario della bobina. In figura 5.3 si riporta lo schema elettrico di un tipico sistema di accensione a transistori:

Volendo immagazzinare sul primario della bobina una energia pari al doppio del valore teorico precedentemente calcolato con una corrente, in condizioni normali pari a 5 A, si ottiene un valore di induttanza Lp = 6.1 mH. Supponendo inoltre che la corrente

attraverso il transistore debba essere inferiore ai 7 A e assumendo un valore massimo di batteria pari a 17 V e VCESAT = 1.5 V, si può dedurre il valore della resistenza totale al

primario come:

Rp = (Vbatteria – VCESAT) / ip = 2,2 Ω (5.5)

Volendo mantenere il più possibile costante l’energia immagazzinata nel primario al variare del numero di giri, si ha che, detta ε =

p p E E ∆ la diminuzione percentuale di energia, il tempo durante il quale si deve verificare circolazione di corrente sul primario è: t = 2.3 p p R L ε 2 log (5.6) Noti pertanto i valori di Lp e Rp e definito l’incremento di energia ammissibile, si tratta

di verificare se al massimo numero di giri, il tempo di circolazione della corrente è superiore a quello sopra definito; in caso contrario si può pensare di introdurre qualche accorgimento circuitale che limiti il tempo di interdizione del transistore finale, a quello strettamente necessario all’esaurirsi della scarica. Per quanto concerne infine il tempo di salita di questi sistemi di accensione, possono svolgersi considerazioni del tutto analoghe a quanto fatto per i sistemi di accensione convenzionali.

5.1.3 Sistemi elettronici di accensione a scarica capacitiva

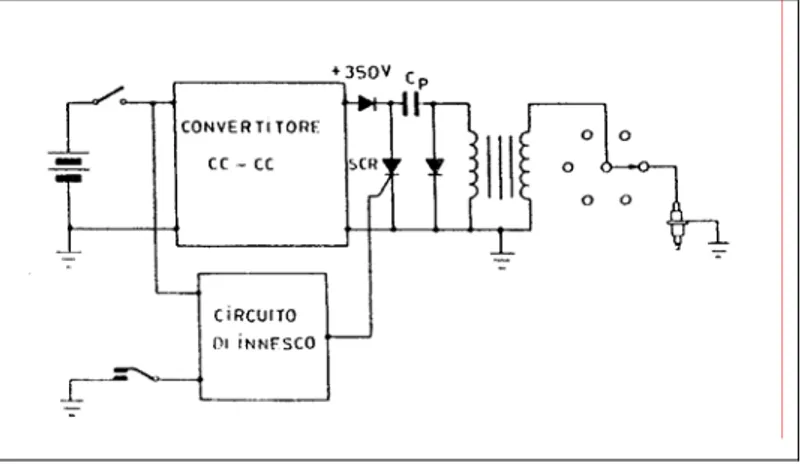

In figura 5.4 è riportato lo schema a blocchi di un sistema d’accensione a scarica capacitiva mentre in figura 5.5 viene evidenziato il circuito elettrico equivalente.

Figura 5.5 – Schema elettrico equivalente di un’accensione a scarica capacitiva

Dette VC e RC la tensione d’uscita e la resistenza interna del convertitore cc-cc, si hanno

i seguenti due casi: con l’SCR interdetto, la capacità Cp si carica alla tensione VC,

mentre con l’SCR in conduzione, la capacità Cp si scarica sul primario del

trasformatore, dando origine ad un aumento di tensione sul secondario che permette così la carica di Cs. La costante di tempo necessaria all’immagazzinamento di energia, è

molto più bassa rispetto al caso del sistema a transistori. Infatti, posto VC = 350 V per

avere un minor rapporto spire e un SCR di costo contenuto, si ha che la capacità Cp è

pari a: Cp = 2 2 C p V E = 1,25 µF (5.7) dove Ep è assunta pari al doppio del valore teorico precedentemente calcolato. Assunta

l’impedenza d’uscita del convertitore cc-cc pari a 500 Ω si ottiene dunque:

T = R Cp = 0,625 ms (5.8)

Questa costante di tempo risulta 4,5 volte inferiore rispetto a quella calcolata per la configurazione a transistori. Si noti come l’energia immagazzinata in questo caso risulti essere proporzionale al quadrato della tensione presente ai capi di Cp; inoltre in genere,

risulta più facile reperire degli SCR in grado di bloccare tensioni dell’ordine dei 350 V e di reggere correnti dell’ordine di 100 A, piuttosto che transistori in grado di sopportare correnti dell’ordine dei 5 A e tensioni attorno ai 400 V. Per quanto concerne il dimensionamento del rapporto spire della bobina, con riferimento allo schema di fig. 5.5, possiamo scrivere, supponendo immutata la quantità di energia presente nel sistema prima e dopo l’andata in conduzione del rettificatore controllato:

2 2 1 C pV C = 2 2 1 s pV C 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ s p N N + 2 2 1 s sV C (5.9) da cui risulta: p s N N = 2 2 2 s s C p s p V C V C V C − = 94 (5.10) avendo posto Cs = 100 pF. In realtà per i sistemi di accensione a scarica capacitiva, si

adottano trasformatori di impulsi, al posto delle bobine tradizionali, il cui valore di Cs

può essere ridotto a 80 pF. Questo implica, insieme al valore di induttanza di tali bobine, dell’ordine dei 200 mH, un valore del tempo di salita fornito dalla (5.4):

ts = 1.02 LC = 4.08 µs

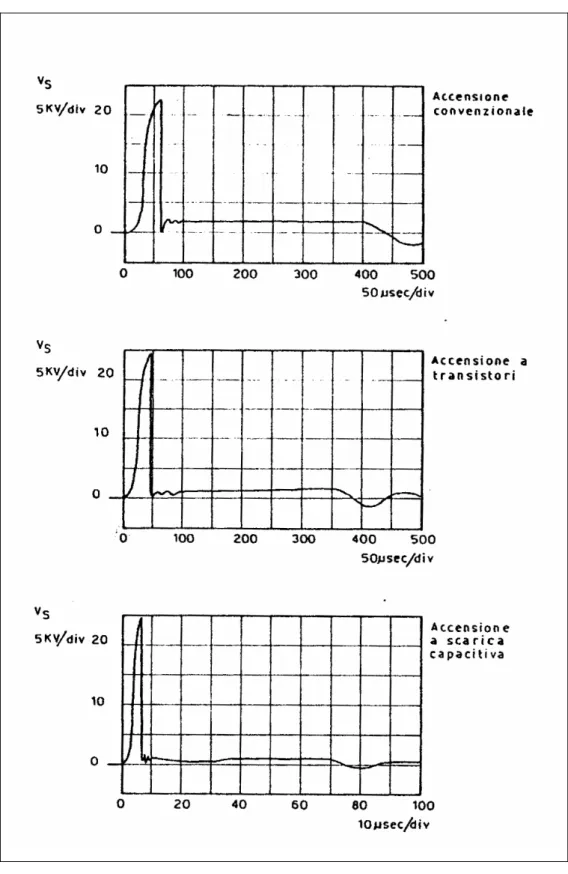

Tale tempo di salita è circa 17 volte più basso di quello calcolato per un sistema tradizionale. Per un confronto tra i tempi di salita dei vari sistemi di accensione, riportiamo in fig. 5.6, l’andamento della scarica sul secondario della bobina per i vari sistemi analizzati:

Figura 5.6 – Andamento della scarica del secondario della bobina per i vari sistemi analizzati

Il parametro mediante il quale si valuta generalmente, la sensibilità del sistema all’imbrattamento delle candele, è il fattore di utilità; tale parametro viene definito come l’inverso del valor minimo della resistenza, misurato in µS, che posta tra gli elettrodi,

permette il susseguirsi di almeno dieci scariche consecutive senza interruzioni. La misura si effettua con gli elettrodi posti a 5 mm di distanza tra loro. Nella tabella 5.1 si riportano alcuni valori tipici del fattore di utilità per i tre sistemi di accensione:

Tipi di accensione Fattore di utilità Accensione tradizionale 3

Accensione a transistori 6,5 Accensione a scarica capacitiva 30

Tabella 5.1: Valori tipici del fattore di utilità per i vari sistemi di accensione

Vista la differenza di tali valori, ben si capisce perché abbiamo deciso di adottare per il nostro progetto, un sistema di accensione elettronica a scarica capacitiva; a questo proposito cerchiamo adesso di valutare le opzioni circuitali possibili all’interno di tale classe di sistemi di accensione, valutando le sollecitazioni cui è soggetto l’SCR.

5.1.4 Analisi e confronto di configurazioni circuitali per sistemi di accensione elettronica a scarica capacitiva

I principali parametri che definiscono la scelta dell’SCR da inserirsi nelle accensioni elettroniche a scarica capacitiva, sono:

- costo (fondamentale nelle applicazioni di grande serie come quelle automobilistiche)

- massima temperatura di giunzione accessibile (sono esclusi componenti al Germanio)

- tensione di bloccaggio diretta ed inversa

- massima corrente ammissibile e durata della stessa - massimo valore del parametro di/dt ammissibile.

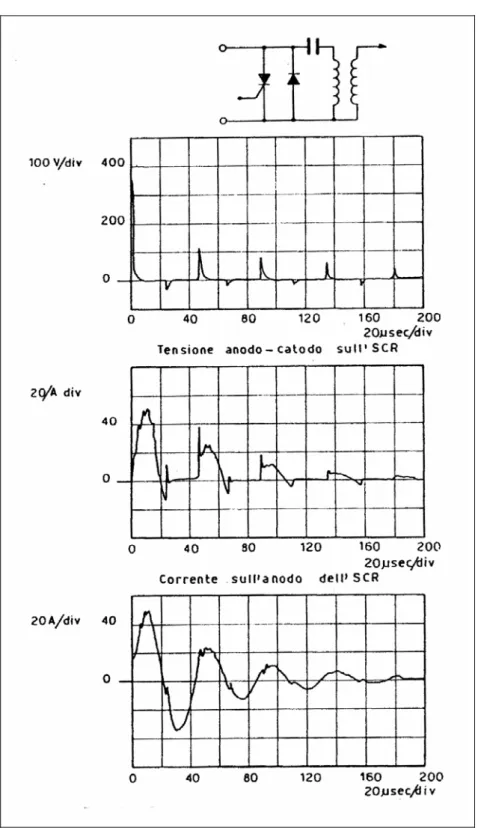

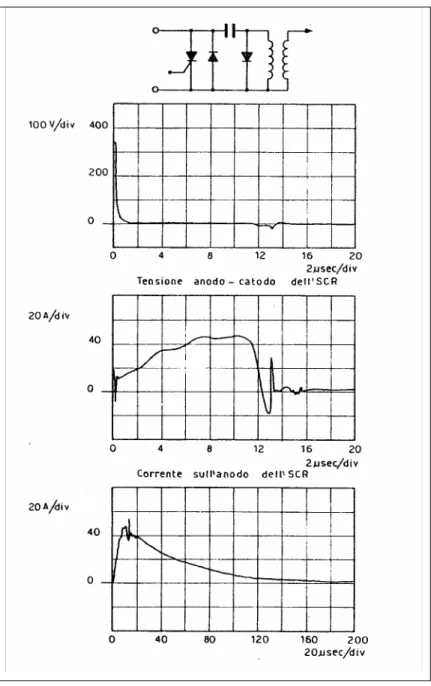

Inoltre le sollecitazioni a cui è soggetto l’SCR, dipendono oltre che dal tipo di bobina adottato, anche dal particolare circuito di uscita; a tal proposito si riportano le seguenti quattro figure rappresentanti quattro diverse configurazioni circuitali, insieme agli andamenti della tensione anodo-catodo, della corrente anodica e della corrente sul primario della bobina:

Figura 5.7 – Prima configurazione circuitale e relative forme d’onda

Figura 5.8 – Seconda configurazione circuitale e relative forme d’onda

Figura 5.9 – Terza configurazione circuitale e relative forme d’onda

Figura 5.10 – Quarta configurazione circuitale e relative forme d’onda

Corrente sul primario della bobina

Dall’esame delle precedenti figure risulta evidente che l’SCR è sollecitato, nelle peggiori condizioni, da picchi di corrente di circa 60 A della durata di 20 µs, da valori medi del parametro di/dt, calcolato durante il tempo di salita della corrente, di circa 60A/µs, da tensioni di bloccaggio dirette di 350 V e da tensioni di bloccaggio inverse trascurabili (fig. 5.7) o pari a 400 V (figg. 5.8, 5.9, 5.10), a seconda del circuito adottato. Per quanto concerne poi le forme d’onda delle correnti sul primario (corrente sull’anodo in ogni figura) si deve rilevare che esse danno luogo a differenti tipi di

scarica sul secondario; per scegliere la configurazione più appropriata al nostro caso sono necessarie delle considerazioni energetiche inerenti i circuiti risonanti. Premesso che nelle configurazioni di figg. 5.7 e 5.9 si hanno dei circuiti risonanti serie formati dal condensatore di carica e dal primario del trasformatore mentre in quelle delle figg. 5.8 e 5.10 si hanno dei circuiti risonanti parallelo, la configurazione di fig. 5.9 risulta essere la più vantaggiosa per quanto riguarda lo scambio energetico: infatti la presenza del diodo in parallelo all’SCR, ma in verso opposto, consente un completo scambio di energia tra l’induttanza del primario e la capacità dato che la loro corrente di scambio può fluire sia direttamente, attraverso l’SCR, che inversamente, attraverso il diodo. Per questo motivo le grandezze dello stadio d’uscita (trasformatore) durante la scarica, seguono un andamento sinusoidale smorzato e la scintilla generata dalla candela risulta essere più vigorosa rispetto a quella generata dalle altre configurazioni circuitali, dove la corrente del primario non può mai invertirsi, a causa della mancanza di un ramo che ne permetta la circolazione in senso opposto. Per questo motivo abbiamo adottato nel nostro progetto la configurazione circuitale di fig. 5.9. A questo punto possiamo pertanto affrontare nel dettaglio lo studio del sistema di controllo elettronico da noi progettato.

5.2 Architettura generale del sistema di controllo elettronico e descrizione delle specifiche funzionali e di interfaccia

5.2.1 Architettura hardware e specifiche di interfaccia

Il sistema di controllo realizzato esegue due funzioni fondamentali: il pilotaggio elettronico del solenoide del carburatore e la gestione dell’anticipo variabile del sistema di accensione. Per fare ciò si rendono necessari due segnali di ingresso: il monitoraggio del numero di giri del motore e l’acquisizione dell’entità del carico applicato.

Il cuore di tutto il sistema è rappresentato da un dispositivo programmabile capace di ricevere, mediante circuiti di interfaccia poco costosi, le informazioni necessarie per effettuare le funzioni esposte. Il grande pregio di una soluzione di questo genere, rispetto ad una puramente analogica a componenti discreti, risiede nella sua flessibilità; visto che il controllo è infatti realizzato mediante l’esecuzione di un programma caricato nella memoria del dispositivo, è possibile pensare di modificarlo opportunamente al variare dei parametri di configurazione del motore. In tal senso risulta evidente l’influenza della configurazione geometrica del motore (alesaggio,

cilindrata, alzata delle valvole) per quanto concerne la determinazione di una mappatura ottimale degli anticipi da caricare in memoria; inoltre, essendo il motore uno stazionario operante a 3000 giri/minuto, è ovvio che tale condizione di rotazione, determini fortemente tutta la logica di controllo insita nel programma. L’utilizzo di un componente programmabile, tipo microcontrollore, permette inoltre di realizzare una struttura circuitale estremamente affidabile ed adattabile alle più varie esigenze, avendo cura di configurare opportunamente i vari blocchi presenti all’interno del medesimo. Vediamo adesso uno schema a blocchi dettagliato del sistema di controllo realizzato:

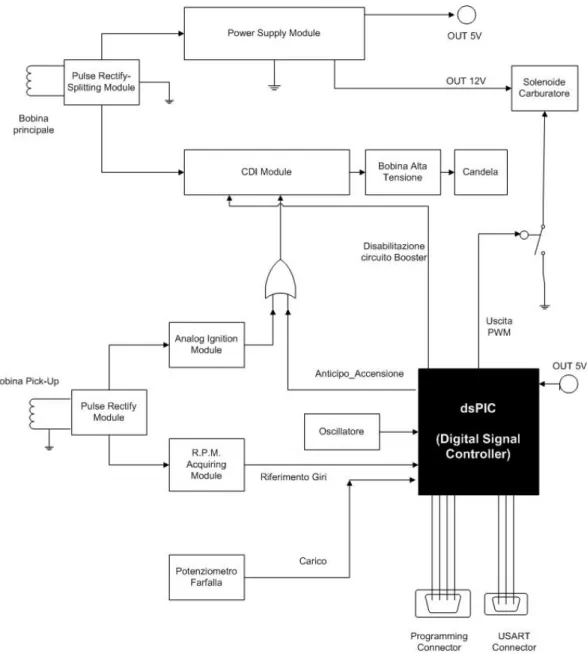

Figura 5.11 – Schema a blocchi completo del sistema di controllo realizzato

Dalla figura 5.11 è possibile apprezzare la tipologia dei diversi blocchi di cui è costituito il sistema di controllo. A monte di tutto, si trovano i due componenti

fondamentali del magnete-volano: la bobina principale e la bobina del pick-up. La bobina principale è responsabile dell’erogazione di potenza al circuito e deve pertanto soddisfare sia la richiesta di corrente del sistema di accensione che quella dell’attuatore del carburatore, nonché quella del resto del circuito. Per soddisfare tali requisiti è stato pertanto implementato un sistema circuitale, approfonditamente descritto nei prossimi paragrafi che divide la fonte di alimentazione in due rami indipendenti. La bobina di pick-up, invece, non deve erogare potenza, ma deve fornire al sistema l’informazione relativa al regime di funzionamento del motore, generando una forma d’onda analoga a quanto riportato in figura 2.10, sfasata di circa 30° rispetto al PMS. Inoltre tale bobina viene utilizzata anche per generare gli impulsi di accensione analogici da inviare al modulo di accensione analogica, indispensabili all’avviamento e per bassi regimi di rotazione, per i quali il sistema di accensione elettronica non è ancora entrato in funzione. Inoltre qualora il dsPIC dovesse cessare di funzionare regolarmente, il modulo di accensione analogica permette ugualmente al motore di continuare a funzionare. Il blocco di accensione è del tipo a scarica capacitiva, come concluso nel capitolo quattro; tale sistema presenta un’unica variazione rispetto alla configurazione circuitale di figura 5.9, rappresentata da un circuito con funzione di booster. Tale circuito si rivela molto utile a bassi regimi per ottimizzare il processo di accensione. Per quanto riguarda il modulo di alimentazione, esso riceve in ingresso il segnale impulsivo, la cui ampiezza è tra 100 e 200V, proveniente dalla bobina principale e fornisce in uscita sia le tensione stabilizzata di 12V necessaria per pilotare il carburatore elettronico che la tensione stabilizzata di 5V richiesta dal dsPIC e dal potenziometro analogico. Questo modulo è realizzato con un’architettura a due stadi: il primo è a componenti discreti e seguendo i principi degli stabilizzatori, genera la tensione da 12V mediante un diodo zener; il secondo stadio invece è realizzato con un regolatore integrato che fornisce in uscita la tensione stabilizzata da 5V. Per quanto riguarda il blocco di acquisizione del numero dei giri, esso è a tutti gli effetti un semplice circuito di interfaccia realizzato con un due resistenze, un condensatore ed un diodo zener. Il modulo pilotante il solenoide del carburatore elettronico è invece un interruttore digitale, realizzato con una coppia Darlington. Vediamo adesso lo schema circuitale completo del progetto realizzato:

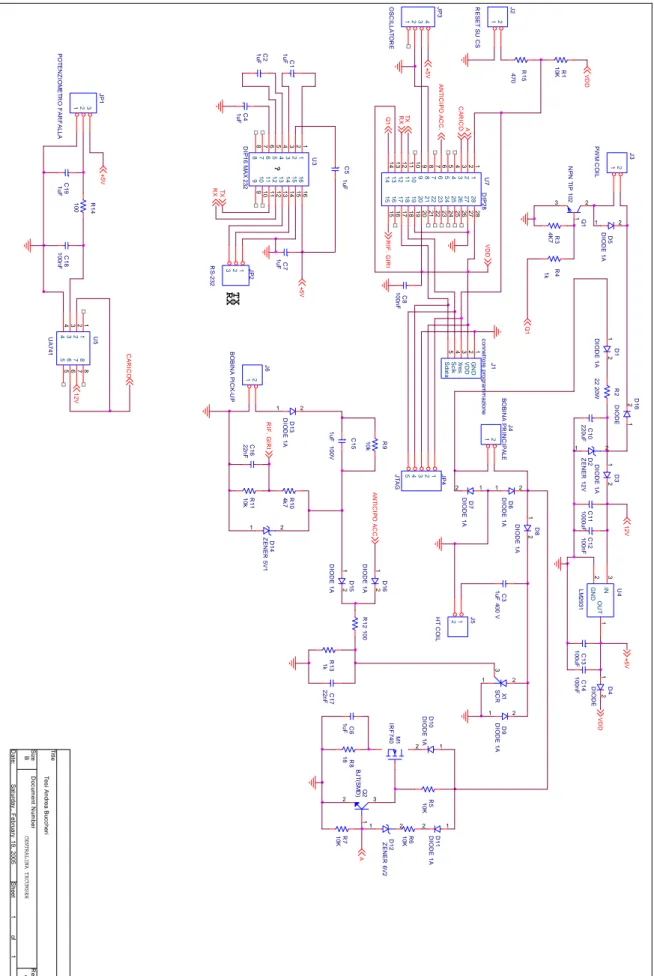

Figura 5.12 – Schema elettrico completo del progetto realizzato U4 LM 2931 3 2 1 IN GN D OU T Q2 BJ T (SM D ) 3 1 2 +5 V ? A D6 DI O D E 1 A 1 2 R1 1 10 k + C1 2 100 nF CA RIC O Q1 C1 4 10 0nF RX TX D1 8 DI O D E 1 2 C1 7 22nF D1 1 DI O D E 1 A 1 2 R1 2 1 0 0 D2 Z E NE R 1 2 V 1 2 + C4 1u F TX RI F . G IRI D1 6 DI O D E 1 A 1 2 RX U3 D IP 16 M A X 23 2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1 2 3 4 5 6 7 89 10 11 12 13 14 15 16 R1 4 10 0 + C1 3 10 0uF + C1 5 1 u F 10 0V 12V R1 3 1k C ENTRALI NA TEC UMSEH M1 IR F 7 4 0 + C1 9 1uF VD D Q1 A T e s i A ndrea B u c c heri B 11 S a tu rday , F ebruary 19, 2005 Ti tle S iz e Do cu m e n t Nu m b e r R e v D a te : S he et of D5 DIO D E 1 A 1 2 R1 5 470 J5 HT C O IL 1 2 + C5 1u F C1 8 100nF + C1 1uF R5 10K VD D TX Q1 NP N T IP 1 0 2 1 2 3 + C7 1uF D3 DIO D E 1 A 1 2 RX R8 18 A N T IC IPO AC C . J4 BO BI N A PR IN C IP A L E 1 2 +5 V R3 4K 7 D1 2 Z E NE R 6 V 2 1 2 CA R ICO J2 R ESE T SU C S 1 2 J6 BO BI N A PI C K -U P 1 2 C3 1uF 4 00 V C8 10 0nF R6 10 K D1 5 DI O D E 1 A 1 2 + C1 1 1000 uF C1 6 22nF 12V A U5 UA 7 4 1 1 2 3 4 5 6 7 8 1 2 3 45 6 7 8 D8 DIO D E 1 A 1 2 D7 DI O D E 1 A 1 2 D4 DIO D E 1 2 R2 22 20 W +5 V JP 1 P O T E NZ IO M E T R O F A RF A L L A 1 2 3 R1 10 K JP 3 O S CIL L A T O RE 1 2 3 4 D9 DI O D E 1 A 1 2 AN T IC IPO AC C . + C2 1uF D1 0 DI O D E 1 A 1 2 + C1 0 220 uF R7 10 K D1 4 Z E NE R 5 V 1 1 2 +5 V X1 SC R 2 1 3 C6 1u F R4 1k D1 DI O D E 1 A 1 2 JP 4 JT A G 1 2 3 4 5 R1 0 4k 7 RIF . G IRI J3 PW M C O IL 1 2 R9 10k D1 3 DIO D E 1 A 1 2 VD D J1 c o nnet to re program m a zion e 1 2 3 4 5 GN D VD D Xr e s Sc lk S dat a U7 DIP 2 8 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 JP 2 R S -232 3 2 1

5.2.2 Definizione degli algoritmi del sistema di controllo

Il nostro obiettivo è stato quello di conseguire il funzionamento ottimale del motore a 3000 giri/minuto, avendo cura di minimizzare i consumi accettando come compromesso un peggioramento nella regolarità della combustione misurabile attraverso una disuniformità di velocità minore del 5% (vedi par. 4.1). La logica di controllo che abbiamo seguito per la realizzazione del progetto, è la seguente: acquisito il regime di rotazione del motore e l’entità del carico applicatovi, il sistema di controllo decide come pilotare il solenoide del carburatore elettronico e quando scoccare la scintilla tra gli elettrodi della candela. In particolare se il regime di rotazione è superiore alla soglia desiderata, si provvede a smagrire la miscela, fino al raggiungimento della condizione desiderata. Se invece siamo al di sotto di tale soglia, ci limitiamo a tenere chiuso il solenoide pulsante, ottenendo così una miscela ricca. Quando si raggiunge la condizione di regime e il carico applicato è inferiore alla metà del massimo valore applicabile, il sistema comincia a smagrire progressivamente la miscela finché non rileva una diminuzione del regime di rotazione. A questo punto si ha un nuovo e veloce arricchimento della miscela, al fine di mantenere il numero di giri costante. Questo processo si ripete ciclicamente nel tempo.

5.3 Analisi e progetto di dettaglio dei blocchi costituenti il sistema

Passiamo adesso ad analizzare la costituzione, il principio di funzionamento e l’analisi di dettaglio dei singoli blocchi costituenti il sistema di controllo:

5.3.1 Pulse Rectify-Splitting Module

Questo blocco riceve in ingresso gli impulsi di tensione della bobina principale del magnete-volano e divide quelli positivi da quelli negativi: i primi vengono utilizzati dal circuito di accensione, mentre i secondi, dopo essere stati raddrizzati, vanno al modulo di alimentazione. Da un punto di vista pratico questo blocco si presenta come un ponte raddrizzatore “riferito a massa”, nel quale i catodi dei due diodi facenti capo al polo positivo, sono mantenuti separati, mentre ognuno pilota un diverso modulo del circuito che ha come primo elemento circuitale un diodo. In figura 5.13 è possibile visualizzare quanto descritto:

Modulo di Accensione D6 1 2 D8 1 2 D7 1 2 D1 DIODE 1A 1 2 J4 BOBINA PRINCIPALE 1 2 Modulo di Alimentazione

Figura 5.13 – Pulse Rectify Splitting Module

Per un corretto pilotaggio di tale modulo è necessario utilizzare una bobina (principale), uscente con un segnale differenziale e non riferito a massa; molti avvolgimenti in uso nelle applicazioni automotive, hanno invece un’uscita single-ended ovvero riferita a massa; la massa è usualmente coincidente con il telaio di supporto del motore al banco di prova. I diodi infine utilizzati per il modulo sono gli S1M della Fairchild [18]; tali dispositivi sono diodi per scopi generici a montaggio superficiale (SMD) e sono caratterizzati da una massima corrente diretta di 1A e da una tensione inversa massima di 1000V.

5.3.2 Modulo di alimentazione

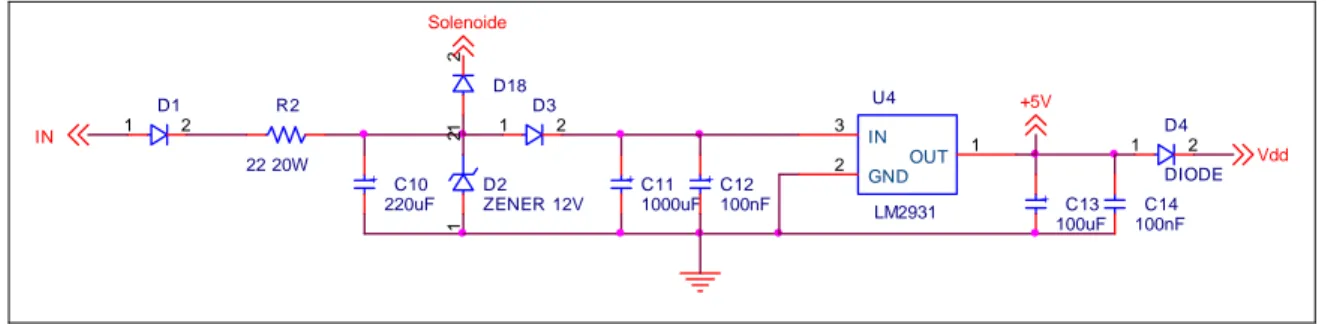

Il modulo di alimentazione deve provvedere a stabilizzare il segnale impulsivo proveniente dalla bobina principale ad un valore di tensione compatibile con le specifiche dei componenti elettronici utilizzati. Vista la necessità di avere contemporaneamente una tensione di alimentazione di 12V per il carburatore elettronico e di 5V per il dsPIC e per il potenziometro della farfalla, questo blocco ha due uscite. Il segnale che arriva in ingresso al sistema è un impulso di ampiezza circa 200V; per questo motivo per il primo stadio si è adottato una soluzione a componenti discreti. Con riferimento alla figura 5.14, abbiamo che il diodo D1 separa il circuito di alimentazione da tutto ciò che si trova a monte, evitando che l’energia immagazzinata nei condensatori a valle, possa tornare indietro.

+ C10 220uF + C11 1000uF Vdd + C12 100nF D1 1 2 D3 1 2 U4 LM2931 3 2 1 IN GND OUT D2 ZENER 12V 1 2 +5V D4 DIODE 1 2 IN + C13 100uF D18 1 2 Solenoide R2 22 20W C14 100nF

Figura 5.14 – Modulo di alimentazione

La resistenza R2 limita la corrente assorbita dalla bobina principale ed il diodo zener D2 taglia i picchi di tensione (clipping) al valore della tensione di Zener, coincidente nel nostro caso con 12V. Per quanto concerne il dimensionamento di R2 si è effettuato il seguente ragionamento: supposto un segnale di ingresso impulsivo di 100V (worst case), abbiamo stimato il suo valor medio con il 60% del valor medio di una sinusoide raddrizzata a singola semionda, avente lo stesso valore di picco. Ciò significa che il valor medio stimato viene:

Valor medio tensione di ingresso = 0,6*(1/π)*100 = 19 V

Visto che il modulo di alimentazione deve garantire nel caso peggiore 150 mA al solenoide più le varie correnti di polarizzazione del diodo zener e del regolatore integrato LM2931 [19], stimando la minima corrente transitante attraverso R2 in 250mA si ottiene:

R2 < 76 Ω

Se a questo aggiungiamo che la carica di C10 (220µF) deve avvenire in metà tempo di un giro motore, anche per il massimo regime di rotazione del motore (6000 Rpm), otteniamo:

R1*C10 < 5 ms ovvero:

R1 < 23 Ω

Il condensatore C10 ha un valore grande di capacità, visto che ha il compito di immagazzinare una certa quantità di energia mentre D1 è in conduzione; tale quantità di energia serve poi ad alimentare i circuiti a valle, nel periodo di tempo in cui D1 è interdetto. Si noti inoltre come con tale valore di C10, il ripple in uscita è inferiore al 2% della tensione massima (ovvero i 12V); infatti dall’appendice 3 sappiamo che la resistenza equivalente Req del solenoide vale 80 Ω, per cui se calcoliamo la scarica del

condensatore C10 in un periodo di 20ms (tempo di rotazione a 3000 giri/minuto) otteniamo: Ripple = q C T eRe * − = 1.06 %

Per quanto concerne poi il dimensionamento di C11,C12,C13,C14 ci siamo attenuti alle tipiche indicazioni dei costruttori di regolatori di tensione integrati; è buona norma porre in parallelo ai condensatori elettrolitici di capacità elevata, dei piccoli condensatori ceramici, al fine di evitare fenomeni di auto-oscillazione nel circuito interno di regolazione della tensione; questo motiva gli inserimenti di C12 e C14. Per quanto riguarda invece la scelta del regolatore di tensione ci siamo attenuti alla specifica dell’alimentazione del dsPIC e del potenziometro analogico (5V), ricadendo sul regolatore integrato LM2931. Tale regolatore infatti, come si evidenzia dal datasheet [18], ha una corrente a riposo dell’ordine di 1mA che, se confrontata con la corrente assorbita dal solenoide, è assolutamente trascurabile. Questo regolatore ha anche il pregio di accettare delle tensioni fino a 26V e di sopportare dei picchi di tensione anche di 60V. A differenza di altri regolatori di tensione, l’LM2931 riesce a stabilizzare l’uscita su 5V, anche se il livello di tensione in ingresso scende fino a 5.6V.

5.3.3 Modulo di accensione a scarica capacitiva (CDI)

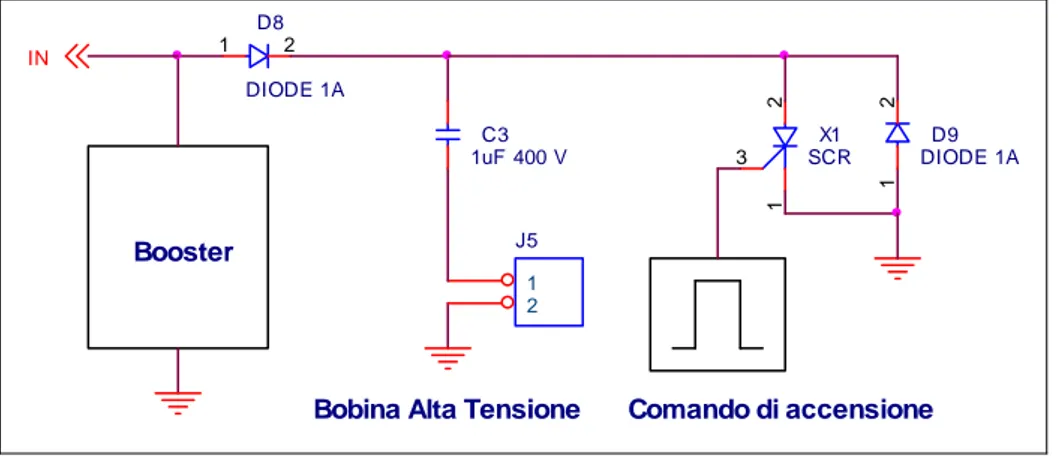

Comando di accensione Booster

IN

J5

Bobina Alta Tensione

1 2 X1 SCR 2 1 3 D8 DIODE 1A 1 2 D9 DIODE 1A 1 2 C3 1uF 400 V

Figura 5.15 – Modulo CDI

Questa parte del circuito genera la scarica di accensione quando riceve il comando sul gate dell’SCR, inviato all’istante opportuno dal dsPIC. Per le forme d’onda di tensione e corrente si fa riferimento alla figura 5.9; per il momento tralasciamo invece lo scopo ed il funzionamento del circuito booster che verrà analizzato nel prossimo paragrafo.

L’uscita del modulo CDI è connessa al trasformatore ad alta tensione, avente un rapporto spire di circa 100, il cui avvolgimento secondario risulta connesso direttamente alla candela di accensione. La tensione in ingresso proviene dalla bobina principale raddrizzata a singola semionda; tale tensione, attraverso il diodo D8, va a caricare il condensatore C3 ad un valore di tensione di circa 200V. Quando arriva l’impulso sul gate di X1, l’SCR si innesca e permette al condensatore di scaricarsi rapidamente attraverso la bobina d’alta tensione in uscita. Il condensatore C3 e l’avvolgimento primario della bobina, costituiscono a tutti gli effetti un circuito risonante serie; per questo motivo, quando arriva l’impulso sul gate di X1 e ha inizio la scarica, la forma d’onda della corrente sul primario della bobina, assume un andamento sinusoidale smorzato con frequenza di oscillazione pari alla frequenza di risonanza del circuito. Tale andamento di corrente è reso possibile dalla presenza del diodo D9 che permette la circolazione della carica, nel verso opposto a quello dell’SCR.

5.3.4 Booster di accensione

Il sistema di accensione precedentemente descritto soffre di un problema, quando il motore funziona a regimi molto bassi; infatti, il segnale generato dalla bobina principale è in questo caso molto debole e pertanto non può garantire una carica del condensatore C3, sufficiente a generare la scintilla di accensione.

R5 10K R7 10K D11 DIODE 1A 1 2 A D12 ZENER 6V2 1 2 R6 10K M1 IRF740 Q2 BJT(SMD) 3 1 2 Bobina Principale D10 DIODE 1A 1 2 R8 18 C6 1uF

Questo bipolo a riposo, connette a massa il segnale di ingresso proveniente dalla bobina principale: in questa condizione la corrente erogata dal magnete-volano assume un valore prossimo al valore di corto circuito, visto che l’unico elemento dissipativo è la resistenza R8, di valore ohmico molto basso. Quando invece la caduta ai capi del booster, supera una certa soglia, il circuito si apre bruscamente, interrompendo “istantaneamente” il flusso di corrente; a causa però della natura induttiva del circuito di alimentazione (bobina principale), si genera così una notevole sovratensione, tale da caricare il condensatore C3 del sistema di accensione. In figura 5.16 è possibile apprezzare i tre rami costituenti il circuito di booster; il ramo a destra è un circuito a soglia. Infatti finché la caduta ai capi del diodo zener non supera 6.2V, tale bipolo è aperto; considerando anche la caduta sul diodo D11, si ha che il diodo D12 comincia a condurre quando la tensione in ingresso vale almeno 6,8V. In realtà a causa anche della caduta su R6, si ha che la conduzione diviene significativa per tensioni di ingresso superiori agli 8V. Il ramo centrale è invece responsabile della commutazione dell’intero circuito di booster: il transistor Q2 (BCR148 [20]) è pilotato dal circuito a soglia ed a sua volta pilota M1 facente parte del ramo di potenza del circuito. Q2 passa molto velocemente da uno stato di interdizione a quello di saturazione, non appena la tensione di ingresso supera gli 8V; in questa condizione infatti, un ulteriore aumento di tensione si ripercuote quasi del tutto sulla VBE di Q2, provocando un consistente aumento di

corrente. Entrando Q2 in conduzione, si ha che il gate di M1 viene portato a massa e ciò comporta la sua apertura, avendo questo una tensione di soglia intorno ai 3V [21]. Il ramo di sinistra, infine, è quello in cui si incanala la maggior parte della corrente: a riposo, la tensione sul gate di M1, segue la tensione di ingresso, visto che Q2 è interdetto. Questo porta M1 ad essere in condizione di condurre molto bene; per questo motivo l’impedenza equivalente del ramo è molto bassa ed è data esclusivamente dalla resistenza R8, di valore molto basso (18Ω). In questa condizione il circuito è attraversato dalla massima corrente erogabile dalla bobina principale del magnete-volano; tale corrente provoca pertanto una caduta sempre più grande ai capi del bipolo booster, il quale non appena raggiunge una caduta di tensione pari a quella di soglia, commuta velocemente, aprendosi ed interrompendo il flusso di carica. A causa della natura induttiva della bobina accensione, questo comporta una elevata sovratensione che va a caricare correttamente C3 anche per bassi regimi di rotazione del motore. In assenza del booster di accensione, il condensatore C3 si caricherebbe ad un valore di tensione circa uguale al picco massimo positivo generato dalla bobina principale: nelle

condizioni nominali di funzionamento del motore (3000 rpm), ciò non crea problemi, visto che si hanno tensioni dell’ordine dei 200V. All’avviamento invece, il regime di rotazione è talmente basso che non si generano nella bobina principale, tensioni accettabili per generare la scintilla di accensione; per questo motivo avremmo pertanto un avviamento del motore estremamente difficoltoso. Proprio perché il circuito booster è molto utile a bassi regimi di rotazione è stato inoltre previsto un comando (A) da parte del dsPIC, che provvede a spengere tale circuito al di sopra dei 1000 giri/minuto, ponendo una tensione di 5V sulla base di Q2.

5.3.5 Circuito di pilotaggio del solenoide del carburatore

Questo circuito ha come ingresso il segnale modulato PWM, proveniente dal dsPIC.

D5 DIODE 1A 1 2 12V J3 Solenoide 1 2 Q1 NPN TIP 102 1 2 3 R3 4K7 IN R4 1k

Figura 5.17 – Circuito di pilotaggio del solenoide del carburatore

Il transistor Darlington Q1 si comporta da interruttore elettronico, attivando o meno il solenoide di controllo del carburatore elettronico. Il valore della resistenza R4 è stato dimensionato considerando che quando l’uscita è bassa, la coppia Darlington deve lavorare in saturazione spinta, in modo da generare una caduta di tensione trascurabile tra collettore ed emettitore. R3 invece serve a collegare a massa la base del TIP 102 [22], qualora l’ingresso si trovi in uno stato di alta impedenza. Il diodo D5 è stato pensato per proteggere il collettore del transistor Q1, a causa della natura induttiva del carico pilotato. Infatti, in assenza di tale diodo, quando Q1 passa dallo stato di conduzione a quello di interdizione, ai capi del solenoide di carico, si genera una sovratensione che tende a mantenere costante la corrente; tale tensione si ripercuote tutta sul collettore del transistor con il pericolo di provocarne la rottura. La presenza del diodo, invece, fa sì che la corrente che attraversa la bobina, abbia la possibilità di fluire

anche con Q1 interdetto, portando in conduzione D5 ed impedendo la formazione della sovratensione.

5.3.6 Pulse Rectify Module

Figura 5.18 – Pulse Rectify Module

Questo semplice modulo si limita a prelevare gli impulsi positivi (uno per giro motore) del pick-up, tagliando invece gli impulsi negativi del medesimo (due per giro motore). L’uscita di questo modulo è poi utilizzata dal modulo per l’acquisizione del numero dei giri e dal modulo per la generazione degli impulsi di trigger dell’accensione analogica.

D13 DIODE 1A 1 2 R9 10k + C15 1uF 100V OUT J6 Bobina Pick-up 1 2

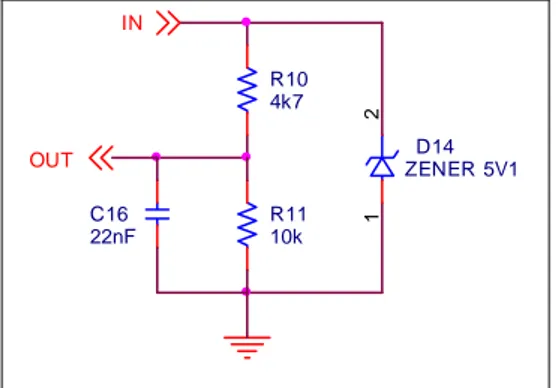

5.3.7 Modulo di acquisizione del regime di funzionamento del motore OUT C16 22nF R11 10k IN D14 ZENER 5V1 1 2 R10 4k7

Figura 5.19 – Modulo di acquisizione del regime di funzionamento del motore

Questo semplice circuito di interfaccia serve per adattare gli impulsi del regime di rotazione del motore affinché il dsPIC possa rilevarli. Come segnale di ingresso vengono utilizzati gli impulsi positivi generati dalla bobina di pick-up, in uscita dal Pulse Rectify Module. Il diodo zener D14 ha la funzione di limitare a 5V l’ampiezza di tali impulsi; per quanto concerne il dimensionamento di R11 e C16, devono essere scelti in modo da fornire una costante di tempo tale da permettere la carica e la scarica di C16 in un tempo inferiore alla durata dell’impulso positivo di pick-up a 3000 giri/minuto (circa 2ms). Per quanto riguarda R10 si deve dimensionare considerando quanto vale la massima corrente sopportabile su un piedino del dsPIC e inoltre deve essere tale da permettere il riconoscimento di un livello logico alto da parte dello stesso dispositivo.

5.3.8 Modulo di pilotaggio del sistema di accensione

Questo modulo è utilizzato per generare gli indispensabili impulsi di accensione sin dall’avviamento del motore, quando tutta la logica digitale è ancora in fase di inizializzazione. IN2 OUT IN1 R13 1k D16 DIODE 1A 1 2 D15 DIODE 1A 1 2 R12 100 C17 22nF

Figura 5.20 – Modulo di pilotaggio del sistema di accensione

All’ingresso 1 giungono gli impulsi positivi di pick-up generati dal modulo di figura 5.6 tagliati a 5V; l’ingresso 2 è invece riservato agli impulsi generati a partire da un certo regime di rotazione (1000 rpm) dal dsPIC, per ottenere un anticipo di accensione. I diodi D15 e D16 implementano, infatti, un OR logico tra i due segnali di ingresso; questo si traduce nella possibilità di poter effettuare un anticipo d’accensione rispetto agli impulsi generati dal pick-up. All’arrivo di un impulso su IN2, in anticipo di fase rispetto al segnale di IN1, sincrono con il pick-up, si ha la generazione anticipata di un impulso di innesco per l’SCR del modulo CDI. Quando poi arriva anche l’impulso su IN1, questo non altera in alcun modo il processo di generazione del trigger d’accensione, ormai già iniziato; l’unico fenomeno riscontrato con il simulatore circuitale PSpice, è un leggero incremento (0.1V) nel valore di picco dell’impulso di innesco dell’SCR, quando entrambi gli ingressi sono alti. La resistenza R12 serve a limitare le correnti nel gate, ma allo stesso tempo deve essere tale da garantire una corrente in modulo sufficiente per l’innesco dell’SCR. La coppia R13,C17 ha invece lo scopo di filtrare il segnale di attivazione, al fine di evitare inneschi indesiderati, dovuti a disturbi captabili dall’esterno.

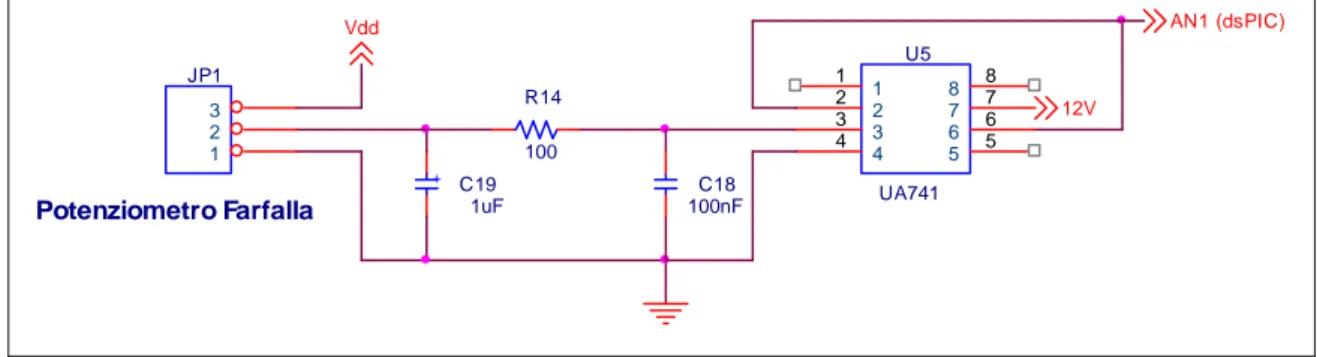

5.3.9 Blocco di condizionamento del segnale del potenziometro della farfalla Vdd + C19 1uF U5 UA741 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 AN1 (dsPIC) 12V C18 100nF JP1 Potenziometro Farfalla 1 2 3 R14 100

Figura 5.21 – Blocco di condizionamento del segnale del potenziometro della farfalla

L’ingresso di questo blocco è costituito dal segnale del potenziometro solidale con la farfalla del gas; tale potenziometro da 5kΩ è alimentato con la Vdd generata dal modulo

di alimentazione. L’uscita di questo blocco è invece inviata all’ingresso analogico del dsPIC, ovvero ad un convertitore A/D, come sarà spigato nelle prossime pagine. La finalità di questo modulo all’interno del nostro circuito stampato, è quella di filtrare adeguatamente il segnale proveniente dal potenziometro solidale con la farfalla del gas; il filtro passa basso implementato con C19,C18 e R14, serve a rispettare la condizione di Nyquist sul campionamento (filtro anti-aliasing) e ad evitare la presenza di eventuali disturbi dovuti al contatto strisciante del potenziometro stesso. L’amplificatore operazionale µA741 serve invece ad adattare l’impedenza della sorgente a quella del carico; in questo modo infatti il piedino AN1 vede un’impedenza equivalente molto bassa.

5.3.10 Oscillatore

Nel nostro progetto è presente anche un oscillatore [24], necessario per fornire il clock al sistema dsPIC. Tale dispositivo è un risonatore ceramico della Murata e fornisce un segnale di riferimento a 40 MHz.

5.3.11 L’interfaccia MAX232

Questo circuito di interfaccia è stato incluso al fine di adattare i livelli di tensioni del dsPIC (da 0 a 5V) a quelli supportati dallo standard di trasmissione seriale RS232 (+12V)

5.3.12 Il circuito di reset del dsPIC

Il semplice circuito presente in fig. 5.22 è stato pensato per eseguire il reset manuale del dsPIC30F2010: Vdd R1 10K R15 470 J2 RESET SU CS 1 2 /MCLR

5.4 Il dsPIC 30F2010

Il dispositivo che abbiamo deciso di utilizzare all’interno del presente lavoro di tesi, rappresenta ad oggi, uno dei prodotti più innovativi dell’azienda Microchip; infatti esso appartiene alla famiglia dei Digital Signal Controllers, annoverabili come microcontrollori embedded che integrano su di un unico chip le potenzialità di controllo tipiche di un microcontrollore embedded assieme alla capacità computazionali tipiche di un DSP. In figura 5.23 è possibile evidenziare la collocazione commerciale del dispositivo in funzione delle sue performance e del suo costo.

Figura 5.23 – Collocazione di mercato del dsPIC

La famiglia dsPIC si suddivide a sua volta in tre diversi tronconi: il primo dedicato ad applicazioni prevalentemente di tipo audio, il secondo dedicato principalmente al controllo di motori elettrici e alla conversione di forme di energia e il terzo dedicato prevalentemente all’acquisizione e all’elaborazione di segnali provenienti da diversi tipi di sensori. Per le nostre finalità di acquisizione ed elaborazione di segnali significativamente rappresentativi del funzionamento del motore, risulterebbe intuitiva la scelta della terza famiglia; facendo però un’indagine di mercato, è emerso che allo stato attuale della produzione, non sono stati ancora lanciati sul mercato i dispositivi di tale famiglia con package a 28 pin o a 18 pin. Inoltre i dispositivi disponibili hanno tutti il package a 80 pin e a montaggio superficiale. Per questo motivo ci siamo orientati sul

implementato sul nostro circuito stampato, al fine di poter eventualmente sostituire il dispositivo, nel caso di malfunzionamento durante il collaudo sperimentale. Naturalmente per un’eventuale produzione di serie del sistema, la scelta verrebbe indirizzata verso packages a montaggio superficiale, preferibili in un’ottica di riduzione dei costi di produzione.

Cerchiamo di dare a questo punto, una caratterizzazione sommaria delle potenzialità della famiglia da noi scelta, da un punto di vista hardware:

- Viene implementata per la CPU RISC, un’architettura modificata di Harvard a 16 bit

- Le istruzioni sono codificate su 24 bit mentre i dati su 16 bit (di tali dimensioni sono pertanto anche i corrispettivi bus)

- Indirizzamento lineare nella memoria di programma (fino a 4M*24 bit)

- Indirizzamento lineare nella memoria dati (fino a 64 kB di dati suddivisi in due blocchi X e Y)

- Sono definite 84 istruzioni assembler di base costituenti un set ottimizzato per un compilatore C

- Sono disponibili fino a 144 kB di memoria FLASH per lo spazio di programma - Sono disponibili fino a 8 kB di memoria RAM per lo spazio dati

- Sono disponibili fino a 4 kB di memoria non volatile EEPROM per lo spazio dati

- 16 registri operativi a 16 bit (W0:W15)

- 3 unità di generazione indirizzi (AGU), due dei quali servono a gestire i blocchi dati X e Y (le istruzioni da MCU operano solo sull’AGU di X mentre le istruzioni da DSP operano attraverso entrambi gli AGU)

- Sono presenti 2 accumulatori a 40 bit con la saturazione logica opzionale

- Moltiplicatore da 17 bit x 17 bit che svolge la moltiplicazione tra numeri interi e tra numeri frazionari, in un solo ciclo

- Barrel Shifter da 40 bit (bidirezionale) capace di traslare fino a 16 bit a destra o a sinistra in un singolo ciclo

- Possibilità di operare fino a 30 MIPS (in tal senso si può utilizzare un clock esterno dalla DC fino a 40 MHz oppure un altro clock da 4 a 10 MHz, da utilizzare con il moltiplicatore di frequenza a PLL 4x, 8x, 16x)

- Sono gestibili fino a 42 sorgenti di interruzione con 8 livelli di priorità, selezionabili dall’utente

- Convertitore Analogico-Digitale da 10 bit con 500 kS/s come velocità di conversione; sono disponibili fino a 16 canali ed è possibile convertire dati anche nelle modalità di funzionamento SLEEP e IDLE

- Modulo Timer con prescaler programmabili: sono disponibili fino a 5 contatori/timer da 16 bit

- Modulo di acquisizione dati in ingresso (Input Capture) utile per misure di frequenza o periodo e per gestire ulteriori sorgenti di interruzione esterne

- Modulo Output Compare utile per la generazione di forme d’onda impulsate aventi duty-cycle predefinito dall’utente

- Modulo PWM per il controllo di motori elettrici; sono disponibili fino a 8 canali di uscita PWM, con 4 generatori di duty-cycle e la possibilità di operare l’inversione della polarità dei segnali.

- Modulo SPI interfaccia seriale asincrona che permette la comunicazione con i dispositivi periferici

- Modulo I2C fornisce il supporto hardware completo mediante un’interfaccia a 16 bit delle modalità previste dallo standard di comunicazione seriale I2C

- Modulo UART transceiver universale asincrono

- Modulo CAN interfaccia seriale utile per comunicare con altri moduli CAN o altri microcontrollori

- Modulo DCI (Data Converter Interface) permette l’interfacciamento di semplici dispositivi come i Codecs audio, i convertitori A-D e D-A

- Modulo d’interfaccia Quadrature encoder per l’acquisizione ed il filtraggio digitale dei segnali di riferimento dei motori AC.

A questo punto possiamo scendere più nel merito della struttura del modello da noi scelto; il dsPIC30F2010 si inquadra come il più “piccolo” dei dispositivi della famiglia Motor Control. Con riferimento alla Figura 5.24, è possibile effettuare un rapido confronto tra le varie caratteristiche dei dispositivi: in particolare ci preme evidenziare come il dispositivo, con i suoi 12kB di program memory flash traducibili in 4k istruzioni e con 512 byte di data memory, si riveli sufficiente a contenere la complessità di un controllo come quello desiderato. A titolo puramente indicativo si segnala inoltre che il succitato dispositivo è disponibile, ad oggi, al prezzo di 5.73$; questo pur non

prototipo realizzato, assicura comunque un costo finale ancora accettabile, se rapportato al costo del motore su cui viene montato (attorno ai 20 €).

Figura 5.24 – Classificazione dei dsPIC della famiglia Motor Control

Passiamo adesso ad esaminare il pinout del dispositivo scelto:

Figura 5.25 – Pinout del dsPIC30F2010

Il dispositivo presenta 28 pin, di cui 21 disponibili per l’I/O; inoltre sono presenti i piedini per l’alimentazione positiva (VDD) e quella negativa (VSS), usualmente riferita a

massa e gli omonimi piedini per l’alimentazione della parte analogica (AVDD e AVSS).

Volendo tracciare brevemente i ruoli di ciascun piedino, si hanno:

• AN0_AN5 sono 6 ingressi analogici per il convertitore A/D interno • CLKI_CLKO sono i piedini necessari per la gestione di un clock esterno

• EMUD_EMUC sono i piedini per la comunicazione dei dati e del clock, con un debugger quale l’ICD2

• IC1,IC2,IC7 e IC8 sono 4 piedini di ingresso per i rispettivi moduli Input Capture

• INT0,INT1 e INT2 sono 3 piedini di ingresso per la gestione di sorgenti di interruzione esterne

• PWM1L, PWM1H_PWM3L, PWM3H sono i piedini di uscita per le forme d’onda PWM

• /MCLR è un piedino di ingresso attivo basso, per il reset del dispositivo • OSC1,OSC2 sono i piedini di ingresso e di uscita del clock del sistema

• PGC e PGD sono i piedini per i dati e per il clock per la programmazione seriale del dispositivo

• RB0_RB5, RC13_RC14, RD0_RD1, RE0_RE5, RE8, RF2, RF3 sono tutti piedini bidirezionali di I/O

• T1CK e T2CK sono i piedini di ingresso per un clock esterno per il Timer1 e il Timer2

• U1RX, U1TX, U1ARX e U1ATX sono i piedini per la trasmissione dati verso una porta seriale RS-232 interfacciabile con quella di un personal computer

• VREF+ e VREF- sono i piedini dedicati alle tensioni di riferimento della parte

analogica

Questi piedini sono facilmente ritrovabili nella fig. 5.26 dove si riporta la struttura a blocchi del dispositivo.

Figura 5.26 – Struttura a blocchi del dsPIC30F2010

Il dispositivo si presenta pertanto come un insieme di blocchi elementari, le cui funzioni saranno descritte nel prossimo paragrafo; in questa sede ci preme invece delineare il modello con cui è possibile schematizzare il dispositivo agli occhi di un programmatore: il dispositivo si presenta con un insieme di 16 registri operativi da 16 bit (W0_W15), 2 accumulatori da 40 bit (AccA, AccB), 1 registro per la lettura dei dati allocati in tabelle (TBLPAG), 1 registro per la visibilità della pagine di Program Memory (PSVPAG), 4 registri per la gestione dei cicli DO e REPEAT (DOSTART, DOEND, DCOUNT e RCOUNT), 1 registro di configurazione del core (CORCON), 1 registro di stato (SR) ed infine un Program Counter da 23 bit (PC).

Figura 5.27 – Modello software equivalente del dsPIC30F2010

istruzioni di salto e quelle di confronto e salto che hanno durata doppia. Caso a sé è invece l’istruzione di divisione che richiede 19 cicli (ottenibili con un apposito ciclo REPEAT) per fornire il quoziente e il resto di una divisione. In tal senso sottolineiamo come il nostro dispositivo sia in grado di svolgere operazioni aritmetiche sia tra numeri interi, con segno o no, che tra numeri frazionari in formato 1.15.

5.4.1 Le periferiche utilizzate

Visto che il software di controllo realizzato si basa essenzialmente su quattro processi che vengono ciclicamente eseguiti, vogliamo cercare di spiegare dettagliatamente le funzionalità delle periferiche utilizzate all’interno di ciascun processo. Il primo processo si occupa dell’acquisizione del numero di giri del motore e sfrutta il modulo Input Capture, avente come base dei tempi il Timer2. Per il processo di acquisizione del carico applicato, si sfrutta il convertitore A/D interno al dsPIC. Per il processo di accensione si sfrutta il Timer1, mentre per il processo della gestione PWM del solenoide, si sfrutta il modulo Output Capture con il Timer3 come base dei tempi. Per questo motivo passiamo ad una descrizione più dettagliata dei suddetti moduli.

5.4.2. Modulo Timer 1

Il modulo Timer1 è un costituito da un registro TMR1 a 16 bit che può svolgere la funzione di Timer, di contatore sincrono o di contatore asincrono, sulla base della configurazione specificata nel registro a 16 bit T1CON. Nella modalità Timer, il modulo incrementa di uno il contenuto del registro TMR1 ad ogni istruzione eseguita, fino al raggiungimento del contenuto specificato nel registro PR1; a quel punto il modulo si resetta e ricomincia a contare. Inoltre è anche possibile impostare un opportuno valore di prescaler, in modo che il registro TMR1 si incrementi ogni n istruzioni con n fattore di prescaler (1,8,64,256). Se invece il modulo funziona da contatore sincrono si ha che il registro TMR1 si incrementa ogni qualvolta riceve un fronte in salita di un opportuno segnale di clock esterno applicato sul piedino T1CK, opportunamente sincronizzato con il clock interno (TCY). Infine quando il modulo

funziona da contatore asincrono si ha che il registro TMR1 si incrementa ad ogni fronte in salita del segnale di clock applicato sul piedino T1CK. Con riferimento alla fig. 5.28 si nota come al raggiungimento del contenuto specificato in PR1, venga settato il flag T1IF, appartenente al registro IFS0 (controllore delle interruzioni); tale evento genera effettivamente un’interruzione di programma se e solo se è stato precedentemente

settato anche il flag T1IE di abilitazione dell’interruzione, presente nel registro di controllo IEC0. In ogni caso deve essere cura del programmatore ripulire il flag T1IF ogni qualvolta si verifica il match tra TMR1 e PR1, al fine di poter riconoscere correttamente i successivi matching tra i due registri.

Figura 5.28 – Schema a blocchi del modulo Timer1

Si può anche far funzionare il modulo in modalità gated time accumulation, settando il bit TGATE; in questo modo il contenuto di TMR1 viene effettivamente incrementato ad ogni colpo di clock, solo se il valore del segnale T1CK viene rilevato allo stato logico alto. Infine ciò che effettivamente distingue questo timer dagli altri due presenti nel dispositivo è la possibilità di operare in modalità Real-Time, sfruttando come clock l’oscillatore interno a basso consumo (Low Power) a 32 kHz, abilitato dal bit di controllo LPOSCEN.

5.4.3 I moduli Timer2 e Timer3

Questi due moduli sono molto simili nel funzionamento al Timer 1 tranne che per il fatto che è possibile unirli in un unico Timer a 32 bit settando l’apposito bit di controllo T32 presente nel registro di configurazione T2CON; inoltre nessuno dei due può utilizzare il clock fornito dall’oscillatore interno a 32 kHz. Nel caso in cui sia abilitato il timer a 32 bit, si ha che il contenuto di TMR2 costituisce la parte meno significativa del

registro a 32 bit di conteggio, mentre il registro TMR3 ne rappresenta la parte più significativa. Lo stesso vale per i registri PR2 e PR3 (vedi fig. 5.29). Se invece i due moduli vengono impostati per funzionare separatamente (vedi figg. 5.30-5.31), possono essere utilizzati come base dei tempi per i moduli Input Capture ed Output Capture; in questo caso entrambi i moduli possono essere impostati come timer, contatori sincroni o contatori asincroni a 16 bit, con l’unica differenza che il Timer2 consente una sincronizzazione del clock applicato esternamente, mentre il Timer3 può fungere da trigger per il convertitore A/D.

Figura 5.30 – Schema a blocchi del modulo Timer2 a 16 bit

5.4.4 Il modulo Input Capture

Il modulo Input Capture è utilizzato per acquisire il contenuto di uno dei due timer (2/3) a 16 bit, ogni qualvolta si presenta un evento prestabilito sul piedino di ingresso associato alla periferica (nel nostro caso IC1, ma tutto quanto vale anche per gli altri ingressi ICx presenti). Impostando i bit ICM<2:0> del registro di configurazione IC1CON è dunque possibile campionare il valore del timer selezionato nei seguenti modi:

• Ad ogni fronte in discesa del segnale applicato al piedino IC1 • Ad ogni fronte in salita del segnale applicato al piedino IC1 • Ogni quattro fronti in salita del segnale applicato al piedino IC1 • Ogni sedici fronti in salita del segnale applicato al piedino IC1

• Ad ogni fronte in salita e ad ogni fronte in discesa del segnale applicato al piedino IC1

Questo modulo si presta pertanto ad effettuare misure di frequenza o di periodo o a gestire ulteriori sorgenti esterne di interruzione, applicate sui piedini di ingresso ICx. Il modulo possiede un buffer FIFO a quattro livelli dove vengono memorizzati fino a quattro valori acquisiti; impostando i bit ICI<1:0> del registro IC1CON, è possibile selezionare ogni quante acquisizioni il modulo genera una richiesta di interruzione, settando il flag IC1IF. Analogamente a quanto visto per i timer, tale richiesta si trasforma in un’effettiva interruzione di programma, solamente se è stato preventivamente settato il bit IC1IE di abilitazione presente nel registro IEC0. In fig. 5.32 si riporta lo schema a blocchi del modulo, dove si evidenziano i flag ICBNE (se settato significa che il buffer non è vuoto) e ICOV (se settato significa che si è verificato una quinta acquisizione senza alcuna lettura dal buffer ed è necessario effettuare quattro letture, prima di poter acquisire nuovamente dei dati); infatti ad ogni lettura dal buffer, si ha un conseguente avanzamento dei dati memorizzati nella struttura del buffer, in accordo alla logica FIFO. Si noti inoltre come una lettura dal buffer, prima di un’acquisizione, porti ad un dato privo di significato. Il modulo può anche essere utilizzato per far entrare o uscire il dsPIC dalla modalità SLEEP, a seguito di un evento rilevato su di un piedino ICx.

Figura 5.32 – Schema a blocchi del modulo Input Capture

5.4.5 Il modulo Output Compare

Il modulo Output Compare è utilizzato per la generazione di impulsi a durata variabile; tale generazione avviene mediante un confronto tra il contenuto del registro di conteggio del timer selezionato (TMR2 o TMR3) ed il contenuto di uno o due registri di riferimento (OC2R e OC2RS nel nostro caso), in base alla modalità di funzionamento prescelta, settando adeguatamente i bit OCM<2:0> del registro di configurazione OC2CON. Le modalità di funzionamento possibili sono:

• Single Compare Match: per la commutazione di un’uscita al riconoscimento di un certo evento predefinito

• Dual Compare Match: per la generazione di un singolo impulso di uscita o di una successione continua di impulsi in uscita

• Pulse Width Modulation: per la generazione di una forma d’onda PWM in uscita, avente duty cycle specificato nel registro OC2RS

Nella modalità Single Compare, si ha una commutazione dell’uscita scelta, quando il Timer impostato come base dei tempi, raggiunge il valore specificato in OC2R; si può scegliere se avere una transizione positiva o negativa. Il flag OC2IF viene invece settato due cicli di clock dopo tale evento e necessita della consueta ripulitura software da parte

del programmatore, al fine di permettere un corretto riconoscimento di più eventi nel tempo.

Nella modalità Dual Compare Match si ha un impulso di durata determinata dai valori specificati in OC2R e in OC2RS; il primo registro infatti contiene il valore di conteggio del TMRx scelto, per il quale si ha l’inizio dell’impulso, mentre invece OC2RS contiene il valore di conteggio di TMRx per il quale si ha la fine dell’impulso. Questo impulso può essere unico o invece può essere continuamente generato con la durata prescelta. Nella modalità PWM il registro PRx del timer scelto contiene il periodo del segnale PWM da generare; il registro OC2RS invece contiene il valore di duty cycle desiderato, mentre il registro OC2R normalmente non è accessibile in scrittura, tranne che per la fase di accensione del modulo, in cui è possibile impostare il valore di duty cycle iniziale. Inoltre è possibile decidere se abilitare l’opzione di protezione FAULT che consente,se attivata, di porre in alta impedenza i piedini OCx in presenza di un livello logico 0 sul piedino OCFA, indipendentemente dallo stato di conteggio del timer utilizzato come base dei tempi. Tale condizione permane fino alla rimozione del livello 0 sul piedino OCFA o fino ad una nuova inizializzazione del modulo.

In caso di modalità SLEEP del dispositivo, il modulo Output Capture mantiene sul piedino d’uscita OCx l’ultimo valore generato, prima dell’entrata del dispositivo in tale modalità. In caso invece di modalità IDLE del dsPIC si ha che il modulo può continuare a funzionare solamente se il Timer associato può continuare a funzionare nella suddetta modalità. In fig. 5.33 riportiamo la struttura a blocchi del modulo, mentre in figg. 5.34 e 5.35 si evidenziano le proprietà del segnale PWM generato. Nel nostro progetto tale segnale è quello destinato al pilotaggio del solenoide del carburatore (10 Hz).

Figura 5.33 – Struttura a blocchi del modulo Output Capture

Figura 5.34 – Formula del periodo del segnale PWM generato

5.4.6 Il convertitore Analogico-Digitale

Il convertitore A/D presente nel dispositivo presenta le seguenti caratteristiche: • Conversione ad approssimazioni successive (SAR)

• Velocità di conversione pari a 500 kS/s

• 6 ingressi analogici (AN0_AN5) multiplexati in 4 amplificatori differenziali S/H • Piedini di ingresso per dei riferimenti di tensione esterni (VREF+_VREF-)

• Campionamento simultaneo fino ad un massimo di 4 piedini • Modalità di scansione automatica dei canali di ingresso • Trigger di conversione selezionabile tra più sorgenti

• Buffer per la memorizzazione dei risultati a 16 bit con profondità sedici (ADCBUF0_ADCBUFF)

• Modalità selezionabile di riempimento del buffer • Quattro formati di memorizzazione dei dati acquisiti

• Impostazione delle attività del modulo all’interno delle modalità IDLE e SLEEP del dispositivo

In fig. 5.36 si riporta la struttura a blocchi del modulo. Il modulo annovera sei registri di configurazione a 16 bit:

• ADCON1 per l’accensione del modulo e la configurazione della sequenza del campionamento e conversione

• ADCON2 per la scelta del canale da utilizzare e per la modalità di generazione di un’interruzione di programma

• ADCON3 per l’impostazione dei tempi di campionamento e conversione • ADCHS per la scelta dei segnali di riferimento dei vari canali

• ADPCFG per la configurazione dei piedini analogici

• ADCSSL per la selezione dei canali da scansionare nell’apposita modalità

Dalla fig. 5.36 è possibile comprendere le due fasi in cui si struttura la sequenza di acquisizione del dato: dapprima viene effettuato il campionamento da parte degli amplificatori Sample and Hold di uno o più dei quattro canali CH0_CH4 connessi ai piedini analogici di ingresso mediante due multiplexer (MUX A e MUX B). In caso di campionamento di più canali, questo può essere sequenziale o simultaneo (bit SIMSAM di ADCON1), in base all’esigenza della particolare applicazione. I bit di controllo dei multiplexer sono invece presenti in ADCHS e consentono di passare da uno all’altro, tra un campionamento ed il successivo.

Figura 5.36 – Schema a blocchi del convertitore A/D

Inoltre è possibile effettuare un campionamento di più segnali analogici di ingresso in scansione. Per quanto concerne la temporizzazione della sequenza campionamento-conversione, si ha che il tempo di campionamento è l’intervallo temporale per il quale il Sample and Hold è connesso al piedino di ingresso; tale evento può essere iniziato manualmente settando il bit SAMP di ADCON1 all’avvio e resettandolo alla fine, oppure può essere gestito automaticamente dal modulo mediante un suo segnale di trigger interno. Il tempo di conversione è invece il tempo che il convertitore A/D (SAR) impiega a convertire il dato mantenuto dal Sample and Hold; in particolare è richiesto un tempo TAD (>154 ns) per convertire ciascun bit più un ciclo di clock addizionale,

cosicché per la conversione completa del dato sono necessari 12 TAD. Il legame tra TAD

Figura 5.37 – Legame tra tempo di conversione di bit e tempo di clock

I bit ADCS<5:0> sono presenti nel registro ADCON3.

Quando è trascorso il tempo necessario alla conversione, il modulo segnala tale operazione mediante il bit DONE di ADCON1 ed il risultato viene memorizzato nella RAM dual port ADCBUF nel formato numerico selezionato dai bit FORM<1:0> in ADCON1, sfruttando entrambi i byte del buffer o uno soltanto sulla base della configurazione specificata dal bit BUFM di ADCON2. Infine in base alla configurazione specificata dai bit SMPI<3:0> si ha una richiesta di interruzione (settaggio del bit ADIF di IFS0) ogni N conversioni effettuate, con 0< N<16, la quale comporta un’effettiva interruzione di programma soltanto se è stato abilitato, durante l’inizializzazione del dispositivo, il bit ADIE in IEC0.

Nel nostro progetto il convertitore è stato configurato per operare una sequenza campionamento-conversione in modalità manuale, con un unico canale CH0 avente come ingresso il segnale applicato al piedino AN1. Concludiamo la trattazione del modulo riportando la temporizzazione adottata nel nostro progetto:

5.4.7 Cenni al DSP engine

Nonostante che in questo progetto non sia stato necessario ricorrere alle grandi capacità computazionali del dispositivo, ci riserviamo di dare una descrizione sommaria del modulo DSP presente all’interno del dsPIC30F2010. Questo modulo hardware si presenta con:

• Un moltiplicatore ad elevata velocità 17 bit*17 bit • Un barrel shifter

• Un sommatore con segno a 40 bit con due accumulatori bersaglio ed una logica configurabile di arrotondamento e di saturazione.

In fig. 5.39 riportiamo la struttura a blocchi del DSP:

Figura 5.39 – Struttura a blocchi del DSP

Il moltiplicatore è in grado di svolgere operazioni tra interi con segno e senza segno, in base al significato attribuito al diciassettesimo bit (settato a 0 per i numeri senza segno); in ogni caso viene fornito un risultato su 32 bit. Inoltre, configurando adeguatamente

tale blocco, è possibile effettuare operazioni tra numeri frazionari in formato 1.15 (Q15), ottenendo in uscita un dato in formato 1.31 (Q31).

Per quanto concerne il sommatore, questo può effettuare operazioni di somma e differenza su numeri a 40 bit, utilizzando uno od entrambi gli accumulatori (AccA,AccB) come sorgenti o destinazioni delle suddette operazioni; durante l’esecuzione di istruzioni quali ADD e LAC è inoltre possibile shiftare di N bit, con N<16, i risultati prima che vengano effettivamente memorizzati. Questa operazione viene eseguita mediante il barrel shifter capace di eseguire shift aritmetici a sinistra di 16 posizioni in un singolo colpo di clock o di 15 posizioni a destra; i dati da shiftare possono essere quelli presenti negli accumulatori, ma anche quelli provenienti dal bus dati X.

5.4.8 Cenni all’interfaccia UART

L’interfaccia UART (Universal Asynchronous Receiver Transmitter) è un modulo di trasmissione dati seriale full-duplex, tipicamente utilizzato per interfacciare il dsPIC con un personal computer, utilizzando lo standard RS232. Nel nostro progetto abbiamo infatti deciso di aggiungere un’opportuna circuiteria atta a realizzare una trasmissione seriale, al fine di poter facilmente adattare il nostro sistema a diverse specifiche future: in questo modo è infatti possibile modificare alcuni parametri del software di gestione del dsPIC direttamente da un computer. Affinché siano adattati i segnali di I/O del dsPIC, aventi livelli logici TTL [0; 5V], allo standard RS-232 con livelli logici +12V, è stato necessario aggiungere un circuito di interfaccia come evidenziato nel paragrafo 5.5.11.

5.4.9 Watch Dog Timer

Questo modulo presente nella maggior parte dei microcontrollori embedded è presente all’interno del dsPIC, con l’intento di migliorarne l’affidabilità. Da un punto di vista hardware tale blocco si presenta come un timer in grado di segnalare eventuali malfunzionamenti software; se infatti durante un flusso di programma costituito da un main che si ripete ciclicamente, si verifica una situazione di blocco (vedi loop senza uscita), il timer evita al processore di rimanere per sempre all’interno di tale situazione di blocco, resettandolo e facendo ripartire da capo l’esecuzione del main. Una buona tecnica di programmazione prevede pertanto di abilitare tale periferica con un fondo scala temporale decisamente più grande rispetto alla durata del programma da realizzare; ripulendo alla fine di ogni main completato tale timer, lo teniamo aggiornato sul corretto evolversi del flusso di programma. In caso di blocco prolungato il modulo interviene, resettando così il dsPIC. In fig. 5.40 riportiamo lo schema a blocchi di tale dispositivo:

Figura 5.40 – Schema a blocchi del Watchdog timer

L’abilitazione del timer è sancita dal valore del bit FWDTEN, presente nel registro di configurazione FWDT. Tale registro è scritto durante la programmazione del dispositivo. Il modulo è comunque attivabile via software, anche nel caso di mancata

che viene azzerato ad ogni reset del processore. Il clock del timer è l’oscillatore interno LPRC a 512 kHz diviso per un fattore 4; in questo modo il timer ha un fondo scala di 2ms. Tale fondo scala è però estendibile mediante l’utilizzo di due prescaler A e B che possono allungare il tempo di conteggio sino a 16,3 s.

5.4.10 Configurazione del clock del microcontrollore

Avendo utilizzato nel progetto una sorgente di clock a 40 MHz, abbiamo impostato la configurazione EC per la circuiteria di acquisizione di tale segnale. In questo modo abbiamo portato a lavorare il dsPIC30F2010 a 10 MIPS; tale velocità è stata ritenuta sufficientemente grande per elaborare un controllo in tempo reale del motore. In fig. 5.41 si riportano i dettagli temporali del flusso di chiamata ed esecuzione delle istruzioni, rispetto al clock scelto (FOSC = 40 MHz; TCY = 100 ns) e al valore del

Program Counter:

5.5 I software utilizzati nella progettazione

Vista la natura analogica-digitale del progetto realizzato, siamo ricorsi a diversi strumenti software per le varie fasi di progettazione. Per la parte di simulazione elettrica dei vari circuiti di interfaccia, abbiamo fatto ricorso al pacchetto OrCAD 9.2 ed in particolare ai suoi applicativi OrCAD Capture CIS e PSpice AD. Mediante il primo applicativo abbiamo disegnato le reti elettriche di nostro interesse che sono poi state simulate con il secondo, arrivando così a definire i vari circuiti di interfaccia illustrati nei precedenti paragrafi. Per quanto concerne la realizzazione del circuito stampato, abbiamo effettuato la sbrogliatura della netlist generata dal Capture, mediante l’applicativo OrCAD Layout Engineer’s Edition; in tale ambiente abbiamo provveduto pertanto a posizionare fisicamente i componenti prescelti ed illustrati nei precedenti paragrafi, avendo cura di realizzare un’occupazione del circuito stampato, tale da rendere facilmente accessibile ed eventualmente sostituibile qualunque dispositivo durante la fase di collaudo. Per questo motivo sono stati tendenzialmente evitati componenti a montaggio superficiale e si è effettuata una realizzazione non ottimizzata in termini di occupazione della superficie del circuito stampato.

Per quanto concerne invece l’ambiente di programmazione del dsPIC30F2010, è stato utilizzato l’ambiente MPLAB IDE v7.00 con la suite MPASM30 della Microchip, del quale parleremo più approfonditamente nei prossimi paragrafi.

5.6 La realizzazione del circuito stampato

Nelle seguenti figure si riportano i layer e le foto del circuito stampato realizzato:

Figura 5.42 – Layer Componenti discreti (Top)

Figura 5.44 – BOTTOM Layer