Capitolo 6

Analisi e Progettazione di un Moltiplicatore

di Tensione Ottimizzato Mediante Simulazioni

e Modelli Semplificati

6.1 Simulazioni Spice del Sistema di Accensione

Nel capitolo precedente sono stati messi in evidenza i limiti del sistema di accensione realizzato, legati principalmente alle prestazioni del moltiplicatore di tensione.

Per cercare di individuare le cause di questi limiti, per prima cosa è stata effettuata una simulazione non solo del moltiplicatore di tensione ma dell’intera parte del sistema adibita alla generazione dell’alta tensione. Lo schema circuitale è mostrato in Fig.6.1. Per ogni componente, eccetto che per i mosfet dello stadio di uscita del driver, sono state utilizzate le model fornite dal costruttore.

RADDRIZZATORE Vout MOLTIPLICATORE GND IN OUT 0 PARAMETERS: P = 10u A = 2 C = 1n T = 50n STADIO DI USCITA DEL DRIVER CIRCUITO DI BOOTSTRAP HALF BRIDGE R5 2 V14 TD = 11u TF = {T} PW = {P/A-3u} PER = {P} V1 = 0 TR = {T} V2 = 15 MOLTIPLICATORE DI TENSIONE V15 TD = 10.5u TF = {T} PW = {P/A-2u} PER = {P} V1 = 15 TR = {T} V2 = 0 0 VB VCC VCC C3 1u V6 15Vdc D6 STTH512B M5C STP4N150 M6D STP4N150 0 HV IN_H OUT RADDRIZZATORE IN_L RIF V16 FREQ = 50 VAMPL = 1 VOFF = 0 HON R6 2 S R7 2 HV M1A STP4N150 M4B STP4N150 0 V13 TD = 9.5u TF = {T} PW = {P/A} PER = {P} V1 = 15 TR = {T} V2 = 0 Vs HOP

Figura 6.1 Schema Circuitale del sistema di accensione

Come si può osservare da Fig.6.1, la simulazione è stata eseguita considerando una tensione sinusoidale in ingresso al raddrizzatore con Vmax = 500 V, quindi (Par.5.3) in uscita dal raddrizzatore sarà disponibile una tensione continua di valore pari a 1000 V; la frequenza dei generatori di onda rettangolare che pilotano il Low Side dell’Half Bridge e lo stadio d’uscita del driver è pari a 100 kHz, per cui il segnale in ingresso del Moltiplicatore sarà un onda PWM a 100 kHz con ampiezza pari a 1000 V. Per rendere più accurata la simulazione i generatori sono stati opportunamente ritardati, in modo tale da tenere in considerazione l’intervallo di dead-time presente ad ogni transizione dei segnali di controllo dei mosfet dell’Half Bridge. Durante questo intervallo di tempo entrambi i mosfet sono spenti, lo scopo è quello di ridurre la corrente di cortocircuito ed evitare la rottura dei dispositivi (driver e mosfet) nel caso in cui si verificasse l’accensione contemporanea di entrambe i mosfet.

In Fig.6.2 sono messi a confronto gli andamenti nel tempo della tensioni in uscita del moltiplicatore in tre casi diferenti:

1. Situazione Ideale: Nessun carico connesso al moltiplicatore;

3. Influenza del Sistema di Misura: Primo partitore e sonda di tensione connessi al moltiplicatore.

Osservando l’andamento della tensione e a vuoto (curva in verde) si può dedurre che il sistema dovrebbe essere in grado di generare tensioni prossime ai 15 kV, coerentemente con le precedenti simulazioni (5.13). La presenza del carico, rappresentato dai due partitori di tensione (Fig.5.5), causa una riduzione del valore di regime pari a ∆V ≈ 2000 V, ma consentono comunque al sistema di superare i 10 kV di tensione d’uscita e soddisfare quindi le specifiche. Da Fig.6.2 si osserva inoltre che l’andamento della tensione nel terzo caso, segue praticamente quello del secondo. Da questo si può dedurre che ad influenzare il valore di regime della tensione di uscita del moltiplicatore è principalmente la presenza del primo partitore.

Sempre in Fig.6.2 è stato marcato il punto in cui, con entrambe i partitori connessi (curva in rosso), la tensione raggiunge i 3 kV. Tale valore viene raggiunto in 256 μs circa, mentre dalle misure sperimentali riportate in Fig.5.11 e Fig.5.12 emerge che il sistema reale impiega un tempo superiore al millisecondo.

Figura 6.2 Andamento della tensione di uscita del moltiplicatore in tre situazioni differnti: 1) Assenza di carico, 2) Entrambe i partitori connessi, 3) Primo partitore e sonda di misura connessi

Questi risultati ci portano a pensare che la presenza di parametri parassiti all’interno sistema realizzato, in particolare nel moltiplicatore di tensione, possano essere la causa della discrepanza tra le simulazioni e le misure.

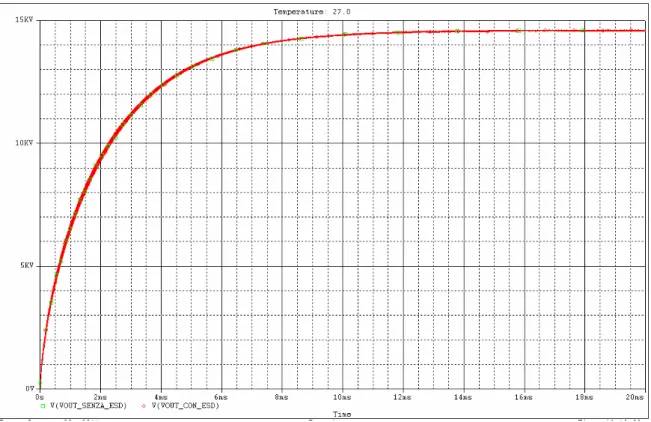

Per rendere più accurata la simulazione sono state considerate le ESD (Equivalent Series

Resistance) dei condensatori utilizzati per il moltiplicatore. Utilizzando un RLC Meter è

stata valutata la ESD dei condensatori alla frequenza di 100 kHz. Essendo i condensatori utilizzati tutti uguali con C = 1nF è stata effettata la misura per 10 condensatori e si è assunta come ESD il valore medio delle misure. Il valore così ottenuto è pari a 25 Ω, in accordo con i parametri forniti dal costruttore [17] . Fig.6.4 mostra lo schema circuitale modificato del moltiplicatore, in Fig.6.3, invece, è riportato l’andamento della tensione d’uscita.

Figura 6.4 Andamento della tensione d’uscita del Moltiplicatore con e senza le ESD

Da Fig.6.3 è evidente che la presenza delle ESD, dato il loro basso valore, non ha praticamente alcuna influenza sull’andamento della tensione di uscita del moltiplicatore. Infatti la costante di tempo introdotta è pari a τ = 25 ns molto minore del periodo di commutazione del segnale di pilotaggio ( 10 us).

C4 3 1n R7 25 C4 5 1n R8 25 C4 7 1n R9 25 C4 9 1n R1 0 25 C5 0 1n R1 1 25 C5 1 1n R1 2 25 C5 2 1n R1 3 25 C5 3 1n R1 4 25 C5 4 1n R1 5 25 C5 5 1n R2 5 25 C5 6 1n R2 6 25 R4 7 25 C7 8 1n C3 5 1n R4 8 25 R3 25 C6 7 1n R3 7 25 C6 8 1n C3 4 1n R3 8 25 R1 7 25 C6 9 1n C5 7 1n R3 9 25 R2 7 25 C7 0 1n R4 0 25 C7 1 1n R4 1 25 C7 2 1n C3 6 1n R4 2 25 R1 8 25 C7 3 1n R4 3 25 C7 4 1n R4 4 25 C7 9 1n R4 9 25 C8 0 1n C3 8 1n R5 0 25 R1 9 25 C5 8 1n R2 8 25 GN D D6 1 ST T H 11 2 D6 2 S TTH 1 1 2 C8 1 1n R5 1 25 C8 2 1n C4 0 1n R5 2 25 R2 0 25 C5 9 1n R2 9 25 D6 3 S TTH 1 1 2 D6 4 ST T H 112 D6 5 ST T H 11 2 IN D6 6 S TTH 1 1 2 C8 3 1n D6 7 ST T H 11 2 R5 3 25 C6 1 1n D6 8 ST T H 11 2 C8 4 1n R3 1 25 C4 2 1n OU T R5 4 25 D6 9 ST T H 112 D7 0 ST T H 11 2 C6 0 1n R2 1 25 R3 0 25 D7 1 S TTH 1 1 2 D7 2 ST T H 112 D7 3 S TTH 1 1 2 D7 4 ST T H 11 2 D7 5 ST T H 112 D7 6 ST T H 11 2 D7 7 ST T H 112 D7 8 S TTH 1 1 2 C6 2 1n R3 2 25 C3 1 1n D7 9 ST T H 11 2 D8 0 S TTH 1 1 2 D8 1 S TTH 1 1 2 D8 2 S TTH 1 1 2 D8 3 ST T H 11 2 D8 4 ST T H 112 D8 5 S TTH 1 1 2 D8 6 ST T H 11 2 D8 7 ST T H 112 D8 8 ST T H 11 2 D8 9 S TTH 1 1 2 D9 0 S TTH 1 1 2 C3 7 1n C3 9 1n C4 1 1n C4 4 1n C4 6 1n C4 8 1n C6 3 1n R3 3 25 C6 4 1n C3 2 1n R3 4 25 R1 6 25 C6 5 1n R3 5 25 C6 6 1n R3 6 25 R2 2 25 R1 25 R2 3 25 R2 4 25 R4 25 R5 25 R6 25 C7 5 1n R4 5 25 C7 6 1n C3 3 1n R4 6 25 R2 25 C7 7 1n

6.2 Analisi del Moltiplicatore mediante Modelli Semplificati

Dalle simulazioni riportate nel paragrafo precedente non risulta ancora chiaro il motivo per cui il sistema realizzato abbia prestazioni così lontane da quelle previste, tanto che è sembrato lecito pensare che le model dei dispositivi, in particolare dei diodi utilizzati, potessero non rispecchiare fedelmente il comportamento reale.

Convinti che il problema vada ricercato nel moltiplicatore, è stato studiato mediante simulazioni, il comportamento di un Cockroft-Walton a tre stadi, utilizzando condensatori e diodi ideali.

L’obbiettivo di questo studio è stato quello di poter trarre informazioni sul funzionamento ideale del moltiplicatore e di conseguenza ricavarne un modello analitico, che risultasse utile sia per comprendere gli effetti delle discrepanze tra simulazioni e misure, sia per la progettazione di un moltiplicatore ottimizzato, al fine di aumentarne il guadagno di tensione reale e di ridurre il tempo di salita della tensione d’uscita.

D3 D94 D95 IN D96 C1 {C} C2 {C} C3 {C} C4 {C} C5 {C} C6 {C} GND D1 D2 OUT

Figura 6.5 Schema circuitale di un moltiplicare a 3 stadi

+ -+ -INV S1 + -+ -DIR S2 + -+ -INV S3 + -+ -INV S5 + -+ -DIR S4 + -+ -DIR S6 C1 {C} C2 {C} C3 {C} C4 {C} C5 {C} C6 {C} GND IN OUT

Figura 6.6 Schema circuitale di un moltiplicare a 3 stadi ideale

In Fig.6.5, in alto, è riportato lo schema tipico di un moltiplicatore a 3 stadi, analogo a quelli visti fino ad ora, in basso invece è mostrato lo schema circuitale del moltiplicatore studiato dove i diodi sono sostituiti da interruttori con le seguenti caratteristiche:

.model DIR VSWITCH Roff=1e12 Ron=10e-12 Voff=0.0 Von=1e-2 .model INV VSWITCH Roff=1e12 Ron=10e-12 Voff=0.0 Von=-1e-2

Dove con DIR si indicano gli interruttori la cui polarità indicata nello schema coincide con quella che manda in conduzione il corrispondente diodo, mentre con INV quelli la cui polarità è invertita.

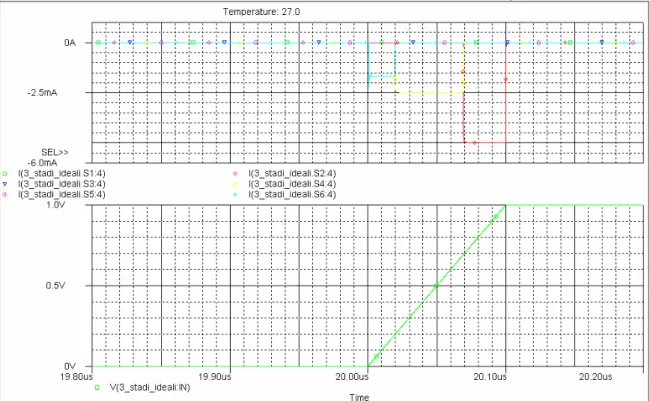

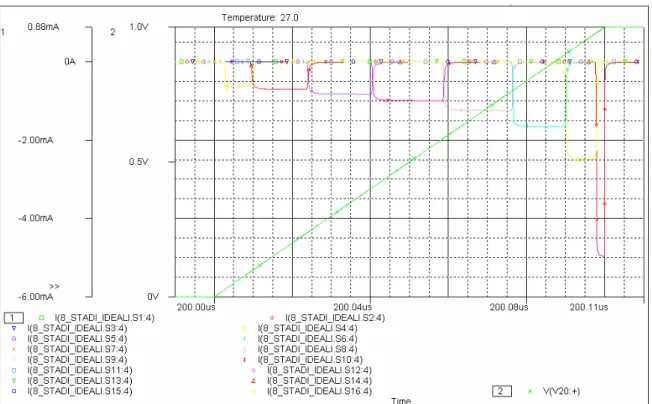

Fig.6.7 mostra, in alto, gli andamenti delle correnti presenti sugli interruttori, mentre in basso quelli del segnale d’ingresso e della tensione d’uscita del moltiplicatore.

I risultati sono stati ottenuti nelle seguenti condizioni:

• Circuito pilotato da un onda quadra con frequenza pari e 100 kHz e Ampiezza 1V; • Condensatori uguali con C = 1nF.

Figura 6.7 In Alto: Andamento della corrente sugli interruttori. In Basso: Andamento del segnale d’ingresso e della tensione d’uscita del moltiplicatore

Come ci si poteva aspettare, si osserva che man mano che la tensione d’uscita tende al valore di regime, l’ampiezza delle correnti che attraversano gli interruttori tende a diminuire, questo è dovuto al fatto che in corrispondenza dei gradini del segnale d’ingresso i condensatori saranno già parzialmente carichi. In condizioni ideali, ovvero senza alcun elemento di perdita presente nel circuito ed in assenza di carico, quando i condensatori sono completamente carichi le correnti assumeranno valore nullo.

Informazioni più interessanti sono fornite dalle Figure 6.8 e 6.9, nelle quali sono state riportati gli andamenti delle correnti sugli interruttori quando in ingresso al circuito è

applicato un gradino negativo e un gradino positivo, corrispondenti in particolare alla terza e quarta commutazione del segnale d’ingresso nella simulazione di Fig.6.7.

Figura 6.8 Corrente sugli interruttori in un moltiplicatore a 3 stadi in presenza di un gradino negativo in ingresso

Figura 6.9 Corrente sugli interruttori in un moltiplicatore a 3 stadi in presenza di un gradino positivo in ingresso

In particolare da queste figure si può dedurre la sequenza di accensione degli interruttori in corrispondenza di ogni gradino. Fig.6.8 mostra che applicando un gradino negativo entrano in conduzione gli interruttori dispari, partendo dall’ultimo stadio fino al primo, fornendo così carica ai condensatori dispari, ossia quelli in alto (Fig.6.6).

Da Fig.6.9 si osserva che applicando un gradino positivo entrano in conduzione gli interruttori pari, sempre partendo dall’ultimo stadio fino al primo, fornendo così carica ai condensatori pari, ovvero a quella in basso (Fig.6.6).

Il procedimento appena descritto si ripete ad ogni gradino del segnale d’ingresso fino a quando i condensatori non saranno completamente carichi.

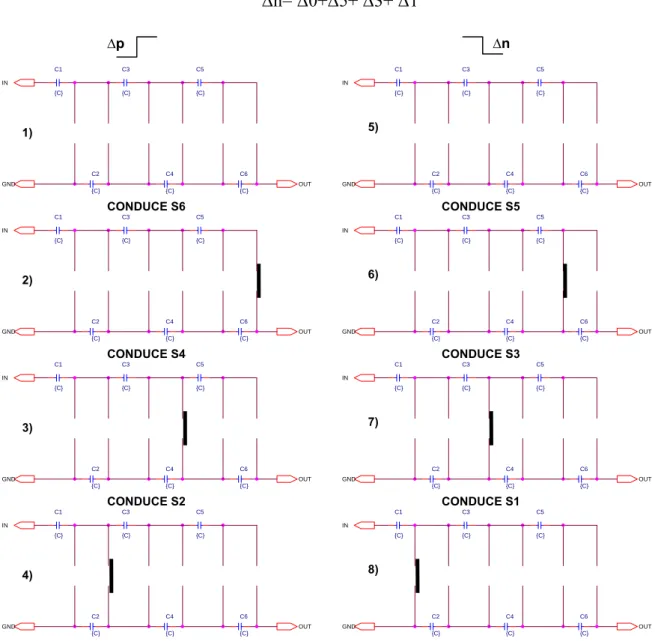

La cosa interessante e che il comportamento resta lo stesso indipendentemente dal numero di stadi. A conferma di quanto appena detto in Fig.6.10 e Fig.6.11 sono mostrati gli andamenti delle correnti sugli interruttori per un Cockroft-Walton a 8 stadi.

Figura 6.10 Corrente sugli interruttori in un moltiplicatore a 8 stadi in presenza di un gradino negativo in ingresso

Da quanto osservato si può dedurre che il gradino in ingresso al circuito si ripartisce in modo tale che ogni parte di esso mandi in conduzione uno degli interruttori del circuito, partendo dall’ultimo stadio fino al primo.

Per capire come avviene la ripartizione del gradino è utile una rappresentazione circuitale della sequenza di accensione degli interruttori, come quella riportata in Fig.6.12. Si noti

che gli interruttori spenti sono schematicamente rappresentati da collegamenti interrotti, mentre un ponticello fra questi collegamenti indica che l’interruttore è acceso.

Figura 6.11 Corrente sugli interruttori in un moltiplicatore a 8 stadi in presenza di un gradino positivo in ingresso

Ognuna delle configurazioni circuitali assunte dal moltiplicatore in Fig.6.12, sarà sollecitata in ingresso, da una frazione del gradino positivo Δp (1-2-3-4) e da una frazione del gradino negativo Δn (5-6-7-8). La ripartizione dei gradini avviene quindi nel modo seguente:

• Gradino Positivo

Δ0 = Parte del gradino che manda in conduzione D6 Δ6 = Parte del gradino che manda in conduzione D4 Δ4 = Parte del gradino che manda in conduzione D2 Δ2 = Δp - Δ0 -Δ6 - Δ4

Δp= Δ0+Δ6+ Δ4+ Δ2 • Gradino Negativo

Δ5 = Parte del gradino che manda in conduzione D3 Δ3 = Parte del gradino che manda in conduzione D1 Δ1 = Δn – Δ0 –Δ5- Δ3 Δn= Δ0+Δ5+ Δ3+ Δ1 ∆p ∆n C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} 5) 1) CONDUCE S5 CONDUCE S6 6) 2) CONDUCE S3 CONDUCE S4 7) 3) CONDUCE S1 CONDUCE S2 8) 4)

Figura 6.12 Rappresentazione circuitale della sequenza di accensione degli interruttori per un moltiplicatore a 3 stadi, in presenza di gradino positivo a sinistra e di gradino negativo a destra

Da questo se ne deduce che, per descrivere l’evoluzione della tensione sui nodi del circuito in un periodo del segnale d’ingresso, è sufficiente analizzare le otto configurazioni circuitali di Fig.6.12, assumendo come valore della tensione d’ingresso la corrispondente frazione Δ i del gradino applicato.

Inoltre i diversi Δi in cui si ripartiscono i gradini possono essere ricavati imponendo, durante lo studio di ogni configurazione, le condizioni sulle tensioni ai nodi del circuito che indicano il termine della configurazione stessa e l’inizio di quella successiva.

Le relazioni ottenute non verranno riportate in queste tesi, in quanto al momento il funzionamento del modello è stato accertato tramite simulazioni, mentre da un punto di vista analitico è ancora in fase di validazione.

Essendo il funzionamento del circuito indipendentemente dal numero di stadi (Fig.6.10-6.11), la rappresentazione di Fig.6.12 può essere estesa facilmente ad un numero n generico di stadi e quindi il modello ottenuto può a sua volta essere generalizzato ad un n qualsiasi.

Da quanto detto e osservando ancora Fig.6.12, è evidente che ad ogni gradino, analizzando le n + 1 configurazioni circuitali, per ogni nodo del circuito si avranno a disposizione n +

1 punti che rappresentano l’evolversi delle tensioni su ogni nodo. E’ chiaro che per un

numero elevato di stadi ed un numero elevato di commutazioni del segnale d’ingresso, l’analisi del modello diventa pesante sia da un punto di vista teorico che da un punto di vista computazionale.

L’obbiettivo del modello è quello di valutare l’andamento della tensione d’uscita, per cui in corrispondenza di ogni gradino sarebbe sufficiente avere a disposizione un solo valore di tensione. Il modello può essere semplificato in questo senso, riducendo le n + 1 configurazioni di Fig.6.12 ad un’unica configurazione. Da un punto di vista analitico, fare questo implica analizzare le relazioni di ogni singola configurazione e sostituirle di volta in volta durante lo studio delle configurazioni successive.

Per fare ciò, dopo aver generalizzato il modello per un generico numero n di stadi, è stato utilizzato MATLAB. In particolare sono state implementate due funzioni in grado di accettare come input il numero di stadi e restituire l’espressione delle tensioni sui nodi del circuito e quelle ai capi dei condensatori, in presenza di un gradino positivo e di un gradino negativo rispettivamente.

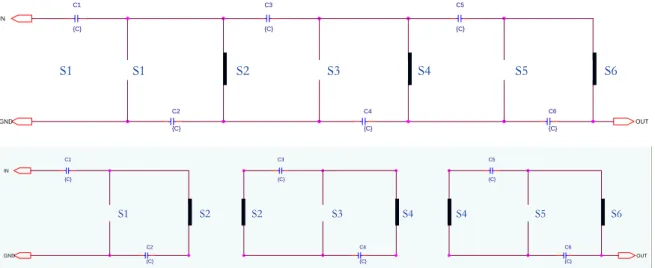

Dopo aver effettuato diverse prove al variare del numero di stadi, dalle relazione ricavate (che non riportiamo per quanto detto prima) è emersa una cosa interessante: considerando accesi tutti gli interruttori mandati in conduzione dal gradino applicato in ingresso (i pari per il gradino positivo, i dispari per quello negativo), e separando il moltiplicatore in più circuiti in corrispondenza di tali interruttori (Fig.6.13, Fig.6.14), dall’analisi dei circuiti

così ottenuti si ottengono gli stessi risultati ricavati dall’analisi precedentemente illustrata e basata sull’osservazione del comportamento del circuito attraverso simulazioni.

C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} S1 S1 S2 S3 S4 S5 S6 C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C}

Figura 6.13 In alto: Rappresentazione circuitale del moltiplicatore considerando accesi tutti i diodi mandati in conduzione da un gradino positivo applicato in ingresso. In basso: Circuiti ottenuti separando il moltiplicatore in corrispondenza degli interruttori accesi e che consentono di caratterizzare in maniera più semplice il comportamento del moltiplicatore.

Figura 6.14 In alto: Rappresentazione circuitale del moltiplicatore considerando accesi tutti i diodi mandati in conduzione da un gradino negativo applicato in ingresso. In basso: Circuiti ottenuti separando il moltiplicatore in corrispondenza degli interruttori accesi e che consentono di caratterizzare in maniera più semplice il comportamento del moltiplicatore.

Fig.6.15 mostra un confronto tra l’andamento della tensione di uscita di un Cockroft-Walton a 3 stadi ideale ottenuto mediante simulazione spice e quello ricavato dal modello, le condizioni di funzionamento sono le seguenti:

1. Simulazione:

• Condensatori uguali con C = 1nF;

S2 S3 S4 S6 IN C1 {C} GND S1 S2 S1 S3 S5 S4 S6 C6 {C} OUT C5 {C} C6 {C} IN C1 {C} C2 {C} GND OUT C3 {C} C4 {C} S1 S2 S3 S4S4 S5 S6S6 S1 S2 S3 S4 S5 S6 IN C1 {C} C2 {C} GND C3 {C} C4 {C} C5 {C} C6 {C} OUT S2 S2 S4 S4 S6 S1 S3 S5 C2 {C} C3 {C} C5 {C} C4 {C}

• Diodi sostituiti con Interruttori;

• Onda quadra in ingresso di Frequenza pari a 1 kHz e Ampiezza 1 kV. 2. Modello:

• Condensatori Uguali; • Ampiezza Gradino 1 kV.

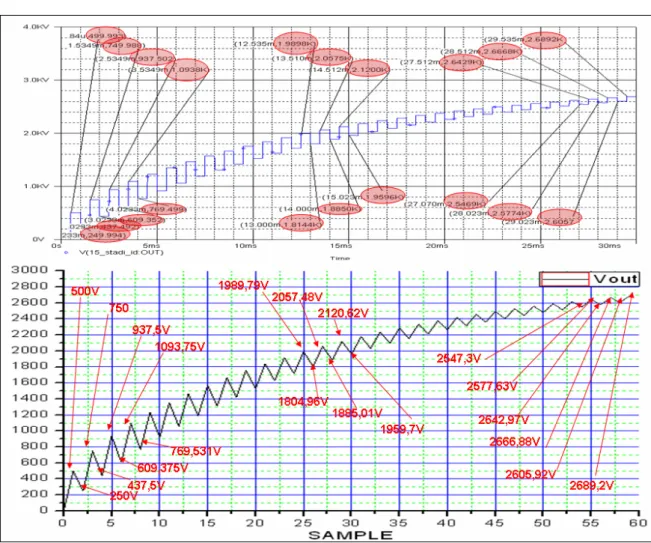

Figura 6.15 Confronto tra simulazione di un Cockroft-Walton a 3 stadi ideale e il risultato ottenuto dal modello studiato

In Fig.6.15 in basso, si osservi che sull’asse delle ascisse non c’è il tempo ma il numero di campioni. Per quanto detto prima, si intuisce che il numero di campioni rappresenta sostanzialmente il numero di volte in cui il modello è stato iterato, ossia il numero di gradini presenti in ingresso al sistema. Ovviamente per ogni coppia di gradini positivi e negativi avremo un periodo del segnale, per cui esiste una relazione fra l’asse temporale e quello dei campioni:

Frequenza Sample

Time 1

2 ⋅

=

Per essere certi della corrispondenza con l’asse dei tempi della simulazione riportata in alto, di seguito viene ricavato il tempo in corrispondenza di Sample = 60:

ms s Time 0.03 30 1000 1 2 60⋅ = = =

Il vantaggio del poter analizzare ogni stadio separatamente sta ovviamente nella semplicità del modello ottenuto, offrendo quindi la possibilità di poter analizzare gli effetti causati dall’introduzione dei componenti parassiti presenti nel circuito reale, come le ESD dei condensatori. Inoltre nel circuito di Fig.6.6, avendo sostituito i diodi con degli interruttori, non si considera il fatto che, nel periodo di non conduzione, i diodi hanno un effetto capacitivo legato al valore della tensione inversa applicata.

Figura 6.16 Andamento della capacità di giunzione in funzione delle tensione inversa applicata per il diodo STTH512 [19]

Fig.6.16 mostra l’andamento della capacità di giunzione in funzione della tensione inversa applicata per il diodo STTH512 [19] della ST Microelectronics, appartenente alla stessa serie dei diodi utilizzati per il moltiplicatore (STTH112 [18]). Per questi ultimi il costruttore non fornisce la curva C-V, comunque avendo i due diodi caratteristiche simili

(si rimanda ai datasheet [18] [19] per i dettagli), è ragionevole assumere che tale grafico si discosti poco da quello di Fig.6.16.

Fig.6.17 mostra come si modifica ogni singolo stadio del circuito di Fig.6.6, per considerare, seppur in maniera semplificata, la presenza delle ESD dei condensatori e delle capacità di giunzione dei diodi polarizzati in inversa (Cj). Quando il generico interruttore Sj è spento si comporta come un condensatore, quando è acceso, invece, la corrispondente capacità CDj viene cortocircuitata e quindi si comporta come un cortocircuito. In pratica mentre in Fig.6.6 si considerano gli interruttori spenti come circuiti aperti, in Fig.6.17 sono rappresentati con le Cj.

Si tenga presente che tutte le volte in cui verrà menzionata la capacità di giunzione, si farà sempre riferimento alla capacità del diodo in polarizzazione inversa.

GND IN OUT C1 {C} C2 {C} R1 {RP} R2 {RP} CD1 {CD} + -+ -DIR S2 CD2 {CD} + -+ -INV S1

Figura 6.17 Schema circuitale di in Singolo Stadio di un Moltiplicatore Ideale con le capacità di giunzione dei diodi polarizzati in inversa

In Fig.6.18 sono confrontati gli andamenti della tensione d’uscita del moltiplicatore di tensione realizzato (Fig.5.5) ottenuti in tre modi differenti:

• Utilizzando il modello ideale del moltiplicatore;

• Utilizzando il modello più accurato con ESD = 25Ω, C = 1nF e capacità di giunzione CD = 5pF;

• Simulazione del moltiplicatore reale utilizzando i diodi STTH112.

In tutti è tre i casi viene considerato un segnale di pilotaggio di ampiezza pari ad 1 kV e frequenza 100kHz.

Figura 6.18 Andamento della tensione di uscita del moltiplicatore realizzato ottenuto utilizzando: a) modello ideale (curva in nero), b) modello con ESD e capacità di giunzione (curva in rosso), c) simulazione con diodi STTH112 (curva in verde)

Fig.6.18 presenta uno scenario interessante, dal quale emerge che la simulazioni del circuito reale fornisce un andamento della tensione prossimo a quello ottenuto tramite il modello ideale ricavato. Il modello più accurato, invece, fornisce un risultato che si discosta parecchio dai precedenti, ma che si avvicina molto a quello ottenuto dalle misure effettuate (Fig.5.15). Quindi l’aver introdotto nel modello le ESD dei condensatori e le Cj dei diodi, ha permesso di ottenere l’effetto di riduzione di guadagno che si verificava anche nei risultati sperimentali.

Figura 6.19 Andamento della tensione di uscita del moltiplicatore ottenuto utilizzando il modello accurato per diversi valori della capacità di giunzione (0.5pF, 1pF, 2pF, 5pF, 10pF).

Dalle simulazioni di Fig.6.3, si è constatato inoltre che la presenza delle ESD, dato il loro basso valore, non causava perdite di tensione in uscita dal moltiplicatore.

A questo punto sembra evidente che il problema sia da attribuire alle Cj dei diodi. A conferma di quanto detto, in Fig.6.19 sono riportati gli andamenti della tensione di uscita, ricavati utilizzando il modello accurato con C = 1nF e facendo assumere alla capacità di giunzione cinque valori differenti: 0.5pF, 1pF, 2pF, 5pF, 10pF.

Si osserva che all’aumentare del valore che assume la capacità di giunzione, aumenta la perdita di tensione rispetto al caso ideale.

Il motivo di questo comportamento può essere facilmente compreso osservando Fig.6.20, dove sono mostrate le due configurazioni circuitali che può assumere il singolo stadio di Fig.6.17, ossia il caso in cui sono accesi gli interruttori DIR e spenti gli INV e quello in cui accade il contrario.

IN GND OUT C1 {C} C2 {C} R1 {RP} R2 {RP} CD2 {CD} IN GND OUT C1 {C} C2 {C} R1 {RP} R2 {RP} CD1 {CD}

Figura 6.20 Configurazioni circuitali assunte dal singolo stadio mostrato in Fig.6.17: A sinistra il caso in cui sono accesi gli interruttori DIR, a destra il caso in cui sono accesi gli interruttori INV

Supponendo di considerare il caso più semplice di moltiplicatore a singolo stadio e ricordando dall’analisi precedente che gli interruttori si accendono in corrispondenza dei gradini del segnale d’ingresso, è chiaro che in presenza di un gradino positivo che accende l’interrutore S2 (Fig.6.17), caso a sinistra di Fig.6.19, parte della carica immessa nel circuito non va a caricare le capacità del moltiplicatore ma finisce sulla capacità di giunzione di S1 (CD1). Questa carica viene persa quando in ingresso giunge il gradino negativo, il quale accende l’interruttore S1 e di conseguenza cortocircuita la capacità CD1. In questa seconda situazione, riportata in Fig.6.19 a destra, si ha inoltre che la capacità C2 del moltiplicatore cede parte della sua carica alla capacità di giunzione di S2 (CD2). Anche questa carica verrà persa, infatti al prossimo gradino positivo si riaccenderà S2 che cortocircuiterà CD2. Ovviamente l’analisi può essere facilmente estesa ad un moltiplicatore con un numero generico di stadi.

Quindi se da una parte è vero che aumentando il numero di stadi aumenta il guadagno di un Cockroft-Walton (Par.4.4), di contro bisogna considerare che maggiore sarà il numero di stadi, maggiore sarà il numero di diodi e quindi maggiore sarà la perdita di tensione per effetto delle capacità di giunzione.

Dalle considerazioni fatte, il motivo per cui tutte le simulazioni del sistema, effettuate considerando il moltiplicatore reale a diodi, portano a dei risultati lontani dalle misure sperimentali, potrebbe effettivamente essere imputabile ad una model errata.

Dato che da Fig.6.18 è emerso che l’andamento della simulazione seguiva quello ottenuto con il modello ideale, è presumibile che il problema della model stia nel considerare una capacità di giunzione in polarizzazione inversa inferiore a quella del dispositivo reale. A conferma di questo sono state ricavate le curve C-V per i diodi STTH112 ed STTH515 effettuando una simulazione AC al variare della tensione inversa applicata al diodo, mediante Performance Analysis su Orcad Spice. I circuiti utilizzati per la simulazione sono riportati in Fig.6.21 mentre in Fig.6.22 e Fig.6.23 sono riportate le curve C-V dei due diodi. V1 1Vac 0Vdc V2 0Vdc D1 STTH112U D2 STTH512B V3 1Vac 0Vdc V4 0Vdc 0 0

Figura 6.22 Curva C-V per il diodo STTH112

Figura 6.23 Curva C-V per il diodo STTH512

Confrontando Fig.6.23 con Fig.6.16, si osserva che la curva C-V dell’STTH512 ottenuta in simulazione è coerente con quella tipica riportata nel datasheet dal costruttore.

Fig.6.22, invece, mostra un andamento anomalo della capacità di giunzione in funzione della tensione inversa applicata. In particolare si nota che per tensioni elevate la capacità ha un valore molto basso (decine di femtofarad ), praticamente trascurabile.

Tutto ciò conferma quanto si era precedentemente intuito grazie all’analisi del moltiplicatore con i modelli implementati.

Fig.6.24 mostra gli andamenti delle tensione fornite dal sistema di Fig.6.1 utilizzando in un caso il diodo STTH112 e nell’altro il diodo STTH512.

Figura 6.24 Andamento della Tensione di uscita del sistema di Fig.6.1 utilizzando per il moltiplicatore in un caso i diodi STTH112 nell’atro gli STTH512

E’ già stato detto che i due diodi appertengono alla stessa famiglia e hanno caratteristiche confrontabili, tra i due comunque l’STTH512, anche se di poco, risulta essere più performante ([18] [19]). I risultati ottenuti in Fig.6.23 mostrano una situazione completamente opposta, a conferma del fatto che purtroppo la model fornita dal costruttore per il diodo STTH112 è errata.

6.3 Progettazione di un Moltiplicatore di Tensione Ottimizzato

Dall’analisi del moltiplicatore utilizzando i modelli implementati, è stato possibile individuare la causa del principale problema del sistema realizzato, ovvero il mancato

raggiungimento della tensione necessaria a generare una scarica fra gli elettrodi della candela in camera di combustione.

Adesso è necessario modificare opportunamente il progetto del moltiplicatore di tensione in modo tale da aumentare il guadagno di tensione reale e cercare di ridurre al minimo il tempo di salita della tensione d’uscita.

6.3.1 Aumentare il Guadagno Reale di un Cockroft-Walton

In Fig.6.19 abbiamo osservato come varia l’andamento della tensione di uscita del moltiplicatore al variare del valore della capacità di giunzione del diodo in polarizzazione inversa. Inoltre nel Par.6.2 è stato illustrato il meccanismo che porta alla perdita di carica ad ogni commutazione del segnale d’ingresso. Dalle informazioni ricavate segue che l’entità della perdita di tensione oltre ad essere legata al valore assunto dalla Cj dei diodi dipende anche dal valore assunto dalle capacità del moltiplicatore.

Considerando un moltiplicatore realizzato con condensatori uguali, in Fig.6.25 si può osservare come varia, secondo il modello, l’andamento della tensione di uscita mantenendo costante il valore della capacità di giunzione a 5pF e variando il valore assunto dalle capacità del moltiplicatore. Fig.6.26 mostra invece il risultato ottenuto tramite simulazione del circuito reale, utilizzando ovviamente i diodi STTH512, per i quali è stata verificata la correttezza della model.

Figura 6.25 Andamento della Tensione di uscita di un moltiplicatore a condensatori uguali, al variare del valore di capacità utilizzato ed ottenuto tramite il modello implementato con capacità di giunzione pari a 5pF

Figura 6.26 Andamento della Tensione di uscita di un moltiplicatore a condensatori uguali, al variare del valore di capacità utilizzato ed ottenuto tramite simulazione con diodi STTH512

La prima cosa interessante che possiamo evidenziare dal confronto tra le figure 6.25 e 6.25, è che il modello implementato permette di ottenere risultati che rispecchiano, con margine di errore tollerabile, quelli ottenuti tramite simulazione. Questo è un risultato importante in quanto permette di svincolarsi durante la fase di progettazione dal simulatore, riducendo così i tempi di attesa dei test, ed inoltre fornisce uno strumento utile per poter ottimizzare il circuito sotto analisi in base alle specifiche di progetto.

Da Fig.6.25 e Fig.6.26, si osserva inoltre che, a parità di capacità di giunzione, all’aumentare del valore assunto dalle capacità del moltiplicatore diminuisce la perdita di tensione in uscita. Un risultato analogo si era ottenuto in Fig.6.19, dove però la perdita di tensione diminuiva al diminuire del valore assunto dalla capacità di giunzione.

Ricordando l’analisi del funzionamento del singolo stadio di Fig.6.17 è chiaro che i due fenomeni sono correlati. In pratica quanto più il valore della capacità di giunzione è prossimo al valore delle capacità del moltiplicatore maggiore sarà la perdita di tensione, in quanto maggiore sarà la carica persa durante ogni commutazione del segnale d’ingresso (Par.6.2).

A questo punto dato che il valore tipico della Cj dei diodi con Vrrp superiore al kiloVolt è dell’ordine del picoFarad, l’unica soluzione possibile per aumentare il valore della tensione

di uscita è quella di aumentare il valore delle capacità del moltiplicatore. Fig.6.25 e Fig.6.26 mostrano che per raggiungere almeno 10 kV, utilizzando diodi con Cj pari a 5 pF, è necessario utilizzare condensatori di valore pari o superiore a 5nF.

Il problema di una soluzione di questo tipo è che l’energia accumulata dai condensatori del moltiplicatore rischia di essere di molto superiore a quella richiesta dalle specifiche del sistema (0.3 ÷ 1 mJ). E’ necessario quindi trovare una maniera per ridurre la capacità di giunzione in modo tale da ottenere il risultato voluto in corrispondenza di una capacità totale (somma delle capacità) del moltiplicatore minore.

Una possibile soluzione è quella di utilizzare più diodi in serie, in questo modo la capacità di giunzione dovrebbe ridursi idealmente di un fattore pari al numero di diodi collegati in serie. Inoltre prendendo in considerazioni diodi con Vrrp pari alla massima tensione inversa a cui è sottoposta l’intera serie, non è necessaria alcuna accortezza per garantire che tale tensione non cada tutta su uno dei diodi della serie stessa.

Supponiamo, ad esempio, di considerare la serie di due diodi e di assumere le capacità del moltiplicatore di valore pari a 2.5nF (Fig.6.27). Ipotizzando che la tensione inversa applicata si ripartisca equamente e considerando che l’ampiezza del segnale d’ingresso sia al solito 1 kV, ogni diodo in polarizzazione inversa sarà sottoposto ad una tensione di 500 V. Da Fig. 6.23 si osserva che la capacità di giunzione per tensioni inverse superiori a 60 V resta inferiore a 10pF per cui, per semplicità, assumeremo come valore della Cj dei diodi lo stesso utilizzato nelle analisi precedenti, ossia 5pF. La capacità complessiva della serie sarà quindi pari a 2.5pF. D90 STTH512 D100 D110 STTH512 D120 D130 STTH512 D140D150 STTH512 D160 D170 STTH512 D180 D190 STTH512 D200D210 STTH512 D220 D230 STTH512 D240 D250 STTH512 D260 D270 STTH512 D280D290 STTH512 D300 D10 STTH512 D20 D30 STTH512 D40 D50 STTH512 D60 D70 STTH512 D80 OUT D9 STTH512 D10 D11 STTH512 D12 D13 STTH512 D14D15 STTH512 D16 D17 STTH512 D18 C1 2.5n D19 STTH512 D20 D21 STTH512 D22 D23 STTH512 D24 D25 STTH512 D26 D27 STTH512 D28D29 STTH512 D30 C2 2.5n C3 2.5n C4 2.5n C5 2.5n C6 2.5n C7 2.5n C8 2.5n C9 2.5n C10 2.5n C11 2.5n C12 2.5n C13 2.5n C14 2.5n C15 2.5n C16 2.5n C17 2.5n C18 2.5n C19 2.5n C20 2.5n C21 2.5n C22 2.5n C23 2.5n C24 2.5n C25 2.5n C26 2.5n C27 2.5n C28 2.5n C29 2.5n C30 2.5n D1 STTH512 D2 D3 STTH512 D4 D5 STTH512 D6 D7 STTH512 D8 GND IN

Figura 6.27 Schema circuitale di un moltiplicatore a condensatori uguali di capacità pari a 2.5nF e con diodi sostituiti dalla serie di due diodi STTH512

Fig.6.28 mostra l’andamento della tensione d’uscita ottenuto con il modello, impostando Cj = 2.5pF, e quello ottenuto dalla simulazione del circuito di Fig.6.27.

Figura 6.28 Confronto tra l’andamento della tensione di uscita del moltiplicatore di Fig.6.27 ricato mediante simulazione e il risultato ottenuto dal modello con C = 2.5nF e Cj = 2.5pF

Dal risultato riportato in Fig.6.28 si osserva che utilizzando la configurazione serie con due diodi, è possibile dimezzare la capacità totale del moltiplicatore che consente di raggiungere la tensione di 10 kV.

6.3.2 Riduzione del Tempo di Salita della Tensione di uscita

Nonostante si sia trovato il modo di far raggiungere al sistema la tensione di 10 kV, da Fig.6.25 e Fig.6.26, è evidente che il tempo necessario per raggiungere tale valore è superiore a 5 ms, un valore decisamente inaccettabile se si pensa che ad una velocità media dell’albero motore di ω=3000[giri/min] l’angolo percorso dall’albero in 5 ms è pari a 90° (Par.5.4.1). Per cercare una possibile soluzione a questo problema è utile riprendere l’analisi del moltiplicatore (Par.6.2).

Da quanto detto nel Par.6.2, il modello ottenuto permette di studiare il comportamento del moltiplicatore analizzando ogni stadio separatamente in presenza di un gradino in ingresso. Questo ovviamente semplifica la comprensione del meccanismo di trasferimento di carica tra i condensatori del moltiplicatore. Per dare una descrizione qualitativa di questo meccanismo, in Fig.6.29 sono mostrate le due configurazioni circuitali che assume un singolo stadio in presenza un gradino positivo (a sinistra) e di un gradino negativo (a destra). I diodi non in conduzione sono rappresentati da collegamenti interrotti, mentre quelli accesi sono raffigurati da cortocircuiti.

IN GND OUT C1 {C} C2 {C} IN GND OUT C1 {C} C2 {C}

Figura 6.29 Configurazioni circuitali assunte da un moltiplicatore a singolo stadio quando in ingresso è applicato un gradino positivo (a sinistra) e un gradino negativo (a destra) . I collegamenti interrotti rappresentano i diodi spenti, mentre i cortocircuiti rappresentano i diodi accesi

In un generico moltiplicatore la tensione d’uscita è determinata dal valore di tensione ai capi dei condensatori nella parte bassa del circuito. Questo implica che il tempo di salita della tensione d’uscita è legato al tempo impiegato per caricare questi condensatori.

In Fig.6.29, essendo un singolo stadio, l’unica capacità che determina la tensione di uscita è C2, tale condensatore si carica in presenza di ogni gradino positivo mentre in presenza di un gradino negativo si trova in condizione di mantenimento.

Osservando Fig.6.29 a sinistra, è chiaro che la carica del condensatore C2 avviene quando questo si trova in serie a C1, per cui quando il gradino sarà andato a regime la carica sui due condensatori sarà la stessa. Essendo la tensione ai capi di un condensatore legata alla carica ed al valore della capacità dalla relazione Q = CV, questo implica che a parità di carica, per due condensatori in serie, le tensioni ai loro capi sono inversamente proporzionali al valore delle rispettive capacità. Da questo si può intuire che scegliere la capacità C1 più grande della capacità C2, implica una ripartizione del gradino a favore di C2 riducendo così il tempo impiegato dal moltiplicatore per andare a regime.

Estendendo il ragionamento ad un moltiplicatore con un numero generico di stadi, dal modello ottenuto si ricava che una buona scelta per ridurre il tempo di salita della tensione d’uscita è quello di utilizzare valori di capacità decrescenti partendo dal primo stadio sino all’ultimo. La situazione migliora quanto più ampio è il salto tra i valori assunti dalle capacità dei condensatori. Questo risultato è coerente con quelli ottenuti in [14] e riportati nel Par.4.5.

A conferma di quanto detto in Fig.6.31 sono confrontati gli andamenti della tensione di uscita del moltiplicatore di Fig.6.27 e di quello di Fig.6.30 dove le capacità assumono valore decrescente partendo da 100nF fino a 1nf negli ultimi stadi. Ovviamente nel circuito reale non verranno usati valori così grandi per le capacità dei primi stadi, è una scelta del

tutto casuale, quindi non ottimizzata, con l’unico scopo di rendere evidenti gli effetti sull’andamento della tensione d’uscita.

D90 STTH512 D100 D110 STTH512 D120 D130 STTH512 D140D150 STTH512 D160 D170 STTH512 D180 D190 STTH512 D200D210 STTH512 D220 D230 STTH512 D240 D250 STTH512 D260 D270 STTH512 D280D290 STTH512 D300 D10 STTH512 D20 D30 STTH512 D40 D50 STTH512 D60 D70 STTH512 D80 OUT D9 STTH512 D10 D11 STTH512 D12 D13 STTH512 D14D15 STTH512 D16 D17 STTH512 D18 C1 100n D19 STTH512 D20 D21 STTH512 D22 D23 STTH512 D24 D25 STTH512 D26 D27 STTH512 D28D29 STTH512 D30 C2 80n C3 60n C4 40n C5 30n C6 20n C7 10n C8 5n C9 2.5n C10 2.5n C11 2.5n C12 2.5n C13 2.5n C14 2.5n C15 2.5n C16 2.5n C17 2.5n C18 1n C19 1n C20 1n C21 1n C22 1n C23 1n C24 1n C25 1n C26 1n C27 1n C28 1n C29 1n C30 1n D1 STTH512 D2 D3 STTH512 D4 D5 STTH512 D6 D7 STTH512 D8 GND IN

Figura 6.30 Schema circuitale di un moltiplicatore con condensatori di valore di capacità decrescente partendo dal primo stadio verso l’ultimo e con diodi sostituiti dalla serie di due diodi STTH512

Figura 6.31 Confronto tra gli andamenti di tensione ottenuti in uscita dal moltiplicatore di Fig.6.27 e quello di Fig.6.30

Da fig.6.31 è evidente che, nonostante la scelta puramente casuale dei valori delle capacità, il tempo di salito della tensione di uscita si è ridotto. Inoltre si osserva anche un aumento del valore di regime dovuto sicuramente al valore significativo assunto dalle capacità dei primi stadi, per i quali diventa di conseguenza trascurabile la perdita di tensione a causa delle Cj dei diodi.

6.4 Ricerca della Configurazione Ottima

Nel precedente paragrafo è stato messo in evidenza che per ottenere valori di tensione elevati e tempi di salita brevi occorre:

1. Non utilizzare valori di capacità troppo bassi;

2. Ridurre la Cj sfruttando i diodi in configurazione serie;

3. Utilizzare valori di capacità decrescenti partendo dal primo verso l’ultimo stadio, massimizzando il salto fra i valori di capacità consecutivi.

Considerando fissata la Cj è chiaro che le prestazioni del moltiplicatore ruotano tutte intorno al valore assunto dalle capacità. Scegliere questi valori non è banale. Nel Par.6.3.1 si è già visto che i valori delle capacità non possono essere assunti molto grandi, altrimenti l’energia disponibile durante la scarica sarebbe elevata. Quindi non potendo utilizzare condensatori con capacità piccola, per ridurre le perdite dovute alle Cj, e neanche troppo grande, per evitare un accumulo eccessivo di energia, il range di valori disponibili è ridotto, ed è quindi difficile riuscire ad ottenere dei valori decrescenti di capacità con un salto significativo tra di essi. Altro fattore che limita il valore della capacità massima dei condensatori del primo stadio è la massima corrente di picco supportata dai Mosfet dell’Half Brige.

Data la presenza di tutte queste variabile, per effettuare una scelta ottima dei valori delle capacità del moltiplicatore, è stato implementato in C un programma che in funzione dei parametri e dei vincoli imposti dall’utente è in grado di ricavare la scelta migliore, rispettando tali vincoli. I principali parametri richiesti sono i seguenti:

• Ampiezza e Frequenza dell’onda quadra in ingresso al circuito;

• Valore assunto dalla Capacità di giunzione dei diodi polarizzati inversamente; • Valore massimo consentito per le capacità del moltiplicatore;

• Valore minimo consentito per le capacità del moltiplicatore; • Impostare punto di Start per la ricerca.

I vincoli invece sono:

• Massimo numero di periodi del segnale d’ingresso in cui effettuare la ricerca.

Il programma una volta avviato, per prima cosa verifica che impostando il valore delle capacità a quello massimo consentito si riesca a raggiungere la soglia desiderata. Se questo test fallisce non ha senso procedere nella ricerca della configurazione ottima, in quanto riducendo i valori delle capacità aumenterebbero le perdite causate dalle Cj e quindi la soglia non sarebbe mai raggiunta. Se invece il test ha esito positivo allora si procede a valutare la scelta migliore per ogni singola capacità del moltiplicatore. Per ridurre i tempi di elaborazione sono stati imposti dei vincoli ai valori possibili, evitando di analizzare così configurazioni già eliminabili in partenza. Come esempio si pensi al caso di capacità crescenti partendo dal primo stadio verso il carico.

Considerando i seguenti parametri:

1. Possibili valori di capacità: 1nF, 2nF, 3nF, 4nF, 5nF, 6nF, 7nF, 8nF; 2. Ampiezza segnale d’ingresso: 1 kV;

3. Frequenza segnale d’ingresso: 500 kHz; 4. Capacità di giunzione: 3 pF; 5. Tensione di soglia: 10 kV; 6. Numero Massimo di Periodi: 500;

la configurazione ottima, per un moltiplicatore a 15 stadi, ricavata dal programma realizzato è la seguente:

CH[1] = 8.00e-009 RH[1] = 2.83e+000 CC[1] = 3.00e-009 RC[1] = 7.53e+000 CH[2] = 8.00e-009 RH[2] = 2.83e+000 CC[2] = 3.00e-009 RC[2] = 7.53e+000 CH[3] = 8.00e-009 RH[3] = 2.83e+000 CC[3] = 3.00e-009 RC[3] = 7.53e+000 CH[4] = 7.00e-009 RH[4] = 3.23e+000 CC[4] = 3.00e-009 RC[4] = 7.53e+000 CH[5] = 5.00e-009 RH[5] = 4.52e+000 CC[5] = 3.00e-009 RC[5] = 7.53e+000 CH[6] = 4.00e-009 RH[6] = 5.65e+000 CC[6] = 3.00e-009 RC[6] = 7.53e+000 CH[7] = 3.00e-009 RH[7] = 7.53e+000 CC[7] = 2.00e-009 RC[7] = 1.13e+001 CH[8] = 2.00e-009 RH[8] = 1.13e+001 CC[8] = 2.00e-009 RC[8] = 1.13e+001

CH[9] = 2.00e-009 RH[9] = 1.13e+001 CC[9] = 1.00e-009 RC[9] = 2.26e+001 CH[10] = 1.00e-009 RH[10] = 2.26e+001 CC[10] = 1.00e-009 RC[10] = 2.26e+001 CH[11] = 1.00e-009 RH[11] = 2.26e+001 CC[11] = 1.00e-009 RC[11] = 2.26e+001 CH[12] = 1.00e-009 RH[12] = 2.26e+001 CC[12] = 1.00e-009 RC[12] = 2.26e+001 CH[13] = 1.00e-009 RH[13] = 2.26e+001 CC[13] = 1.00e-009 RC[13] = 2.26e+001 CH[14] = 1.00e-009 RH[14] = 2.26e+001 CC[14] = 1.00e-009 RC[14] = 2.26e+001 CH[15] = 1.00e-009 RH[15] = 2.26e+001 CC[15] = 1.00e-009 RC[15] = 2.26e+001

Dove con CH[i] si indicano i condensatori del moltiplicatore in alto e con RH[i] le corrispondenti ESD, mentre con CC[i] si indicano i condensatori del moltiplicatore in basso ed analogamente le RC[i] indicano le rispettive ESD. I valori delle capacità sono espressi in Farad mentre per le resistenze in Ohm.

Figura 6.32 Andamento della Tensione d’Uscita del Moltiplicatore di Tensione Ricavato mediante il Modello utilizzando Cj = 2,5 pF e facendo assumere alle capacità i valori ricavati dall’analisi per la configurazione ottimale.

6.5 Moltiplicatore Full-Wave

Il moltiplicatore Full-Wave viene spesso utilizzato quando si desidera minimizzare il ripple sulla tensione d’uscita. Lo schema circuitale per la configurazione a tre stadi è mostrato in Fig.6.33. Per il corretto funzionamento occorre applicare in ingresso due segnali in opposizione di fase, ottenuti tipicamente utilizzando un trasformatore a presa centrale.

IN_HIGH CH1 {C} C2 {C} GND {C} CL1 IN_LOW OUT CH3 {C} C4 {C} {C} CL3 CH5 {C} C6 {C} {C} CL5 DH1 DH2 DH3 DH4 DH5 DH6 DL5 DL6 DL3 DL4 DL1 DL2

Figura 6.33 Schema Circuitale di un Moltiplicatore Full-Wave a 3 Stadi

Confrontando lo schema con quello di un Half-wave a tre stadi (Fig.6.5) si osserva che la struttura simmetrica del Full_Wave può essere vista come composta da due Half-wave che condividono l’array di condensatori che determinano la tensione d’uscita del moltiplicatore. Dallo studio fatto nei precedenti paragrafi segue che pilotando questi due half-wave in opposizione di fase il tempo impiegato dai condensatori per caricarsi si riduce e quindi si riduce il tempo di salita della tensione d’uscita.

Per essere più convinti è possibile estendere l’analisi semplificata di un singolo stadio effettuata nel Par.6.3.2 ad un moltiplicatore Full-Wave. In tal caso Fig.6.29 si modifica come mostrato in Fig.6.34, dalla quale si osserva che gli interruttori del lato alto e del lato basso si accendono alternativamente in quanto in presenza di un gradino positivo nel lato superiore della struttura, nel lato inferiore si avrà un gradino negativo e viceversa.

Questo implica che la carica del condensatore C2 avviene in entrambe le configurazioni mostrate in Fig.6.34. Infatti in un caso il trasferimento di carica si ha quando C2 finisce in serie a CH1, nell’altro quando C2 finisce in serie a CL1. In sostanza si ottiene un risultato analogo a quello che avremmo utilizzando un half-wave pilotato a frequenza maggiore (all’incirca doppia).

Quanto detto giustifica il motivo per cui la struttura Full-Wave permetta la riduzione del fattore di ripple sulla tensione di uscita.

IN_HIGH CH1 {C} GND C2 {C} OUT IN_LOW CL1 {C} IN_HIGH CH1 {C} GND C2 {C} OUT IN_LOW CL1 {C}

Figura 6.34 Configurazioni circuitali assunte da un moltiplicatore Full_Wave a singolo stadio in corrispondenza dei gradini dei segnali di ingresso. I collegamenti interrotti rappresentano i diodi spenti, mentre i cortocircuiti rappresentano i diodi accesi

![Figura 6.16 Andamento della capacità di giunzione in funzione delle tensione inversa applicata per il diodo STTH512 [19]](https://thumb-eu.123doks.com/thumbv2/123dokorg/7541490.108235/16.892.135.782.495.909/figura-andamento-capacità-giunzione-funzione-tensione-inversa-applicata.webp)