Capitolo 6 - Layout

Capitolo 6

Layout

L‘ultima fase che completa il progetto è la descrizione fisica o layout che consiste nel definire le maschere usate per la realizzazione dell‘integrato. Esso, infatti, viene prodotto attraverso l‘uso di n maschere relative agli n strati di diverso materiale necessari per realizzare fisicamente il dispositivo e le connessioni.

In questo capitolo saranno descritte le tecniche utilizzate per migliorare il matching fra i componenti e diminuire gli effetti parassiti, in particolar modo per i BJT del core. Nella realizzazione si è cercato di fare particolare attenzione nel migliorare la compattezza del BVR, rispettando le regole di layout della tecnologia. Nella tecnologia usata sono disponibili fino a sei livelli di metal, in questo caso, è stato necessario utilizzare i primi tre per il routing, il quinto e il sesto per la realizzazione delle capacità MIM mentre il quarto è stato usato come schermo per evitare accoppiamenti capacitivi parassiti con il circuito sottostante. L‘utilizzo di più livelli di metal aumenta la compattezza del circuito.

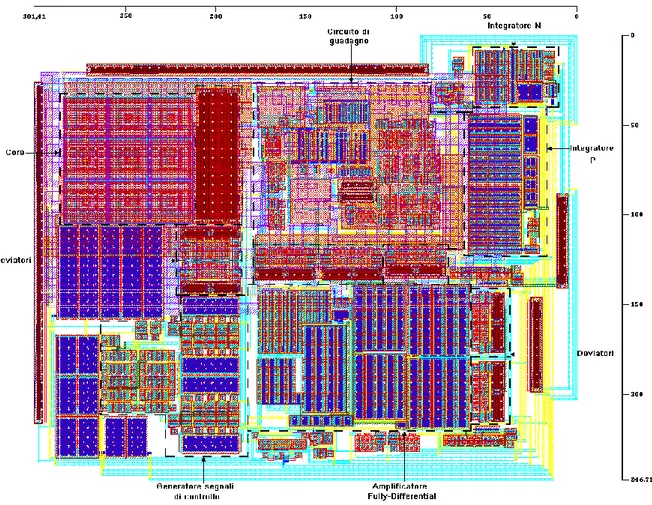

In figura 6.1 è mostrato il layout completo del BVR e sono messi in evidenza i blocchi base che compongono il circuito. Le dimensioni visualizzate sono espresse in μm, l‘area occupata dal chip è quindi di: .

Figura 6.1 - Layout completo BVR

6.1 Layout del deviatore

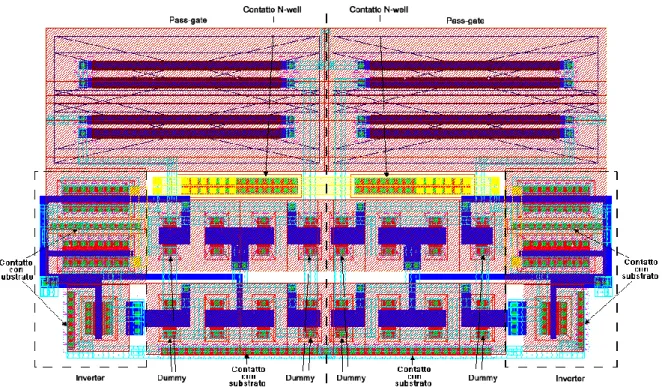

Nella realizzazione del layout è stata dedicata particolare attenzione a ridurre le dimensioni dei deviatori e delle pass-gate che sono i circuiti più ricorrenti nel sistema. In figura 6.2 è mostrato il layout di un deviatore che riceve in ingresso i due segnali di controllo con fasi non sovrapposte. Le pass-gate presentano in serie all‘uscita e all‘ingresso le due resistenze per equilibrare la redistribuzione di carica. Dalla figura si possono individuare le due pass-gate disposte simmetricamente rispetto all‘asse verticale e gli inverter di ciascuna pass-pass-gate. Si nota, per migliorare la loro funzione di cancellazione della redistribuzione di carica, la disposizione simmetrica dei ―dummy‖ rispetto al corrispondente pass-transistor.

Capitolo 6 - Layout

Figura 6.2 - Layout dei deviatori con doppio controllo e pass-gate resistive

6.2 Layout del Core

Dal layout del core presentato in figura 6.3 sono ben visibili le strutture dei BJT nella parte sinistra mentre le resistenze in quella destra. Per quanto riguarda i BJT è stata usata una struttura a centroide comune con una matrice 3x3 in cui le basi e i collettori dei BJT sono tutti connessi fra loro come nello schematico. In particolare il BJT (Figura 4.6), composto solo da un elemento, è posto al centro della struttura, mentre i singoli BJT che, in parallelo formano , sono stati disposti intorno. Tale tipologia è una struttura compatta simmetrica e avvicina i risultati ottenuti durante le simulazioni a quelli ottenuti nella realtà migliorando il matching fra i BJT e diminuendo quindi, le cause di non idealità che inciderebbero sulle prestazioni del circuito. Per rendere più compatto il layout, ciascuna delle resistenze sono state scomposte nella serie di sette resistenze.

Figura 6.3 - Layout Core

6.3 Layout del circuito di guadagno

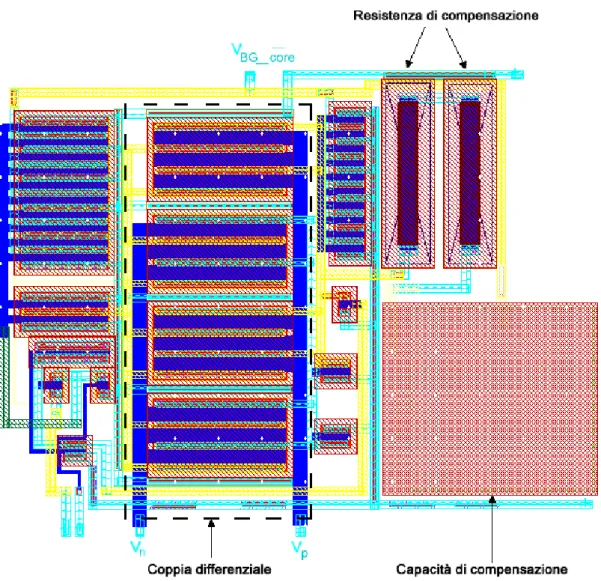

Nel progetto svolto ricorrono spesso coppie differenziali e specchi di corrente. Questi tipi di strutture con diverse orientazioni o con correnti che scorrono in versi opposti, sono particolarmente sensibili ad un cattivo matching e ciò dà luogo ad un offset, che spesso risulta dannoso per le prestazioni del circuito. L‘interdigitazione consiste nell‘alternare i fingers che compongono i singoli MOSFET, in una struttura a matrice. Con la tecnica dell‘interdigitazione, i difetti di processo intervengono su entrambi i MOS della coppia differenziale in modo simile, ottenendo MOS con caratteristiche simili, minimizzando così l‘asimmetria della coppia differenziale e quindi l‘offset. Per l‘amplificatore utilizzato nel sistema di guadagno è stata utilizzata una cella progettata in precedenti lavori che è stata parzialmente modificata. Nel layout mostrato in figura 6.4, la coppia differenziale dell‘amplificatore è stata realizzata con una tecnica di interdigitazione alternando su

Capitolo 6 - Layout

implementando la tecnica di interdigitazione sulle coppie differenziali e sugli specchi di corrente cosa che eventualmente si potrà fare successivamente nel caso si dovessero riscontrare problemi in tal senso. In figura 6.4 sono ben visibili la resistenza e la capacità di compensazione e la coppia differenziale d‘ingresso.

Figura 6.4 – Layout Opamp del circuito di guadagno

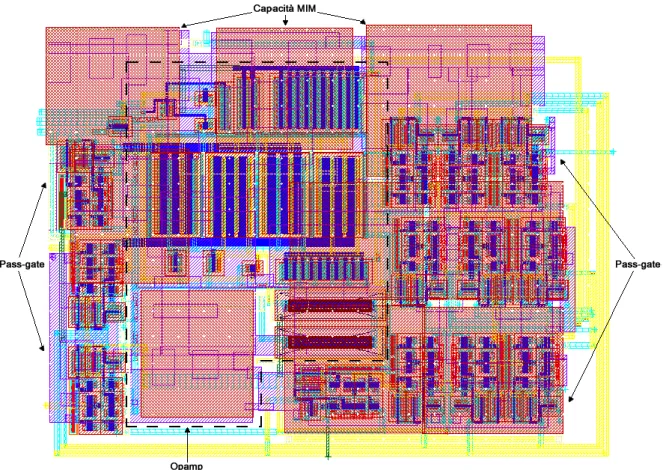

Dal layout mostrato in figura 6.5 del blocco di guadagno si possono notare le capacità MIM utilizzate per l‘architettura switched-capacitor. La loro struttura, che si sviluppa sui livelli di metal cinque e sei, consente di rendere più compatto il layout dell‘intero BVR.

Figura 6.5 – Layout del circuito di guadagno

6.4 Layout del generatore dei segnali di controllo

L‘altro blocco del BVR consiste nella logica di controllo delle fasi di funzionamento, il cui layout, dove sono stati evidenziati i principali componenti circuitali, è mostrato in figura 6.6. E‘ possibile notare la compattezza e una struttura replicata caratteristica del layout di un sistema digitale.

Come spiegato nel corso del capitolo 4, si sfrutta la capacità di gate dei MOSFET per creare gli opportuni ritardi al fine di ottenere le fasi non sovrapposte. Il loro gate è connesso lungo il percorso del segnale mentre il source e il drain sono cortocircuitati tra loro e collegati a massa. I quattro MOSFET occupano circa un quarto dell‘intero sistema digitale. Si è scelto di utilizzare questo approccio, pur aumentando le dimensioni del BVR, per lasciare più libere le metal cinque e sei, per motivi legati all‘architettura del chip, e perchè per esse non

Capitolo 6 - Layout

Stesse considerazioni sono state fatte per le capacità di disaccoppiamento e del meccanismo di start-up.