CAPITOLO 1

Caratteristiche delle schede

Le schede utilizzate oltre a mettere a disposizione un numero di risorse di elaborazione congruo all’applicazione, devono essere dotate di bus ad elevato parallelismo e devono poter operare ad alte frequenze.

L’architettura del sistema di comunicazione per lo scambio dei dati entro la scheda assume un’importanza fondamentale. Oltre l’esigenza di garantire elevati bit rate, al sistema di comunicazione si richiede di occupare un numero di risorse accettabile.

Le applicazioni in tempo reale richiedono che i sottosistemi di input mantengano il ritmo del flusso di dati dagli output dei sensori. Tradizionalmente, il problema veniva risolto suddividendo l’algoritmo su più processori o DSP, quando un singolo elemento non era in grado di sostenere l’elaborazione dei dati. In molti sistemi, gli output dei sensori trasmettono i dati, in modalità normale o multi-cast, a un array di elementi di elaborazione attraverso uno switch fabric.

In funzione dell’applicazione, un singolo FPGA può sostituire dieci o più processori RISC.

Le implementazioni FPGA hanno dimostrato di fornire rapporti FLOP/Watt di gran lunga migliori dei processori RISC, consentendo upgrade dei sistemi che devono funzionare con i sistemi di alimentazione in presenza di limitazioni nell’alimentazione e nel raffreddamento.

Gli FPGA sono ottimizzati per le operazioni in virgola fissa, che tuttavia presentano ulteriori sfide progettuali per i sistemisti. I progettisti software, infatti, preferiscono creare codice in virgola mobile piuttosto che fissa, eliminando così i problemi legati alla gamma scalare e dinamica.

Questo è il motivo per cui i processori RISC, come il PowerPC, trovano sede nel “back end” dei sistemi, dove i requisiti di sistema richiedono un’implementazione più flessibile: i processori tendono a essere più adatti per algoritmi decisionali. I sistemi eterogenei sono diventati più comuni con gli FPGA che risolvono requisiti numericamente intensivi.

In generale, date le notevoli varietà di ambiti di applicazione, la distinzione tra DSP in virgola mobile ("floating-point", in genere a 32 bits) e DSP in virgola fissa ("fixed-point", in genere a 16 bits) risulta fondamentale. .

I fattori che fanno propendere per una categoria, piuttosto che per l'altra sono svariati, anche se in primo luogo si utilizzano quelli in virgola mobile per applicazioni che richiedono una maggiore

quantizzazione) o che hanno una dinamica più ampia (e richiedono per una discretizzazione adeguata, un numero elevato di bits).

Inoltre i floating-point sono più comodi se si desidera il supporto per il DSP del calcolatore con linguaggi ad alto livello (per esempio Matlab o C/C++), e quindi compatibilità più vasta con tipi di dati utilizzati in tali ambienti.

Le applicazioni per i DSP continuano a proliferare soprattutto a causa dell’incessante richiesta di funzioni video a bordo degli apparecchi consumer e anche per l’aumento della domanda relativa a nuovi sistemi riconfigurabili.

In molte di queste applicazioni, tuttavia, è parimenti forte il contrasto fra il desiderio di ottenere alte prestazioni multimediali e la necessità di abbassare il più possibile i costi di produzione.

Per questo sul mercato sta diventando sempre più importante la richiesta di DSP che siano contemporaneamente potenti e a basso costo, ma finora la tecnologia non è stata in grado di soddisfare questa domanda.

Per implementare le funzioni DSP, le due tecniche più diffuse sfruttano i DSP general-purpose oppure gli FPGA.

Entrambi hanno i propri vantaggi e svantaggi e la reale convenienza può, a volte, dipendere dall’applicazione di destinazione.

Per quanto riguarda i DSP, le più comuni elaborazioni che vengono eseguite sono:

Filtri Finite Impulse Response (FIR), che lavorano registrando una serie di n elementi, ciascuno ritardato di un ciclo temporale, comunemente chiamati “tap”. Ogni tap è moltiplicato per un coefficiente e tutti i risultati vengono sommati insieme per produrre l’uscita. Alcuni algoritmi eseguono tutte le moltiplicazioni in parallelo, ma più generalmente l’intero processo viene suddiviso in N stadi, con una fase di accumulo intermedio che serve a passare i risultati parziali fra uno stadio e l’altro. Questo approccio media fra la velocità di esecuzione e le risorse funzionali e necessita di N stadi di calcolo e n/N moltiplicatori.

Filtri Infinite Impulse Response (IIR), Questi filtri sono molto simili ai FIR, tranne che per la presenza di una retroazione; offrono un’efficienza operativa molto più elevata, a parità di area occupata sul silicio, rispetto ad ogni altro filtro matematico.

Trasformate Fast Fourier Transform (FFT), che sono usate in un’ampia varietà di applicazioni, dalla compressione delle immagini fino al riconoscimento del contenuto spettrale in un campione di dati.

Ciascuna richiede un’opportuna combinazione di moltiplicazioni, addizioni, sottrazioni e accumulo dei risultati.[1]

Un generico DSP esegue le operazioni matematiche tramite quattro moltiplicatori e un core microprocessore che si occupa di gestire i risultati intermedi e gli accumuli.

La velocità tipica è dal centinaio di MHz fino a 1 GHz, con prestazioni medie dell’ordine del migliaio di MMAC (Millions of Multiply Accumulates) al secondo. Se un’applicazione richiede maggior potenza di elaborazione, talvolta si possono trovare più DSP installati insieme.

L’elemento che caratterizza maggiormente le schede analizzate è la flessibilità; infatti la struttura base di ogni scheda è composta da un insieme di risorse fisse quali bus, sorgenti diverse di clock, memorie RAM, un certo numero di FPGA di dimensioni medio-alte, un certo numero di DSP, memorie FIFO, FLASH ecc…

La capacità complessiva di elaborazione è quindi molto elevata. Inoltre il sistema risultante è quasi completamente programmabile dall’utente e capace di adattarsi ad applicazioni molto diverse.

La flessibilità è resa possibile dal numero elevato di bus che connettono i vari moduli fra loro e che consentono elevate frequenze di lavoro.

Le schede comunicano con il mondo esterno tramite connettori che consentono di colloquiare con dispositivi di vario tipo. Il più importante di questi è sicuramente il connettore PCI, con cui è possibile interfacciare la scheda con un Personal Computer.

Ogni scheda è corredata di un insieme di utilità software che consentono di configurarla e di gestire in modo semplice ed efficace i trasferimenti di dati tra la scheda e il Pc host.

Gli FPGA di produttori come Xilinx e Altera si interfacciano con segnali standard quali LVTTL, LVCMOS, LVPECL o LVDS e operano di solito fino a 600-800 MHz.

Le interfacce RocketIO dei Virtex II Pro di Xilinx operano fino a 3,125 GHz e gestiscono interfacce standard come PCI Express, Serial RapidIO, Aurora e XAUI. I dispositivi Virtex II Pro di Xilinx si interfacciano con varie interfacce di sensori consentendo al flusso dati di entrare e uscire dall’FPGA a velocità elevate.

L’I/O ad alta velocità in un sistema embedded può entrare nell’FPGA da numerose sorgenti, inclusi:

• Moduli PMC – PCI Mezzanine Card. Un bus PCI da 66 MHz a 64 bit consente una larghezza di banda di circa 500 MB/s

• Moduli XMC – Mezzanine Card con capacità switch fabric. 20 coppie di segnali differenziali consentono una larghezza di banda di circa 1 GB/s

• Seriale ad alta velocità (RocketIO) – Una connessione 4x a 2,5 GHz consente una banda di circa 1 GB/s

• Bus parallelo ad alta velocità (LVTTL o LVDS) – Un’interfaccia a 32 bit consente una banda di circa 2 GB/s

• Switch Fabric – Il RACE++ fornisce circa 200 MB/s mentre un collegamento StarFabric bundled fornisce circa 440 MB/s tramite un bus PCI.

Negli FPGA le funzioni DSP richiedono molta memoria per completare l’esecuzione. Gli FPGA dispongono di memoria interna ottimizzata per RAM a singola o doppia porta, FIFO e registri shift.

Gli algoritmi tendono a scorrere in sequenza continua (pipeline) su blocchi di dati, nei quali ciascun passaggio dell’algoritmo richiede una memorizzazione temporanea. L’FPGA richiede memoria esterna quando opera su grossi blocchi di dati, dal momento che la densità della memoria interna è limitata a 128 Kbyte o meno.

Le interfacce della memoria esterna devono essere in grado di sostenere i flussi di trasmissione dati del sottosistema I/O. Per tenere il ritmo del tasso operativo di trasmissione dati di alcune funzioni DSP, i progettisti possono utilizzare un’interfaccia SRAM veloce.

Per lo storage più a lungo termine, gli scroll buffer o le mappe dello storico dei dati, è possibile utilizzare una memoria più densa, come una SDRAM. In entrambi i casi, non bisogna sottovalutare l’importanza della velocità operativa del trasferimento dati. Gli esempi di interfacce di memoria esterna possono includere:

• SRAM (Sync, DDR o QDR)

• SDRAM (SDR, DDR, RLDRAM o FCRAM)

• FIFO

• Content Addressable Memory (CAM).

Un’implementazione FPGA di successo deve includere uno schema di clock flessibile. Un clock esterno dovrebbe essere fornito o da un oscillatore a bordo, o da una sorgente di clock di sistema esterna alla scheda. Questo consente di sincronizzare il sistema e permette l’appropriato campionamento dei dati in entrata.

Gli FPGA Xilinx utilizzano i Digital Clock Manager (DCM) per fornire un controllo completo su frequenza, variazione e asimmetria di fase del clock. Per ottenere questo risultato, il DCM impiega un “circuito a ritardo bloccato” (Delay-Locked Loop, DLL), un sistema di controllo totalmente digitale che utilizza il feedback per mantenere le caratteristiche di segnale del clock con un alto grado di precisione.

Il DCM è in grado di generare un’ampia gamma di diverse frequenze del clock di output utilizzando operazioni di moltiplicazione/divisione. I dispositivi Virtex II Pro più grandi dispongono di otto o più moduli DCM interni.

basate su JTAG consentono una rapida riprogrammazione durante il debug in laboratorio. Altre funzioni quali LED, switch DIP e punti di collaudo sono funzioni di diagnostica particolarmente utili nei progetti.

Inoltre, Xilinx dispone di un’utilità Integrated Logic analyzer (ILA) denominata ChipScope Pro, che consente agli sviluppatori di visualizzare le forme d’onda di temporizzazione del segnale. [2] Questo strumento ha estese capacità di triggering oltre ad approfonditi buffer capture per isolare i problemi logici più difficili da individuare. ChipScope Pro utilizza un blocco di memoria interna che serve come capture buffer e usa la porta JTAG per la comunicazione. [2]

Le utilità di sviluppo ad alto livello, come SimuLink di Math Works e System Generator di Xilinx, consentono di sviluppare graficamente algoritmi, filtri e varie funzioni DSP senza focalizzare sugli specifici dettagli dell’implementazione FPGA. Questo approccio offre un rapido tempo di risposta per analizzare le aree critiche nelle prestazioni del sistema e l’utilizzo dell’FPGA. [2]

Un altro elemento chiave per una piattaforma di sviluppo è l’ambiente di simulazione.

Che si tratti di VHDL o Verilog per gli Fpga o C++ per i Dsp deve essere utilizzato un linguaggio che modelli accuratamente l’ambiente di sistema completo.

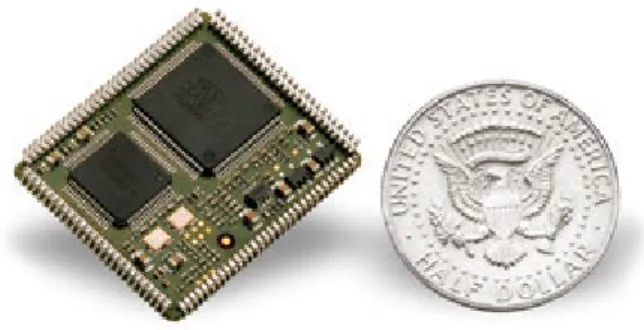

Per quanto riguarda le dimensioni dei dispositivi si può osservare la figura 1, dove si vede una particolare scheda che monta DSP e FPGA confrontata con una moneta da mezzo dollaro.

Fig 1: Dimensioni dei dispositivi.

Ultime parole sul problema del consumo energetico. Naturalmente le schede analizzate sono collegate alla rete fissa di alimentazione tramite Personal Computer, per questo non è stato ritenuto importante.