4

Circuiti di campionamento

In questo capitolo vogliamo analizzare quei blocchi, componenti il DDS completo, il cui uso era già stato introdotto precedentemente. Tali circuiti si occupano prevalentemente del campionamento del dato utilizzando uno dei clock prodotti dal sistema d’interpolazione e della selezione di uno di questi.

4.1 Il flip-flop D-negative-edge-triggered

Si è visto come affinché i segnali prodotti dai due livelli d’interpolazione introducano il ritardo desiderato sul segnale MSB, sia necessario effettuare delle operazioni di campionamento utilizzando due flip-flop.

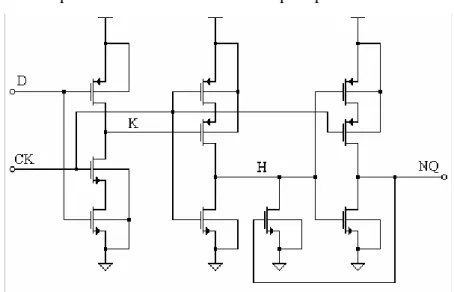

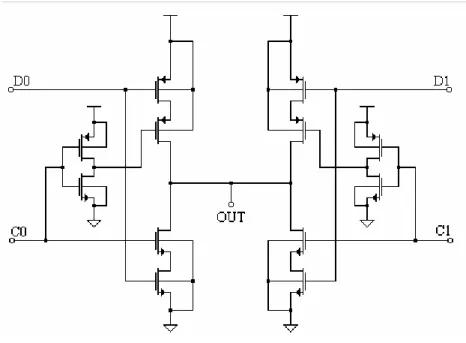

Figura 4.1 Schema elettrico del flip-flop negative-edge-triggered TSPC.

Poiché le caratteristiche di questi flip-flop risultano essere critiche per il corretto funzionamento del sistema, abbiamo optato per una loro realizzazione fullcustom,

in modo tale da poterne ottimizzare il comportamento mediante un opportuno dimensionamento dei transistori. L’architettura che si è deciso di utilizzare è di tipo dinamico True Single Phase Clock (TSPC), la quale a differenza dell’implementazione statica consente un minore ingombro di area. La Figura 4.1 mostra lo schema elettrico del circuito, si noti come esso risulta essere costituito dalla cascata di un inverter di tipo TSPC di tipo n, da una porta dinamica di tipo n e da un inverter TSPC di tipo p; si è inoltre prevista la presenza del transistore di reazione, il quale ha la funzione statica di mantenere il nodo H a valore logico basso quando l’uscita si trova a livello logico alto, e quella dinamica di abbreviare il tempo di risoluzione della metastabilità. Il funzionamento del sistema può essere compreso osservando la Figura 4.2.

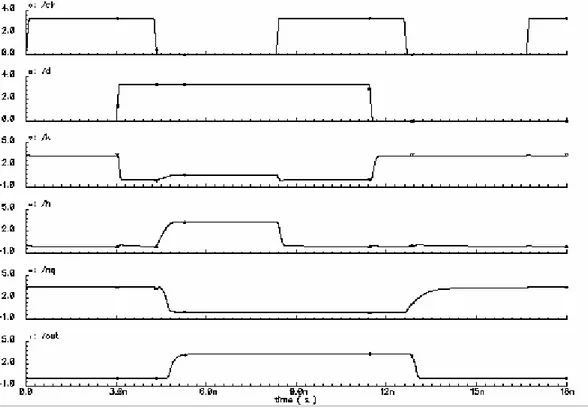

Figura 4.2 Andamento dei segnali nel circuito del flip-flop.

Quando il segnale CK si trova a livello logico alto abbiamo che il nodo H viene precaricato a 0 e il flip-flop si trova in condizioni di mantenimento, in quanto nessun transistore può imporre alcun valore logico in uscita. Fintanto che CK è 0 il potenziale del nodo K è fissato dallo stato dell’ingresso D, se infatti questo è a livello logico alto avremo che K viene precaricato a 0, se invece è a livello logico basso K viene precaricato ad 1. Nell’istante di arrivo del fronte in discesa di CK,

avremo che l’uscita assume il medesimo potenziale del nodo K; a questo punto successive variazioni dell’ingresso D non apportano alcuna modifica sull’uscita e il flip-flop mantiene il dato campionato. Si è quindi osservato che il campionamento del dato avviene in corrispondenza del fronte in discesa del clock. Tale fatto avrà importanti conseguenze sul funzionamento di tutti i restanti blocchi che compongono i circuiti di campionamento. Dalla descrizione del funzionamento del circuito si comprende che il segnale D dovrà arrivare un tempo

SETUP

t prima dell’arrivo del fronte in discesa del segnale CK, in modo che il nodo K possa essere precaricato al suo valore finale in modo corretto.

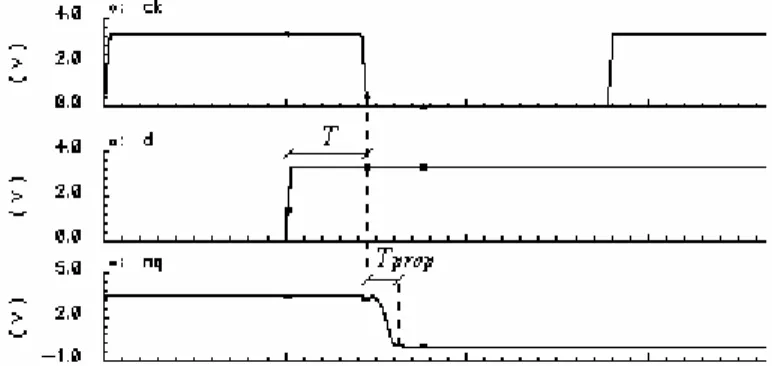

Figura 4.3 Schematizzazione del metodo di misura del tempo di setup del flip-flop.

Riferendoci alla Figura 4.3 si ha che il tempo di setup del flip-flop può essere determinato variando parametricamente il valore T. Il tSETUP corrisponde a quel valore di T oltre il quale il tempo di propagazione del flip-flop risulta essere costante. Per valori di T <tSETUP si ha invece che il tempo di propagazione è variabile, a causa del fatto che il circuito funziona in zona metastabile. I tempi di setup nel caso di simulazioni WS e WP sono riportati in Tabella 19.

Tabella 19 Tempi di setup del DFF nel caso di simulazioni WS e WP.

WS WP

SETUP

t 210 ps 115 ps

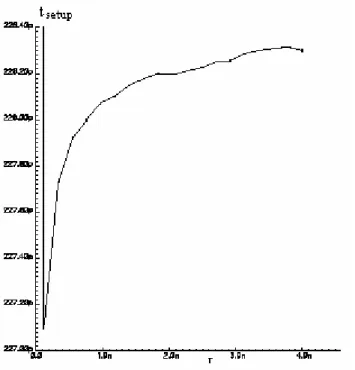

Tuttavia abbiamo osservato che per T >tSETUP il tempo di propagazione è solo in prima approssimazione costante, infatti come mostrato in Figura 4.4 e Figura 4.5, abbiamo una leggera variazione al crescere all’aumentare di T. Tale fatto costituisce un problema in quanto il flip-flop viene utilizzato per campionare il

segnale MSB, da cui si verrebbero ad avere tempi di propagazione differenti a seconda dell’uscita della DLL seriale che abbiamo selezionato per realizzare il primo livello d’interpolazione.

Figura 4.4 Variabilità del tempo di propagazione: caso WS.

In particolare si noti come la variazione complessiva di tprop sia di 17.03 ps nel caso WS e di 1.22 ps nel caso WP. Volendo ridurre tali variazioni basterebbe restringere l’intervallo utile di funzionamento del flip-flop, considerando un tempo di setup maggiore. Ad esempio se si volesse mantenere la massima variazione inferiore ai 2 ps, si dovrebbe considerare nel caso WS un tempo di setup di 1.375 ns, tuttavia operando in questo modo si avrebbe una notevole restrizione dell’intervallo utile di funzionamento.

4.2 Il multiplexer

Il circuito multiplexer ha il compito di selezionare una delle 32 uscite della DLL seriale, in funzione dei segnali di comando prodotti dall’unità di calcolo (vedi capitolo 2). Più nel dettaglio abbiamo che nel particolare tipo di applicazione dove questo circuito serve, si deve utilizzare una architettura ottimizzata in modo che il ritardo introdotto su tutti gli ingressi sia identico. La necessità del rispetto di una tale specifica ha portato ad una progettazione del circuito interamente fullcustom, in modo da poter uguagliare i percorsi dei vari ingressi verso l’uscita, in fase di realizzazione del layout.

Le differenze tra i ritardi introdotti, possono essere dovute a diversi fattori quali asimmetrie del circuito o accoppiamenti capacitivi dovuti alla variabilità dei segnali d’ingresso e alle capacità parassite dei transistori. Utilizzando un multiplexer a due livelli di logica a causa della complessità del circuito la specifica che ci siamo proposti diventerebbe difficilmente verificabile. Si è quindi pensato ad una realizzazione di tipo 3-state, in questo modo solo l’ingresso abilitato impone il suo dato in uscita mentre tutti gli altri si trovano in alta impedenza. L’utilità di tale realizzazione è notevole, in quanto tutti gli ingressi sono connessi all’uscita mediante circuiti identici, e quindi a parte a causa di eventuali mismatch risentono tutti del medesimo ritardo. Il problema del mismatch è notevolmente sentito in questo circuito in quanto i tempi di propagazione del multiplexer sono dell’ordine del nano-secondo, da cui si possono avere errori di matching di qualche pico-secondo, ossia confrontabili con

la risoluzione del sistema d’interpolazione. Per ovviare a questo abbiamo progettato il sistema in modo da ridurre il più possibile gli errori di matching.

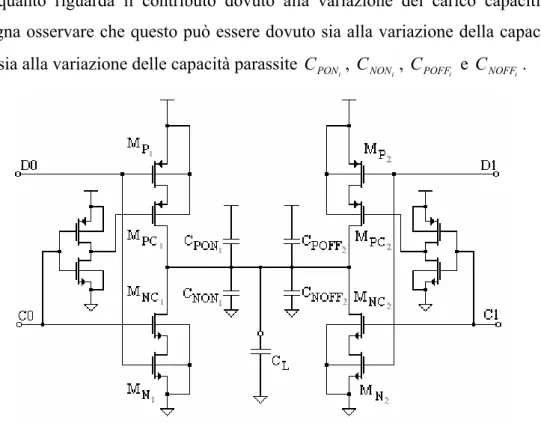

Figura 4.6 Schema elettrico di due celle 3-state con uscita cortocircuitata.

Nella Figura 4.6 mostriamo lo schema elettrico di due porte 3-state con uscita cortocircuitata. I segnali C0 e C1 rappresentano i comandi di abilitazione della cella, e devono essere a livello logico alto non contemporaneamente. Si noti inoltre come entrambi gli ingressi D0 e D1 risentano del medesimo carico capacitivo e come propagandosi verso l’uscita attraversino il medesimo circuito elettrico.

Figura 4.7 Circuito elettrico delle due 3-state cortocircuitate, in cui si sono messe in evidenza i

Il funzionamento della porta 3-state può essere facilmente compreso osservando che quando C0 è a livello logico alto e C1 a livello logico basso, la cella di destra si trova in alta impedenza mentre quella di sinistra impone il dato in uscita. Viceversa quando C0 è a livello logico basso e C1 a livello logico alto, la cella di sinistra si trova in alta impedenza mentre quella di destra impone il dato.

Cerchiamo adesso di comprendere quali siano gli effetti del mismatch sul ritardo di propagazione, per un circuito di questo tipo. La Figura 4.7 mette in evidenza le capacità presenti nel circuito. Poiché abbiamo detto che C0 e C1 non sono a livello logico alto contemporaneamente, possiamo ricondurre il nostro circuito a quello equivalente mostrato in Figura 4.8. In tale circuito i valori di capacità risultano essere:

Pi PCi PCi i DB SB DB PON C C C C = + + ( 4-1 ) Ni NCi NCi i DB SB DB NON C C C C = + + ( 4-2 ) PCi i DB POFF C C = ( 4-3 ) NCi i DB NOFF C C = ( 4-4 )

Per determinare tali valori si è supposta la resistenza di canale trascurabile, in questo modo accade che la cella 3-state attiva vede in uscita oltre alle capacità parassite dovute ai transistori interni, anche quelle dovute ai transistori esterni1. Come abbiamo osservato nel paragrafo 2.2, il ritardo di una cella di questo tipo risulta essere:

β

C K

tP = ⋅ ( 4-5 )

Le differenze sul tempo di propagazione possono essere dunque attribuite sia ad un mismatch sul carico capacitivo sia ad uno sul valore del β. Da cui l’errore

assoluto che potremo avere sarà: ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛∆ + ∆ ⋅ = ∆ β β C C t tP P ( 4-6 )

1 Nel calcolo della capacità si sono trascurati i contributi dovuti alla capacità di sovrapposizione, in

Per quanto riguarda il contributo dovuto alla variazione del carico capacitivo bisogna osservare che questo può essere dovuto sia alla variazione della capacità

L

C , sia alla variazione delle capacità parassite CPONi, CNONi, CPOFFi e CNOFFi.

Figura 4.8 Circuito elettrico equivalente delle due 3-state con uscita cortocircuitata.

Notiamo infatti che la capacità CL, è dovuta al circuito connesso in uscita al multiplexer, da cui potrà variare, in quanto le dimensioni reali dei dispositivi di tale circuito potranno essere differenti da quelle nominali. Il suo effetto non viene risentito se la cella è realizzata come in figura, in quanto la variazione della capacità è la medesima sia per cella di sinistra che per quella di destra, mentre è causa di differenza dei tempi di propagazione se non tutte le celle presentano la loro uscita cortocircuitata2. Per quanto riguarda la variazione dovuta alle capacità parassite, questa è presente indipendentemente dal tipo di architettura utilizzata. Si fa infatti osservare che i valori di tali capacità dipendono dai parametri geometrici dei dispositivi e quindi solo nominalmente hanno il medesimo valore. Dunque nel caso reale avremo che i valori assunti dalle capacità parassite saranno differenti a seconda della cella selezionata e quindi avremo che ciascuna cella vedrà un carico capacitivo totale differente da quello delle altre. Si vuol infine fare notare che la riduzione degli errori di matching dovuto al β e alla capacità, può essere ottenuta

2 Questo risulterà essere maggiormente chiaro quando analizzeremo le due strutture di multiplexer

andando ad aumentare le dimensioni dei transistori utilizzati. Detto questo andremo, nel seguito del paragrafo, ad analizzare due possibili architetture di multiplexer entrambe basate su una struttura ad albero 3-state, ma con un numero di livelli differente. Le due architetture si differenziano per velocità ed errore di matching introdotto, effettueremo quindi un confronto fra le due basato su tali prestazioni descrivendo il perché della scelta effettuata. Vogliamo inoltre mettere in evidenza che sia nel calcolo della velocità del multiplexer che nell’analisi del matching, ci riferiremo al solo fronte in discesa, infatti come detto nel paragrafo precedente il flip-flop è di tipo negative-edge-triggered da cui solamente tale fronte è rilevante ai fini del campionamento. Questo fatto avrà importanti conseguenze sulla realizzazione finale del multiplexer.

4.2.1 Struttura ad albero 3-state ad un livello

Questa struttura presenta un unico livello 3-state, ossia abbiamo 32 celle identiche cortocircuitate assieme per formare l’uscita. Il vantaggio di tale realizzazione è senza alcun dubbio la riduzione dell’errore di matching, infatti abbiamo che le variazioni sulla capacità possono essere dovute solamente alle capacità parassite mentre la capacità CL risulta essere identica per tutte. Tuttavia a causa del fatto che tutte le uscite sono connesse insieme avremo che ciascuna cella risente delle capacità parasite delle altre trentuno, da cui il carico capacitivo complessivo sull’uscita può risultare elevato e quindi portare ad un aumento del tempo di propagazione. Tale problema è fortemente sentito, se si osserva anche che non è eliminabile semplicemente aumentando le dimensioni dei transistori, in quanto questo apporterebbe un corrispondente aumento anche delle capacità parassite. La Figura 4.9 mostra una simulazione WS effettuata sul sistema, si noti come il segnale d’uscita abbia un andamento triangolare a causa della lentezza del circuito ed inoltre come non sia abbia mai il raggiungimento dei pieni livelli logici. La verifica del corretto funzionamento del multiplexer può essere effettuata andando a valutare il tempo di propagazione relativo a ciascun ingresso.

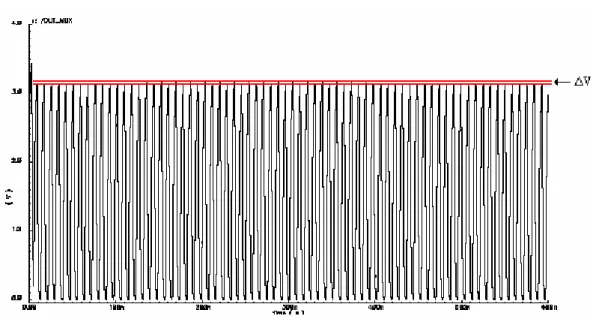

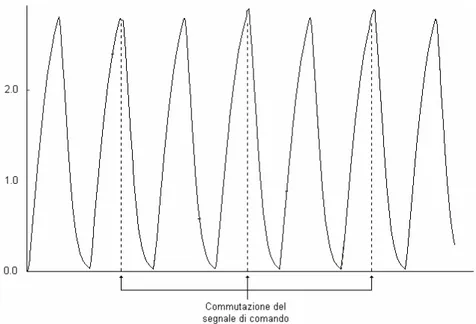

Figura 4.9 Andamento del segnale in uscita dal multiplexer nel caso WS.

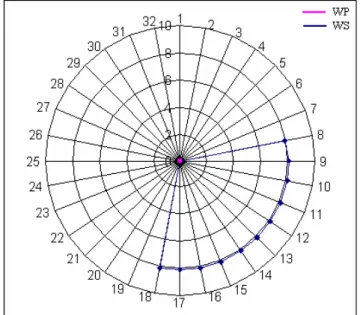

Per fare questo abbiamo effettuato una simulazione nella quale si seleziona successivamente tutti e 32 gli ingressi, e si va a valutare il ritardo di ciascuno di questi rispetto all’uscita. I risultati ottenuti nel caso WS e WP sono mostrati in Figura 4.10.

Si noti come nel caso della simulazione WP l’errore commesso sia sempre nullo, mentre in quella WS si abbia un picco dell’errore per i clock compresi fra CK8 e CK18. L’entità dell’errore è relativamente piccola, tuttavia non è desiderata in quanto porta ad un errore sistematico sul funzionamento del sistema. Poiché l’errore è presente solo nel caso WS, la causa è da ricercarsi nella scarsa velocità di commutazione del multiplexer. Mediante simulazioni abbiamo potuto constatare una variazione dell’errore in funzione dell’istante di arrivo del segnale di comando. A causa del fatto che l’uscita non riesce a raggiungere i pieni livelli logici accade che il segnale di comando arrivi in un istante di tempo in cui la tensione di uscita sta variando. Avremo quindi che la commutazione tra la conduzione di una cella e la successiva comporta un picco di tensione sull’uscita (vedi Figura 4.11), il quale introduce una variazione sul tempo di propagazione del multiplexer. Sostanzialmente poiché il picco di tensione porta l’uscita ad un valore di tensione maggiore di quello raggiunto nelle altre condizioni, si viene ad avere un aumento del tempo necessario all’uscita per tornare a valore logico basso, e quindi un aumento del tempo di propagazione sul fronte in discesa. L’entità del picco di tensione è stata valutata attorno ai 100 mV.

Figura 4.11 Uscita del multiplexer i condizioni WS, relativa al selezionamento di tutti gli

ingressi.

L’andamento di Figura 4.11 mostra come non tutti i segnali d’uscita della DLL seriale siano influenzati dal segnale di comando, tale fatto è attribuibile allo sfasamento presente fra i vari segnali selezionati.

Figura 4.12 Influenza del segnale di comando sull’uscita del multiplexer.

Si è notato infatti che l’influenza del segnale di comando è sempre presente, ma tuttavia porta a effettive variazioni del tempo di propagazione solamente per quei segnali il cui raggiungimento del valore massimo è prossimo all’istante di arrivo del segnale di comando. La Figura 4.12 mette in evidenza quanto detto, consentendo una maggiore comprensione del problema.

La presenza di tale errore, il quale risulta essere quattro volte superiore alla risoluzione del sistema d’interpolazione, ha portato a scartare questo tipo di implementazione, dirigendo le nostre scelte verso una architettura di multiplexer più veloce la quale è costituita da due livelli 3-state e sarà dettagliatamente analizzata nel paragrafo seguente.

4.2.2 Struttura ad albero 3-state a due livelli

Questa struttura presenta due livelli di celle 3-state connesse come in Figura 4.13. L’idea di base è stata quella di realizzare una struttura più veloce che quindi presentasse livelli logici in uscita migliori di quella ad un unico livello. Poiché il problema della bassa velocità di commutazione della struttura ad un livello era dovuto alla presenza delle capacità parassite di tutte e 32 le celle, si è pensato di risolvere questo problema connettendo le celle a gruppi di 8.

Figura 4.13 Schema a blocchi della struttura 3-state a due livelli.

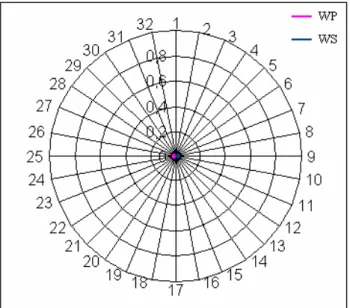

In questo modo si ha una drastica riduzione della capacità vista in uscita dalla singola, e quindi un conseguente miglioramento dei livelli logici in uscita. A questo punto una delle uscite dei quattro gruppi in cui sono state divise le celle del primo livello, può essere selezionata mediante le celle 3-state del secondo livello. Questo multiplexer necessita quindi di ulteriori quattro segnali di comando che identifichino il gruppo di appartenenza del segnale d’ingresso da selezionare. La verifica del corretto funzionamento del circuito è stata effettuata andando a selezionare successivamente tutti e 32 gli ingressi, e valutando il ritardo di ciascuno di questi rispetto all’uscita. I risultati ottenuti nel caso WS e WP sono mostrati in Figura 4.14.

Figura 4.14 Grafico dell’errore sui tempi di propagazione del multiplexer.

In figura possiamo osservare come il multiplexer realizzato con questa architettura non sia affetto dall’errore dovuto all’arrivo dei segnali di comando; tale fatto è

dovuto alla maggiore velocità del circuito e al netto miglioramento dei livelli logici in uscita. Il sistema tuttavia presenta maggiori problemi dal punto di vista del matching, in quanto le uscite delle celle del primo livello 3-state non sono tutte cortocircuitate tra loro, da cui celle appartenenti a gruppi diversi vedono come carico un differente inverter. Dunque come accennato nel paragrafo 0, avremo una variazione della capacità d’uscita dovuta all’aleatorietà della capacità

L

C . Poiché il sistema d’interpolazione utilizzato presenta una risoluzione di 2 ps, dobbiamo limitare sotto questo valore l’errore di matching, altrimenti si verrebbe ad avere un errore sui tempi di propagazione superiore alla risoluzione del sistema. Tale specifica è stata rispettata ricorrendo a simulazioni Montecarlo sul multiplexer, le quali ci hanno consentito di dimensionare opportunamente il circuito. Come detto nel paragrafo 0, si deve limitare l’errore di matching per i soli fronti in discesa, cosa che può essere ottenuta andando ad aumentare solamente le dimensioni dei transistori NMOS (vedi relazione (4-6)), evitando dunque di aumentare troppo l’area del multiplexer finale.

Figura 4.15 Densità di probabilità dell’errore di matching sul tempo di propagazione del

La Figura 4.15 mostra l’andamento della densità di probabilità dell’errore di matching ottenuto tramite le simulazioni effettuate. Tale figura è relativa all’errore di matching nel caso peggiore ossia a quello relativo a due ingressi appartenenti a blocchi differenti. Si osservi come l’andamento sia approssimativamente gaussiano, con media centrata su 260.4 ps. Da tale figura si osserva che il 66% dei multiplexer prodotti presenterà un errore di matching inferiore ai 2 ps, ossia inferiore alla risoluzione del sistema d’interpolazione, come appunto si desiderava ottenere3. Le dimensioni dei transistori componenti le celle 3-state che consentono di ottenere questi risultati sono quelle riportate in Tabella 20.

Tabella 20 Dimensioni dei transistor dei due livelli 3-state.

Primo livello 3-state

Transistor Dimensioni

Mp1 W = 6 um, L = 0.3 um

Mpc1 W = 6 um, L = 0.3 um

Mnc1 W = 10 um, L = 0.3 um

Mn1 W = 10 um, L = 0.3 um

Secondo livello 3-state

Transistor Dimensioni Mp1 W = 2 um, L = 0.3 um Mpc1 W = 2 um, L = 0.3 um Mnc1 W = 2 um, L = 0.3 um Mn1 W = 2 um, L = 0.3 um

4.3 Campionamento corretto

Nel paragrafo 2.3 abbiamo tracciato le linee generali sul funzionamento del sistema a due livelli d’interpolazione. In questo paragrafo si intende effettuare una

3 Tale percentuale risulta essere abbastanza buona, se si tiene di conto del fatto che il design-kit

utilizzato per le simulazioni Montecarlo risulta essere un po’ datato rispetto all’attuale processo tecnologico utilizzato dalla AMS.

analisi maggiormente dettagliata, atta ad individuare i problemi di corretto campionamento del circuito. Si è gia osservato come la DLL seriale riceva in ingresso il segnale di clock e fornisca in uscita i 32 segnali CK0,….CK31, che vengono utilizzati per ritardare i fronti di MSB generato dall’accumulatore. Dato che quest’ultimo funziona alla stessa frequenza di clock della DLL seriale, avremo che i fronti di MSB risultano sfasati rispetto a quelli del clock di una quantità pari al tempo di propagazione tprop del registro di uscita dell’accumulatore. A seconda del valore di tprop, è possibile che le prime uscite della linea non possano essere impiegate per campionare il segnale MSB, in quanto il fronte in salita di questo potrebbe arrivare dopo il loro fronte in discesa, causando un campionamento errato. E’ inoltre importante osservare che il fronte in discesa dell’uscita della DLL seriale selezionata, deve arrivare dopo un tempo

SETUP

t rispetto al fronte di MSB, in modo tale da far funzionare il flip-flop in modo corretto (vedi Figura 4.16). E’ stato quindi necessario introdurre degli opportuni circuiti di ritardo, realizzati mediante due inverter in cascata, dopo il multiplexer, in modo tale da rispettare queste specifiche.

Figura 4.16 Relazione temporali fra i segnali interni all’interpolatore.

Osservando la Figura 4.16 si ricava che il valore del ritardo da introdurre è pari a: MUX

prop SETUP

RIT t t t

t = + − ( 4-7 )

L’introduzione di tali circuiti risolve solo in parte il problema del corretto campionamento di MSB, infatti se da una parte siamo riusciti a fare in modo che

le prime uscite della DLL seriale campionino in modo corretto, dall’altra avremo che inevitabilmente le ultime uscite non potranno essere direttamente utilizzate per ritardare i fronti; infatti poiché ciascuna uscita è traslata rispetto a quella che la precede di un tempo pari a 260.4 ps, avremo che inevitabilmente i fronti in discesa delle ultime arriveranno quando oramai il segnale MSB è tornato a valore logico basso (vedi Figura 4.16). Per ovviare a questo problema si può pensare di fare campionare il segnale MSB a tutte le uscite della DLL seriale fino ad una CKi opportuna, e fare campionare una replica di questo ritardata MSB_RIT, alle restanti. La Figura 4.17 riassume in termini grafici quanto detto. Si osservi che il segnale MSB_RIT si può ottenere andando a campionare MSB con una opportuna uscita CKp della DLL seriale.

Figura 4.17 Metodo di campionamento da parte di tutti e 32 i clock ricorrendo ad MSB e

MSB_RIT.

Dal punto di vista pratico abbiamo effettuato delle simulazioni necessarie a determinare il valore del tempo tRIT che consentisse il corretto funzionamento in tutte le condizioni operative. Per comprendere il modo in cui si è operato chiamiamo con, DFF1 il flip-flop che realizza il primo livello d’interpolazione, D_DFF1 il dato in ingresso a questo e con CK_DFF1 il segnale connesso al suo ingresso di clock. In Figura 4.18 è mostrata la simulazione effettuata sul circuito. Si osservi come il fronte in discesa del segnale CK_DFF1 arrivi in anticipo rispetto alla transizione da 0 ad 1 del segnale D_DFF1 di una quantità pari a 256.377 ps.

Figura 4.18 Simulazione dell’interpolatore: calcolo di tRIT.

Dovremo quindi introdurre un ritardo pari a:

ps t

tRIT =256.377+ SETUP =466.377 ( 4-8 ) Poiché la simulazione è stata effettuata in condizioni TM conviene introdurre sul segnale CK_DFF1 un ritardo superiore a quello dato dalla relazione (4-8), pertanto il valore che abbiamo scelto è stato di 1.112 ns, in questo modo oltre a consentire il corretto campionamento in tutte le condizioni operative, abbiamo anche ridotto l’errore dovuto alla variabilità del tempo di propagazione (vedi paragrafo 4.1). In Figura 4.19 è riportato il circuito di ritardo utilizzato, con le relative dimensioni dei transistori che lo compongono.

La simulazione effettuata con l’aggiunta del circuito di ritardo ci ha permesso di valutare il corretto campionamento da parte di CK0, con un margine fra il fronte in salita di D_DFF1 e quello in discesa di CK_DFF1 pari a 1.04 ns. A questo punto è necessario andare a valutare il numero di clock che riescono a campionare correttamente il segnale MSB. Per fare questo abbiamo effettuato una simulazione WS mediante la quale abbiamo determinato il tempo T (vedi Figura 4.20).

Figura 4.20 Calcolo di T.

Poiché ciascun clock è sfasato rispetto a quello che lo precede della quantità

ps

TS =260.4

∆ , avremo che il numero di clock che campiona correttamente MSB è: 27 10 4 . 260 10 1023 . 7 12 9 = ⎥ ⎦ ⎥ ⎢ ⎣ ⎢ ⋅ ⋅ = ∆ = ° −− S CLOCK T T n ( 4-9 )

Quindi tutti i clock fino a CK27 riescono a campionare correttamente MSB. Tuttavia a causa di inevitabili differenze fra il circuito reale e quello simulato abbiamo deciso di fare campionare il segnale MSB ai clock da CK0 a CK24, in modo tale che quando è selezionato CK24 il fronte in discesa del clock CK_DFF1 anticipa quello del segnale D_DFF1, di una quantità pari a 0.781 ns. In queste condizioni avremo che i clock da CK25 a CK31 devono campionare il segnale MSB_RIT, dunque il ritardo che deve essere introdotto sul segnale MSB affinché si possa avere un campionamento corretto da parte di tali clock, risulta essere:

(

)

T nstRIT_MSB = 31−25 ∆ S =1.5624 ( 4-10 ) Tale ritardo può essere ottenuto sfruttando il clock CK6 per campionare il segnale MSB. Vogliamo fare notare che operando in questo modo in realtà si introduce un ritardo su MSB pari a:

porp MSB

rit ns t

Dove tprop rappresenta il tempo di propagazione del registro utilizzato per effettuare l’operazione di campionamento di MSB. Poiché il registro che si utilizza è il flip-flop di tipo TSPC, il tempo di propagazione è di circa 0.2 ns, quindi trascurabile.

Figura 4.21 Simulazione dell’interpolatore: campionamento di CK31.

In Figura 4.21 è possibile constatare il corretto campionamento del clock CK31 sul segnale MSB_RIT. Anche in questo caso abbiamo che quando è selezionato CK31, il fronte in discesa di CK_DFF1 anticipa quello di D_DFF1 di un tempo pari a 1.49 ns, garantendoci un buon margine di sicurezza. Detto questo dobbiamo valutare quali siano le condizioni temporali da rispettare per l’arrivo dei segnali di comando al multiplexer. Abbiamo detto che il circuito sincrono produce i segnali di comando un ciclo di clock prima dell’arrivo del fronte in salita di MSB. Tuttavia a causa delle modifiche circuitali apportate per consentire il corretto campionamento può accadere che i segnali di comando arrivino prima del fronte in discesa del clock CK31 (vedi Figura 4.22). Questo comporterebbe che tale clock non riesca a campionare il segnale MSB_RIT, infatti prima che questo campioni il multiplexer ha già ricevuto i nuovi segnali di comando e quindi si troverebbe in una fase di commutazione. Dunque è necessario ritardare

opportunamente l’arrivo di tali segnali in modo che la loro variazione in ingresso al multiplexer avvenga dopo l’arrivo del fronte in discesa di CK31.

Figura 4.22 Relazioni temporali fra i segnali di comando e i segnali interni all’interpolatore.

Per ottenere questo si è provveduto ad utilizzare un circuito di ricampionamento dei segnali di comando sfruttando uno dei clock prodotti dalla DLL seriale. Osservando la Figura 4.21 ricaviamo che il clock utile a questo scopo è:

11 1 1 ⎥= ⎥ ⎤ ⎢ ⎢ ⎡ ∆ = S COM COM T T CK ( 4-12 )

Lo stesso clock viene utilizzato anche per campionare il segnale di selezione di MSB o MSB_RIT, in modo tale che la scelta di quale dei due utilizzare avvenga dopo il corretto campionamento di tutti i clock. Mediante simulazioni abbiamo potuto valutare il corretto arrivo dei segnali di comando, e dunque il corretto campionamento del primo livello d’interpolazione.

Una analisi analoga a questa deve essere svolta anche per il secondo livello d’interpolazione, in quanto anche per questo bisogna garantire il corretto campionamento del flip-flop. Bisogna infatti osservare che il segnale di campionamento del primo flip-flop viene inviato anche in ingresso al secondo livello d’interpolazione, in modo tale che il ritardo ulteriore introdotto da questo stadio consenta di realizzare l’interpolazione completa del sistema. Il dato in uscita dal primo flip-flop è poi inviato al secondo flip-flop, il quale sfrutta come

segnale di clock l’uscita del secondo livello d’interpolazione. Si ha dunque che il dato in ingresso a questo arriva dopo un tempo tprop rispetto al primo campionamento, mentre il segnale di clock del secondo flip-flop arriva dopo un tempo tR +M⋅∆T/128 pari al ritardo introdotto dal secondo livello d’interpolazione. Affinché il campionamento possa avvenire in modo corretto è necessario garantire che il segnale di clock del secondo flip-flop arrivi dopo un tempo tSETUP dall’arrivo del dato. Similmente a prima indicheremo con, DFF2 il flip-flop che realizza il secondo livello d’interpolazione, D_DFF2 il dato in ingresso a questo e con CK_DFF2 il segnale connesso al suo ingresso di clock.

Figura 4.23 Simulazione dell’interpolatore: campionamento di DFF2.

La Figura 4.23 mostra la simulazione del sistema con la cella C della DLL innovativa impostata per introdurre il ritardo minimo; tale situazione è la più sfavorevole per il segnale CK_DFF2, dunque il funzionamento in tale condizioni garantisce il corretto campionamento qualunque sia la condizione di aggancio dell’anello ad aggancio del ritardo. Osservando la Figura 4.23 abbiamo che il fronte in discesa di CK_DFF2 arriva dopo la transizione da 0 ad 1 di D_DFF2 di un tempo pari a 0.817 ns, nettamente superiore al tempo di setup del flip-flop. Quindi il secondo campionamento avviene in modo corretto e non si necessita di aggiungere alcun circuito di ritardo. Anche per questo stadio è poi necessario

garantire l’arrivo dei segnali di comando dopo il campionamento del dato, da cui abbiamo impostato la cella C sulla condizione di ritardo massimo ed effettuando una simulazione WS abbiamo determinato il tempo tCOM2 di Figura 4.24.

Figura 4.24 Simulazione dell’interpolatore: calcolo di tCOM2.

Avremo pertanto che il clock da utilizzare per effettuare il ricampionamento dei segnali di comando è: 19 10 4 . 260 10 1234 . 5 12 9 2 2 ⎥= ⎥ ⎤ ⎢ ⎢ ⎡ ⋅ ⋅ = ⎥ ⎥ ⎤ ⎢ ⎢ ⎡ ∆ = −− S COM COM T t CK ( 4-13 )

Sulla base dell’analisi di corretto campionamento fatta, si ha che il circuito d’interpolazione completo, è quello mostrato in Figura 4.25.

Si vuole infine fare osservare che poiché i circuiti di ricampionamento sono costituiti da un elevato numero di flip-flop di tipo D, l’uscita della DLL non può essere direttamente utilizzata come segnale di clock ma necessiterà dell’inserimento di opportuni buffer che consentano il corretto pilotaggio di un carico capacitivo così elevato. Vogliamo fare notare che tali buffer vengono inseriti in modo automatico dal tool di sintesi Design Analizer, andando a specificare il carico capacitivo di tale nodo, e quindi non devono essere realizzati a livello fullcustom.

Figura 4.25 Schema a blocchi del sistema d’interpolazione.

Andiamo adesso a valutare il funzionamento globale del sistema, andando ad analizzare il caso più critico, ovvero quello di sintesi della massima frequenza d’uscita. In questo caso avremo che il segnale MSB è costituito da un’alternanza di 0 ed 1 di durata pari a un periodo di clock. Avremo inoltre che i segnali di comando saranno tali da selezionare in successione tutte le uscite della DLL seriale, da cui avremo la selezione di CK0, CK1, …, CK31, per poi tornare di nuovo a selezionare CK0. Il circuito funziona correttamente se il ritardo introdotto dal campionamento di due clock successivi è pari a 260.4 ps.

In Figura 4.26 è riportata la caratteristica di conversione del primo livello d’interpolazione, si osservi come il comportamento del circuito sia con ottima approssimazione lineare4. Una valutazione maggiormente precisa della non linearità dell’interpolatore può essere valutata osservando la Figura 4.27, nella quale è stato riportato l’errore, nel caso WS e WP, fra il ritardo reale ottenuto dalla simulazione e quello ideale pari a 260.4 ps.

Figura 4.27 Errore introdotto dal circuito interpolatore.

Come possiamo osservare l’errore è praticamente nullo nel caso WP, mentre è diverso da zero nel caso WS, tuttavia l’entità di tale errore è notevolmente contenuta, da cui il comportamento globale dell’interpolatore è molto buono.

4 In questa simulazione sono stati inviati in ingresso al multiplexer 32 segnali ideali sfasati fra loro

di 260.4 ps, e non le uscite della DLL seriale, in modo tale da valutare le eventuali differenze di ritardi dovute alle restanti parti circuitali.