Capitolo 1

Riferimenti di tensione

I circuiti analogici fanno largo utilizzo di riferimenti di tensione e corrente. Questi riferimenti forniscono grandezze continue che hanno la minima dipendenza ottenibile dalla tensione d’alimentazione e dalla temperatura. I riferimenti maggiormente utilizzati sono i cosidetti a

‘band gap’. Questi circuiti sono realizzati in forma integrata in qualsiasi tecnologia CMOS

standard sfruttando i BJT verticali parassiti di substrato.

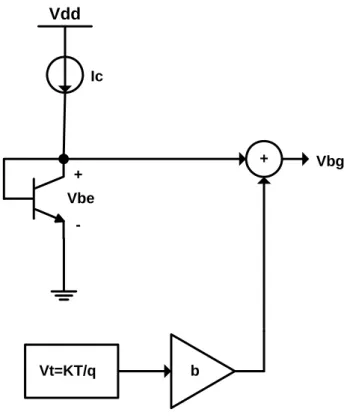

Schema di principio del band-gap

In figura 1.1 è mostrato lo schema di principio del band-gap [1]. Un transistore bipolare montato a diodo è alimentato da un generatore di corrente I . La caduta c V sulla giunzione be

base-emettitore dipende dalla temperatura applicata con un coefficiente termico negativo (NTAT).

Per compensare questa variazione si somma alla V una tensione proporzionale a quella be

termica q kT Vt = dove 1 5 10 617 . 8 ⋅ − − = JK

k costante di Boltzmann, q=1.6⋅10−19C carica

dell’elettrone, che quindi abbia un coefficiente termico positivo (PTAT). In questo modo è possibile annullare la derivata della tensione d’uscita V : bg

Vbg =Vbe +bVt (1.1) T V b T V T Vbg be t ∂ ∂ + ∂ ∂ = ∂ ∂

Vediamo ora più in dettaglio le dipendenze dei termini dalla temperatura. b + Vt=KT/q Vdd Ic Vbe Vbg +

-Figura 1.1: Schema di principio del band-gap

Tensione con coefficiente termico negativo

La tensione base-emettitore di un transistore bipolare o più in generale una giunzione p-n polarizzata in diretta, ha un coefficiente termico negativo. Per un transistore bipolare possiamo scrivere: ⎟⎟⎠ ⎞ ⎜⎜ ⎝ ⎛ = t be V V s c I e I (1.2)

b n i e s N D n qA I 2 = (1.3)

dove N è il drogaggio della base, b A l’area di emettitore, e D la costante di diffusione degli n elettroni, n la concentrazione di portatori nel silicio intrinseco. Esplicitandoi D come: n

q kT

Dn =μn (1.4)

dove μnè la mobilità degli elettroni, e sostituendo nella (1.3) si ottiene:

2 2 2 i n b i n e n b i e s kTn N kTn A q kT N n qA I = ⋅μ = μ ∝μ (1.5)

Le dipendenze dalla temperatura di μne

2 i n sono: m n μ0T μ ∝ dove 2 3 − ≈ m (1.6) ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − ∝ kT E i g e T n2 3

con Eg ≈1.12eV energia del gap del silicio. La corrente di saturazione risulta quindi:

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = + − kT E e cT Is 4 m g (1.7)

Dalla (1.2) posso ricavare l’espressione di V : be ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = s c t be I I V V ln (1.8)

Andiamo a calcolare la derivata di V rispetto alla temperatura considerando in prima be

approssimazione che la I sia costante con essa. Otteniamo: c

T I I V I I T V T V s s t s c t be ∂ ∂ − ∂ ∂ = ∂ ∂ ln (1.9) Dalla (1.7) abbiamo:

(

)

⎟⎟⎠ ⎞ ⎜⎜ ⎝ ⎛ − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + + + = ∂ ∂ kT E g m kT E m s g g e kT E cT e T m c T I 2 4 3 4 (1.10) quindi:(

)

t g t s s t V kT E T V m T I I V 2 4+ + = ∂ ∂ (1.11)Sostituendo quest’espressione nella (1.9) possiamo scrivere:

(

)

(

)

T q E V m V V kT E T V m I I T V T V g t be t g t s c t be − + − = − + − = ∂ ∂ 4 4 ln 2 (1.12)Da quest’equazione si nota che il coefficiente termico di V dipende anch’esso dalla be

temperatura, pertanto l’annullamento perfetto della

T Vbg

∂ ∂

si avrà solo per uno specifico valore

0

T di quest’ultima.

Tensione con coefficiente termico positivo

Per generare una tensione con coefficiente termico positivo è possibile sfruttare ancora le proprietà del transistore bipolare. Infatti se due transistori sono polarizzati con correnti diverse, la differenza tra le loro tensioni di base-emettitore è proporzionale a V e quindi alla t

temperatura. In figura 1.2 è mostrato un semplice circuito che genera una tensione con coefficiente termico positivo [2].

Vdd

+

-Q1 Q2

V

nI0 I0

Figura 1.2: Circuito per la generazione di una tensione con coefficiente termico positivo.

Se i due transistori sono uguali Is1 =Is2 e ipotizzando le loro correnti di base trascurabili rispetto a quelle di collettore, si ottiene:

V n I I Vt I nI V V V V V t s s t be be be ln ln ln 2 0 1 0 2 1 − = − = = Δ = (1.13) quindi: n q k T Vbe = ln ∂ Δ ∂ (1.14)

Band-gap tradizionale

Avendo ottenuto due tensioni con coefficienti termici opposti, è possibile ottenere un riferimento che ha nominalmente un coefficiente termico nullo. Scriviamo

n V V V V

Vref = be +αΔ be = be +α tln . A temperatura ambiente:

• T Vbe ∂ ∂ varia da K mV o 3 − a K mV o 2 − • K mV T V o t =0.087 ∂ ∂

Supponendo ricavato dalle simulazioni il valore di

T Vbe ∂ ∂ , per avere =0 ∂ ∂ T Vref occorre fissare il valore di αlnnopportuno. Un circuito che implementa quanto detto prima è quello di

Figura 1.3: Circuito che genera una tensione indipendente dalla temperatura.

In questo circuito Q1 è un singolo transistore, Q2 è costituito da n transistori in parallelo.

Supponendo ideale l’amplificatore e ponendo R1 =R2abbiamo:

3 3 2 1 3 ln R n V R V V I = be − be = t (1.15)

e quindi una tensione d’uscita pari a:

V n V V n R R V Vout be 1 tln be2 t ln 3 2 2 ⎟⎟ = + α ⎠ ⎞ ⎜⎜ ⎝ ⎛ + + = (1.16) A R1 R2 R3 + + -Vout nA A Q1 Q2

L’analisi che abbiamo effettuato è vera con l’ipotesi che la corrente di collettore non dipenda dalla temperatura. In realtà l’equazione (1.15) mostra che questo non è vero. Vediamo come cambia la (1.9) includendo la T Ic ∂ ∂ : ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ∂ ∂ − ∂ ∂ + ∂ = ∂ ∂ T I I T I I V I I T V T V s s c c t s c t be ln 1 1 (1.17) Sostituendo T I R n V T T Ic t c = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ∂ ∂ = ∂ ∂ 3 ln ottengo:

(

)

T q E V m V T V g t be be − + − = ∂ ∂ 3 (1.18)L’espressione (1.18) indica che il coefficiente termico di V e’ leggermente meno negativo di be

quanto previsto dalla (1.12). In pratica sono necessarie accurate simulazioni per prevederne il valore.

CMOS band-gap

Abbiamo visto come ottenere una tensione indipendente dalla temperatura sfruttando le proprietà dei transistori bipolari. Per realizzare un circuito band-gap in tecnologia standard CMOS è quindi possibile utilizzare i transistori pnp parassiti di substrato come mostrato in figura 1.4. La zona drogata p+ dentro la n-well funziona da emettitore, la n-well stessa da base, il substrato p da collettore ed è connesso al potenziale più basso. Il circuito di figura 1.3 può essere implementato con transistori pnp come mostrato in figura 1.5 [2].

Figura 1.4: Realizzazione di un transistore bipolare pnp in tecnlogia CMOS. A R1 R2 R3

-++

Vout -A nA Q1 Q2Tensione indipendente dalla variazione dell’alimentazione

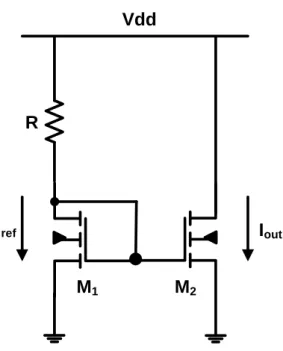

Torniamo allo schema di figura 1.1. Per ottenere una tensione di riferimento indipendente dalla variazione dell’alimentazione, allo stesso modo deve essere la corrente I che polarizza c il transistore bipolare. La corrente I , può essere generata con uno specchio di corrente come c quello di figura 1.6 [2].

M1 M2

Iref Iout

R

Vdd

Figura 1.6: Specchio di corrente con resistenza di polarizzazione.

La corrente d’uscita Iout di questo circuito però è sensibile alla V : dd

1 2 1 1 ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⋅ + Δ = Δ L W L W g R V I m dd out (1.19)

Una soluzione può essere quella di figura 1.7 [2].

M

1M

2I

refI

outM

3M

4V

ddK(W/L)

N(W/L)

N(W/L)

P(W/L)

PFigura 1.7: Specchio di corrente con corrente d’uscita indipendente dall’alimentazione.

Se trascuriamo la modulazione della lunghezza del canale otteniamo:

Iout = KIref (1.20) Per definire unicamente le correnti, si aggiunge nel circuito una resistenza nello specchio n-mos come in figura 1.8 [2].

M

1M

2I

refI

outM

3M

4V

ddK(W/L)

N(W/L)

N(W/L)

P(W/L)

PR

Figura 1.8: Aggiunta di R per definire le correnti.

Possiamo scrivere: Vgs1 =Vgs2 +RIout (1.21) ref out I I = out th N ox n out th N ox n out

RI

V

L

W

K

c

I

V

L

W

c

I

+

+

⎟

⎠

⎞

⎜

⎝

⎛

=

+

⎟

⎠

⎞

⎜

⎝

⎛

1 22

2

μ

μ

out N ox n out RI K L W c I = ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ 1 1 2 μ (1.22) e quindi: 2 2 1 1 1 2 ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = K R L W c I N ox n out μ (1.23)

La corrente d’uscita risulta indipendente dalla tensione d’alimentazione.

Circuito di start up

Il circuito di figura 1.8 ha due punti di lavoro stabili. Uno è quello previsto dall’equazione (1.28), l’altro è quello con correnti nulle. Per portare il circuito a lavorare nel corretto punto di funzionamento viene aggiunto un circuito detto di start up. Ad esempio per il circuito di figura 1.8, il problema viene risolto semplicemente aggiungendo il transistore M5 connesso a diodo (figura 1.9) che fornisce un percorso per la corrente dall’alimentazione a massa attraverso i transistori M3 e M1[2]. In questo modo M3 e M1 e quindi M2 e M4 non possono rimanere spenti. Devono essere verificate la condizioni Vth1 +Vth5 +Vth3 <VDD e

DD gs

th

gs V V V

M1 M2 M3 M4 Vdd R M5

Figura 1.9: Aggiunta di M5 al circuito di figura 1.8 per ottenere il circuito di start up.

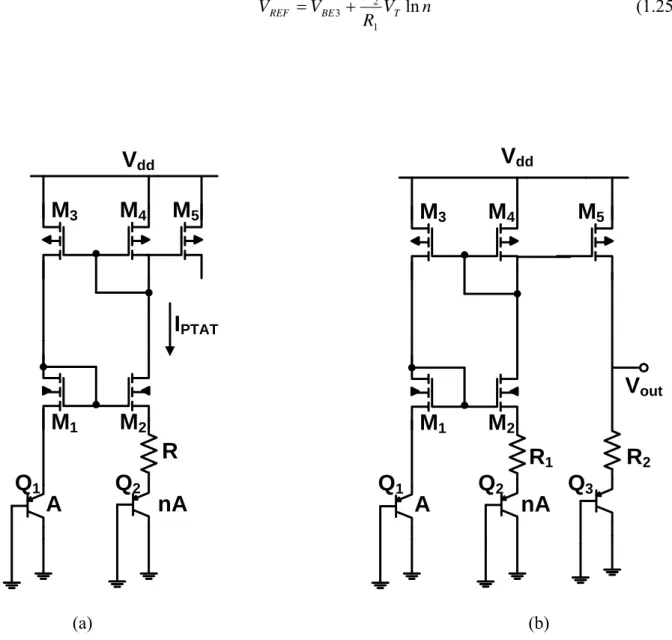

Generazione di una corrente con coefficiente termico positivo

In molte riferimenti presenti in letteratura è utile un circuito che generi una corrente con coefficiente termico positivo (PTAT). Una topologia che realizza quanto detto è quella di figura 1.11 a. Se M1 =M2, M3 =M4: R n V I Id d t ln 2 1 = = (1.24)

Dove ne’ il rapporto tra l’area di Q2e Q1.

Sfruttando questo schema è possibile realizzare un riferimento di tensione a band-gap (figura 1.10 b) sommando la tensione PTAT Id5R2 alla tensione base emettitore di Q . Si ottiene la 3

tensione d’uscita [2]: V n R R V VREF BE T ln 1 2 3 + = (1.25)

M

1M

2M

3M

4V

ddR

I

PTATM

5A

nA

Q

1Q

2M

1M

2M

3M

4V

ddR

1M

5A

nA

Q

1Q

2R

2Q

3V

out (a) (b)Riferimenti di tensione presenti in letteratura

Passiamo adesso in rassegna alcune delle possibili soluzioni presenti in letteratura per la generazione di riferimenti di tensione cercando di indagare quali potrebbero essere adatte alle specifiche del nostro progetto che sono:

• Tensione d’alimentazione ≤ 1 V • Basso consumo di potenza <1 μW • Completa integrabilità

• Ridotta occupazione dell’area occupata sul chip • Sensibilità di linea e coefficiente termico bassi

I band-gap tradizionali forniscono in uscita una tensione di riferimento di circa 1.25 V e quindi necessitano di un’alimentazione maggiore. Questi circuiti quindi non possono essere utilizzati per applicazioni in cui è richiesto un basso consumo di potenza. Altri sfruttano i transistori bipolari che in tecnologia CMOS richiedono passi di fabbricazione aggiuntivi ed ulteriori maschere litografiche [3], [4]. Sono necessari quindi circuiti che impiegano solo MOSFET.

La soluzione[5] presenta un riferimento in tecnologia AMS 0.6 μm CMOS basato sulla differenza pesata tra le Vgs di un n-mos e di un p-mos. Tutti i transistori lavorano in saturazione. I transistori M1, M2 e RBgenerano la corrente di polarizzazione IB (PTAT). Il

transistoreM amplifica la corrente di un fattore M e la inietta in un carico attivo formato 5

dalle resistenze R1, R2 e dai MOSFET M e N MP. La tensione d’uscita viene ricavata

⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + ⋅ ⋅ + ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ − ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = − ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = p ox p n ox n B thp thn gsp gsn ref L W C L W C R R I V V R R V V R R V μ μ 1 1 1 1 1 2 1 2 1 2 1 (1.26) dove IB vale: 2 1 2 2 1 1 2 ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = L W L W R C I B ox p B μ (1.27)

La sua derivata rispetto alla temperatura è costituita dalla somma di un termine lineare ed uno non lineare e si annulla se sono verificate le condizioni:

1 2 1 = − vthn vthp R R β β (1.28)

( )

( )

2 2 0 0 0 2 2 1 ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − p n vthn vthp r p n n p n p T T T T L W L W μ μ β β β β β β μ μ μ μ n μβ eβμpsono gli esponenti della dipendenza della mobilità dalla temperatura nel processo AMS 0.6 μm CMOS. Questo schema però non riesce ad operare sotto un volt d’alimentazione

occupata sul chip. Inoltre la dipendenza della mobilità dalla temperatura viene eliminata solo alla temperatura di riferimento come è evidente dalla seconda relazione delle (1.28). Lo schema è mostrato in figura 1.12.

Figura 1.12: Riferimento basato sulla differenza pesata tra le Vgs di un n-mos e di un p-mos [5].

La soluzione [6] utilizza un processo CMOS 0.35 μm e non prevede l’utilizzo di resistori. La resistenza di polarizzazione è sostituita da due MOSFETM , 3 M4 montati a diodo e quelle

d’uscita da un divisore di tensione costituito da M , 9 M . Inoltre, mentre in [5] tutti i 10

MOSFET lavorano in saturazione, in [6] M1, M2lavorano sottosoglia e l’espressione della

⎥ ⎦ ⎤ ⎢ ⎣ ⎡ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − = T ds T th gs T D V V mV V V L W V I μ 2 exp 1 exp (1.29)

Questo permette sia di ottenere un’area d’occupazione molto piccola (0.015 mm2), che bassi consumi di potenza (300nW). La tensione d’uscita vale:

0 7 9 9 10 10 8 2 1 / / 1 1 I k L W L W k V Vref th ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + + = (1.30) Dove I ha l’espressione: 0 C V h L W L W N N K V m I T n ox T 2 / / ln 1 2 2 1 1 2 2 2 2 4 2 2 0 μ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = (1.31)

dove N = K3/ K4 , m è il parametro di ‘swing’ sottosoglia. La derivata della tensione di

riferimento rispetto alla temperatura si annulla se è verificata la condizione:

⎟⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − + = 1 / / / / / 7 7 8 8 8 8 1 9 9 10 10 L W L W h L W k qK L W L W B t (1.32)

La dipendenza della mobilità dalla temperatura è in questo caso completamente eliminata e non solo alla temperatura di riferimento. Questa soluzione però ha una tensione d’alimentazione minima di 1.5 V. Lo schema proposto in [6] è mostrato in figura 1.13.

Figura 1.13: Riferimento con divisore di tensione in uscita [6].

Altra soluzione ancora in tecnologia CMOS 0.35 μm è quella in [7] in cui si utilizza un’architettura ripiegata ed un carico attivo formato da un n-mos montato a diodo. Il circuito utilizza transistori con due diverse tensioni di soglia: M1 e M sono 5V-NMOS con tensione 3

di soglia di 0.7 V, M2 e M4 sono 3.3V-NMOS con tensione di soglia di 0.45 V e -0.75 V per

n-mos e p-mos rispettivamente. Le due tensioni di soglia permettono di far lavorare i transistoriM1 e M sottosoglia 3 M2 e M4 in saturazione. In queste condizioni, la corrente I 0

ha l’espressione:

(

)

⎟⎟⎠ ⎞ ⎜⎜ ⎝ ⎛ − = 1 1 3 3 2 2 2 2 4 4 0 0 / / ln 1 2 / L W L W V m N L W C I μ ox T (1.33)dove 2 2 4 4 / / L W L W N =

La tensione d’uscita vale:

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + = + = 1 1 3 3 10 10 4 4 10 10 0 10 / / ln / / 1 2 L W L W L W L W N mV V K I V V T th th ref (1.34)

La sua derivata rispetto alla temperatura si annulla se è verificata la condizione:

(

)

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − = 1 1 3 3 10 10 4 4 / / ln 1 / / L W L W q k m N K L W L W B tn (1.35)Anche per questo schema, viene eliminata la dipendenza della mobilità dalla temperatura, inoltre, essendo i p-mos connessi alla tensione d’alimentazione e gli n-mos a massa, non è presente l’effetto body. Il circuito proposto ha il più piccolo coefficiente di temperatura (10 ppm), la tensione d’alimentazione più bassa (0.9 V), e il consumo di potenza di gran lunga inferiore a quello di tutti gli altri (decine di nW). Lo schema è quello di figura 1.14.

Figura 1.14: Riferimento con architettura ripiegata [7].

L’unico riferimento di tensione in tecnologia CMOS 90 nm in letteratura è quello della pubblicazione [8] (figura 1.15). Il circuito è costituito da due generatori di corrente diversi. Il primo genera una corrente proporzionale alla temperatura (PTAT), il secondo una corrente proporzionale ad una V e quindi con coefficiente termico negativo (NTAT). Le due correnti gs con coefficienti termici opposti sono sommate ed inviate ad un blocco convertitore corrente-tensione che genera la corrente-tensione di uscita. I transistori MOSFET M1, M2 dello specchio Widlar lavorano sottosoglia. La loro corrente di drain puo’ essere espressa come:

⎟⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − ≅ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − = T th gs D T ds T th gs D D nV V V L W I nV V nV V V L W I

I 0 exp 1 exp 0 exp (1.36)

n è il parametro di ‘swing’ sottosoglia, ID0e’ la corrente di drain per Vgs =Vth e = S =1

L W

. I transistori M3, M4 dello specchio semplice lavorano in saturazione. Per lo specchio Widlar possiamo scrivere:

Vgs2 =Vgs1 +R1IR1 (1.37)

Ricavando Vgs1, Vgs2 dalla 1.36 e sostituendo nella 1.37 si ottiene il valore della corrente IR1:

( )

( )

( )

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ≅ = = 2 1 1 1 1 1 ln S S qR kT n R T V T I T IR PTAT R (1.38)Il generatore di corrente NTAT e’ costitutito dai MOSFET M5-M9. M5 lavora sottosoglia, la sua tensione gate-source e’ data da:

( )

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + ≅ 5 0 5 ln S I I q kT n V T V D D th gs (1.39)La corrente che scorre in M7 risulta:

9 8 2 5 2 S S R V I IR = Vgs = gs (1.40)

Le due correnti PTAT e NTAT sono specchiate rispettivamente da M10 e M11 sommate ed inviate alla resistenza R ottenendo in uscita la tensione: 3

⎥ ⎦ ⎤ ⎢ ⎣ ⎡ + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = 9 8 2 5 2 1 1 3 ln S S R V S S R mV R V T gs ref (1.41)

Questa soluzione però non è la più adatta per i nostri scopi avendo un consumo di potenza superiore al μW, sensibilità di linea e coefficiente di temperatura troppo elevati.

Figura 1.15: Riferimento in tecnologia CMOS 90 nm [8].

![Figura 1.12: Riferimento basato sulla differenza pesata tra le Vgs di un n-mos e di un p-mos [5]](https://thumb-eu.123doks.com/thumbv2/123dokorg/7288728.85571/18.892.183.714.312.812/figura-riferimento-basato-differenza-pesata-vgs-mos-mos.webp)