4 Ambiente di sviluppo e setup di test

In questo capitolo sarà descritto l’ambiente di sviluppo software, setup di test e misure fatte sul tag.

4.1 Ambiente di sviluppo

4.1.1 Software di scrittura, compilazione e simulazione

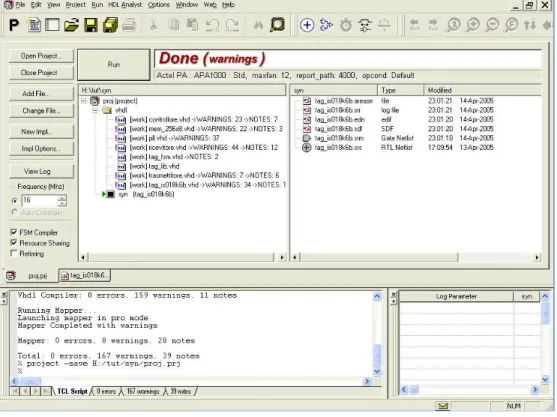

Il software utilizzato per la scrittura, compilazione e simulazione del progetto VHDL è Active - HDL. La versione utilizzata è la 6.2, con licenza evaluation di durata 45 gg, versione che si presenta molto valida per progetti abbastanza complessi, come quello affrontato nella presente tesi.

L’interfaccia utente come mostra la figura 4.1 evidenzia i punti di forza di questo software: semplice ed intuitiva. Ogni blocco VHDL descritto nel capitolo 3 sarà costituito da un file .vhd.

A questo livello si ha una compilazione sintattica, per verificare che il codice VHDL sia stato correttamente utilizzato.

Il software presenta anche gli strumenti di simulazione pre layout, simulazione funzionale che non tiene conto dei ritardi introdotto dalle porte logiche del dispositivo FPGA che verrà scelto per il test finale, e di post

layout, simulazione effettuata dopo la sintesi.

Le simulazioni del tag vengono effettuate tramite la creazione di file chiamati test bench, file che permettono di definire forme d’onda d’ingresso fittizie e che permettono di osservare il comportamento del modello. Questo

è un primo approccio di debugging dal punto di vista funzionale, molto utile.

Le simulazioni fatte attraverso il file di test bench sono state quelle di riproduzione delle forme d’onda d’ingresso, segnale seriale asincrono, con le trame ricevute dal tag, sul segnale line_in. Sono state effettuate simulazioni con tutte le istruzioni del protocollo implementate, ai fini di valutare la risposta del tag a tutte le istruzioni del protocollo di comunicazione.

Tutti i comandi sono stati simulati correttamente. Sono state fatte anche simulazioni con errori, sia di framing che di CRC, e questi sono stati individuati correttamente dal tag, che ha eseguito correttamente le operazioni di ripristino (riportare le macchine a stati dei diversi blocchi, nelle condizioni di iniziali). Sono state effettuate anche simulazioni da parte del micro, di scrittura e lettura in memoria, e nei registri accessibili del tag, specificati nel capitolo 3.

Figura 4.1 Interfaccia utente Active – HDL 6.2

Figura 4.2 Simulazione istruzione GROUP_SELECT_EQ con BYTE_MASK (0x00)

4.1.2 Software di sintesi

Il software di sintesi utilizzato è il SYNPLIFY PRO 7.5.1, compresa nel pacchetto LIBERO, disponibile sempre con licenza evaluation. Abbiamo

detto nel capitolo 3, che una prima operazione fondamentale per l’implementazione hardware è rappresentata dalla sintesi. La sintesi non è altro che la traduzione del codice VHDL in una struttura in forma di rete di porte logiche (netlist). Non è sempre possibile sintetizzare ciò che si è scritto in VHDL, anche se si è rispettata la sintassi del linguaggio e si è effettuato una simulazione corretta del modello, perché alcuni costrutti potrebbero essere non orientati alla sintesi.

Figura 4.3 Software synplify pro 7.5.1

Il software ha bisogno di tutti i file utilizzati per il progetto in formato .vhd, indicando il file che rappresenta il top dell’intero progetto, file che esegue il collegamento fisico tra tutti i blocchi e che fornisce i segnali accessibili dall’esterno del FPGA (line_in, line_out, clock, reset, etc.), la

frequenza di clock di sistema ed il dispositivo FPGA da utilizzare. Il dispositivo FPGA è un Actel della famiglia APA 1000 (Actel Pro Asic), dispositivo presente sulla scheda prototipale fornita dalla CAEN e che verrà utilizzata per il test.

Il risultato della sintesi sarà costituito da un file .edn che costituisce la netlist delle porte logiche del progetto, con un primo timing analisys. Nel report di sintesi, saranno evidenziate la frequenza massima di lavoro, anche se quella effettiva sarà letta nel report di fitting finale, occupazione celle logiche dell’FPGA.

Il file .edn sarà utilizzato anche per la simulazione post layout del progetto, simulazione che vengono fatte considerando i ritardi introdotti fisicamente dalle porte logiche. Per questo tipo di simulazione si adotta nuovamente lo strumento Active – HDL, utilizzando gli stessi file di test bench per la simulazione funzionale.

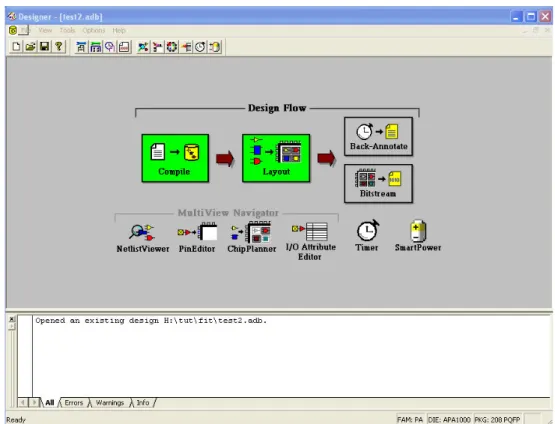

4.1.3 Software di Place & Route

L’ultima fase prima di programmare fisicamente il dispositivo è il fitting

device o place and route. Lo strumento software viene fornito solitamente

dal produttore del FPGA (ogni produttore usa il suo software di fitting). Il software utilizzato per il nostro progetto fa parte sempre del pacchetto LIBERO 6.0, ed è il Designer v6.0, software fornito dall’ ACTEL, produttore dell’ APA1000.

Attraverso questo software è possibile scegliere il dispositivo FPGA, il tipo di package ed il pin out (scelta dei pin accessibili esternamente dell’FPGA).

Figura 4.4 Interfaccia Actel Designer 6.0

Il report di fitting ci indica qual’è lo spazio occupato e ci da informazioni sul timing analisys, specificando la frequenza di lavoro massima del sistema. A questo punto, verificati i valori, si passa alla creazione del file binario .stp, che servirà per la programmazione del FPGA (è un dispositivo flash based), tramite il programmatore dell’ACTEL ed il software Actel FlashPro.

Figura 4.5 Fase di programmazione dell’FPGA

4.2 Dispositivo FPGA

4.2.1 Introduzione ai circuiti integrati digitali

I circuiti digitali comunemente richiesti nei progetti elettronici sono disponibili sul mercato come circuiti integrati già pronti, per questo detti anche componenti off-the-shelf. La realizzazione di un nuovo circuito integrato si rende necessaria quando non esiste sul mercato un dispositivo per l'applicazione richiesta. In questo caso il dispositivo è detto ASIC (Application Specific Integrated Circuit). Il progettista disegna un ASIC e lo fa realizzare da un produttore di dispositivi; oppure acquista dal produttore un dispositivo che poi dovrà configurare per ottenere le funzioni richieste.

Gli ASIC si classificano in base alla metodologia di progettazione adoperata. L'approccio Full Custom fornisce il massimo grado di libertà al progettista, che può disegnare i dettagli a livello dei transistors nelle

maschere di produzione. Con il metodo Standard Cell, il produttore fornisce una libreria di celle logiche già disegnate, tra cui scegliere quelle adatte. Le celle scelte possono essere posizionate nel dispositivo, e poi configurate e collegate intervenendo solo sulle maschere di metallizzazione. Il metodo Gate Array è una variante del precedente. Tutte le celle utilizzabili sono già posizionate in una matrice nel dispositivo e si possono solo stabilire le connessioni negli strati di metallo. Infine è possibile acquistare un dispositivo già fisicamente realizzato prima che il progetto applicativo specifico abbia inizio. In questo caso il produttore vende un dispositivo programmabile (PLD Programmable Logic Device), cosiddetto perchè dotato di un set di funzioni elementari che, opportunamente configurate attraverso un'operazione di "programmazione", permettono di realizzare un'applicazione specifica richiesta dal progettista. (Notare che l'acronimo PLD viene spesso utilizzato al posto di PAL per indicare un particolare tipo di PLD, il Programmable Array Logic).

Tra i diversi tipi di PLD, attualmente sono molto diffusi gli FPGA (Field Programmable Gate Array). L'acronimo indica che il dispositivo è fondamentalmente un gate array, solo che le connessioni tra le celle non si eseguono una volta per tutte col disegno delle metallizzazioni, ma si

programmano sul campo, anche più di una volta. Un FPGA contiene un

insieme di celle logiche, celle di I/O e linee di interconnessione. Per definire un circuito si configura ogni cella logica affinché realizzi una particolare funzione combinatoria o sequenziale tra quelle elementari disponibili e si definiscono le interconnessioni tra le celle. Questa configurazione è rappresentata da un file, una sequenza di bit (risultato finale del progetto) che può essere inserita in una memoria del dispositivo quando questo viene alimentato e può essere conservata in una memoria esterna non volatile.

4.2.2 FPGA

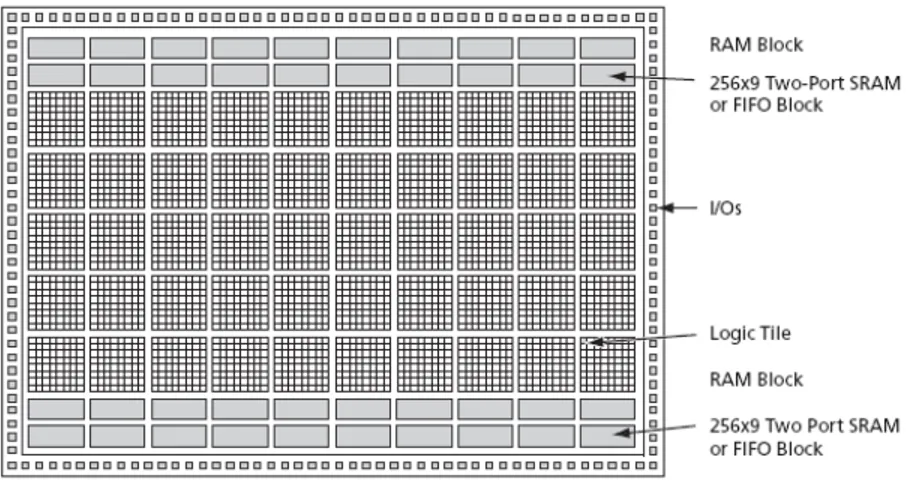

Il disposto FPGA scelto per l’implementazione hardware ed il test è della famiglia ACTEL ProASICPLUS, APA1000. Le specifiche del dispositivo

sono mostrate in figura 4.3.

L’architettura ACTEL ProASICPLUS offre fino ad un milione di system

gate, 198 kbits di SRAM dual port e fino a 712 celle di I/O. Il dispositivo ha

una granularità molto fine, con un core organizzato in una Sea-of-Tile come mostra la figura 4.7.

Figura 4.7 Architettura del dispositivo ACTEL ProASICPLUS

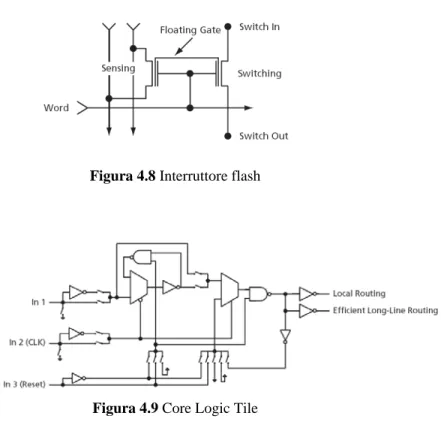

Ogni tile può essere configurata come una funzione logica a tre ingressi (porta NAND, D-Flip-Flop, etc.) ed una uscita, programmando appropriatamente gli interruttori Flash di interconnessione. Gli interruttori Flash sono presenti in tutto il dispositivo, e provvedono ad una programmazione non volatile e riconfigurabile.

Il dispositivo contiene anche alcuni componenti dedicati quali memorie SRAM sincrone e asincrone, blocchi FIFO, PLL, componenti presenti in FPGA di ultima generazione, utili per supportare un ampio spettro di progetti (saranno utilizzati anche in questo progetto).

Figura 4.8 Interruttore flash

Figura 4.9 Core Logic Tile

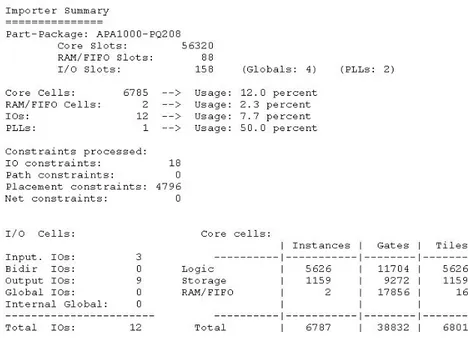

4.3 Risultati di sintesi e fitting device

Di seguito riportiamo i file di report dei risultati di sintesi e place and

route del tag progettato, su dispositivo FPGA APA1000.

La frequenza stimata dal sintetizzatore è compatibile con la frequenza utilizzata per l’intero sistema.

Figura 4.11 Risultati di fitting (timing analysis)

Qui la frequenza stimata è di 20.94 MHz, anche questa compatibile con la frequenza utilizzata ne sistema. Questa risulta maggiore della prima, ed è questa la frequenza effettiva.

Figura 4.12 Risultati fitting (occupazione porte logiche)

4.4 Setup di test

Elenchiamo, in seguito, quali sono stati gli strumenti di misura utilizzati per il test del tag.

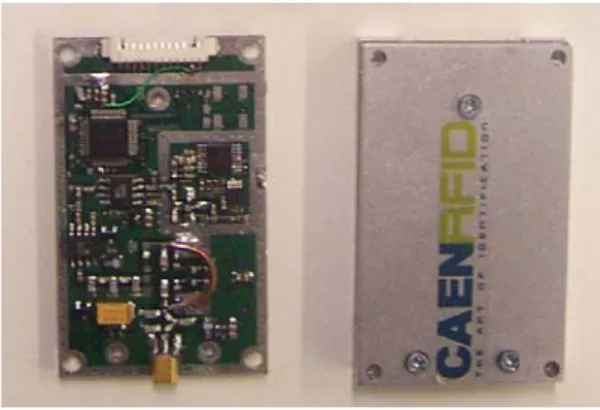

4.4.1 Scheda prototipale

La scheda prototipale su cui è montato l’ FPGA è stata fornita dalla CAEN ed è mostrata in figura.

Figura 4.13 Scheda prototipale ed FPGA

La scheda monta un oscillatore esterno a 20 MHz, che è collegato al pin 145 dell’ FPGA (da considerare nelle impostazioni di pin out, pin dedicato al clock esterno o all’ingresso del PLL quindi si è avuto la necessità di utilizzare il PLL interno del FPGA, per abbassare la frequenza di clock e ottenere quella richiesta del progetto: 16MHz.

Presente anche un tasto di reset asincrono collegato sulla scheda al pin 30 (anche questo sarà considerato nell’impostazione di pin out).

Si è utilizzata la libreria del PLL e dell’ FPGA anche per le simulazioni e la sintesi, ed infine per fitting del progetto.

Altre componenti embedded utilizzate sono: RAM256x9SST e

FIFO256x9SST che corrispondono rispettivamente ad una memoria dual

port ed una fifo entrambe sincrone da 256 locazioni da 9 bit. Anche per questi due componenti sono state utilizzate le librerie vhdl per la simulazione, sintesi e fitting. Utilizzando queste strutture, si è ottenuto un

risparmio delle celle logiche occupate nell’ FPGA (le locazioni di memoria avrebbero occupato 256 registri da 8 bit per la memoria del tag, più 10 della fifo). Questo problema non si pone per le dimensioni del FPGA utilizzato (1000000 di porte logiche fig. 4.3), ma è da precisare che insieme al tag sarà implementato anche il micro, un progetto grande che richiede molto spazio. Comunque entrambi sono stati correttamente sintetizzati e piazzati all’interno dell’FPGA.

4.4.2 Lettore RFID

Il lettore RFID utilizzato è un lettore portatile che CAEN ha realizzato, e che implementa il protocollo di comunicazione ISO18000 - 6. Il lettore genera una onda RF, con potenza massima di 50 mWatt. In figura 4.14 è mostrato il lettore.

Figura 4.14 Lettore RFID

Il software che gestisce il lettore è un semplice emulatore di terminale, il tera term, liberamente scaricabile dalla rete. La comunicazione PC - lettore avviene attraverso la porta seriale (COM1), ad una velocità di 19200 kbps.

Non appena il lettore viene alimentato a 5 volt, la schermata del tera term che si presenta è quella mostrata in figura

Figura 4.15 Schermata del tera term all’accensione del lettore

La figura 4.15 mostra le istruzioni utilizzate per il test del tag.

Quelle che serviranno per il test del tag sono il Group Select Equal (con BYTE_MASK “00”), da cui ci aspettiamo la risposta del tag tramite la trasmissione del suo UID, i due comandi di Write e Write4byte (2,3), i comandi di Read e Read Unadressed (4,5), e il comando di anticollisione (6).

4.4.3 Antenna del lettore

Antenna: Planar Antenna Huber+Suhner:

Figura 4.0.16 Specifiche antenna test

4.4.4 Parte RF

Per il test del tag, è necessaria la parte analogica di front-end e RF. Il blocco RF utilizzato è quello presente su un tag implementato già da CAEN, il tag semipassivo modello A927, da cui sono stati collegati i pin di line_in (in del tag) e line_out (out del tag) come mostra la figura 4.17.

4.5 Test del prototipo

I test effettuati sul prototipo, sono test orientati alla verifica del corretto funzionamento della macchina a stati del tag progettato, caratterizzazioni di performance di lettura a distanze diverse (verifica del protocollo), e test in condizioni di disturbo per verificare se le scelte di progetto fatte, sono compatibili con tag passivi e semipassivi di tipo commerciale, già utilizzati da CAEN.

Le distanze di misura utilizzate sono di 2 e 3 m (distanze più piccole rispetto a quelle specificate perchè i test sono stati effettuati in ambienti con forti riflessioni).

![Figura 4.6 Specifiche tecniche famiglia Actel Pro Asic plus [10]](https://thumb-eu.123doks.com/thumbv2/123dokorg/5673014.72138/9.918.209.760.403.915/figura-specifiche-tecniche-famiglia-actel-pro-asic-plus.webp)