________________________________Capitolo 4

Progettazione hardware del prototipo

4.1 Introduzione

Questo capitolo si occupa della progettazione hardware del prototipo di display led che è stato realizzato nel corso di questa tesi.

Come è stato accennato nei capitoli precedenti, il dispositivo realizzato consiste in un display a led con interfaccia seriale compatibile nelle proprie funzionalità con una famiglia di display lcd grafici Matrix Orbital.

In particolare si è fatto riferimento ad uno specifico modello di display lcd di questa famiglia, il GLK12232-25SM, che possiede uno schermo a matrice 122 x 32. Per motivi di carattere pratico il prototipo a led ha una matrice differente (125 x 28), ma questo non crea alcun problema nell’utilizzo del software MOGD, che risulta compatibile con una vasta gamma di formati di display.

Nel corso di questo capitolo verrà fornita dapprima una descrizione funzionale dell’intero oggetto, e successivamente saranno esposti i criteri che hanno portato alla scelta dei componenti. L’ultima parte del capitolo è dedicata invece a una breve descrizione delle fasi che hanno portato alla realizzazione dei circuiti stampati e al montaggio dell’intero prototipo.

4.2 Struttura del prototipo

Vista l’intenzione di voler realizzare un dispositivo che sia compatibile e che abbia le stesse funzionalità (o quasi) del display lcd Matrix Orbital, si sono dovute garantire le seguenti caratteristiche fondamentali:

• Possibilità di rappresentazione grafica e testuale.

• Opportunità di salvare in modo permanente fonts e bitmaps.

• Presenza di un’interfaccia seriale per la comunicazione con il sistema esterno. • Piena compatibilità circa i comandi e il protocollo di comunicazione.

• Opportunità di connessione con una tastiera a matrice con al più 25 tasti.

Dal punto di vista hardware questo si è tradotto nel dotare il dispositivo di un connettore seriale RS-232, di uno per la tastiera, di una memoria per il salvataggio di fonts e bitmaps ed infine di un microcontrollore dalle potenzialità sufficienti a svolgere tutte le operazioni. Il resto delle caratteristiche è dipendente solamente dal firmware che viene caricato nel microcontrollore stesso. Nella versione attuale del firmware non sono state implementate le funzioni relative all’utilizzo della tastiera, anche se l’hardware è stato già predisposto completamente a tale scopo. Tuttavia per quanto riguarda i comandi di tipo grafico e testuale la compatibilità è totale.

La struttura del pannello led è molto simile a quella del display Matrix Orbital. Le uniche grosse differenze risiedono nella diversa modalità di pilotaggio del display led rispetto a quello lcd e nelle correnti in gioco: per questo sono stati utilizzati dei drivers appositamente studiati per il pilotaggio di led e inoltre è stato adottato un adeguato alimentatore in grado di fornire correnti dell’ordine di alcuni Ampere.

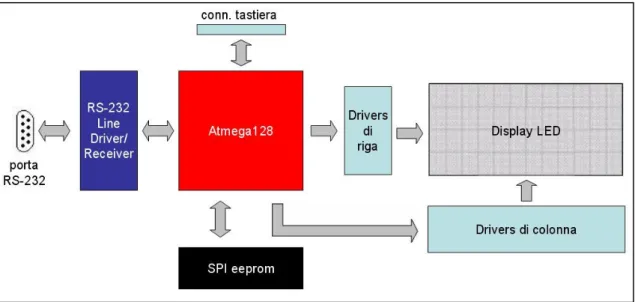

Passiamo a questo punto a elencare gli elementi principali di cui è costituito il prototipo progettato:

• Microcontrollore Atmel con architettura RISC 8 bit. • Memoria EEPROM esterna.

• RS-232 line driver/receiver. • Drivers di riga e di colonna.

• Display LED.

Per quanto riguarda il microcontrollore, esso deve svolgere le stesse attività di quello relativo al modulo lcd. Di conseguenza dovrà comunicare con il mondo esterno attraverso la porta RS-232, elaborare i comandi da essa provenienti, comunicare con la memoria EEPROM, pilotare i drivers di riga e di colonna della matrice, ed infine gestire l’interfaccia tastiera.

Per la memorizzazione di fonts e bitmaps, è stata adottata una memoria non volatile di tipo EEPROM che colloquia direttamente con il microcontrollore. Essa ha una capacità di memorizzazione analoga a quella del display lcd (16 kB), ma a differenza di quest’ultima, presenta una diversa interfaccia di comunicazione: infatti, mentre nell’unità lcd è presente una memoria con interfaccia seriale I²C, nel pannello a led viene utilizzata una memoria con interfaccia SPI. Questa è una scelta progettuale dettata dal fatto che i drivers di riga e di colonna vengono pilotati con questo tipo di interfaccia e in tal modo è stato possibile semplificare il firmware del microcontrollore.

Per quanto riguarda l’interfaccia RS-232, è noto che lo standard EIA232 utilizza dei livelli logici che non sono TTL compatibili: visto che l’intero sistema è alimentato a 5 V, è stato necessario l’utilizzo di un line driver/receiver che converta i livelli tipici dello standard RS-232 con quelli compatibili con il microcontrollore. A tale scopo sono presenti in commercio una grande varietà di circuiti integrati, dalle caratteristiche più disparate: nel prototipo è stato usato un MAX232 della Maxim, ma potevano essere utilizzati con lo stesso risultato molti altri circuiti integrati.

Come detto in precedenza, il dispositivo di visualizzazione utilizzato nel nostro progetto è un display a led: quest’ultimo costituisce la differenza fondamentale tra il modulo lcd e il prototipo. La scelta di usare un display a led costituisce il punto di partenza per il nostro progetto: infatti lo scopo a cui si voleva arrivare era proprio quello di realizzare un dispositivo simile al GLK12232-25SM, ma nella versione con display a led. Il display è costituito da 125 x 28 pixel (per un totale di 3500 led) organizzati a matrice: questo significa che tutti i led appartenti ad una stessa riga hanno un terminale a comune e tutti quelli di una stessa colonna hanno in comune l’altro terminale. In tal modo è possibile pilotare in multiplexing il display risparmiando notevolmente sul numero di drivers.

Ogni led della matrice ha un diametro di 2 mm e un passo di 2.54 mm.

Per quanto riguarda i drivers utilizzati, c’è da dire che l’uso di un display led comporta delle soluzioni circuitali di natura differente rispetto a quelle adottate nel modulo lcd. Un display lcd, infatti, si pilota in modo molto diverso rispetto ad uno a led (sia per quanto riguarda il tipo di segnali da applicare, sia per il diverso ordine di grandezza delle correnti necessarie al pilotaggio). Questo implica che nel pannello a led siano utilizzati dei drivers di potenza con i quali pilotare righe e colonne della matrice, diversamente da quanto avviene per il modulo lcd, che necessità di correnti nettamente inferiori. È stato accennato che la matrice viene pilotata in multiplexing; più precisamente la tecnica che utilizzeremo consiste nell’attivare le righe singolarmente e in successione: ogni volta che una riga diviene attiva, vengono forniti contemporaneamente tutti i segnali relativi alle colonne. Questo comporta l’utilizzo di drivers di riga che possano sopportare correnti di picco ripetitive anche dell’ordine di alcuni Ampere (nel prototipo anche fino a 5 A). I drivers di colonna, dovranno invece essere in grado di fornire (in modo praticamente continuo) qualche decina di milliampere (nel caso del prototipo 40 mA).

In figura 1 viene riportato lo schema a blocchi relativo all’hardware del prototipo; nei paragrafi successivi verranno descritti con maggiore dettaglio i componenti utilizzati per la sua realizzazione.

4.2.1 Il display LED

Il modulo Matrix Orbital preso in esame è costituito da un display lcd di matrice 122 x 32 pixel. Il display led del prototipo, invece, ha una dimensione differente, pari a 125 x 28 pixel. Questa diversità nelle dimensioni è stata dettata dal fatto che per la realizzazione dell’intero display sono stati utilizzati dei moduli led preassemblati, costituiti cioè da un insieme di led già connessi internamente a matrice. L’alternativa a questa soluzione sarebbe stata quella di utilizzare led singoli e collegarli fra loro in modo da ottenere una configurazione analoga. Se consideriamo il costo di un led tradizionale in package singolo, in linea generale esso risulta inferiore rispetto al costo unitario di un led in un modulo già assemblato (considerando led con caratteristiche simili e dello stesso costruttore). Questo deriva dal fatto che nel modulo è compreso il costo dell’assemblaggio. Quindi, dal punto di vista del costo del solo materiale, si dovrebbero utilizzare i led singoli.

Ragionando invece in termini di complessità del circuito stampato del display, l’utilizzo dei moduli comporterebbe un enorme vantaggio: questi infatti, essendo già assemblati, presentano al loro interno tutte le interconnessioni dei led secondo righe e colonne. Tali connessioni non devono pertanto essere effettuate nel pcb, consentendo una notevole semplificazione del layout. Un altro importante vantaggio che si ha con l’utilizzo dei moduli è relativo alla fase di montaggio del display: essa infatti risulta nettamente più semplice e veloce. Per fare un esempio, consideriamo un modulo 5 x 7 come quello usato per il prototipo: esso dispone di 12 terminali (5 per le colonne e 7 per le righe) per la connessione su pcb. Quindi per 35 led (cioè quelli presenti in un solo modulo) sono necessarie 12 saldature; se avessimo invece utilizzato dei singoli led avremmo dovuto compiere ben 70 saldature (senza contare eventuali fori di via che potrebbero rendersi necessari).

Queste considerazioni hanno portato alla scelta di moduli led a discapito dei led singoli. Sono stati scelti moduli 5 x 7 in quanto di facile reperibilità; inoltre per ciò che riguarda le dimensioni, si è scelto di adottare i moduli più piccoli disponibili per motivi di costo: infatti è importante notare che il costo del singolo modulo (a parità di caratteristiche e di numero di led che contiene) è proporzionale alle dimensioni dello stesso.

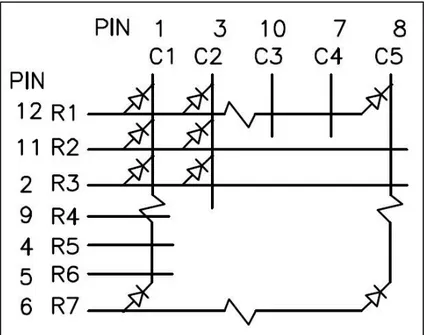

Tra i vari modelli disponibili in commercio, si è optato per il Kingbright TC07-11EWA, di cui ne viene fornita in figura 2 una rappresentazione tratta dal suo datasheet.

Figura 2 – Connessioni e piedinatura del modulo Kingbright TC07-11EWA.

Esso è costituito da una matrice di led 5 x 7 ad alta efficienza, ove questi sono connessi con colonne a catodo comune. Il singolo led ha diametro di 2 mm ed è di colore rosso. Il passo tra un led ed uno adiacente è pari a 2.54 mm. Il singolo modulo ha dimensioni pari a 12.7 mm x 17.78 mm ed ha un totale di 12 terminali.

Il display è costituito nel suo complesso da 100 moduli di questo tipo, disposti su 4 file orizzontali di 25 moduli ciascuna, per un totale di 3500 led.

Nel paragrafo successivo verrà analizzato il sistema di pilotaggio del display, specificando inoltre la struttura dei drivers utilizzati.

4.2.2 Drivers di riga e di colonna

Dal paragrafo precedente è emerso che nel display del prototipo realizzato i led di una stessa colonna hanno il catodo come terminale a comune.

Per accendere un led qualsiasi della matrice, tenendo presente la sua struttura, è necessario che in esso scorra una corrente di valore opportuno tra l’anodo (connesso alla riga) ed il catodo (connesso alla colonna). Ciò che viene fatto nel prototipo consiste nel portare la riga corrispondente al led da accendere alla tensione di alimentazione positiva e attivare il solo generatore di corrente (di sink) della relativa colonna.

Quindi, più in generale, la tecnica di pilotaggio del display consiste nell’attivare le righe singolarmente ed in successione fornendo di volta in volta, per ogni riga attivata, tutti i 125 bit corrispondenti alle colonne: sulla base di questi bit saranno quindi attivati o disattivati i vari generatori di corrente di colonna. L’aggiornamento del display avviene a una frequenza di circa 56 Hz, al fine di permettere una visualizzazione stabile agli occhi dell’osservatore.

Vediamo di descrivere meglio i drivers di riga e di colonna.

I drivers di colonna devono essere in grado di fornire per ogni uscita la corrente necessaria ad alimentare un solo led (quindi qualche decina di milliampere), visto che non accade mai che risulti attiva più di una riga del display per volta. Si ritrovano inoltre ad operare in modo praticamente continuativo. Per come essi risultano strutturati infatti, possono ricevere i bit relativi alla riga successiva mentre stanno pilotando i led della riga corrente: in seguito ad alcune azioni compiute dal microcontrollore, viene attivata la riga successiva e si ha un cambio di stato dei bit relativi alle colonne. Accade quindi che i drivers di colonna risultano disattivi solo per alcuni cicli di clock.

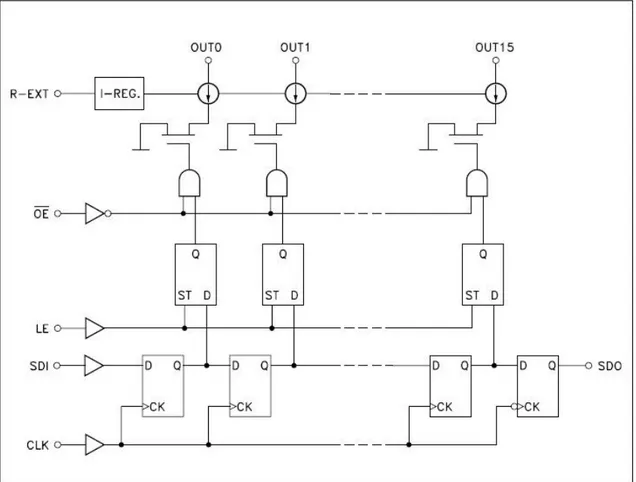

Il circuito integrato che è stato utilizzato come driver di colonna è l’STP16C596, della ST. Esso è un driver studiato appositamente per il pilotaggio di led; è costituito da 16 uscite a corrente costante con capacità di assorbire una corrente (regolabile) compresa tra 15 mA e 120 mA. È formato da uno shift register a 16 bit caratterizzato dall’avere ingresso seriale e uscita parallela. Le uscite dello shift register sono collegate agli ingressi di una barriera di latch attraverso i quali è possibile memorizzare (all’attivazione del segnale LE) lo stato dello shift register stesso. Lo stadio di uscita è formato da 16 generatori di corrente, capaci di assorbire da 15 mA a 120 mA, abilitati per mezzo del segnale /OE. Il valore della corrente per tutte le uscite di uno stesso driver, può essere impostato dall’esterno, attraverso l’impiego di una resistenza.

Figura 3 - Diagramma circuitale del circuito integrato STP16C596 (tratta dal datasheet del circuito integrato).

La figura 3 riportata in questa pagina mostra la struttura di questo circuito integrato (tratta dal datasheet del circuito integrato stesso).

Come è possibile notare dalla figura 3, il dispositivo riceve in ingresso i dati in forma seriale (attraverso il pin SDI), memorizzandoli nei flip flop di tipo D in corrispondenza di ogni fronte in salita del clock (CLK). Una volta che sono stati inviati tutti i bit attraverso il terminale SDI, è possibile memorizzarli nei latch attivando LE. Tutti i led collegati alle uscite risultano spenti finchè /OE si trova al livello alto: portandolo a livello logico basso vengono abilitate le uscite, comportando quindi l’attivazione dei generatori di corrente opportuni. È importante evidenziare che il sistema può acquisire i dati relativi alla riga successiva mentre sta pilotando i led della riga corrente. Questo è possibile per la presenza della barriera di latch i quali risultano insensibili ai loro ingressi finchè LE risulta disattivo. Il dispositivo consente la connessione in cascata, permettendo di lavorare correttamente fino alla frequenza di 25 MHz. Da notare che

l’ultimo flip flop campiona l’ingresso sul fronte in discesa del segnale di clock per consentire un corretto collegamento in cascata. Tutti i segnali necessari alla gestione dell’integrato (CLK, SDI, LE, /OE) provengono direttamente dal microcontrollore presente nel sistema. I segnali CLK, /OE, LE sono comuni a tutti i circuiti integrati di colonna, per cui, per la gestione di tutte le 125 colonne del display, sono sufficienti solamente 4 uscite del microcontrollore (ottenendo quindi un utilizzo molto contenuto delle sue linee di I/O). Stabilito il funzionamento del circuito integrato costituente il driver di colonna, possiamo procedere indicando l’organizzazione del driver di riga.

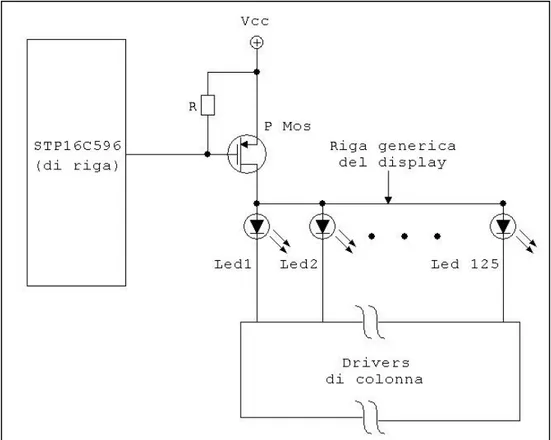

I drivers di riga devono poter fornire correnti molto più elevate rispetto ai drivers di colonna (fino a 5 Ampere) in quanto, nel peggiore dei casi, devono essere in grado di accendere tutti i 125 led di cui è costituita un’intera riga. A tale scopo è stato previsto l’utilizzo di mosfet a canale P con funzione di interruttore. Ogni volta che una riga viene attivata, il mosfet ad essa relativo si porta in conduzione, consentendo quindi alla riga stessa di raggiungere un livello prossimo alla tensione di alimentazione. A questo punto l’accensione o meno dei singoli led di quella riga è affidata esclusivamente alla condizione delle uscite dei drivers di colonna.

I mosfet utilizzati per alimentare le righe del display sono degli IRF7416, della International Rectifier. Sono mosfet a montaggio superficiale in package SO-8. Accettano una VDS massima pari a -30 V ed una corrente IDS continuativa fino a -10 A

(@VGS = -10 V, TA = +25 °C); inoltre possono dissipare fino a 2.5 W (@TA = +25 °C) e

hanno una tensione di soglia minima pari a -1 V. La resistenza RDS(on) è al massimo pari

a 0.020 Ω (@VGS = -10 V, IDS = -5.6 A). Nel dispositivo progettato, quando questi

mosfet vengono attivati, la tensione VGS risulta circa pari a -4.6 V. Valutando le caratteristiche di uscita dell’IRF7416, si evince una tensione VDS nello stato ON

inferiore a 0.2 V (per IDS = -5 A e TA = +25 °C). Questo significa, considerando il duty

cycle pari a 1/28, che ogni mosfet dissipa una potenza massima inferiore a 1 W e una potenza media pari a meno di 40 mW, quindi pienamente sopportabile. È da notare che i mosfet utilizzati sono piuttosto sovradimensionati per il contesto nel quale sono utilizzati: tuttavia, data l’esigua differenza di costo con modelli di caratteristiche inferiori e per consentire sviluppi futuri del prototipo (ad esempio un aumento della

corrente impostata nei drivers di colonna) si è ritenuto di utilizzare il modello sopraccitato.

Il pilotaggio dei gate dei mosfet di riga avviene grazie agli stessi circuiti integrati utilizzati per i drivers di colonna. Più precisamente, vengono adottati due STP16C596 connessi in cascata, le cui uscite sono collegate direttamente ai gate dei mosfet. Inoltre ogni uscita dei due drivers è anche connessa attraverso un pull-up resistivo alla tensione positiva di alimentazione.

Nei due drivers di riga, quando viene attivato il segnale /OE (comune ad entrambi), è un solo generatore per volta ad essere attivo, cioè quello corrispondente alla sola riga da accendere. L’unico generatore attivo provoca una caduta di tensione (in modulo superiore rispetto alla tensione di soglia del mosfet) sulla resistenza di pull-up che porta il mosfet in conduzione. In figura 4 è possibile vedere come avviene il pilotaggio di una riga generica del display.

È da notare che i drivers di riga e di colonna vengono pilotati attraverso segnali indipendenti, compreso il segnale di clock. Un’alternativa poteva consistere nel collegare in cascata, insieme ai drivers di colonna, anche i due drivers di riga: in tal modo si sarebbero utilizzate almeno due linee di I/O in meno (SDI e CLK). Tuttavia questa idea è stata abbandonata in quanto durante il caricamento dei dati di colonna si sarebbero dovuti caricare anche i 4 bytes relativi alle righe attraverso l’interfaccia SPI e questo avrebbe comportato un dispendio inutile delle risorse del microcontrollore. La tecnica che invece è stata adottata si basa su una considerazione: le righe devono essere accese in sequenza ed una per volta. Ciò che viene fatto viene descritto di seguito.

A livello hardware si collegano ad anello i due shift register contenuti negli STP16C596 e si connettono fra loro le coppie di pin /OE, LE e CLK; durante la fase di inizializzazione del sistema si provvede a caricare nei due driver di riga una sequenza di bit costituita da un solo livello logico 1 seguito da 31 livelli logici 0: per attivare la riga successiva è sufficiente fornire un solo impulso di clock in ingresso agli shift register (per spostarne il contenuto di una posizione) ed attivare i segnali LE e/OE. Si ottiene in questo modo un consistente risparmio di risorse adottando solamente 4 linee di I/O del microcontrollore aggiuntive.

Per quanto riguarda la frequenza di refresh del display, essa è facilmente impostabile a livello firmware. Attualmente l’ìntero display viene rinfrescato con una frequenza pari a circa 55.8 Hz. Siccome il display è costituito da 28 righe, significa che le righe commutano ad una frequenza pari a circa 1562.5 Hz.

4.2.3 Interfaccia tastiera

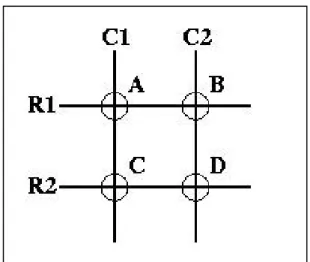

Così come per il modulo lcd della Matrix Orbital, nel pannello a led è previsto un connettore a 10 pin per la connessione di una tastiera a matrice con al più 25 tasti. In una tastiera di questo tipo, in seguito alla pressione di un tasto si crea una connessione elettrica tra la riga e la colonna corrispondenti al tasto premuto. Nella figura 4 viene indicata l’illustrazione di una tastiera con soli 4 tasti. Se ad esempio nella tastiera di figura viene premuto il tasto indicato con A, viene creata una connessione tra la riga R1 e la colonna C1.

Figura 5 - Esempio di connessione in una tastiera a matrice di 4 tasti.

È il sistema a cui è connessa la tastiera che deve individuare e riconoscere il tasto premuto.

Nel modulo lcd Matrix Orbital, in seguito alla pressione di un tasto si procede all’invio del codice ASCII relativo al carattere premuto, con diverse modalità a seconda delle disposizioni fornite dal controller esterno.

Nel caso del pannello a led è stato completamente predisposto a livello hardware l’uso dell’interfaccia tastiera, ma allo stato attuale del firmware non ne sono state implementate ancora le funzioni: esse tuttavia potranno essere realizzate per uno sviluppo futuro ed utilizzate semplicemente aggiornando la versione del firmware.

Un microcontrollore, per rilevare la pressione di un tasto, può operare principalmente secondo due modalità:

• Effettuare una continua scansione della matrice. Questa metodologia può essere utilizzata qualora tale operazione non vada a compromettere le altre funzionalità del microcontrollore: infatti il grosso difetto di questa tecnica è che il microcontrollore risulta impegnato nella scansione della tastiera anche se non è stato premuto alcun tasto.

• Utilizzare un sistema che, a seguito della pressione di un tasto, generi una richiesta di interruzione al microcontrollore. È sicuramente il metodo più efficiente,

in quanto impegna il microcontrollore solamente se è stato effettivamente premuto un tasto.

Nel prototipo realizzato, l’hardware è stato predisposto per generare una richiesta di interruzione al microcontrollore: questo permette così di gestire la tastiera sfruttando al minimo le risorse disponibili.

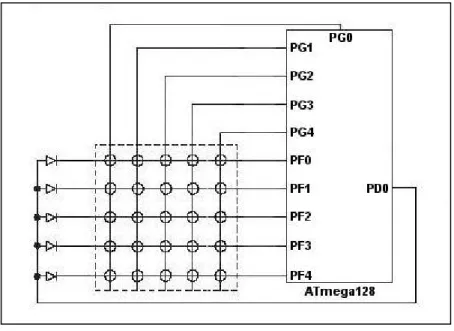

A questo punto passiamo a descrivere in che modo è stata realizzata a livello hardware l’interfaccia tastiera. In figura 6 ne viene riportato lo schema circuitale.

Figura 6 - Schema circuitale adottato per l’interfaccia tastiera.

Come è possibile notare dalla figura, le linee relative alle righe e alle colonne della tastiera sono direttamente connesse al microcontrollore. In particolare le righe sono state collegate alla porta F, mentre le colonne alla porta G. Il principio di funzionamento è il seguente: a livello firmware vengono settate come uscite, e portate a livello logico 0, le linee relative alle colonne, mentre quelle relative alle righe vengono impostate come ingressi con i pull-up attivati. Ogni riga della matrice è anche connessa a un diodo di segnale 1N4148, con il catodo rivolto verso la porta F e l’anodo in comune con tutti gli altri diodi delle restanti righe. Questo terminale a comune viene a sua volta connesso alla linea PD0 del microcontrollore, che viene impostata come ingresso con pull-up attivo.

Quando nessun tasto viene premuto i diodi non sono in conduzione, risultando i loro terminali tutti a livello logico alto. Nel momento in cui viene premuto un tasto qualsiasi, il diodo corrispondente alla riga del tasto premuto si porta in conduzione, forzando a livello basso il terminale PD0. Quest’ultimo ha la caratteristica (ma non è il solo) di poter essere impostato per ricevere richieste di interruzione dall’esterno del microcontrollore. Una volta che questo pin si trova a livello logico basso viene avviata l’esecuzione della routine di servizio. Essa a questo punto può effettuare una scansione delle linee per determinare il tasto premuto ed inviare il codice ASCII corrispondente per mezzo dell’interfaccia seriale.

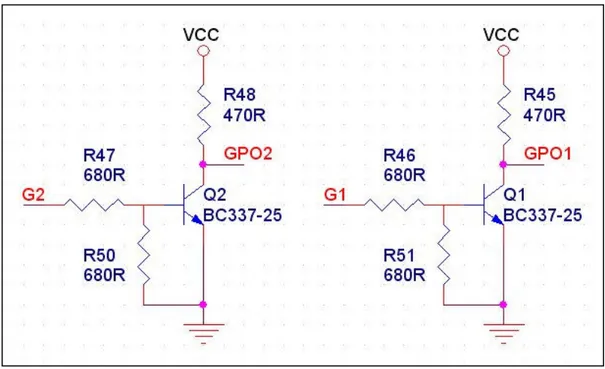

4.2.4 Uscite general purpose

Il modulo GLK12232-25SM prevede due uscite general purpose (G1 e G2), con le quali l’utente può pilotare dispositivi di vario genere. Esse differiscono leggermente nelle specifiche:

• G1 è un’uscita che si porta a livello basso quando abilitata; quando non lo è si trova a 5 V grazie ad un pull-up costituito da una resistenza da 150 kΩ. La corrente massima che può essere assorbita è di 250 mA.

• G2 si trova a livello logico basso quando è attiva, ma oltre a capacità di sink ha anche capacità di source. Anche in questo caso la corrente massima è di 250 mA. Nel pannello a led sono stati riservati due pin del microcontrollore allo scopo di costituire le due uscite general purpose. Tuttavia, visto che non è stato posto particolare interesse per questa caratteristica del modulo lcd, per semplicità entrambe le uscite sono state realizzate allo stesso modo, ovvero con capacità di assorbire una corrente massima (in realtà superiore) a 250 mA.

In condizioni di carico collegato sulle uscite, quando queste sono disattivate, è possibile prelevare una corrente di pochi milliampere, con un ovvio degrado del livello logico 1. La corrente massima di source in condizioni di cortocircuito verso massa delle

uscite e con i bjt interdetti è pari a circa 10 mA. In figura 7 viene rappresentato lo schema circuitale relativo alle uscite general purpose.

Figura 7 - Implementazione delle uscite general purpose nel pannello a led.

Lo schema circuitale utilizza due inverter a bjt; quando ad esempio l’uscita del microcontrollore G1 (G2) è attiva, il valore delle resistenze collegate alla base del transistor Q1 (Q2) gli consentono di raggiungere la saturazione, portando a livello basso l’uscita GPO1 (GPO2). L’inverter funziona correttamente anche senza il resistore R51 (R50). Tuttavia la sua presenza permette al bjt di uscire più velocemente dalla saturazione nel momento in cui l’uscita del microcontrollore commuta dal livello alto al livello basso.

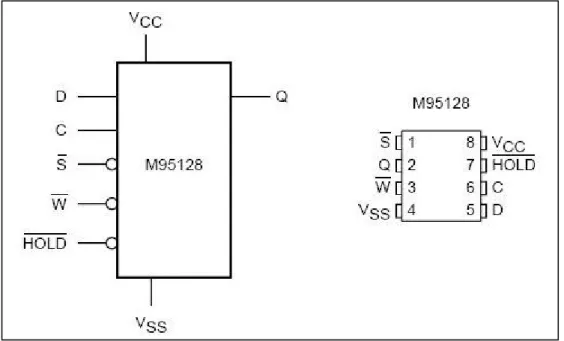

4.2.5 Memoria EEPROM esterna

La memoria EEPROM che è stata utilizzata nel pannello a led ha lo scopo di salvare fonts e bitmaps al suo interno al fine di una loro utilizzazione anche a seguito dello spegnimento del sistema. La memoria utilizzata è una M95128-WMN6, della Sgs-Thomson. Essa ha una capacita di 128 Kb, organizzati secondo 16384 locazioni da 8 bit ciascuna. Per la comunicazione utilizza un’interfaccia SPI compatibile e riesce a

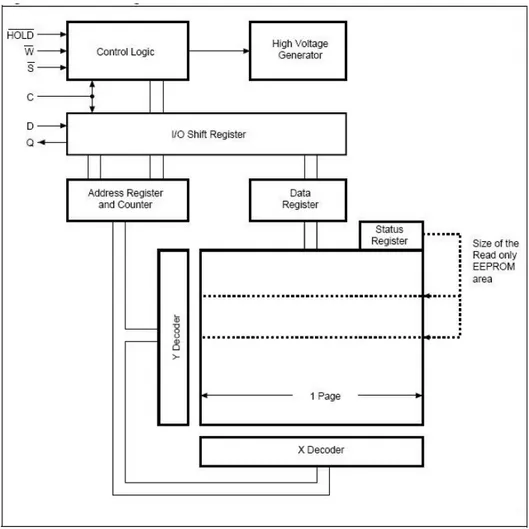

lavorare correttamente fino ad una frequenza di 10 MHz. Il range di alimentazione può variare da un minimo di 2.5 V fino ad un massimo di 5.5 V. Ha una data retention superiore a 40 anni e consente più di 100000 cicli di scrittura. Essa permette di effettuare scritture e letture di un singolo byte oppure è possibile scrivere fino a 64 bytes in un unico ciclo di scrittura; per la lettura invece non vi sono limitazioni nel numero di bytes da leggere: se viene raggiunta l’ultima locazione, il contatore interno di lettura riparte dall’inizio della memoria. A questo punto passiamo a descrivere con maggiore attenzione la struttura della memoria. La figura 81 mostra il diagramma logico e la disposizione dei pin del package del circuito integrato M95128.

Figura 8 - Diagramma logico e disposizione dei pin nella memoria M95128-WM6.

I pin D, Q, C, e /S fanno parte dell’interfaccia di comunicazione e rappresentano rispettivamente l’ingresso seriale dei dati, l’uscita seriale dei dati, il clock e il chip select; quando /S risulta disattivo la memoria è inattiva e l’uscita Q si trova in alta impedenza. VCC e VSS costituiscono i pin di alimentazione. Il segnale /HOLD ha lo scopo, quando diviene attivo, di mettere in pausa il trasferimento di dati in corso senza

1

dover riportare a livello alto il chip select. In queste condizioni il dispositivo è insensibile ai segnali D e C, e inoltre porta in alta impedenza l’uscita Q. L’ultimo pin disponibile (/W) ha lo scopo di permettere che una parte dell’area di memoria (la cui dimensione può essere impostata per mezzo dei bit BP1 e BP0 dello Status Register) possa essere protetta da comandi di scrittura.

Nella figura riportata di seguito 2 (figura 9) viene mostrato il diagramma funzionale della memoria.

Figura 9 – Diagramma a blocchi della memoria M95128-WM6.

2

Vediamo di descrivere brevemente come viene utilizzata la memoria nel prototipo realizzato. La protezione (hardware e software) in scrittura non è stata utilizzata, di conseguenza a tutta l’area di memoria è sempre concessa l’operazione di scrittura. Questo si traduce nel fissare a VCC il pin /W. Il chip select (/S) è collegato al pin /SS del microcontrollore, mentre per D,C e Q si sono utilizzati i pin appositi disponibili nel microcontrollore, cioè MOSI (PB2), SCK (PB1) e MISO (PB3). Il pin /HOLD è stato connesso invece al pin PB4.

Prima di eseguire qualsiasi operazione il dispositivo master (nel nostro caso il microcontrollore) deve selezionare la memoria, ponendo a livello logico basso il pin /S. A questo punto il dispositivo master invia, in corrispondenza del segnale di clock generato da quest’ultimo, un comando relativo all’operazione da eseguire. Il comando è costituito da un byte che lo identifica univocamente, seguito da eventuali dati.

La memoria è stata dotata di un registro di stato, attraverso il quale è possibile valutare se un’operazione di scrittura è terminata o meno, impostare la dimensione dell’area di memoria che deve essere eventualmente protetta, ed altro.

I comandi che costituiscono il set di istruzioni della memoria sono i seguenti (si ricorda che prima di inviare ciascuno di essi è necessario selezionare il dispositivo):

• WREN (WRite ENable): deve essere inviato alla memoria prima di ogni istruzione WRSR e WRITE; costituisce una protezione contro scritture accidentali. • WRDI (WRite DIsable): permette di disabilitare le operazioni di scrittura della memoria; questa istruzione viene anche eseguita automaticamente dalla memoria stessa dopo ogni operazione di scrittura (WREN, WRSR e WRITE).

• RDSR (ReaD Status Register): permette la lettura dello status register; questa operazione può essere eseguita in qualsiasi momento (anche quando è in corso un’operazione di tipo WRITE e WRSR) e permette di ricavare informazioni utili circa lo stato del dispositivo. La lettura dello status register, in particolare del bit WIP (Write In Progress) deve essere sempre fatta prima di inviare una nuova istruzione alla memoria, al fine di valutare se il dispositivo è pronto a ricevere un nuovo comando.

• READ (READ from memory array): consente di effettuare l’operazione di lettura dalla memoria; dopo il comando di lettura deve seguire l’indirizzo della locazione di memoria da leggere: se dopo la trasmissione del primo byte il dispositivo è ancora selezionato, la memoria trasmette anche il contenuto delle locazioni successive fino a che non viene riportato a livello alto il chip select. L’incremento dell’indirizzo viene eseguito automaticamente grazie all’utilizzo di un contatore interno alla memoria. • WRITE (WRITE to memory array): questa istruzione, così come accade anche per WRSR, deve essere sempre preceduta dal comando WREN. Dopo l’istruzione WRITE il dispositivo master fornisce anche l’indirizzo della locazione da scrivere seguito dal byte da salvare. Se una volta terminato l’invio del dato da salvare viene riportato il chip select a livello alto, il dispositivo assume che l’operazione di scrittura ha coinvolto un solo byte. Se invece il chip select viene mantenuto a livello basso esso attende in sequenza i bytes successivi fino ad arrivare alla fine della pagina a cui tali dati appartengono.

4.2.6 Il microcontrollore

Il microcontrollore costituisce il cuore di tutto il sistema: infatti ad esso è affidato il compito di svolgere tutte le operazioni necessarie al corretto funzionamento dell’unità. Tra i vari produttori di microcontrollori esistenti sul mercato, si è posta particolare attenzione alla famiglia Atmel AVR. Questa scelta è stata dovuta principalmente a motivi pratici, in quanto per tali dispositivi si dispone di tutti gli elementi necessari per la programmazione ed il debug.

A questo punto la scelta del microcontrollore è derivata da alcune considerazioni circa le funzionalità che esso è tenuto a svolgere per l’intero funzionamento del prototipo. Nel seguito vengono riportate le operazioni che devono essere eseguite dal nostro dispositivo e che hanno contribuito alla scelta del microcontrollore:

• Gestire la comunicazione con il controller esterno: questo significa che il microcontrollore deve poter colloquiare con il mondo esterno per mezzo di un protocollo seriale asincrono. Per tale motivo è stata posta maggiore attenzione ai

dispositivi che presentavano almeno una UART, così da minimizzare le operazioni svolte dal firmware per la gestione dell’interfaccia seriale.

• Pilotare opportunamente i drivers di riga e di colonna, nonchè leggere e scrivere nella memoria esterna: a questo scopo risulta molto vantaggioso che il microcontrollore abbia già l’hardware predisposto per la gestione dell’interfaccia SPI.

• Ricevere i dati da tastiera: a tale scopo era richiesto un dispositivo che avesse un numero sufficiente di linee di I/O, visto che per la sola interfaccia tastiera sono necessarie ben 11 linee; inoltre sarebbe stato vantaggioso che disponesse di terminali capaci di accettare richieste di interruzione esterne.

• Elaborare i comandi ricevuti attraverso l’interfaccia seriale: gran parte delle potenzialità del microcontrollore vengono impegnate per questo scopo e quindi si è reso necessario l’impiego di un microcontrollore che avesse un‘architettura avanzata. Oltre a queste considerazioni, anche altri aspetti hanno condizionato la scelta del microcontrollore candidato ad assolvere i compiti per il prototipo . Nel seguito ne vengono riportati i più importanti:

• Frequenza massima di lavoro: è un parametro molto importante, perchè permette di stabilire il tempo di esecuzione delle istruzioni. Tipicamente gli Atmel AVR hanno una frequenza massima pari a 20 MHz.

• Quantità di memoria SRAM: è un parametro fondamentale in quanto una parte di questa memoria viene utilizzata come una sorta di “memoria video”. In particolare almeno 448 bytes di SRAM sono destinati a tale utilizzo e a questo spazio deve essere aggiunta la parte destinata all’allocazione delle variabili del firmware.

• Memoria di programma: è la memoria (di tipo flash) destinata a contenere il firmware del microcontrollore. Per questo parametro sono richiesti almeno 8 kB di memoria flash.

• Memoria EEPROM: viene utilizzata per la memorizzazione permanente di alcune informazioni relative a fonts e bitmaps. Nessuno dei microcontrollori presi in esame aveva una memoria EEPROM sufficiente a memorizzare la stessa quantità di fonts e bitmap del display Matrix Orbital.

• Presenza di almeno un timer: l’uso di un timer è necessario per l’operazione di rinfresco del display al fine di generare una richiesta di interruzione con una specifica cadenza. Questo dispositivo è praticamente presente (anche in numero superiore a uno) in tutti i microcontrollori Atmel AVR.

• Costo: anche questo è un parametro che è stato preso in considerazione per la scelta del microcontrollore. Tuttavia le differenze di costo tra i dispositivi che presentavano le caratteristiche desiderate erano molto contenuti, soprattutto in relazione al costo totale del pannello led: di conseguenza questo aspetto è diventato meno rilevante rispetto ad altri.

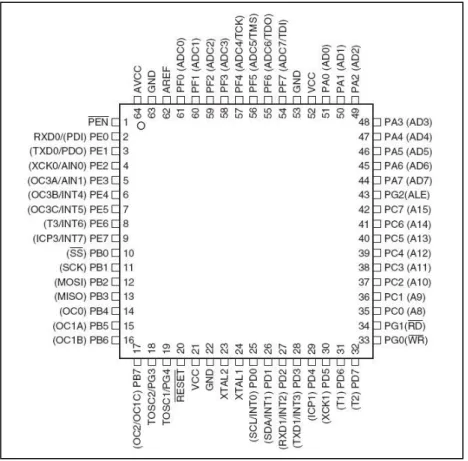

Sulla base di tutte le considerazioni fatte, si è optato per la scelta di un ATmega128-16. Nella figura 10 ne viene proposta la piedinatura 3.

Figura 10 – Piedinatura del microcontrollore ATmega128.

3

L’ATmega128 è un microcontrollore CMOS a 8 bit a bassa potenza, basato su un’architetettura RISC avanzata. È dotato di ben 133 istruzioni, la maggior parte delle quali vengono eseguite in un solo ciclo di clock. Può operare alla frequenza massima di 16 MHz e ha al suo interno 32 registri connessi direttamente alla ALU (Arithmetic Logic Unit). Ha 128 kB di memoria flash di programma, 4 kB di EEPROM, 4 kB di memoria SRAM, 53 linee di I/O general purpose, un real time counter (RTC), 4 Timer/Counters con modalità “compare match” e “PWM”, 2 USART, un’interfaccia TWI, un convertitore A/D 10 bit ad 8 canali, un watchdog timer con oscillatore interno, un’interfaccia SPI con possibilità di operare in diverse modalità, e un’interfaccia JTAG per il debug e la programmazione. Inoltre ha 6 modalità di power-saving.

L’ATmega128 può essere programmato in diversi modi: è possibile effettuare il download del firmware in maniera seriale (per mezzo dell’interfcacia SPI, cioè come avviene nel prototipo realizzato, o JTAG) o parallela. Inoltre è possibile effettuare il download del firmware nella memoria flash di programma, utilizzando un programma di boot: quest’ultimo può utilizzare una qualsiasi interfaccia per scaricare il firmware nella memoria flash; inoltre l’aggiornamento della memoria flash di programma viene fatto mentre è in esecuzione il programma di boot. Questa particolarità viene definita “read while write”, ovvero lettura (esecuzione del programma di boot in una parte della memoria flash) mentre è in corso la scrittura. Quando viene utilizzato il bootloader, la memoria flash viene suddivisa in due parti: la “application section” e la “bootloader section”. La prima sezione contiene il firmware dell’applicazione, mentre la seconda il bootloader. Mentre il programma che risiede nella application section non può memorizzare del codice nella sezione del bootloader, quest’ultimo può farlo in entrambe le sezioni.

Nel capitolo successivo verrà descritto il firmware che è stato realizzato per il microcontrollore, e saranno analizzate in dettaglio le varie parti di quest’ultimo che sono state utilizzate nel progetto del display. In particolare verrà illustrato il funzionamento dell’interfaccia SPI, del timer usato per il refresh del display, e della USART.

4.2.7 Alimentatore

Il prototipo realizzato dispone di un alimentatore che permette di fornire a tutto il sistema la tensione fissa di 5 V. Per scelta progettuale, non è stato incluso nel lavoro di tesi l’intera progettazione del sistema di alimentazione, ma si è cercato di utilizzare una soluzione realizzata almeno in parte.

Come è stato detto in questo capitolo, le righe del display vengono attivate una alla volta e il caso peggiore che si può presentare in termini di corrente di picco assorbita dal display led è quella in cui almeno una riga abbia tutti i 125 led accesi. In questo caso, siccome la corrente impostata nei driver di colonna è pari a circa 40 mA per ogni uscita, si ottiene una corrente totale assorbita pari a circa 5 A. Tenendo presente che il consumo a display completamente spento si aggira intorno ai 100 mA e supponendo di prelevare la massima corrente dalle due uscite general purpose, si otterrebbe un consumo di corrente massimo totale intorno ai 5.6 A.

Questo significa che l’alimentatore del prototipo deve riuscire a fornire, senza subire danni, una corrente di poco inferiore a 6 A. Tuttavia, visto che il dispositivo progettato si tratta di un prototipo, si è pensato di utilizzare un alimentatore sovradimensionato, in modo tale da poterlo utilizzare anche in futuro a seguito di un aumento delle correnti in uscita impostate nei drivers di colonna.

Avendo a disposizione un certo numero di alimentatori per pc portatili inutilizzati, è stato pensato di sfruttare uno di essi per alimentare il prototipo. Tuttavia si presentava il problema di dover adattare la tensione di uscita di questi alimentatori, che solitamente è sempre superiore a 15 V, alla tensione di 5 V mantenendo un buon livello di efficienza.

Il problema è stato risolto adottando lo schema elettrico, corredato dal relativo layout del pcb, fornito dall’application note 1882 della Maxim dal titolo “Increase the power of a buck (step down) switching power supply”. In essa viene trattato un alimentatore switching dalle dimensioni molto contenute e dalla potenza di ben 100 W con una tensione di 5 V, che utilizza il circuito integrato MAX1653 della stessa Maxim. Si tratta di un controller PWM di tipo step-down ad alta efficienza disponibile nel package QSOP a montaggio superficiale. Può raggiungere un livello di efficienza fino al 96%, ed è pin compatibile con il suo più noto predecessore, il MAX797. Accetta una tensione in ingresso fino a 30 V e può lavorare ad una frequenza fissa (150 kHz o 300 kHz) o

sincronizzata con un segnale esterno (da 190 kHz fino a 340 kHz). Inoltre ha un circuito di soft start, ed è dotato di una protezione contro una corrente eccessiva in uscita: infatti la protezione viene innescata quando ai capi di un sense resistor posto tra due dei suoi terminali (CSH e CSL), è presente una caduta di tensione pari a 100 mV. In tal modo è possibile, utilizzando un resistore di valore opportuno, impostare la soglia di intervento della protezione al valore desiderato.

Il circuito proposto dalla Maxim utilizza dei condensatori ceramici in ingresso e degli elettrolitici a bassissimo ESR sull’uscita per mantenere l’efficienza su valori elevati. Inoltre vengono utilizzati 4 mosfet della International Rectifier a montaggio superficiale dalle dimensioni estremamente contenute (package SO-8): due di essi sono degli IRF7811W (che sopportano una corrente massima di 14 A per VGS = 4.5 V,

TA = +25 °C), mentre gli altri due sono degli IRF7822 (che accettano una corrente

massima di ben 18 A per VGS = 4.5 V, TA = +25 °C). Entrambe queste coppie di mosfet

vengono connessi in parallelo.

In figura 11 si riporta lo schema circuitale relativo all’alimentatore proposto nell’application note della Maxim.

L’unico parametro che è stato calcolato per questo alimentatore è il valore del sense resistor, che è stato determinato per ottenere una limitazione della corrente al valore di circa 6 A.

Dopo aver fornito una breve descrizione dell’alimentatore, nel paragrafo successivo saranno descritte in modo sommario le fasi relative alla realizzazione pratica dell’intero prototipo.

4.3 Cenni alla realizzazione pratica del prototipo

Una volta conclusa la fase relativa allo studio dell’hardware dell’intero sistema, è seguita la fase di progettazione del layout dei circuiti stampati e la realizzazione pratica degli stessi.

È stata adottata una struttura modulare per l’intero sistema: questo significa che le varie parti dell’hardware sono state realizzate su circuiti stampati differenti e connesse tra loro in fase di montaggio. Questo ha consentito di testare separatamente le varie parti del sistema, anche se la fase relativa al montaggio è stata più complessa.

Prima di procedere con la progettazione del layout è stato realizzato lo schema circuitale dell’intero sistema grazie all’ausilio del software Orcad Capture, della Cadence Design Systems inc. Una volta terminata questa fase è stato realizzato il layout con l’uso di Orcad Layout, appartenente allo stesso pacchetto software.

La realizzazione del layout è stato un processo laborioso, a causa del fatto che non è stato possibile realizzare dei circuiti stampati a singola faccia; inoltre sono stati necessari un grande numero di fori di via disposti per la maggioranza in modo manuale.

Per quanto riguarda invece la realizzazione pratica dei circuiti stampati, è stata utilizzata una fresa a controllo numerico disponibile nell’officina del Dipartimento di Ingegneria dell’Informazione. Sono stati impiegati alcuni giorni per la realizzazione dei circuiti stampati, in quanto il tempo di lavorazione è stato piuttosto lungo. Inoltre è da tenere in considerazione che si è presentato il problema dell’allineamento dei due layer di ogni pcb, con un conseguente aumento del tempo impiegato.

Terminata la fase di realizzazione dei circuiti stampati si è passati al montaggio di tutti i componenti e all’assembleggio dell’intero sistema.

Nelle figure seguenti vengono riportati i circuiti realizzati in seguito alla fase di montaggio.

La figura 12 mostra il display LED, mentre nella figura 13 viene mostrata la scheda di controllo lato componenti, dove risiedono il microcontrollore, i drivers di riga (i due STP16C596 e i mos di potenza), e il line driver/receiver.

In figura 14 si riporta sempre la scheda di controllo ma dal lato saldature. In essa è presente il connettore a 10 pin per l’interfaccia tastiera, il connettore a 4 pin relativo alle due uscite general purpose e infine il connettore ISP (In System Programming) per l’aggiornamento del firmware del microcontrollore. È inoltre possibile notare la porta di comunicazione dell’interfaccia seriale.

In figura 15 viene mostrata la scheda relativa ai drivers di riga (costituita da 8 STP16C596), mentre nella figura 16 è illustrato il circuito stampato lato componenti dell’alimentatore.

Figura 13 – Scheda di controllo lato componenti.

Figura 15 – Drivers di colonna del prototipo.

4.4 Test effettuati per la verifica dell’hardware

Una volta terminato l’assemblaggio del sistema, è seguita la fase di verifica delle funzionalità di tutti i circuiti prodotti.

Prima di tutto sono state verificate le connessioni dei vari circuiti stampati e fatte le dovute correzioni. Dopodiché per testare il sistema sono stati realizzati (e caricati nel microcontrollore) semplici firmware di test ognuno dedicato ad una specifica funzionalità; in particolare ne è stato realizzato uno per eseguire l’operazione di rinfresco del display (quindi è stato verificato il funzionamento dei drivers di riga e di colonna, il display LED, e il corretto svolgimento delle operazioni a carico della routine di interruzione 4), ed un altro per testare il trasferimento dati attraverso l’interfaccia seriale (a tale scopo è stato utilizzato il software Hyper Terminal con il quale è stato possibile inviare dei caratteri al prototipo e valutare la correttezza della risposta ricevuta da quest’ultimo. In particolare il firmware di test inviava un carattere al prototipo e quest’ultimo ne doveva restituire l’echo).

Dalle prove effettuate l’hardware si è dimostrato funzionante.

4