Capitolo 2

Struttura e funzionamento del circuito integrato di Interfaccia

Messa a punto della basetta di Test

2.1 Introduzione

In questo capitolo saranno presentate le idee che hanno portato alla realizzazione dell’interfaccia; in modo specifico si partirà dalle specifiche dell’integrato e successivamente si discuteranno alcuni circuiti, tra cui quello base su cui si sviluppa l’intera idea e cioè il convertitore capacità-frequenza, insieme al circuito integratore. Successivamente si discuterà di come l’interfaccia possa generare un segnale modulato PWM, ricordando quali problemi si potrebbero incontrare, e quali i possibili vantaggi. Nella parte finale del capitolo si discuterà di come, il circuito realizzato dalla STMicroelectronics, sarà montato su una basetta per effettuare i relativi test di caratterizzazione.

2.2 Specifiche dell’interfaccia

In questo paragrafo vogliamo definire quali siano le specifiche dell’interfaccia:

• Frequenza di clock dell’interfaccia f = 50kHz con valore massimo Vpp di 3.3V;

Uscita in PWM;

• Possibilità d’interfacciamento con microcontrollore; • Sensore di temperatura incorporato;

• Calibrazione programmabile delle correnti;

• Simulazione del sensore di pressione attraverso un condensatore programmabile a tre bit con intervallo di variazione da 800 fF a 1200 fF;

• Possibilità di disattivare i condensatori interni (condensatore simulato) ed effettuare la misura su un condensatore esterno (Cext)

Il circuito prevede inoltre l’insensibilità dell’uscita al rumore e alle variazioni di temperatura in un ampio range di variazione di temperatura, in oltre, variazioni dell’alimentazione non dovrebbero modificare il corretto funzionamento entro ampi limiti. Per il momento non andiamo oltre anche perché le misure per verificare le specifiche previste, saranno oggetto del prossimo capitolo.

2.3 Convertitore Corrente-Frequenza

Nel precedente capitolo abbiamo accennato al principio di funzionamento su cui si basa l’interfaccia, in particolare, la soluzione adottata è quella che utilizza un convertitore

capacità-frequenza che genera un segnale PWM (Pulse Width Modulation) con una

relazione lineare tra la durata dell’impulso e la capacità del sensore di pressione.

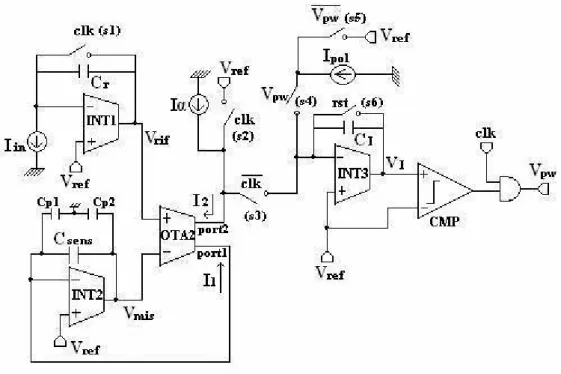

La figura 2.1 mostra, un convertitore capacità-frequenza (rif. [1]); le relazioni che regolano il funzionamento del circuito ci fanno intuire l’importanza dell’utilizzo di questa particolare soluzione.

Infatti, il legame che lega il periodo della tensione d’uscita, alla capacità di misura è lineare e dipendente solamente da grandezze che possono essere controllate in fase di calibrazione del circuito.

fig. 2.1 Convertitore Capacità-Frequenza

Vediamo brevemente qual è il principio di funzionamento del convertitore.

La corrente del generatore I entra sul drain del transistore M1 e viene specchiata su M2 ed M3; gli interruttori S1 ed S2 vengono aperti alternativamente in un periodo in modo che la corrente I venga specchiata una volta da M4 e una volta da M5.

Se si considera, ad esempio, come situazione iniziale quella in cui S2 sia aperto ed S1 sia chiuso la corrente I andrà a caricare il condensatore C aumentando la tensione ai suoi capi in maniera lineare, infatti, si ha una carica a corrente costante. Ricordiamo che con C si è indicata la capacità del sensore.

Per le ipotesi fatte sugli interruttori (S2 aperto, S1 chiuso), il trigger ha in uscita una tensione bassa e commuterà nel momento in cui la sua tensione di ingresso, che equivale alla tensione ai capi del condensatore, avrà raggiunto la tensione di soglia alta (Vih ), in

questo istante la commutazione del trigger provocherà l’apertura di S1 e la chiusura di S2 con conseguente scarica della tensione ai capi di C sempre in maniera lineare.

La tensione ai capi di C, raggiungerà la soglia bassa (Vil) e si avrà una nuova

commutazione con la conseguente ripartenza del ciclo di carica e scarica di C.

Ora che abbiamo visto il principio di funzionamento andiamo a ricavare la relazione che intercorre tra C e Vout; nella prima fase, quando S2 è aperto e S1 è chiuso, I carica il

condensatore secondo la legge:

V

c= I

●t + V

il(2.1)

C

Nella relazione 2.1 oltre al termine di carica lineare è presente il termine Vil che è

necessariamente la tensione iniziale del condensatore e vale a dire quella che permette al trigger di commutare.

In queste condizioni il condensatore continua a caricarsi fino a quando non si raggiunge la tensione di soglia alta del trigger, Vih, che a questo punto commuta portando la sua uscita

bassa ma la Vout alta; si può calcolare il periodo in cui l’uscita è bassa e cioè:

T

low= ( V

ih-V

il)

•C

(2.2)

I

Una volta che si è raggiunta la soglia, inizia la scarica di C, e il circuito tende a riportarsi nelle condizioni iniziali; è facile calcolare il periodo totale in cui viene compiuto un ciclo e questo sarà pari a due volte Tlow, in quanto la corrente è sempre I sia nella carica che nella

scarica di C.

In definitiva tenendo conto anche della capacità parassita (Cp) il periodo totale risulta:

T

tot= 2 · (V

ih-V

il)· (C + C

p) (2.3

)

I

Dalla 2.3 si evince che il periodo d’oscillazione ha un valore molto preciso ed in particolare può essere regolato facilmente variando il valore della corrente I, inoltre i parametri che compaiono nella 2.3 possono essere realizzati con buona precisione; in pratica la corrente I può essere regolata in fase di calibrazione e le soglie del trigger

possono essere rese sufficientemente costanti in modo che non si alteri il valore di Ttot.

Tuttavia questo è vero solo per ridotti intervalli di temperatura.

Inoltre abbiamo una dipendenza di tutto il periodo del segnale dal condensatore C, e non solo la durata dell’impulso come richiesto per la PWM.

Infine il sistema non è immune alle capacità parassite.

2.4 Struttura dell’ Interfaccia – “Integratore e schema

differenziale

In questo paragrafo vedremo come parte dei problemi del convertitore capacità-frequenza sono stati superati nel chip oggetto dei test di questa tesi.

L’interfaccia utilizza uno schema ad integratore che permette di attenuare gli effetti dovuti alle capacità parassite del sensore, lo schema è quello di figura 2.2

fig. 2.2 Circuito Integratore

In questa configurazione il sistema risente meno degli effetti parassiti, infatti, Cp2 viene a

trovarsi sull’uscita dell’operazionale e quindi ha una tensione imposta, anche se in realtà la resistenza d’uscita non è nulla; Cp1 invece viene a trovarsi tra gli ingressi dell’operazionale

che si trovano allo stesso potenziale e quindi, non influenza il circuito integratore che vede soltanto la capacità del sensore Csens.

Il solo circuito integratore non consente però di legare il valore della capacità al segnale PWM con duty cycle proporzionale alla capacità del sensore che si vuole generare, abbiamo bisogno di aggiungere alcuni blocchi che ci permettono di effettuare quest’operazione.

Il circuito definitivo che viene utilizzato dall’interfaccia ha lo scopo di eliminare la dipendenza della durata del segnale dalla temperatura, di cui risente il generatore I, e dalla parte di offset tipico dei sensori capacitivi.

La figura 2.3 mostra il circuito definitivo:

fig. 2.3 Sistema Master-Slave

Cerchiamo di capire come funziona il seguente circuito: l’integratore INT1 (MASTER), permette la carica del condensatore Cr tramite la corrente costante Iin, questo avviene

durante il segnale basso di clock; a questo punto l’OTA2 (amplificatore transconduttivo a larga dinamica di modo comune con uscita sdoppiata) si sbilancia facendo aumentare la corrente I1 che va a caricare il condensatore Csens dell’integratore INT2 (SLAVE).

Istante per istante la tensione Vmis insegue la tensione Vrif e quindi alla fine del semiperiodo

di clock, la tensione in uscita all’INT2 (SLAVE) sarà aumentata dello stesso valore di Vrif, cioè coprono lo stesso ΔV di variazione. A questo punto poiché risulterà I2=I1, la corrente I2 trasporterà l’informazione relativa alla capacità del sensore (vedi formula 2.26); il dettaglio di questa situazione verrà analizzato nel paragrafo successivo.

2.3 Principio di funzionamento e temporizzazione

dell’interfaccia

Fino ad ora abbiamo analizzato separatamente, i vari blocchi che costituiscono l’interfaccia,

una rappresentazione schematica dei blocchi che la costituiscono, è mostrata in figura 2.7.

fig. 2.7 Schema a blocchi dell’ Interfaccia

I blocchi contrassegnati con INT1 ed INT2, sono gli amplificatori operazionali di cui avevamo discusso nel paragrafo 2.3.

Il blocco INT1 (INT2), è un elemento fondamentale del sistema, infatti, deve avere un’amplificazione tale da garantire il cortocircuito virtuale ed avere un’alta impedenza d’ingresso che permetta di non caricare gli eventuali stadi a monte.

L’amplificatore operazionale utilizzato in questo circuito integrato, è un OTA (Operational

Transconductance Amplifier) a larga dinamica, in modo da aumentare la dinamica di modo

comune.

Il blocco contrassegnato con il simbolo OTA2, è un amplificatore derivato sempre da un OTA a larga dinamica, e serve a garantire una buona precisione sulla misura e soprattutto deve essere poco rumoroso.

Abbiamo accennato che OTA2 è un amplificatore transconduttivo modificato, infatti, è costituito da uno stadio d’ingresso a larga dinamica come INT1, e da uno stadio d’uscita con due porte identiche di cui una chiusa in reazione con l’amplificatore INT2. (fig. 2.7) Il blocco contrassegnato con il simbolo INT3 è un integratore di Miller (come INT1 e INT2), mentre CMP è un comparatore rigenerativo.

Il circuito è inoltre dotato di un segnale di reset che pilota INT3 (carica, scarica di CI) e

disabilita il normale funzionamento del circuito.

Le correnti Iα, Iin e Ipol, sono ottenute da un circuito che genera i riferimenti di corrente.

Sono realizzate con specchi di corrente di precisione e cosa più importante, sono molto stabili con la temperatura, cosa che sarebbe dannosa per il circuito stesso di interfaccia perché se i riferimenti non fossero stabili, varierebbero le soglie di scatto dei comparatori con isteresi che sono all’interno del sistema di misura.

Le correnti Iα e Ipol sono regolate dalle seguenti relazioni:

I

α= k

1· I

ine

I

in= k

2· I

pol(2.9)

Vediamo più in dettaglio il funzionamento dell’interfaccia:

Supponiamo che all’istante t=0 il reset (rst=0, pass gate s6 aperta) sia disabilitato, perciò il circuito può funzionare correttamente.

Il segnale di clock (clk) che ricordiamo è un’onda quadra con duty cycle pari al 50%, comanda le pass gate S1,S2 ed S3, quindi poiché il segnale di clock è basso gli switch S1 ed S2 sono aperti ed S3 è chiuso.

In questa situazione il condensatore di riferimento Cr comincia a caricarsi con corrente

costante Iin .

La carica accumulata dal condensatore nell’intervallo temporale [0-Tck/2] risulta:

Q

r= I

in· T

cke V

rif(T

ck/2) = Q

r= I

in· T

ck(2.10)

2 C

r2 · C

rdove con Cr si è indicato il condensatore di riferimento, con Qr la carica accumulata da esso quando il segnale di clock è nullo e Tck indica la durata temporale del clock.

L’aumento della tensione Vrif provoca uno sbilanciamento sull’ingresso dell’operazionale

OTA2; poiché esso tende ad annullare questo sbilanciamento, risponderà alla variazione del suo ingresso, aumentando la corrente I1.

Questa situazione è resa possibile grazie al fatto che l’integratore INT2 è chiuso in reazione negativa con OTA2, e quindi il sistema tende a recuperare ogni sbilanciamento degli ingressi.

Ciò rende possibile, istante per istante, l’uguaglianza tra le tensioni Vrif e Vmis,quindi

valgono le seguenti relazioni:

Q

r= I

1· T

cke V

mis(T

ck/2) = Q

sens= I

1· T

ck(2.11)

2 C

sens2 · C

sensdove per Csens si è indicata la capacità introdotta dal sensore e con Qsens la carica accumulata nel semiperiodo basso del segnale di clock.

In equivalenza alle 2.10 e 2.11 si può esprimere l’uguaglianza tra Vrif e Vmis anche nel

seguente modo:

Tck/2

Tck /2

1

∫

I

1dt = 1

∫

I

indt

=T

ck· I

in( 2.12)

C

sens 0C

r 02

· C

rDurante la fase in cui il clock è basso, l’integratore INT3 è attivo, poiché la pass gate s3 è chiusa essendo pilotata dal clock negato. In questa situazione INT3 integra la differenza tra la corrente I2, che è una replica di I1, e una corrente costante fornita dal generatore Iα.

In questa fase, che chiameremo di integrazione, la tensione VI comincia a salire ed il

condensatore CI comincia a caricarsi con corrente costante (I2 – Iα) e la carica accumulata

risulta:

Q

I= (I

2– I

α)· T

ckV

I(T

ck/2) = Q

I= (I

2- I

α)· T

ck(2.13)

2 C

I2 · C

ISi noti bene che la tensione VI ha come valore iniziale Vref valore che tra l’altro fa da

riferimento anche per gli altri due integratori INT1 ed INT2, quindi tutti e tre gli integratori hanno come valore, iniziale nella fase d’integrazione (carica di Cr, Csens e CI) una tensione

pari a Vref.

La figura 2.8 mostra questa situazione nel caso in cui Vref sia uguale a zero volt.

fig. 2.8 Fase di Integrazione degli Amplificatori INT1, INT2 e INT3 con Vref = 0 Volt

Analizziamo ora la fase successiva che parte dall’istante temporale t = Tck/2.

In questa fase il clock è a livello alto perciò le pass gate S1 ed S2 sono chiuse ed S3 risulta aperta.

L’integratore INT3 è disconnesso dall’amplificatore OTA2, e la carica accumulata dal condensatore CI (QI della 2.12), comincia a diminuire, quindi CI si scarica attraverso una

corrente costante fornita dal generatore Ipol (vedi fig. 2.7).

Si noti che il segnale Vpw, nel semiperiodo basso del clock, risulta nullo perché è il risultato

di un’operazione di and tra l’uscita del comparatore (CMP) e il clock stesso, ed essendo nullo il clock è nullo anche Vpw.

La fase di scarica di CI (fase di deintegrazione), comincia quando VI è maggiore di Vref; a

questo punto l’uscita Vpw diventa alta e ci rimane fin tanto che il valore di VI rimane

della fase di integrazione. Da ciò si capisce che nel semiperiodo alto del clock, Vpw è

forzato a zero dal CMP non appena la VI scende sotto la soglia Vref.

Risulta facile a questo punto calcolare la durata Tpw del segnale di uscita Vpw poiché esso coincide con la durata della fase di deintegrazione.

Un bilancio di carica sul condensatore CI dà come risultato la seguente espressione:

Tck/2

Tpw

∫

( I

2– I

α) dt =

∫

I

poldt

=T

pw· I

pol(2.14)

0 0 da cui si ottiene:T

pw· I

pol=

( I

2– I

α) ·

T

ck(2.15)

2

Dalla 2.12 si ricava il rapporto tra I2 e Iin che risulta:

I

2= I

in· C

sense quindi

T

pw· I

pol=

(

C

sens· I

in- I

α)

· T

ck(2.16)

C

rC

r2

Ricordando che Iαè proporzionalealla corrente Iin secondo la prima della 2.9 cioè:Iα = k1 · Iin ,si ottiene la seguente:

T

pw· I

pol= I

in·

(

C

sens– k

1C

r)

·

T

ck(2.17)

C

r2

Dalla seconda espressione della relazione 2.9 (Iin = k2 · Ipol ) si ricava il rapporto tra Iin ed

Ipol che è proprio k2.

L’espressione finale di Tpw che rappresenta la durata dell’impulso alto d’uscita risulta:

T

pw= k

2·

(

C

sens– k

1C

r)

·

T

ck(2.18)

C

r2

La figura 2.9 mostra, la temporizzazione del circuito di figura 2.7, con la relativa generazione dell’impulso d’uscita PWM (Vpw); in cui la scarica della tensione VI è lineare,

.

fig. 2.9 Temporizzazione completa dell’Interfaccia

I condensatori Csens e Cr in fase di deintegrazione, poiché il clock è alto e le pass gate di INT1 ed INT2 sono chiuse, si scaricano molto velocemente (scarica esponenziale) fino al valore Vref o nel caso preso in considerazione fino al valore zero (Vref = 0 V, fig. 2.9).

Al termine dell’impulso alto di clock il sistema è tornato nelle condizioni iniziali.

La formula 2.18 dimostra come il duty-cycle (Tpw/Tck)del segnale sia funzione lineare della

capacità del sensore, ma anche delle costanti k1 e k2; queste sono funzioni dei rapporti dei

generatori di corrente che alimentano il circuito (Iin, Ipol e Iα) di interfacciamento, e

vengono ottenute con specchi di precisione dallo stesso riferimento di corrente.

Il fatto di utilizzare degli specchi di precisione ci permette di dire che ogni eventuale disturbo agisce sia nella fase di carica di Csens, sia nella fase di scarica, in definitiva il

disturbo si propaga in uguale misura su tutti i generatori di corrente e questo permette di ottenere dei valori k1 e k2 che sono virtualmente costanti ed indipendenti dalla temperatura.

Quindi se Csens e Cr sono indipendenti dalla temperatura anche il duty-cycle del segnale di

Un ulteriore vantaggio di questo circuito di misura è che il valore dell’impulso che si ottiene e’ pressoché costante; infatti, il termine k1·Cr presente nella 2.18 permette di

eliminare l’offset tipico dei sensori di pressione capacitivi, e questo permette di avere una buona risoluzione nella misura di Tpw.

Supponiamo, ad esempio, che il condensatore che rappresenta il sensore, sia costituito da una parte fissa e da una variabile, cosa tra l’altro vera perché la parte variabile rappresenta il comportamento del sensore alle variazioni di pressione;avremo quindi la seguente situazione:

C

sens= C

0+ ΔC (2.19)

Il valore dell’impulso è:T

pw= k

2·

(

C

0+ ΔC – k

1C

r)

·

T

ck(2.20)

C

r2

Dalla 2.20 si capisce l’utilità del termine k1·Cr; infatti, scegliendo opportunamente il valore

di k1 si può ridurre notevolmente il contributo relativo all’offset (C0).

Per completare lo studio del comportamento del circuito in figura 2.7, osserviamo che la connessione in reazione del sensore, nell’integratore di Miller INT2, ha come risultato quello rendere insensibile il sistema alle capacità parassite Cp1, Cp2.

2.3 Riferimenti di tensione e di corrente

Nel paragrafo precedente, abbiamo visto come il circuito di interfaccia, utilizzi dei generatori di tensione e di corrente che abbiamo supposto ideali.

In realtà bisognerebbe tener conto degli effetti causati sia dal rumore sia dalla temperatura. Per eliminare i problemi relativi a questi due effetti, l’interfaccia utilizza un circuito denominato band-gap che realizza i riferimenti di tensione in modo che siano insensibili alle variazioni di temperatura.

Un riferimento di tensione denominato band-gap, è realizzato, in un processo CMOS, utilizzando solamente delle resistenze, dei condensatori, dei MOS e dei BJT di substrato. Nel nostro caso, sono stati utilizzati come BJT dei dispositivi npn a 5 V disponibili nel BCD6.

Il circuito sfrutta la combinazione dei coefficienti termici positivi dei resistori e dei coefficienti termici negativi della Vbe dei BJT montati a diodo, per ottenere un coefficiente

termico globalmente nullo (rif. [2]).

Dal nome si capisce che esso utilizza la dipendenza dalla temperatura dell’energia di gap del silicio in giunzioni polarizzate direttamente.

L’interfaccia ha un circuito band-gap capace di realizzare una tensione stabile ed indipendente dalla temperatura di 1.2 V.

Questa tensione è sfruttata per realizzare i riferimenti di corrente Iin, Ipol e Iα e poiché la

tensione di bandgap è stabile con la temperatura anche le tre correnti saranno stabili, da qui deriva anche la stabilità dell’impulso generato.

In realtà la tensione di bandgap subisce piccole variazioni in ampi intervalli di temperatura, e questo consente di dire che la tensione generata è stabile.

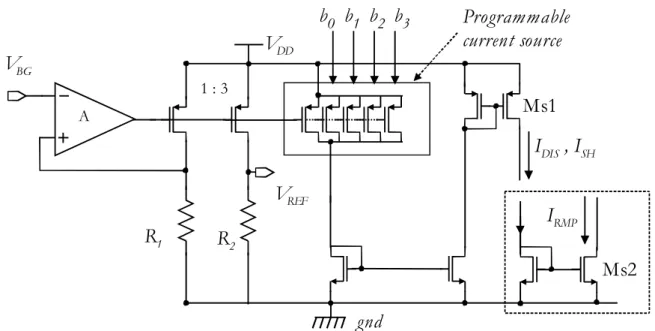

L’ interfaccia prevede inoltre la possibilità di variare le tre correnti, Iin, Ipol e Iα , attraverso

un blocco di calibratura che consente di modificarne il valore. La calibratura delle correnti è realizzata, con uno “specchio” di corrente programmabile a quattro bit; questo permette di regolare le correnti in modo che gli integratori rimangano in zona lineare e consente gli aggiustamenti opportuni per regolare l’offset, attraverso la modifica del termine k1 per

mantenere una buona risoluzione di misura. Uno schema del circuito e mostrato in figura 2.10.

gnd

b

1b

0b

2b

3V

BGV

REFV

DDR

1R

2 AI

DIS, I

SHI

RMP 1 : 3Programmable

current source

Ms1

Ms2

fig. 2.10 Generatore di Riferimenti

2.4 Sensore di temperatura

Nel paragrafo 2.2 sono state elencate le specifiche di progetto dell’interfaccia e abbiamo visto che tra queste si prevedeva la realizzazione di un sensore di temperatura on-board in grado di misurare temperature tra –40°C e 150°C.

Il circuito band-gap, utilizzato nell’interfaccia, per la generazione di riferimenti di corrente e di tensione costanti e insensibili alla temperatura, si presta bene alla realizzazione di questa specifica.

La corrente generata internamente al circuito band-gap è funzione della temperatura; perciò si sfrutta questa dipendenza per ottenere una tensione proporzionale alla temperatura T (rif. [3]).

2.5 Simulazione del Sensore Capacitivo

Il circuito di fig. 2.7 ci fa capire quali siano le grandezze significative dell’ interfaccia che dovranno essere misurate in fase di caratterizzazione.

Particolare importanza hanno le tensioni all’uscita degli integratori Vrif, Vmis e VI che ci

permetteranno di capire se la trattazione affrontata nel paragrafo 2.5 ha un riscontro reale. Il circuito integrato, realizzato con il processo BCD6 della STMicroelectronics (Bipolar- CMOS-DMOS), prevede insieme al circuito di figura 2.7, il sensore di temperatura e il

band-gap utilizzato per la realizzare i generatori programmabili di corrente Iin, Ipol e Iα.

Per rilevare le tre tensioni, sono stati aggiunti degli amplificatori in configurazione buffer la cui uscita va a finire direttamente in un PAD dell’integrato.

Il sensore capacitivo è stato sostituito con un equivalente “condensatore programmabile “ capace di simulare il sensore nell’intervallo richiesto dalle specifiche dell’interfaccia. Questo modello è utilizzato per verificare il principio di conversione di cui abbiamo parlato nel paragrafo 2.5.

Il sensore “simulato” è realizzato con un decoder 3-8 che abilita la capacità corrispondente (fig. 2.11). Nella tabella 2.1 sono riportati la configurazione in bit e l’equivalente valore di capacità. bc2 bc1 bc0 Capacità[fF] 0 0 0 Cext 0 0 1 C1=799 0 1 0 C2=869 0 1 1 C3=930 1 0 0 C4=992 1 0 1 C5=1060 1 1 0 C6=1130 1 1 1 C7=1200

Il circuito prevede anche la possibilità di effettuare delle misure su un condensatore esterno (Cext), che deve essere posto tra l’ingresso e l’uscita dell’integratore INT2 di fig.2.7,

quando i condensatori interni sono disattivati. I PAD in cui è possibile inserire questa capacità sono denominati CONPOS e CONNEG; i termini POS e NEG indicano la polarità del potenziale ai capi dei due terminali.

2.7 Analisi delle non Idealità dell’Interfaccia

In questo paragrafo saranno esaminati gli effetti delle non idealità che possono modificare il comportamento dell’interfaccia.

Nell’analisi sviluppata nel paragrafo 2.5, abbiamo trascurato dei fattori d’errore che sono ineliminabili, per questo motivo devono essere presi in considerazione per valutare le reali prestazioni del sistema.

I fattori da considerare sono tre, e sono: guadagno finito dell’integratore INT2, dalla stabilità dell’anello di reazione INT2-OTA2 e rumore.

Vediamo come intervengono sul funzionamento del circuito di figura 2.7

2.7.1 Errore da guadagno finito

Nel paragrafo 2.5 abbiamo sostenuto che l’integratore OTA2 doveva avere un guadagno elevato per garantire il cortocircuito virtuale, teoricamente il guadagno dovrebbe essere infinito.

L’integratore però ha un guadagno finito e questo determina l’introduzione di una tensione che provoca uno scostamento tra le tensioni Vmis e Vrif.

Dalla 2.17 si può ricavare la carica QI accumulata da CI alla fine della fase di

deintegrazione; questa risulta:

Q

I= Tpw

· I

pol= I

in·

(

C

sens– k

1C

r)

·

T

ck(2.21)

Con semplici considerazioni ([rif. 5]) si può dimostrare che, in presenza di guadano finito, la carica accumulata risulta:

Q

I= I

in· T

ck· C

sens·

[

1 - f

ck]

con f

pl= G

m2(2.22)

2

·

C

r( π · f

pl) C

sensL’errore introdotto nella carica accumulata dal condensatore CI alla fine della fase

d’integrazione risulta:

ΔQ

I =f

ck· C

sens· I

in· T

ckcon f

pl= G

m2(2.22)

(

π · f

pl)

2 · C

rC

sensdove fck è la frequenza di clock, Gm2 è la transconduttanza di OTA2 e fpl è la frequenza di

guadagno unitario dell’anello INT2-OTA2; per semplicità si è assunto k1 nullo.

Questo produce un errore sull’impulso d’uscita dato da: ΔQI/Ipol e il conseguente errore

risulta:

Δ T

pw=

f

ck·

C

sens(2.23)

T

pw(

π · f

pl)

(Csens

-k

2·C

r)

Per minimizzare quest’effetto deve essere rispettata la condizione fck<<fpl; se la frequenza

di clock è troppo piccola però ci sarebbe il rischio che le rampe generate dagli integratori vadano in saturazione compromettendo il corretto funzionamento del circuito; per evitare ciò in presenza di piccole capacità d’integrazione sarebbero necessarie delle correnti di caricamento dei condensatori molto piccole e questo introdurrebbe un ulteriore errore dovuto ad una possibile corrente addizionale (corrente di leakage).

Si può pensare di realizzare una fpl che, sia la più alta possibile, tale condizione, purtroppo,

si scontra con la necessità di mantenere stabile l’anello di reazione INT2-OTA2, e con la necessità di minimizzare il rumore nel circuito.

L’equazione 2.23 dimostra, inoltre, come l’errore sull’impulso misurato è dipendente sia dal processo sia dalla temperatura, tramite la relazione che lega fpl alla transconduttanza

Gm2 dell’amplificatore OTA2.

2.7.2 Errore da offset e da stabilità dell’anello di reazione

Le fonti che producono un effetto rilevante, sulla durata dell’impulso, sono principalmente tre:

1. l’offset introdotto dal comparatore CMP e dall’integratore INT3; 2. la corrente di rumore di Iin, Ipol e Iα;

3. la corrente di rumore del transistor della porta 2 dell’amplificatore OTA2.

Il contributo di rumore dovuto all’offset del comparatore e dell’integratore, subisce un filtraggio di tipo passa-alto con frequenza di taglio nell’ordine della frequenza di clock (fck= 50KHz), pertanto risultano importanti le componenti di alta frequenza.

Per ridurre questo contributo è stata limitata la banda di CMP e INT3.

Diverso è il discorso sul rumore introdotto dalle correnti di rumore ( punti 2. e 3.).

Questi contributi subiscono all’interno del sistema un filtraggio di tipo passa-basso con frequenza di taglio nell’ordine di due volte la frequenza di clock (2fck).

In questo range di frequenze, purtroppo si manifesta il rumore flicker, che ricordiamo ha una densità spettrale di potenza proporzionale all’inverso della frequenza (1/f).

Un modo per ridurre l’effetto del rumore flicker sarebbe quello di incrementare l’area dei transistor, ciò porta dei problemi sulla stabilità dell’anello OTA2-INT2.

Per capire meglio consideriamo la porta 1 del circuito di figura 2.7, essa è inclusa nell’anello di reazione cosi che il rumore per la corrente I1 subisce un filtraggio passa alto

con frequenza di taglio fpl; questo contributo non influisce sulla durata dell’impulso.

Diverso è il discorso relativo alla porta di uscita 2 dello stadio OTA2, infatti, esso è fuori dall’anello di reazione e quindi introduce un contributo di rumore a bassa frequenza che influisce sulla durata dell’impulso.

L’aumento dell’area di gate, dei transistor della porta 2 di OTA2, per ridurre il rumore flicker, provoca come risultato il deterioramento della risposta in fase; poiché per mantenere il matching dei transistor bisogna aumentare anche l’area dei transistor della porta 1 di OTA2.

Il sistema INT2-OTA2 ha, infatti, un guadagno d’anello (βΑ) con uno zero (f0) a parte

reale positiva, ed un polo; entrambe le singolarità possono portare instabilità se la loro frequenza si avvicina o scende sotto fpl.

L’aumento di area dei transistori in uscita provoca proprio un abbassamento della frequenza delle singolarità, siccome si dimostra che con le dimensioni in gioco la frequenza di zero è inferiore a quella di polo, è lo zero che impone un limite superiore alla fpl che non può essere superato (vedi paragrafo 2.7.1).

Per risolvere questo problema è stata adottata, per l’amplificatore OTA2, una topologia che permette alle rampe Vrif e Vmis di avere un grande intervallo di variazione in modo da non

richiedere piccole correnti di polarizzazione; questo consente poter allargare l’area del gate del MOS della porta 1 di OTA2, e quindi di avere lo zero del βΑ in una posizione tale che f0> fpl senza rischiare l’instabilità del sistema.Si ricordi che, f0 dipende dalla corrente dell’

amplificatore OTA2 attraverso il Gm ( transconduttanza di INT2) di INT2.

L’effetto delle sorgenti di rumore comunque si manifesta sull’impulso di uscita attraverso un jitter, causato principalmente dal blocco CMP-INT3.

2.8 Realizzazione Basetta di Test

Quello che ci proponiamo di raccontare in questo paragrafo, sono i passi effettuati per testare il circuito partendo dal Wafer su cui è stato realizzato fino al posizionamento su basetta di test. Prima di far questo, riepiloghiamo gli elementi del circuito integrato che interesseranno la fase di testing.

Il circuito integrato che andremo a testare è stato fabbricato dalla sezione MEMS della

STMicroelectronics con il processo BCD6.

Il chip comprende, come accennato nel paragrafo 2.2 oltre al circuito di figura 2.7, un sensore di temperatura, un generatore di tensione di riferimento “band-gap” e dei generatori di correnti programmabili che provvedono a fornire Iin, Ipol e Iα.

Il chip è disegnato usando dispositivi CMOS a 0.35 mm –3.3 V, eccezion fatta per il band-gap che utilizza anche i transistori bipolari npn a 5 V, previsti dal processo.

Il sensore è simulato attraverso un set di differenti condensatori, selezionabili attraverso tre interruttori controllati da ingressi digitali a tre bit.

Il valore della capacità è variabile e parte da un valore minimo di 0.8 pF, fino ad un valore massimo di 1.2 pF con valori intermedi determinati dalla configurazione degli ingressi digitali; esiste la possibilità di inserire un sensore esterno selezionando una particolare configurazione dei bit. (vedi paragrafo 2.8 tab. [1])

Sono previsti, dei PAD, da cui andare a prelevare le tensioni significative del circuito e cioè: Vrif, Vmis e VI che nel circuito realizzato si chiamano convenzionalmente testrif, testmis e testrampa, e naturalmente i pad relativi alla tensione di alimentazione (Vdd) alla

massa del circuito (gnd), al segnale di reset e al segnale di clock.

Il clock è un segnale digitale con duty-cycle del 50% con valori di soglia 0 e 3.3 V.

Per effettuare i nostri test, dobbiamo realizzare una basetta da cui poter prelevare-inserire 26 segnali, tanti quanti sono i piedini (PAD) del circuito.

La prima cosa da fare, consiste nel tagliare dal Wafer la porzione di circuito che c’interessa.Questa è un’operazione delicata, poiché il wafer è tagliato manualmente con una punta diamantata, che anche se precisa, se si esercita una forza elevata rischia di rovinare il circuito.

Una volta tagliata la porzione di nostro interesse, controlliamo, al microscopio che non ci siano danni al circuito, provocati da quest’operazione.

Ora che abbiamo verificato la bontà del taglio, si passa alla fase successiva che consiste nel realizzare la basetta su cui depositare il circuito.

Per realizzare la basetta, abbiamo bisogno realizzare le piste, che andranno a costituire i collegamenti tra i PAD del circuito e i PAD esterni.

Per fare questo, prendiamo una basetta completamente ramata su una superficie, munita di uno strato fotosensibile (fotoresist) su cui impressioneremo le piste.

Quest’operazione, si effettua appoggiando un foglio lucido, su cui sono disegnate le piste, sul fotoresist. Per impressionare il fotoresist e quindi realizzare le piste in rame inseriamo la basetta, su cui abbiamo appoggiato il foglio lucido, nel bromografo per circa due minuti. Il bromografo è basato su una lampada UV che, permette di rendere solubili le porzioni di fotoresist non protette dalle parti scure del lucido.

In altre parole, il disegno che sta sul foglio, fa da filtro alla luce del bromografo e impedisce che il fotoresist che sta in corrispondenza del disegno delle piste, sia eliminato nella successiva fase di sviluppo.

Dopo lo sviluppo, la basetta viene immersa in un attacco del rame (acido cloridrico, acqua e acqua ossigenata).

Il rame protetto dal fotoresist non rimosso dallo sviluppo, permane dopo l’attacco realizzando la geometria richiesta di piste conduttive.

In previsione, delle successive misure in temperatura, che dovremo effettuare, realizziamo dei fori in corrispondenza degli spigoli della basetta. Le misure in temperatura saranno effettuate utilizzando un criostato; i fori serviranno per fissare la basetta sul criostato in modo da ottenere un buon contatto termico.

Ora che le piste sono pronte incolliamo il circuito sulla basetta, con un sottile strato di colla epossidica.

Una volta incollato il circuito bisogna collegare i PAD del chip con le piste in rame, in modo che questi siano facilmente accessibili all’esterno. I collegamenti, PAD-piste, sono realizzati con microsaldature da un tecnico qualificato, mediante WEDGE BONDING. L’accessibilità dei piedini, si realizza saldando dei fili elettrici sui pad delle piste in rame.

Un accorgimento molto importante in questa fase consiste nel mettere allo stesso potenziale, in genere a massa, il saldatore, il piedino di alimentazione e il piedino di massa; questa operazione serve per evitare che dispersioni o elettricità statica dal saldatore causino dei cortocircuiti tra i PAD del chip che renderebbero inutilizzabile il sistema.

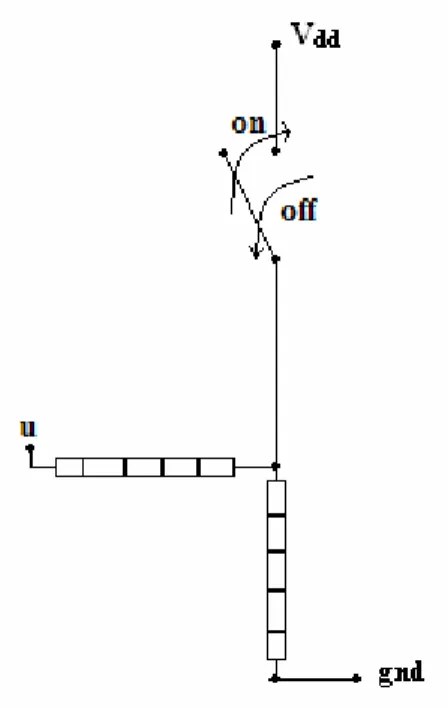

2.9 Circuito ad Interruttori per la calibratura delle correnti

Programmabili

Abbiamo visto nei paragrafi precedenti, come nell’interfaccia si abbia la possibilità di variare le correnti di carica-scarica dei condensatori, attraverso la modifica di alcuni bit di configurazione. Esistono tre distinti generatori di corrente, Iin, Ipol e Iα, e ognuna di esse è

modificabile attraverso un set di bit; in particolare ogni sorgente ha a disposizione quattro bit per la modifica della configurazione delle correnti.

La possibilità di modificare le correnti è molto importante, perché ci permette di mantenere il circuito in un regime di funzionamento lineare, evitando che le rampe generate dagli integratori vadano in saturazione; ad esempio per valori troppo piccoli, o troppo grandi di capacità, che fanno saturare le rampe di generazione dell’impulso, la modifica delle correnti permette un recupero di questa situazione di non linearità.

Guardando l’equazione (2.17) si capisce il significato dell’affermazione precedente; infatti modificando Iin e Ipol si modifica il guadagno del sistema, mentre il termine relativo ad Iα

contribuisce alla riduzione dell’offset. Il contributo dovuto alla programmabilità consente di ottenere una buona calibratura del sistema.

Una possibile procedura di calibratura è la seguente:

− Si fissa il valore di Iin, in modo che l’integratore di riferimento Cr, generi una

rampa, sfruttando il più possibile la dinamica, ma senza raggiungere la zona di saturazione; in pratica si possono raggiungere valori picco-picco di circa 2 V.

− Si attribuisce ad Iα, un valore che consenta alla rampa generata sull’uscita, quando

il sensore è al valore minimo, di raggiungere la tensione di soglia alta del comparatore cosicché si possa avere lo scatto per la generazione dell’impulso.

− Si fissa il valore di Ipol, in modo da avere una buona risoluzione di lettura

sull’impulso di uscita (impulso il più ampio possibile senza eccedere il semiperiodo).

Per eff configu

tal fine è stata costruita una scheda di “calibrazione” delle correnti e di modifica dei

ontrollata da quattro bit di configurazione mentre il condensatore è gestito

ente di abilitare-disabilitare ogni singolo bit in modo

è disabilitato (posizione OFF), questo è connesso al potenziale di ettuare queste operazioni di calibratura è necessario poter controllare i bit di razione.

A

condensatori che simulano il sensore. Ogni corrente è c

da un insieme di tre bit.

E’ stato realizzato un sistema che cons

che quando il bit è abilitato (posizione ON), questo è connesso alla tensione di alimentazione, mentre se

riferimento (ground).

Il sistema di calibratura è stato realizzato con una basetta “mille-fori”, in cui sono stati sistemati degli switch per modificare i bit di configurazione e delle resistenze secondo la figura 2.11.

Il risultato finale che si ottiene è quello di figura 2.12.

fig. 2.12 Sche della capacità

ON, l’uscita relativa (ui) si trova ad un potenziale di

dd assa.

Un ultim il chip, è quello di

me

ceram veloci, la tensione

fornita al circuito.

ndo di reset

(rst), che com dell’integratore

INT3. (fig. 2.7)

A questo punto, siam a; prima di fare

Il circuito n i PAD

attraverso delle microsaldature, il sistema nel suo complesso risulta molto delicato; dei da per la calibrazione delle correnti e modifica

Quando gli switch sono in posizione

V ; in posizione OFF l’uscita si trova a potenziale di m

Il connettore di uscita, serve per collegare i fili che precedentemente abbiamo saldato sulla basetta, per poter pilotare le grandezze di controllo del sistema.

o piccolo accorgimento che riguarda la basetta su cui è disposto

ttere tra piste relative alla tensione di alimentazione e il ground, un condensatore ico da 1µF; ciò serve a mantenere stabile, rispetto alle variazioni

Dalla figura 2.12, si nota che è presente anche un bit per il controllo del coma e abbiamo detto permette di scaricare il condensatore CI

o in grado di cominciare la caratterizzazione del sistem ciò, vogliamo discutere sulle difficoltà incontrate con questo tipo di board-testing.

situato sulla basetta, abbiamo detto, contatta le piste di rame co

movimenti bruschi o degli urti potrebbero far “saltare” le saldature. Viste le dimensioni e le distanze ridotte, non è stato possibile mettere una copertura di protezione delle

microsaldature, che sarebbe risultata di difficile realizzazione, la figura 2.13 mostra la basetta finita realizzata come indicato al paragrafo precedente.

fig. 2.13 Basetta per le misure di caratterizzazione

Nonostante le difficoltà, questa soluzione ci ha permesso di effettuare numerosi test sia a temperatura ambiente sia variando la temperatura, (si vedrà nel capitolo successivo che iamo riusciti a testare il chip a temperature comprese tra 0°C e 80°C), proprio per la

vista m

Per spieg ato al

centro d

eriore

e delle mi

Le m e; in

purtroppo, a contatta no al perimetro del

s

facilità di sistemazione all’interno del criostato.

Purtroppo la fragilità di questa board di misura, non si è manifestata soltanto dal punto di eccanico, ma anche dal punto di vista elettrico.

are cosa si intende per fragilità elettrica, ricordiamo che il chip è posizion ella basetta e fatto aderire ad essa con l’utilizzo di una colla.

Anche se si usa uno strato sottile di colla, il chip si troverà sempre ad un’altezza sup rispetto alle piste in rame, essendo esse posizionate sulla basetta.

Questa posizione di rilievo del circuito, crea notevoli difficoltà alla realizzazion crosaldature.

icrosaldature, infatti, partono dai PAD e finiscono sulle piste in ram

quest’operazione esse tendono a schiacciarsi sulla superficie del circuito, andando rsi con la linea di massa (scribe-line) che sta intor

Il contatto dei PAD con la metal della CHIP-OUTLINE, causa un cortocircuito, che fa perdere la funzionalità al piedino corrispondente, o altre volte portava il piedino ad avere

lla per nostra scelta, essa si trovava

esente la microsaldatura

o di microsaldatura.

un valore diverso da quello che ci saremmo aspettati; ad esempio se il bit due di Iin, tramite la scheda di calibrazione, doveva risultare a tensione nu

a valori superiori a zero; questo provocava un malfunzionamento con conseguente inutilizzabilità dell’intero chip.

Le fotografie di figura 2.14 [a] e 2.14[b], realizzate con il microscopio elettronico, evidenziano il contatto tra PAD e CHIP-OUTLINE, quando è pr

(fig. 2.14[a]). La figura 2.15[b] mostra il danneggiamento della CHIP-OUTLINE dopo la rimozione del fil

Le fotografie evidenziano il cortocircuito di cui abbiamo discusso.

UTLINE fig. 2.14[a] Microsaldatura e contatto tra PAD e CHIP-O

fig. 2.14[b] Rimozione della saldatura ed evidenza del cortocircuito

Il modo che abbiam di alloggiare il chip in un

case con 28 piedini.

Il case cons collegati i piedini

del case; il filo delle m saldato arrivando dall’alto in

aniera quasi

tangenziale com il contatto con la

chip-outline.

arrivando su a l’opposto.

In questo m ente, urtando la

chip-outline.

Questo tipo d zionalità dei

piedini del circuito; inoltre il case può essere coperto e questo garantisce una maggiore o adottato, per risolvere il problema, è quello

ente di sistemare il chip sotto il livello delle piste a cui sono icrosaldature, in questo modo, viene

una posizione quasi perpendicolare rispetto al piano dei pad e non in m e avveniva in precedenza, condizione che provocava

Inoltre, decisiva è stata anche la scelta di effettuare la saldatura partendo dal PIN del case e l PAD invece che con la tecnica convenzionale che prevedev

odo si ha un ulteriore garanzia che il filo non parta tangenzialm

i saldatura garantisce una maggiore sicurezza sulla futura fun