8

8

IL SISTEMA GESTIONE DATI

8.1 Introduzione

Grazie alle nuove tecnologie, è ora possibile utilizzare a bordo dei satelliti po-tenze di calcolo notevolmente maggiori di quelle usate fino a una ventina di anni fa a fronte di una netta diminuzione di costo.

Nel presente capitolo si cerca di dare una stima preliminare dell’architettura di sistema e degli ingombri e delle potenze richieste tipiche dei singoli componenti. Si deve notare che la maggior parte di questi sistemi sono progettati per quote molto più alte di quella a cui la piattaforma si troverà ad operare, quindi i sistemi di gestio-ne dati sono progettati tegestio-nendo conto delle problematiche legate all’attraversamento delle fasce di Van Halen, e quindi implicitamente molto più complicati e costosi.

Resta sottointeso che, in fase di progetto più dettagliato, sarà possibile adope-rare tecnologie molto meno complicate in grado di fornire prestazioni e costi migliori di quelle qui considerate.

8.2 Architettura del sistema

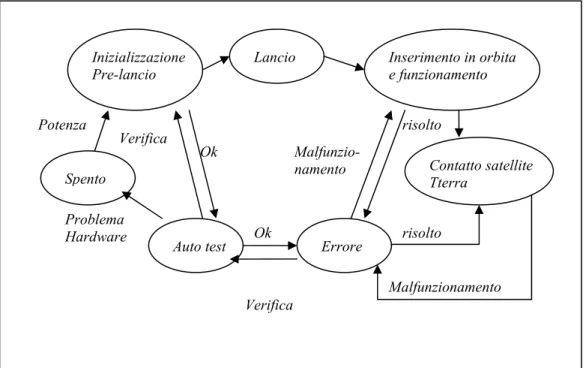

L’intero sistema dev’essere in grado di avere più livelli di funzionamento come illustrato nella figura 8.2.1.

figura 8.2.1 Stati tipici di lavoro di un calcolatore di bordo

L’arrangiamento dei singoli componenti può aver differenti architetture le più comuni sono:

• Architettura centralizzata: va bene per sistemi piccoli in quanto ogni componente si interfaccia con il componente centrale ed un malfunzio-namento in uno dei componenti non pregiudica il funziomalfunzio-namento degli al-tri. D’altra parte è molto complicato cambiare o espandere l’hardware.

Inizializzazione

Pre-lancio Lancio Inserimento in orbita e funzionamento

Contatto satellite Tterra Errore Auto test Spento Ok Malfunzio-namento Ok risolto Problema Hardware risolto Malfunzionamento Verifica Potenza Verifica Sensori di

stelle Sensori di terra

Ruote

Propulsori

GPS Giroscopi

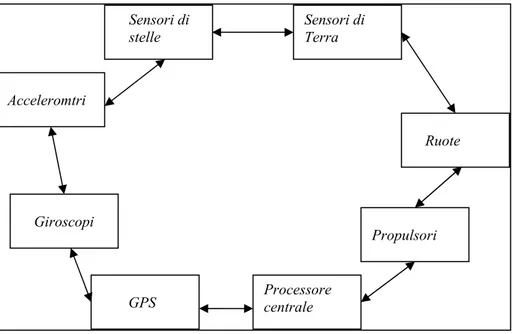

figura 8.2.3 Schema di una tipica architettura ad anello

• Architettura distribuita: in cui la trasmissione dei dati è migliorata dal fat-to che è diretta verso i singoli componenti; devono, però, essere progettati ognuno una interfaccia opportuna.

figura 8.2.4 Schema di una tipica architettura distribuita

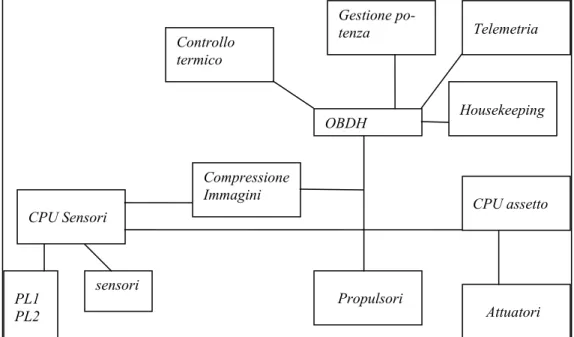

Nel caso in questione è stata adottata una configurazione mista in cui le fun-zioni più complicate, quali il controllo dei sensori ed il controllo d’assetto, sono state assegnate ad unità specifiche.

Sensori di stelle Sensori diT-terra Ruote Propulsori GPS Giroscopi Acceleromtri Processore centrale Sensori di stelle Sensori di Terra Ruote Propulsori GPS Giroscopi Acceleromtri Processore centrale

figura 8.2.5 Architettura dell’elettronica di gestione dati

8.3 Scelta dei componenti

E’stato possibile ricercare sul mercato componenti simili a quelli voluti, e quindi di stimarne il peso e la potenza assorbita. Tutti questi componenti hanno po-tenze di calcolo sufficienti se non superiori a quelle desiderate; la scelta è, dunque, da considerarsi solo come una stima di massima. Infine si tenga presente che l’acronimo OBDH sta per On Board Data Handling, trattamento dei dati a bordo, e nella nostra configurazione indica il computer centrale che gestisce tutte le operazio-ni e controlla i sottocomponenti.

8.3.1 Memoria di massa

figura 8.3.1 EROS Memory Board (In via di sviluppo)

OBDH Controllo termico Compressione Immagini Propulsori CPU Sensori Housekeeping Telemetria Gestione po-tenza PL1 PL2 sensori Attuatori CPU assetto

• capacità di eseguire auto-test singoli o completi per ogni banco di memoria;

• 2 linee ridondanti 54LVTH245 Internal bus • fino a 10 MHz di frequenza;

• potenza assorbita < 7 W max; • massa della memoria : 850 g • dimensioni : 237 mm x 240 mm.

• temperature di esercizio: - 35°C to +85 °C.

8.3.2 Compressione immagini

figura 8.3.2 EROS JPG Immage compression Board • potenza assorbita : 14 W max a 36 Mpix/s @ + 5 V; • massa: 1,1kg;

• dimensioni: 230 x 300 x 25 mm; • capacità di compressione ¼; • 1 canale a 36 Mpix/s; • 3 canali a12 Mpix/s; • 4 canali a 6 Mpix/s.

8.3.3 CPU controllo d’assetto

figura 8.3.3 CRISA Attitude control computer • massa : 5.9 Kg;

• dimensioni : 279 x 200 x 158 mm;

• potenza assorbita : 4.3 W min. 7 W max.; • vita operativa: 10 anni;

• processore: 9 MHz 0.9 MIPS;

• 32 kwords x 16 ROM 64 kwords x 16 RAM; • capace di eseguire auto –test;

• ridondanza fredda.

8.3.4 CPU sensori

figura 8.3.4 CRISA Data Processing Electronics • velocità 13.3 MHz 1.25 MIPS;

o attesa: 8.2 W;

o modo minore Potenza: 1.9 W;

• acquisizione fino a 5Mbps di dati scientifici su 2 canali; • acquisizione su 4 canali di dati sullo stato degli strumenti; • acquisisce fino a 16 sensori simultaneamente;

• completamente ridondante.

8.3.5 OBDH

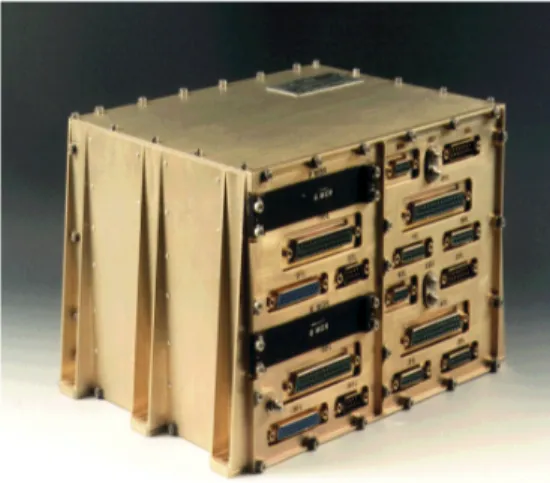

figura 8.3.5 OHB Sytstems

• DSP (digital signal processor, processore del segnale digitale) com-puter a lato singolo;

• memoria: 5.5 Mbyte fast SRAM and 1.4 Mbyte EEPROM; • dimensioni: 160 mm x 140 mm;

• potenza Assorbita: 5.5 W (tipica); • voltaggio: 5V e 3.3V DC.

tabella 8.3-1 Pro e contro della configurazione adottata

Scelta effettuata Vantaggi Svantaggi

Architettura del sistema

Maggiore capacità di ge-stione dati.

Maggiore complessità del sistema e maggiore difficoltà nell’aggiunta di nuovi componenti. Componentistica Componenti affidabili e

disponibili sul mercato.

Necessità di riqualificazione e di progetto del-le varie interfacce.