31

Capitolo 2

Piattaforme di sviluppo

Introduzione

Viste le specifiche di progetto è possibile motivare la scelta delle piattaforme hardware e software sfruttate per la realizzazione del sistema elettronico sviluppato dal gruppo di lavoro dell’Università di Pisa nell’ambito del progetto SPADA. Verranno pertanto mostrate le risorse hardware comprendenti le schede di supporto progettate e realizzate su PCB (Printed Circuit Board) e la scheda di elaborazione dei segnali provenienti dai sensori. In seguito si darà una descrizione della piattaforma di sviluppo software ossia dei tool di progetto utilizzati per la realizzazione del sistema.

2.1 Piattaforma di sviluppo Hardware

2.1.1 Una visione d’insieme

Come si è visto nel capitolo precedente, il collegamento tra la

detection board e la data processing board è realizzato in modo differenziale

tramite una coppia di cavi SCSI a 68 pin. Si è resa necessaria pertanto la progettazione e realizzazione di due schede (una scheda sola, a causa dell’ingombro fisico dei connettori SCSI non sarebbe stata sufficiente) per l’acquisizione dei segnali provenienti dagli iAQC. Tali schede sono dotate, oltre che di connettori SCSI, di ricevitori differenziali che operano la conversione in single ended dei segnali e le cui uscite sono direttamente connesse alla Data Processing Board.

Per la gestione dei segnali di gate e interlock necessari rispettivamente al mascheramento degli iAQC e allo spegnimento dei sensori in casi di emergenza è stato deciso di utilizzare una connessione

32 tramite cavi coassiali sfruttando dei connettori SMC. Ciò ha reso necessarie pertanto la progettazione e realizzazione di un’ulteriore scheda che consentisse il corretto interfacciamento con la Detection Board. Si è deciso di dotare questa scheda di otto connettori SMC, quattro di ingresso e quattro di uscita, in modo da rendere possibile l’utilizzo in futuro di altri segnali di controllo.

Per quanto riguarda la parte audio richiesta dalle applicazioni AO e LS, è stata sviluppata una scheda per la generazione dei toni sinusoidali sulla quale è stato inserito anche un connettore seriale per i comandi e le letture relative alla detection board (temperatura, over-voltage, hold-off time).

La parte centrale del sistema, ovvero il conteggio degli impulsi provenienti dagli iAQC, l’upload dei risultati e tutta la parte di data-processing è stata affidata ad una scheda commerciale, la Micro-line Compact C6713 prodotta da Orsys di cui si darà una descrizione più dettagliata in seguito. La scelta di questa scheda, dotata di grande potenza di calcolo, di una ampia capacità in termini di logica programmabile e soprattutto in grado di supportare la connettività IEEE1394 è stata dettata dalla necessità di elaborazione dati con alta velocità di esecuzione, dal bisogno di implementare un hardware ingombrante in termini di risorse programmabili e dai requisiti di acquisizione in tempo reale dei risultati di conteggio. Quest’ultimo requisito si traduce nella necessità di poter effettuare l’upload dei risultati di conteggio senza perderne alcuno anche nel caso peggiore, ossia nell’applicazione FTI con la minima finestra di acquisizione pari a 10 µs. In questo caso, come visto, è necessario un bitrate pari almeno a 96 Mbps. Ciò ha portato a scegliere come link per l’upload dei risultati di conteggio il collegamento FireWire, definito dallo standard IEEE1394, che supporta una velocità di trasferimento massima pari a 400 Mbps.

La scheda Orsys necessita di una tensione di alimentazione pari a 5V. Vista tuttavia la necessità di disporre di una tensione di alimentazione

33 più elevata (pari a 12V) per poter far funzionare l’amplificatore presente sulla scheda audio, è necessario un regolatore di tensione che fornisca i 5V richiesti dalla scheda Orsys. Si è resa necessaria pertanto la progettazione di un alimentatore (Power Supply Board) che, a partire dai 12V richiesti dalla parte audio, generasse i 5V necessari alla C6713. Tale alimentatore consiste in una ulteriore scheda ausiliaria direttamente connessa alla Data

Processing Board tramite il connettore micro-line di cui si parlerà in seguito.

Tutte le schede a cui si è fatto cenno sono connesse tra loro attraverso un back panel ovvero una scheda PCB sulla quale sono stati montati dei connettori DIN per l’interfacciamento con le altre schede e che garantisce la distribuzione dell’alimentazione e dei segnali tra le stesse. Il back panel, assieme alle diverse schede è ospitato in uno chassis rack da 19 pollici fornito da ESO, dotato di un’alimentatore che provvede a fornire i 12V richiesti a partire dalla tensione di rete.

Figura 2.1: Chassis Rack da 19" con schede montate. Da sinistra: Scheda GPIO, coppia di schede ricevitori, scheda audio e RS-232, Data Processing Board.

34

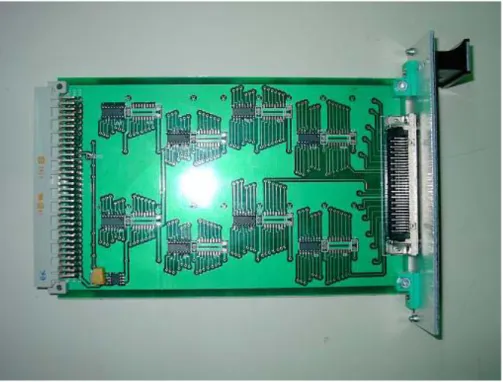

2.1.2 Schede ricevitori

Come accennato tali schede provvedono a ricevere i segnali differenziali tramite i connettori SCSI connessi ai cavi provenienti dalla

Detection Board e ad operare la conversione in single ended dei segnali stessi

ridistribuendoli sul back panel. I dispositivi scelti per assolvere a questa funzione sono gli integrati appartenenti alla famiglia 26LV32. In particolare si è scelto il dispositivo Texas Instruments AM26LV32: esso è costituito da quattro ricevitori differenziali alimentati a 3.3V, quindi con uscite legate a tale tensione, che tuttavia possono sopportare in ingresso tensioni differenziali superiori a 5V. La massima frequenza di utilizzo garantita è di 32 MHz, sufficiente al caso in esame, in cui la massima frequenza dei segnali provenienti dagli iAQC è di circa 20 MHz. Ogni scheda è dotata di otto AM26LV32, in modo da poter ricevere fino a 32 canali differenziali (nel caso in esame due canali sono inutilizzati).

35 Vista la necessità di avere due schede di ricevitori differenti a livello di PCB esclusivamente per quanto riguarda la connessione con il back panel è stata prevista una connettività personalizzabile a questo livello in modo da poter saldare tra loro i contatti in prossimità del connettore DIN in senso orizzontale o verticale a seconda che si tratti della scheda per i primi trenta segnali o di quella per gli ultimi.

Figure 2.3: Personalizzazione verticale ed orizzontale dei contatti delle schede ricevitori con i connettori DIN.

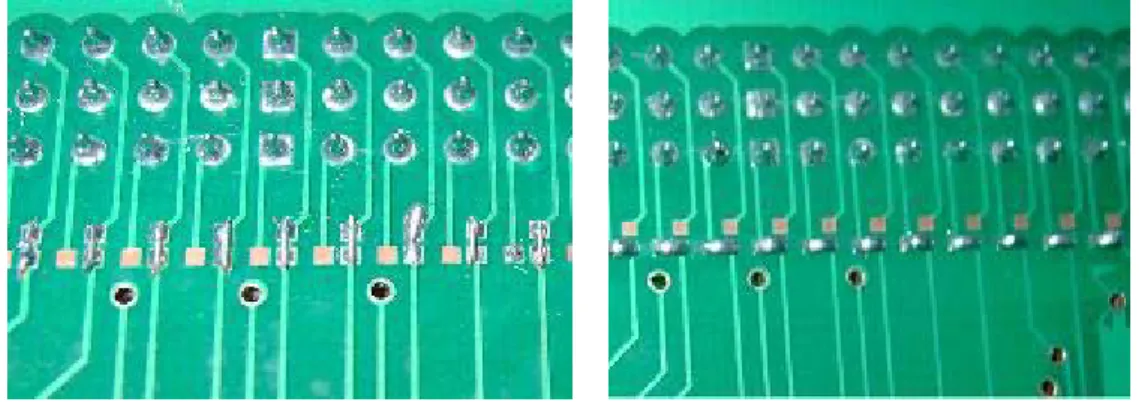

2.1.3 Scheda GPIO

La scheda GPIO (General Purpose Input Output) provvede alla ricezione o all’invio dei segnali di Gate e Interlock la cui funzione è stata esposta in precedenza. Oltre ai connettori dedicati alla ricezione dei segnali di Gate e Interlock hardware e all’invio dei segnali di Gate e Interlock alla Detection Board sono presenti altri quattro connettori utilizzabili per scopi futuri. I totale quindi sono stati montati sulla scheda 8 connettori coassiali SMC. Sono stati scelti i connettori coassiali SMC per montaggio su pannello della Radiall.

I segnali provenienti dai o inviati ai connettori passano attraverso dei buffer per la regolazione dei livelli di tensione richiesti dalle specifiche. Come buffer di uscita è stato scelto il Quad Buffer (3 state) 74ABT125 della Philips, mentre come buffer di ingresso è stato scelto il Quad Buffer (3

36 state) SN74LVT125D della T.I. entrambi funzionanti a bassa dissipazione e alta velocità.

Figura 2.4: Scheda GPIO.

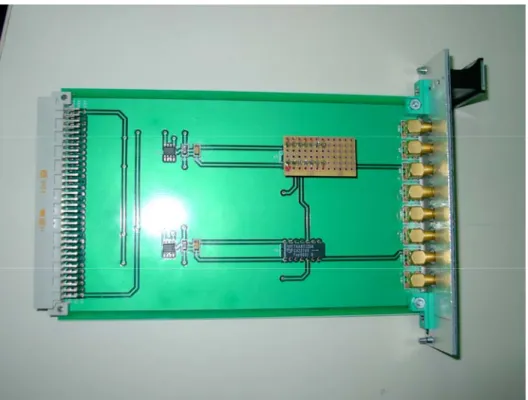

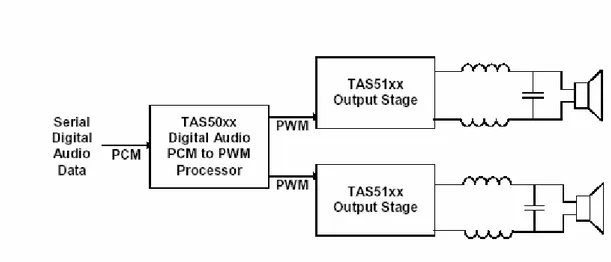

2.1.4 Scheda audio

La scheda dedicata alla generazione della sinusoide nell’ambito delle applicazioni AO e LS è la seconda per complessità dopo la Data

Processing Board all’interno dell’intero sistema. La progettazione della

scheda è stata effettuata seguendo lo standard proposto da Texas Instruments per la riproduzione di segnali in banda audio ad alta fedeltà denominato TDAA (True Digial Audio Amplifier). Lo standard è studiato per applicazioni digitali e prevede la conversione di un segnale audio da formato PCM (Pule Code Modulated) a PWM (Pulse Width Modulated), l’amplificazione del segnale stesso attraverso un amplificatore PWM e in seguito la demodulazione del segnale modulato attraverso un semplice filtro passa basso. Il sistema TDAA è caratterizzato inoltre da un anello di reset detto closed loop reset che serve a evitare situazioni di errore e funge

37 da ulteriore protezione per l’intero sistema. Il pregio principale di questo standard è ovviamente la possibilità di lasciare il segnale nel dominio digitale fino alla fine in modo da minimizzare gli effetti di distorsione dovuti alla presenza di rumore grazie alla intrinseca robustezza del segnale digitale.

Figura 2.5: Schema a blocchi riassuntivo dello standard TDAA.

Sulla scheda sviluppata nell’ambito del progetto SPADA sono presenti due integrati che implementano lo standard TDAA: il modulatore PCM-PWM TAS5001 e l’amplificatore PWM TAS5121. Il TAS5001 presenta due ingressi dati sui quali supporta diversi formati audio PCM tra cui l’IIS (Inter Integrated Sound) che è stato sfruttato nel progetto SPADA ed è in grado di generare due segnali PWM differenziali in modo da poter pilotare due amplificatori e fornire globalmente un segnale stereofonico. Nel caso in esame solo una delle due uscite differenziali è stata sfruttata, quella relativa al canale sinistro, essendo sufficiente un solo canale audio. Le modalità di funzionamento sono diverse. Tra le tante è stata scelta quella che consiste nel far lavorare l’integrato come slave di un altro dispositivo il quale fornisce al TAS5001 i segnali di sincronizzazione necessari al riconoscimento dei dati e al funzionamento del modulatore.

38

Figura 2.6: Scheda audio

Il TAS5121 è un amplificatore digitale PWM fully differential a basso rumore in grado di erogare 100W su un carico da 4Ω con un rapporto

THD+N/P (Total Harmonic Distorsion+Noise/Power) inferiore al 10%.

Nel caso in esame, con una tensione di alimentazione pari a 12V e un carico previsto pari a 4Ω, l’amplificatore eroga una potenza pari circa a 12W. L’integrato prevede circuiti di protezione che garantiscono il funzionamento in modo sicuro dell’amplificatore stesso e della circuiteria a valle, proteggendo il sistema da sovracorrenti, sovratensioni o eccessivi surriscaldamenti. Il filtro di uscita per la ricostruzione della sinusoide è un filtro di Butterworth del secondo ordine, costituito da un’induttanza e da una capacità per ogni uscita differenziale. L’uscita del filtro è connessa ad un connettore LEMO il quale dovrà interfacciarsi all’altoparlante per la generazione della sinusoide. Per ulteriori dettagli sulla progettazione e realizzazione della scheda audio e sullo standard TDAA si rimanda alla bibliografia ([H]).

39

2.1.5 Power Supply Board

La Power Supply Board è una scheda in formato eurocard che fornisce, a partire dai 12V presenti sul back panel i 5V necessari alla Data

Processing Board e, tramite un convertitore DC/DC i livelli di tensione pari

a ±15V necessari per l’alimentazione del chipset IEEE1394 presente sulla scheda Orsys. L’intefacciamento tra la Power Supply Board e la Data

Processing Board è garantito dal connettore micro-line, di cui si darà la

descrizione in seguito.

Figura 2.7: Power Supply Board

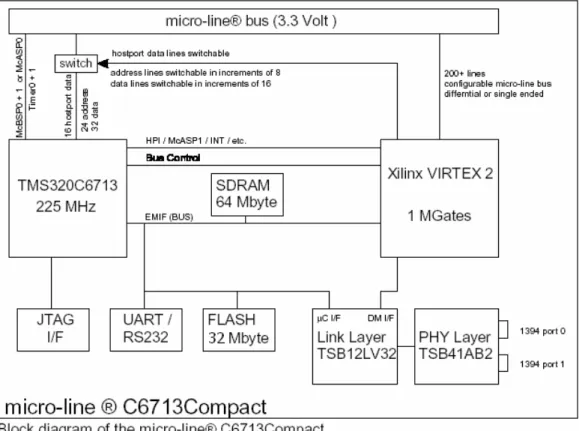

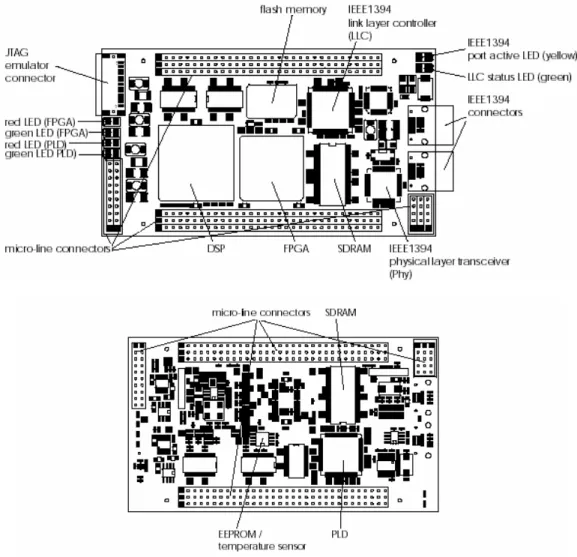

2.1.6 Data processing board Orsys CPT6713

Il cuore del sistema è rappresentato, come si è visto, proprio dalla data processing board la quale, opportunamente programmata, assolve a tutte le funzioni di data processing per le tre applicazioni chiave del progetto e si occupa del trasferimento dei risultati al PC remoto e della ricezione dei comandi tramite il link FireWire. La scheda scelta per compiere queste operazioni è la micro-line® C6713Compact prodotta da Orsys.

40

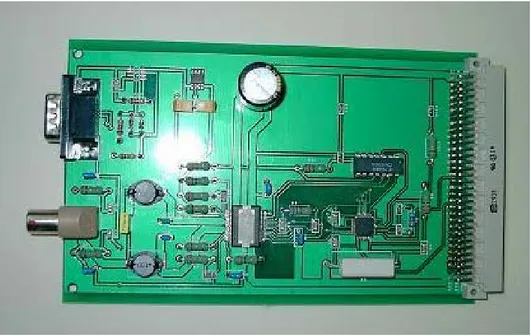

Figura 2.8: La Data Processing Board Orsys micro-line CPT6713.

La scheda è una board di elaborazione dati, basata su DSP (Digital Signal Processor), ad elevate prestazioni sulla quale sono montati i seguenti dispositivi di cui si darà una descrizione più dettagliata in seguito:

- Un DSP floating point Texas Instruments TMS320C6713

- Un FPGA (Field Programmable Gate Array) Xilinx Virtex-II XC2V1000

- Un PLD (Programmable Logic Device) sul quale sono implementati dei registri di configurazione della scheda.

- Chipset LLC (Link Layer Controller) e PHY (Physical Transceiver) per la gestione del trasferimento dati attraverso le due porte FireWire IEEE1394-1995.

- Chip UART TL16C550 per la gestione della comunicazione seriale secondo lo standard RS-232.

- 32 Mbyte di memoria EEPROM - 64 Mbyte di memoria SDRAM - Connettore JTAG

41 La scheda dispone inoltre di un particolare tipo di connettore, caratteristico delle schede prodotte da Orsys detto appunto micro-line, i cui pin permettono un accesso diretto alle risorse della scheda stessa. Tali connettori sono inoltre studiati in modo da consentire l’affiancamento di altre schede dotate dello stesso tipo di risorsa semplicemente impilandole l’una sopra l’altra. Nell’ambito del progetto SPADA questa caratteristica è sfruttata connettendo la Power Supply Board alla Data Processing Board proprio attraverso il connettore micro-line.

42

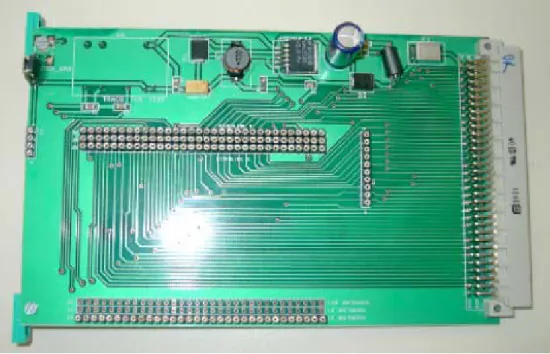

Figura 2.10: Viste top e bottom della Data Processing Board.

Incentreremo l’attenzione nei prossimi paragrafi sulla descrizione delle potenzialità della scheda e in particolare sulle caratteristiche dei due dispositivi principali, il DSP e il FPGA.

43

2.1.6.1 DSP Texas Instruments TMS320C6713

La rivoluzione operata da Texas Instruments nel mondo del data processing con l’introduzione del primo DSP basato su un architettura multi-issue iniziò nel 1996 con l’inserimento nel mercato del TMS320C62xx ed è stata poi seguita da altri produttori come Motorola, Analog Devices e Lucent Tecnologies. Il TMS320C62xx si presentò con caratteristiche di gran lunga superiori rispetto ai DSP prodotti fino ad allora. Rispetto alle architetture convenzionali una architettura multi-issue permette di eseguire più istruzioni in un unico ciclo di clock attraverso l’elaborazione da parte del processore di un’unica parola detta VLIW (Very Long Instruction Word) che codifica un certo numero di operazioni elementari. Le istruzioni elementari sono quindi codificabili in maniera più semplice e permettono quindi ai processori che adottano questo tipo di architettura di lavorare con frequenze di clock più alte nonché di essere estremamente “compiler friendly”. La VLIW è costituita da un numero di bit dipendente dalla complessità del processore stesso ovvero da quante unità funzionali dispone. Il concetto base è infatti quello di fare operare in parallelo più unità funzionali le quali quindi possono presentare i risultati delle elaborazioni contemporaneamente. Esistono altri tipi di architetture multi-issue come quelle basate sui superscalari, tuttavia le architetture basate su VLIW sono quelle che hanno riscontrato di gran lunga il maggior successo presso i costruttori per le loro maggiori prestazioni.

Il DSP TMS320C6713 è un DSP in virgola mobile che sfrutta proprio questo tipo di architettura con istruzioni codificate in VLIW a 256 bit e pertanto vanta come prestazioni la possibilità di eseguire fino a 8 istruzioni da 32 bit per ciclo ovvero, con una frequenza di clock pari a 225 MHz, è in grado di eseguire fino a 1800 MIPS (Mega Instructions Per Second) e 1350 MFLOPS (Mega FLoating point Operations Per Second). Il CPU core è costituito da due set di unità funzionali, ognuno dei quali comprende quattro unità (MAC, ALU, shifter e generatore di indirizzi) e un register file, costituito da 16 registri a 32 bit. E’ inoltre presente un gran

44 numero di periferiche che rendono il DSP molto più simile a un GPP (General Purpose Processor) piuttosto che a un processore dedicato alla sola elaborazione di segnali digitali. Diamo una rapida descrizione di queste periferiche, soffermandoci su quelle che hanno avuto particolare rilevanza nella progettazione del sistema nell’ambito del progetto SPADA.

Figura 2.11: Diagramma a blocchi del processore TMS320C6713.

Generatore di clock (PLL)

I segnali di sincronizzazione utilizzati dalle periferiche hanno frequenze diverse impostabili dal programmatore scrivendo negli appositi registri di configurazione del processore. Ciò è reso possibile grazie alla presenza di un apposito circuito costituito da alcuni divisori di frequenza e da un PLL (Phase Locked Loop) dal quale è possibile ottenere le frequenze desiderate per le periferiche.

45

Figura 2.12: Diagramma a blocchi del generatore di clock interno al DSP TMS320C6713.

Multi-channel Audio Serial Ports (McASP)

Le periferiche McASP sono due porte seriali dedicate alla trasmissione e alla ricezione di segnali audio digitali in vari formati. Esse sono contraddistinte dalle sigle McASP0 e McASP1. Nell’ambito della scheda Orsys i pin della McASP0 sono connessi al bus micro-line, tranne che per la linea AMUTEIN0, connessa all’FPGA. McASP1 è invece connessa al solo FPGA. Vale la pena soffermarsi maggiormente sulle caratteristiche di questa periferica quali l’architettura interna e i vari formati audio supportati in quanto risulterà utile nella comprensione della descrizione dell’applicazione sviluppata per il DSP.

46

Figura 2.13: Diagramma a blocchi della periferica audio McASP. In verde è evidenziata la sezione di trasmissione, in rosso quella di ricezione ed in blu i blocchi condivisi.

Si nota la presenza di due sezioni, una dedicata alla trasmissione dei dati e l’altra alla ricezione. Ogni sezione è costituita da:

• Una macchina a stati che controlla le interazioni tra le varie unità della rispettiva sezione, segnala le eventuali situazioni di errore in un apposito registro e determina lo stato della porta seriale.

• Un generatore dei segnali di clock e di sincronizzazione. • Un’ unità di formattazione dei dati.

• Un sequenziatore per il formato TDM (discusso in seguito).

Le unità suddette sono duplicate per ogni sezione. Vi sono inoltre delle risorse condivise dalle due sezioni:

47 • Una batteria di serializzatori i quali per mettono la trasmissione seriale

del contenuto dei registri buffer di uscita o la ricezione dei dati seriali con la conseguente immissione nei buffer d’ingresso.

• Un circuito per il controllo delle condizioni di errore nella generazione dei segnali di clock.

• La logica necessaria a impostare la corretta funzionalità dei pin come specificato nel registro PFUNC.

Le due sezioni sono indipendenti per quanto riguarda il formato dei dati di cui gestiscono il trasferimento e i segnali di sincronizzazione necessari al trasferimento stesso, tuttavia è da notare che, poiché i serializzatori condividono la stessa unità di formattazione dati, non è possibile utilizzare formati differenti in una stessa sezione. Ad esempio se un serializzatore è configurato per trasmettere nel formato IIS, tutti gli altri serializzatori configurati per la trasmissione devono trasmettere nello stesso formato, mentre i serializzatori configurati per la ricezione di dati possono supportare un formato differente.

Ogni pin può essere configurato come “McASP pin” o come “GPIO (General Purpose Input Output) pin” e in entrambi i casi come pin di ingresso o uscita semplicemente scrivendo negli appositi registri. Nel secondo caso i pin possono assolvere funzioni non strettamente correlate con la trasmissione di una stringa di dati audio e il loro valore dipende da quanto specificato direttamente dal programmatore.

Diamo una descrizione della funzione dei pin nel caso in cui vengano configurati come McASP pin (m : [0,1], n : [0..7]):

• AXRm[n] : hanno la funzione della vera e propria trasmissione/ricezione dei dati audio.

48 • AFSRm : “Frame Sync Receive” pin dedicato al segnale di

sincronizzazione dei frame in ricezione. Determina il sample rate in ingresso.

• AFSXm : pin dedicato al segnale di sincronizzazione dei frame in trasmissione. Determina il sample rate ovvero la frequenza dei campioni in uscita.

• ACLKRm : pin dedicato al bit clock in ricezione. La durata di un periodo di questo segnale coincide con la distanza temporale tra due bit successivi nella stringa ricevuta.

• ACLKXm : pin dedicato al bit clock in trasmissione. La durata di un periodo di questo segnale coincide con la distanza temporale tra due bit successivi nella stringa trasmessa.

• AHCLKRm : pin dedicato al clock ad alta frequenza ricevuto. Con tale segnale vengono campionati i bit costituenti la stringa ricevuta. • AHCLKXm : pin dedicato al clock ad alta frequenza trasmesso.

Tale segnale può essere usato come clock di sistema per un dispositivo a valle.

La periferica è in grado di supportare la ricezione e la trasmissione di dati audio in diversi formati. Alcuni di essi sono ridondanti rispetto alle richieste del sistema, tuttavia di seguito si dà una breve descrizione di ognuno di essi.

• I2S o IIS (Inter Integrated Sound) : E’ un formato largamente utilizzato per applicazioni audio digitali. Esso è un caso particolare del formato TDM, discusso in seguito. E’ studiato principalmente per trasmettere segnali stereo. I campioni destro e sinistro sono costituiti ognuno da una stringa di bit trasmessa su uno dei piedini AXRm[n] e ogni coppia di campioni costituisce un “frame”. I singoli bit verranno campionati dal dispositivo a valle tramite il segnale ACLKXm e un frame è distinto dal successivo grazie al segnale AFSXm.

49

Figura 2.14: Schematizzazione del formato IIS (Inter Integrated Sound)

• TDM (Time Division Multiplexed format) : Tale formato viene usato tipicamente quando i dati vengono trasmessi da un dispositivo ad un altro sulla stessa scheda o su schede diverse ma dotate dello stesso hardware. Il metodo di trasmissione dei dati è molto simile al formato IIS, tuttavia il frame è in questo caso composto da più di due campioni in modo da generare segnali audio su più di due canali completamente indipendenti tra loro. I campioni sono chiamati “time slots” e ogni bit costituente un time slot è sincrono con il clock di trasmissione ACLKXm. Non c’è ritardo tra un time slot e il successivo, la trasmissione dell’ultimo bit di un time slot è immediatamente seguita dalla trasmissione del primo bit del time slot successivo. Tuttavia si può ritardare di uno o due cicli il segnale AFSXm che assolve sempre alla funzione di distinguere un frame dal successivo.

50 • S/PDIF, IEC60958-1, AES3 : Questi formati utilizzano un’unica

linea di trasmissione per i dati da trasmettere, sfruttando una codifica denominata Biphase Mark Code (BMC). La codifica BMC consente di trasmettere l’informazione sul clock seriale ACLKXm, sui campioni da trasmettere e sul segnale di sincronismo dei frame AFSXm, sull’unica linea AXRm[n]. Nell’intervallo temporale in cui si trasmette un bit di dati utili, viene trasmessa una coppia di valori logici denominata “cella”: 00 o 11 rappresentano l’1 logico, 01 o 10 lo 0. Inoltre il primo livello logico di una cella è l’inverso dell’ultimo livello logico della cella precedente. Il clock seriale ACLKXm ha un periodo pari all’intervallo di trasmissione di un bit utile ed è in un rapporto costante con il periodo del segnale di sincronizzazione dei frame AFSXm tale che fACLKXm = 128*fAFSXm. In

questo modo il dispositivo che riceve il segnale in codifica BMC riesce a ricavare tutte le informazioni necessarie alla ricostruzione del segnale utile.

Figura 2.16: Esempio di formato S/PDIF.

I formati di codifica audio sopra riportati possono essere modificati dal programmatore con varie opzioni che possono influenzare le frequenze dei segnali di uscita, il numero di bit costituenti i campioni, il numero di campioni costituenti un frame in modo da rendere adatto alle varie esigenze l’utilizzo della periferica. Nell’applicazione in esame

51 l’utilizzo di una codifica di tipo IIS è più che sufficiente a soddisfare le esigenze del sistema in quanto il segnale da generare è un semplice tono. External Memory Interface (EMIF)

La EMIF è l’interfaccia tra il processore e il mondo esterno. Gestisce quindi tutte le transizioni di dati tra il processore stesso e i dispositivi che si interfacciano con esso. Nel caso della Data Processing Board la EMIF gestisce le richieste di accesso al bus dati da parte del controllore EDMA (di cui si parlerà in seguito), gli accessi diretti del processore alla memoria esterna (SDRAM e EEPROM), ai registri dell’FPGA e delle altre periferiche esterne (UART, LLC e PLD). Lo spazio di indirizzamento logico del DSP è caratterizzato da una larghezza del bus indirizzi pari a 32 bit. La variazione del bit meno significativo di un indirizzo comporta l’indirizzamento del byte successivo nello spazio di memoria. Esternamente al processore lo spazio di indirizzamento è organizzato in quattro sottospazi selezionabili tramite i bit /CE0, /CE1, /CE2, /CE3 (Chip Enable). Ciascuno di questi segnali, attivi bassi, corrisponde ad una diversa configurazione dei primi quattro bit del bus indirizzi a 32 bit e seleziona uno spazio di memoria esterno in cui può essere montata una periferica indirizzabile con i 20 bit meno significativi degli indirizzi.

La scheda è inoltre progettata in modo tale che, tramite la EMIF, il processore possa accedere anche al connettore micro-line attraverso dei buffer bidirezionali comandati dall’FPGA. A tal fine è ovviamente necessario un design dedicato del FPGA stesso.

Inter-Integrated Circuit (I2C) Interface

Si tratta di interfacce per la comunicazione seriale di dati tra circuiti integrati presenti sulla stessa scheda. Le interfacce I2C del DSP sono due:

esse possono essere usate per accedere a integrati quali il sensore di temperatura, memoria Flash, convertitori D/A e A/D. Sulla scheda è

52 tuttavia disponibile una sola delle due interfacce I2C poiché l’altra è

dedicata al GPIO.

General Purpose Input/Output Peripheral (GPIO)

Esistono dei pin che possono essere liberamente configurati dal programmatore come ingressi o uscite generiche per il processore e utilizzati per diversi scopi. Per come è montato il processore sulla scheda tuttavia l’utilizzo di questa risorsa è sconsigliato da Orsys non essendovi collegamento con il connettore micro-line. E’ necessario lasciare lo stato di questi pin nello stato di default previsto da Texas Instruments.

Multi-Channel Buffered Serial Ports (McBSP)

Le periferiche McBSP sono presenti su tutti i DSP Texas Instruments appartenenti alle famiglie TMS320C2x ‘C3x, ‘C5x e ‘C6x. Sono periferiche per la trasmissione seriale sincrona di dati e sono configurabili dal programmatore in modo da essere compatibili con un gran numero di standard di comunicazione seriale. La velocità di trasmissione può raggiungere i 75Mbps e la comunicazione può avvenire in full duplex. Sul processore TMS320C6713 esistono due interfacce McBSP tuttavia a causa della condivisione tra i pin della McASP0 e i pin di entrambe le McBSP nessuna delle due è stata utilizzata durante la progettazione del sistema vista la necessità di utilizzare la McASP.

Timers

Sono implementati due timer indipendenti, a 32 bit. Ognuno di essi ha un pin di ingresso ed uno di uscita. Per maggiore versatilità d’utilizzo essi possono ricevere il clock da una sorgente esterna o da quella interna.

53 Host Port Interface (HPI)

Si tratta di una porta parallela con la quale un processore host può accedere direttamente allo sazio di memoria del DSP. Può quindi essere utile in sistemi in cui il DSP opera come slave in un sistema più complesso. Nel caso in esame tuttavia il DSP è master dell’intero sistema, pertanto la HPI non è stata presa in considerazione nello sviluppo del progetto. Inoltre la stessa Orsys sconsiglia l’utilizzo di tale periferica in quanto non direttamente collegata al connettore micro-line.

Controllore di interrupt

Il controllore di interrupt presente sul TMS320C6713 è dotato di 16 linee di interrupt a priorità decrescente a partire dalla linea INT00, dedicata al reset, alla linea INT15 a priorità minima. Esiste la possibilità di assegnare ad ogni linea di interrupt una sorgente diversa scrivendo negli appositi campi dei registri selettori di interrupt MUXH e MUXL, in accordo alla tabella del selettore di interrupt.

54 Controllore EDMA (Enhanced Direct Memory Access)

Il meccanismo di trasferimento dati tramite DMA è stato pesantemente utilizzato nello sviluppo del sistema in quanto le stesse specifiche di progetto presuppongono un trasferimento di dati continuo, operazione che si presta perfettamente all’utilizzo questo tipo di risorsa la quale permette di svolgere trasferimenti di dati completamente in

background ovvero senza l’esplicito intervento della CPU. Si sofferma

quindi l’attenzione su quali siano le potenzialità di tale meccanismo nel caso in esame e su come possano essere sfruttate.

Figura 2.18: Diagramma a blocchi del controllore EDMA

A differenza dei controllori DMA presenti nelle famiglie di DSP C620x e C670x , basati su architettura register based, il controllore EDMA implementato sul TMS320C6713 è caratterizzato dal fatto che i parametri dei descrittori dei vari canali sono impostabili in una porzione di memoria pari a 2 Kb dedicata al controllore stesso e nominata nella documentazione del processore “PaRAM” (Parametric RAM). La “PaRAM” è organizzata in blocchi da 24 byte ciascuno, per un totale di 2040/24 = 85 blocchi più altri 8 byte usati come “scratch pad area”. 16 di questi blocchi sono utilizzati per

55 impostare i parametri di ognuno dei 16 canali del controllore mentre i restanti 69 vengono usati per ricaricare i parametri al termine di un trasferimento dati. Ognuno dei canali è caratterizzato da un evento di sincronizzazione hardware corrispondente cioè alla transizione logica di uno specifico segnale proveniente da una periferica oppure può essere configurato nel descrittore per essere sincronizzato via software. L’evento di sincronizzazione determina l’inizio del trasferimento dei dati tra due qualsiasi locazioni dello spazio di indirizzamento del processore. Ogni descrittore è dotato di numerosi parametri che rendono estremamente flessibile la configurazione del trasferimento. Di seguito si riporta la struttura di un generico descrittore. Per dettagli sul significato dei vari parametri e su come vadano impostati si rimanda alla bibliografia ([32] e [33]).

Un altro meccanismo di trasferimento possibile sul TMS320C6713 è quello denominato QDMA (Quick DMA). Esso è caratterizzato dal fatto che il trasferimento viene fatto partire nel momento stesso in cui si completa la configurazione dell’ultimo parametro del descrittore.

Per ulteriori dettagli sul processore TMS320C6713 e sulle sue periferiche si rimanda alla bibliografia ([D]).

Si passa ora alla descrizione delle caratteristiche principali dell’altro dispositivo principe montato sulla Data Processing Board, l’ FPGA Xilinx Virtex-II XC2V1000.

2.1.6.2 FPGA Xilinx Virtex-II XC2V1000

Il FPGA Xilinx Virtex-II XC2V1000 appartiene alla famiglia Virtex-II la quale comprende dispositivi con capacità fino a 8 Mgate. Il XC2V1000 è un FPGA SRAM-based con una capacità pari a 1 Mgate, realizzato con processo 8-layer CMOS a 0.12 µm e si pone, nel panorama dei dispositivi a logica programmabile, come valida soluzione a problemi di velocità, potenza dissipata e costi.

56

Figura 2.19: Blocchi logici all’interno del FPGA Xilinx Virtex-II XC2V1000.

Gli elementi di logica programmabile presenti nel dispositivo sono suddivisi in quattro categorie:

• CLB (Configurable Logic Block). Rappresentano il cuore della logica programmabile del dispositivo in quanto comprendono 4

slices, le unità logiche elementari del CLB con le quali è possibile

realizzare funzionalità combinatorie o sequenziali. L’XC2V1000 dispone di 1280 CLB per un totale di 5120 slices.

• IOB (Input Output Block). Sono i blocchi logici dedicati alla connessione del dispositivo con il mondo esterno. E’ possibile configurare questi blocchi in modo da rispettare i livelli elettrici di diverse famiglie logiche, dalla TTL (3.3V, 2.5V, 1.8V, 1.5V) alla CMOS fino agli standard AGP2X, PCI e altri. E’ possibile inoltre impostare, per ogni pad di I/O, lo slew rate e la corrente erogata. Gli IOB sono a loro volta organizzati in 8 banchi gerarchicamente superiori, ognuno dei quali comprende 54 IOB, per un totale di 432 pad di I/O. Funzionalità interessante presente nelle architetture Virtex-II è la possibilità di controllare l’impedenza d’ingresso dei pad utilizzando il cosiddetto DCI (Digitally Controlled Impedence). Tale caratteristica permette al progettista di limitare fortemente i

57 disturbi sui segnali dovuti alle riflessioni che avvengono sulle interconnessioni tra l’FPGA e altri dispositivi in presenza di segnali a frequenza sufficientemente alte da causare un comportamento come linea di trasmissione delle interconnessioni stesse in quanto l’utilizzo del DCI permette al progettista di adattare l’impedenza di ingresso del FPGA a quella caratteristica della linea.

• DCM (Digital Clock Manager). Questi blocchi permettono di controllare e gestire i segnali di sincronizzazione in modo da minimizzare il ritardo di distribuzione ai vari CLB programmati con funzionalità sequenziale. L’XC2V1000 dispone di 8 DCM posti in posizioni ottimali al fine di distribuire i segnali di sincronizzazione nel modo migliore.

• SelectRAM Block. E’ presente una certa quantità di RAM interna organizzata in blocchi e configurabile in vari modi sia per quanto riguarda la modalità di indirizzamento che per quanto riguarda le temporizzazioni di accesso. L’XC2V1000 dispone di 40 blocchi da 18Kbit per un totale di 720Kbit.

I vari blocchi logici sono interconnessi tra loro attraverso una soluzione gerarchica delle interconnessioni. Esistono cioè connessioni in qualità variabile a seconda della lunghezza del percorso da compiere. Tutti i blocchi sono collegati a delle matrici programmabili dette switch

matrix le quali provvedono a distribuire i segnali sulla linea che consente

le prestazioni migliori in termini di ritardo di propagazione e fanout. Per approfondimenti sulla struttura interna degli FPGA della famiglia Virtex-II si rimanda alla bibliografia ([E]).

58

Figura 2.20: Interconnessioni tramite switch matrix tra i blocchi logici

Nella tabella seguente è mostrata la gerarchia delle interconnessioni programmabili possibili presenti nella famiglia Virtex-II. I quadrati rappresentano il blocco logico generico, in quanto tutti i blocchi possono accedere allo stesso tipo di risorsa di routing attraverso le switch matrix.

59

2.1.6.3 Interfacciamento

Nel contesto della scheda Orsys il FPGA è montato in modo tale da avere a disposizione sul connettore micro-line gran parte dei pin del dispositivo. Per quanto riguarda l’interfacciamento tra DSP e FPGA esso avviene ovviamente via EMIF per quanto riguarda dati ed indirizzi ed è possibile impostare, agendo sui registri di configurazione della scheda presenti sul PLD quale tra DSP e FPGA sia il busmaster. Configurare il FPGA come busmaster comporta ovviamente l’implementazione nell’architettura FPGA di una logica per l’arbitraggio del bus.

Esistono altre linee di connessione tra FPGA e DSP: vi sono infatti 26 linee di connessione con la HPI, 5 linee con il controllore di interrupt e 2 con il generatore di clock.

Figura 2.21: Linee di interconnessione tra i vari dispositivi della Data Processing Board.

60 Come si vede in figura 2.21 sono inoltre montati sulla scheda dei driver bidirezionali il cui stato è definito da 9 linee connesse al FPGA e che permettono di connettere o meno i pin della HPI, del bus dati e del bus indirizzi del DSP al connettore micro-line attraverso un design dedicato. Il FPGA è inoltre connesso a due led, uno verde e uno rosso utili in fase di debug o per indicare un particolare stato del sistema.

Delle 5 linee di interrupt sono in realtà direttamente filate al DSP solo tre. Le rimanenti due possono essere connesse al DSP agendo su degli appositi registri del PLD, azione che però va a scapito di altre risorse della scheda, come il controllore UART e il LLC i quali perdono la facoltà di interrompere la CPU, come si vede in figura 2.22. Ulteriori informazioni riguardo alla Data Proccessing Board sono reperibili in bibliografia ([C] e [F]).

source DSP interrupt line

LLC interrupt EXT_INT6

LLC STAT0 line EXT_INT7

UART interrupts EXT_INT7

Flash memory ready condition EXT_INT7 FPGA I/O power fail condition EXT_INT7

FPGA EXT_INT6, EXT_INT7

Figura 2.22: Connettività programmabile sulla scheda Orsys dei segnali di interrupt attraverso il PLD.

61

2.1.7 Back Panel

Il Back Panel garantisce la distribuzione dell’alimentazione alle varie schede nonchè la trasmissione dei segnali provenienti dalla Detection

Board, attraverso le schede ricevitori, alla Data Processing Board. Su di esso

viaggiano inoltre i segnali relativi alla porta seriale, alla scheda audio e alla scheda GPIO, tutti connessi alla Data Processing Board.

Per ulteriori dettagli sui dispositivi utilizzati nella realizzazione delle schede ausiliarie si faccia riferimento alla bibliografia ([H]).

Figura 2.23: Back Panel

Si dà ora una rapida descrizione dell’ambiente di sviluppo software che è stato utilizzato nell’ambito del progetto SPADA.

62

2.2 Piattaforma di sviluppo software

Gli strumenti software necessari alla progettazione del sistema sono stati utilizzati per:

• lo sviluppo del firmware del DSP tramite il tool “Code Composer

Studio” distribuito da Texas Instruments.

• la descrizione dell’hardware implementato sull’FPGA in linguaggio VHDL (Very high speed integrated circuits Hardware Description Language) sfruttando il tool “Xilinx ISE 5.1”, fornito da Xilinx, e il software “ActiveHDL” distribuito da Aldec Inc. per eseguire le simulazioni timing.

• realizzare l’interfaccia grafica delle tre applicazioni tramite il software di strumentazione virtuale “LabView”, sviluppato da National Instruments.

Per compiere il debug del firmware e per l’upload dello stesso sulla scheda si è scelto di utilizzare l’emulatore JTAG (Join Test Action Group) XDS510PP di Spectrum Digital Inc.

2.2.1 Code Composer Studio v2

Code Composer Studio (CCS) è un software IDE (Integrated Design Environment) sviluppato da Texas Instruments specificatamente per i programmatori di DSP prodotti dalla compagnia texana. Il tool fornisce diverse funzionalità atte a facilitare il più possibile la stesura e l’ottimizzazione del codice. E’ possibile utilizzare il software sia con la presenza fisica del dispositivo che senza di essa, impostando il programma in modo da funzionare come emulatore o come simulatore di un particolare processore. La scrittura del codice può avvenire sia in linguaggio C che in linguaggio assembly di più basso livello, con la possibilità di visualizzare il codice in modalità mista, ossia istruzioni C seguite dalla loro traduzione in assembly eseguita dal compilatore. Per

63 ogni specifico modello di DSP esistono inoltre le cosiddette CSL (Chip Support Library) tramite le quali il programmatore può facilmente accedere ai vari registri della CPU e delle periferiche attraverso dei nomi simbolici, corrispondenti a quelli riportati nella documentazione del processore senza dover ridefinire delle macro nei file di intestazione. Utilizzando le funzionalità del DSP/BIOS, presente in tutte le versioni del prodotto, è inoltre possibile sfruttare, tamite un’interfaccia grafica e quindi di facile utilizzo, le API (Application Programmers Interface) per la gestione delle periferiche del DSP definite sempre nelle CSL. Durante l’esecuzione del programma è inoltre possibile monitorare il contenuto dell’intero spazio di memoria del DSP e il valore degli oggetti dichiarati utilizzando le watch window oppure associando a un grafico un qualunque indirizzo dello spazio di memoria a partire dal quale verranno visualizzati i contenuti delle locazioni in successione. Altra funzionalità interessante di CCS è la possibilità di valutare il peso sulle risorse, in termini di cicli di clock, di una qualunque porzione di codice in fase di esecuzione tramite l’uso del profiler. Per maggiori dettagli sull’utilizzo di Code Composer Studio si rimanda alla bibliografia [28,29 e 31].

64

2.2.2 Xilinx ISE 5.1

ISE 5.1 è un pacchetto di software EDA (Electronic Design Automation) sviluppato da Xilinx per ottimizzare l’implementazione di architetture digitali sui dispositivi programmabili da essa prodotti. Il pacchetto comprende diversi tool atti a rendere la programmazione dei dispositivi il più personalizzabile possibile, consentendo al progettista di agire in modo completo sulla definizione delle connettività del dispositivo. E’ infatti possibile ad esempio tramite l’FPGA editor visualizzare, in seguito alla fase di place and route, come l’architettura descritta in un certo progetto verrà implementata sul dispositivo e introdurre modifiche alle interconnessioni in maniera grafica. Nelle figure successive è mostrato ad esempio come sia possibile, tramite l’FPGA editor, semplicemente trascinando il mouse, decidere su quale slice verrà implementata la logica relativa ad un bit di un contatore (COUNT<7>). A sinistra si notano le interconnessioni con la switch matrix e a destra, in viola, sono evidenziate le long lines che attraversano il dispositivo in tutta la sua lunghezza.

65

Figura 2.24: Utilizzo dell’FPGA editor per personalizzare la mappatura del dispositivo

Esiste anche una modalità testuale per indicare al tool di sintesi i vincoli che devono essere rispettati nella mappatura del dispositivo. Ciò avviene nel cosiddetto constraint file. Si tratta di un file in formato .ucf in cui vengono specificati dei vincoli associando ai nomi simbolici dei pin definiti nella descrizione dell’architettura, la desiderata localizzazione sul pinout del dispositivo. Nel constraint file è inoltre possibile indicare lo slew-rate desiderato per i pad configurati come pad di uscita, di quale

66 famiglia logica il pad debba generare e riconoscere i livelli elettrici e il drive del pad, ossia la corrente erogata sul piedino.

ISE offre inoltre la possibilità di fornire indicazioni circa la potenza che verrà dissipata dall’FPGA una volta che l’architettura verrà implementata sul dispositivo. Il tool che assolve a questa funzione, ovviamente eseguibile solo una volta che è stato completato il processo di place and route, si chiama XPower e fornisce un resoconto detagliato della potenza assorbita dall’FPGA, stilando una classifica dei segnali più “power

hungry” ovvero cui corrispondono connessioni sulle quali si dissipa la

maggior potenza.

Il file finale di programmazione del dispositivo può essere generato in diversi formati. Oltre al normale formato binario .bit per la configurazione diretta dell’FPGA è infatti possibile generare un file di programmazione in formato .rbt dal quale utilizzando tool di terze parti come il bintohex fornito da Orsys si può ottenere un file sorgente in linguaggio C. Ciò ha reso possibile, nell’ambito del progetto SPADA, aggiungere tale file al progetto creato con CCS inserendo così nel firmware anche l’architettura dell’FPGA.

Come ultima nota su Xilinx ISE inseriamo, seppur scontata, la caratteristica di generare un file sorgente in formato .vhd che fornisce un modello post place and route dettagliato per poter compiere simulazioni timing del sistema.

67

2.2.3 National Instruments LabView

LabView è un ambiente di sviluppo software per la creazione dei cosiddetti strumenti virtuali, ovvero di pannelli di controllo e indicazione i quali, comunicando con una strumentazione di misura esterna connessa al PC, consentono di impostare parametri di misura e di visualizzare i risultati. E’ basato su un particolare tipo di linguaggio di programmazione, denominato G. Un programma scritto in linguaggio G è detto VI (Virtual Instrument). Mentre la maggior parte dei linguaggi di programmazione sono text-based ovvero si basano su una stesura testuale del codice, LabView adotta un approccio di tipo grafico associando ad ogni funzione, a partire dagli operatori aritmetici elementari fino a sottoprogrammi detti subVI, un blocchetto con ingressi e uscite corrispondenti rispettivamente all’argomento e al risultato restituito dalla funzione. Anche le VI sono caratterizzate da ingressi e uscite, denominati rispettivamente “controls” e “indicators”. Ogni VI è caratterizzata da due visuali, dette “front panel” e “block diagram”. Il front panel è la vera e propria interfaccia grafica con la quale l’utente andrà a impostare i parametri di misura tramite i controlli e a visualizzare i risultati tramite gli indicatori. Il block diagram rappresenta ciò che sta dietro l’interfaccia ossia il vero e proprio codice scritto in linguaggio G.

E’ possibile gestire tramite LabView i principali protocolli di comunicazione, con i quali il software riceve o trasmette i dati da e verso il mondo esterno, come il protocollo RS-232, il VXI, il TCP/IP (Transmission Control Protocol/Internet Protocol) o il protocollo UDP (User Datagram Protocol). Non esistono purtroppo VI di libreria per la gestione del protocollo di comunicazione IEEE1394. Nell’ambito del progetto SPADA tale mancanza ha contribuito alla ricerca di soluzioni alternative al trasferimento dei dati via FireWire dalla detection board al PC remoto, come si mostrerà nei prossimi capitoli.