49

CAPITOLO 4

Strutture realizzate

4.1 Introduzione

Dopo che il chip verrà realizzato in fonderia, le prime misure consisteranno nel caratterizzare il comportamento ottico dei singoli transistor della tecnologia AMS 0.35 µm. Dapprima sono dunque stati disegnati dispositivi nmos e pmos e, poi, strutture più complesse, al fine di testare tutti i tipi di misure possibili con tale strumento. Si tratta, quindi, di circuiti sia analogici, come fet ed un amplificatore operazionale, che digitali, come i ring oscillator, ma anche di tipo mixed signal.

4.2 Singoli mosfet

4.2.1 MOS standard

E’ stato disegnato il layout di transistor sia nMOS che pMOS con larghezza di canale fissata a 10 µm, in modo da renderli facilmente visibili alla CCD, e con lunghezze crescenti a partire da quella minima: 0.3 , 0.35 , 0.4 , 0.5 , 0.6 µm. . I fet, sia di tipo n che di tipo p, sono stati connessi con gate a comune e source a comune, mentre i drain sono stati lasciati separati al fine di ridurre il numero di pad esterni e di poter avere un controllo sui singoli dispositivi.

Per dimensionare correttamente le larghezze delle piste di drain e source, sono state fatte tracciare al simulatore SPECTRE alcune caratteristiche dei transistor, in modo da ricavare i seguenti valori di corrente per tensioni di polarizzazione massime, cioè VDS =VGS =3.3V .

Lunghezza canale max

DS I 0.3 µm 5.47 mA 0.35 µm 5.03 mA 0.4 µm 4.69 mA 0.5 µm 4.15 mA 0.6 µm 3.75 mA

Dalla conoscenza della densità di corrente portata dalle metal impiegate, è stata fissata la larghezza delle piste connesse ai terminali di source e drain in modo da permettere l’accensione di un mos soltanto alla volta, o di tutti contemporaneamente.

Le misure consisteranno nel polarizzare i mos con tensioni VGS,V variabili nel DS

range 0 V - 3.3 V, e, dall’osservazione con la camera CCD, verrà ricavata la caratteristica ottica completa in DC, ovvero l’andamento dell’intensità luminosa in funzione di tali tensioni. Tali misure saranno poi ripetute al variare della lunghezza di canale. I risultati che si otterranno a Milano dovranno dare degli andamenti simili a quelli delle figure seguenti, ricavati per altre tecnologie. In

figura 4.1 si osserva come l’emissione ottica varia con VGS e VDS per lunghezze di canale di 0.45 e 0.9 µm; al variare della lunghezza di canale, poi, tali curve dovrebbero spostarsi secondo gli andamenti di figura 4.2.

Figura 4.1: dipendenza dell’emissione ottica dalle condizioni di polarizzazione nel caso di due

nMOS con L= 0.45 µm e L=0.9 µm.

Figura 4.2: andamento della luminescenza al variare della VGS e per lunghezze di canale crescenti

da 0.2 fino a 1 µm.

I contatti di bulk sono stati posizionati il più vicino possibile ai mos di test, messi a comune e portati ad un pad esterno per poter misurare la corrente di substrato, con l’intenzione di dimostrare come questa sia in stretta relazione con l’emissione fotonica. Questo perché i portatori caldi possono compiere transizioni intrabanda, ma anche ionizzazioni da impatto, generando correnti di substrato dell’ordine del nA. Dal pad di source verrà letta a sua volta la corrente I , in modo da metterla in S

relazione col numero di fotoni emessi secondo l’equazione (1.3), discussa nel capitolo 1.

La caratterizzazione verrà effettuate sia sugli nMOS che sui pMOS; l’intensità ottica sarà poi normalizzata per µm di larghezza di canale e per unità di tempo, in modo da poter essere confrontata facilmente con quanto ricavato da altre tecnologie. Si dovrà ottenere qualcosa che segue il trend di figura 4.3, riferita a due tecnologie da 0.2 e 0.55 µm. Osservando tale grafico, si nota come gli andamenti per la seconda tecnologia abbiano una pendenza minore e tendano ad abbassarsi. Questo avviene perché, se la riduzione della tensione di alimentazione (applicata alla VGS) fa diminuire l’emissione, la contemporanea riduzione della lunghezza di canale tende ad aumentare l’emissione stessa. Nel caso specifico della tecnologia a 0.35 µm, in riferimento sempre a tale figura, si dovrà ottenere qualcosa di intermedio. I layout di questi transistor sono riportati nelle tavole finali.

Figura 4.3: trend dell’emissione fotonica al progredire delle tecnologie.

4.2.2 MOS “a gradino”

Per tutti i transistor, i contatti di drain, di source e le metal corrispondenti sono stati posizionati alla distanza minima dal gate che la tecnologia consente. Si è pensato anche di andare a vedere come varia l’emissione se si lascia scoperta una superficie maggiore di canale dalla parte del drain, regione in cui il fenomeno avviene. A questo scopo è stato disegnato un singolo nMOS con gate lungo 0.3

µm e largo 25 µm, dove la metal di drain ha una forma a gradino con distanza dal poly del gate che varia ogni 5 µm con i seguenti valori: 0.3 , 0.4 , 0.5 , 0.7 , 0.9 µm. Anche qui, è stato necessario portare fuori indipendentemente il contatto di substrato per poterne misurare la corrente. Verranno effettuate delle misure quantitative dell’emissione per mezzo della camera CCD. In figura 4.4 è riportato un disegno semplificato di tale struttura, il layout effettivo è osservabile nelle tavole finali.

4.3 Ring Oscillator

Queste prime semplici strutture ci consentono, quindi, di ottenere informazioni di tipo analogico. L’intensità della luminescenza dipende, infatti, dalle condizioni operative dei transistor, per cui, una volta modellizzato il comportamento di questi, da una semplice osservazione sarà possibile risalire ai valori di tensione e corrente in condizioni statiche.

Se, invece, si compiono misure con la tecnica del Time-Correlated Photon-Counting (TCPC), con la quale si vanno a rivelare fotoni mediante lo SPAD, se ne calcola l’istante di arrivo e si rappresenta l’istogramma della distribuzione della luminescenza nel tempo, si otterranno informazioni di tipo digitale.

La struttura ideale per compiere misure di timing è il ring oscillator: si tratta di un oscillatore costituito da una catena di inverter chiusa ad anello con una nand, alla quale giunge un segnale di abilitazione (enable) esterno per poter arrestare o avviare l’oscillazione. Il vantaggio di questo schema sta nel fatto che non c’è bisogno di ciclicizzare un segnale di sollecitazione esterno.

Sono stati progettati due ring a frequenze diverse, uno a 200 MHz e l’altro a 700 MHz; per ottenere tali specifiche bisogna andare a mettere in cascata un numero adeguato di porte, a seconda del ritardo porta-porta. I tempi di commutazione ed i valori dei ritardi dipendono dalle dimensioni dei transistor delle singole porte, per cui il punto di partenza è stato quello di dimensionare l’nMOS ed il pMOS del singolo inverter a seconda degli obiettivi proposti.

4.3.1 Dimensionamento di un singolo inverter

Quando si rappresentano le misure effettuate con lo SPAD come forma d’onda ottica, la larghezza FWHM di un certo “impulso ottico” mi darà informazioni riguardo al tempo di commutazione. Se stiamo osservando un nMOS, tale valore temporale sarà relativo ad una transizione high-low, se, invece, si punta lo SPAD su un pMOS, otterremo informazioni riguardo alla transizione low-high. L’obiettivo è stato quello di raggiungere tempi di commutazione più brevi

possibile, compatibilmente con quanto la tecnologia permette, in modo da ridurre la larghezza degli impulsi.

Solitamente, a causa della diversa mobilità dei portatori, si realizzano i due tipi di transistor con larghezze che stanno in rapporto di circa 2-3; dai parametri di processo forniti dalla AMS si ricavano i valori delle mobilità, 370 cm2/V s⋅ per

gli elettroni e 126 cm2/V s⋅ per le lacune, che danno un rapporto di circa 2,9. Per

esaminare come variano i tempi di commutazione ed i ritardi porta-porta in funzione della larghezza del nMOS e del rapporto Wp/Wn, sono state fatte delle simulazioni parametriche su di un anello con numero fittizio di inverter.

La larghezza Wn è stata fatta variare tra 10 µm e 20 µm, mentre la Wp è stata fissata a 2 volte Wn nella prima simulazione e a 2,5 volte nella seconda. Per ogni simulazione parametrica sono stati calcolati i tempi di fall e di rise, per il quarto inverter della catena, ed il ritardo porta-porta in entrambi i casi, inteso come il tempo che intercorre tra l’attraversamento al 50 % (della tensione di alimentazione) dell’uscita della quarta porta e quello della quinta. I tempi di commutazione sono stati calcolati dal 90 % al 10 % della tensione di alimentazione e viceversa.

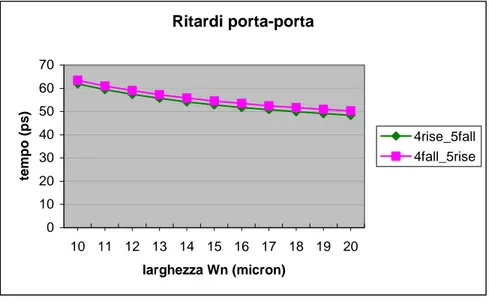

I risultati della prima simulazione hanno dato gli andamenti di figura 4.5 e figura

4.6, mentre dai risultati della seconda sono stati ricavati gli andamenti di figura 4.7 e figura 4.8. Tempi di commutazione 0 20 40 60 80 100 120 140 10 11 12 13 14 15 16 17 18 19 20 larghezza Wn (micron) te m p o ( p s ) t_rise t_fall

Figura 4.5: tempi di commutazione dell’uscita del quarto inverter, con Wn variabile tra 10 e 20

Ritardi porta-porta 0 10 20 30 40 50 60 70 10 11 12 13 14 15 16 17 18 19 20 larghezza Wn (micron) temp o (p s) 4rise_5fall 4fall_5rise

Figura 4.6: tempi di ritardo tra la commutazione in uscita del quarto inverter e quella in uscita del

quinto, con Wn variabile tra 10 e 20 µm e Wp = 2 Wn.

Tempi di commutazione 0 20 40 60 80 100 120 10 11 12 13 14 15 16 17 18 19 20 larghezza Wn (micron) temp o (p s) t_rise t_fall

Figura 4.7: tempi di commutazione dell’uscita del quarto inverter, con Wn variabile tra 10 e 20

Ritardo porta-porta 0 10 20 30 40 50 60 70 10 11 12 13 14 15 16 17 18 19 20 larghezza Wn (micron) temp o (p s) 4rise_5fall 4fall_5rise

Figura 4.8: tempi di ritardo tra la commutazione in uscita del quarto inverter e quella in uscita del

quinto, con Wn variabile tra 10 e 20 µm e Wp = 2,5 Wn.

In primo luogo si osserva che, al crescere di Wn, il tempo di fall dell’uscita dell’inverter tende a circa 66 ps, limite imposto dalla tecnologia, per cui non ha senso eccedere più di tanto con le dimensioni del nMOS. Per quanto riguarda il rapporto tra le dimensioni dei due tipi di transistor, si osserva che, al crescere di Wp, i due tempi di commutazione si avvicinano tra loro, ed in teoria dovrebbero coincidere per Wp = 2,9 Wn. Il rendere il pMOS più grande, se da una parte consente di ottenere tempi di commutazione simili, dall’altra dà uno svantaggio: mentre il tempo di rise dell’uscita dell’inverter diminuisce, quello di fall tende a crescere. Poiché, con il tester a elettroluminescenza, l’attenzione verrà focalizzata quasi sempre sull’emissione dagli nMOS, perché più intensa, si è preferito favorire le commutazioni di questi ultimi, scegliendo un rapporto tra la larghezze dei fet pari a: Wp/Wn = 2.

Dovendo poi realizzare i singoli transistor con struttura standard, ovvero con un unico gate di polisilicio, si è cercato di evitare dimensioni troppo grandi che potrebbero causare effetti indesiderati non previsti dal simulatore, quali ritardi nell’accensione dei mos per effetto della resistenza di gate. E’ stata, quindi, fissata la dimensione Wn a 15 µm, di conseguenza la Wp vale 30 µm.

Con tali dimensioni, le simulazioni con la vista schematic danno un tempo di fall pari a 73,2 ps ed un tempo di rise di 110,1 ps. I ritardi porta-porta, come si nota dal confronto tra le figure 4.6 e 4.8, sono circa uguali e valgono 52,8 ps, tra la transizione low-high in uscita di un inverter e la transizione high-low in uscita al successivo, e 54,5 ps nel caso opposto. Si calcola un ritardo medio di 53,7 ps. In figura 4.9 è raffigurato il layout di un inverter.

Figura 4.9: layout di un inverter.

4.4 Ring Oscillator 200 MHz

Una volta noto il valore del ritardo porta-porta medio, si tratta di andare a mettere in cascata un numero adeguato di inverter per raggiungere la frequenza desiderata. Si definiscono T il periodo dell’oscillazione, τ il ritardo dovuto ad una singola porta ed N il numero totale di porte. Si supponga poi, in prima approssimazione, che la nand introduca lo stesso ritardo degli inverter (in realtà sarà maggiore): così facendo verrà sottostimato il periodo e, quindi, sovrastimata la frequenza effettiva di oscillazione.

Quando il segnale di enable in ingresso alla nand è a livello basso, l’uscita della stessa porta sarà forzata al livello alto, per cui nell’anello tutte le uscite degli inverter saranno stabili. Quando, invece, enable viene portato ad un uno logico, la nand si comporterà come un invertitore e, se N é dispari, commuterà la sua uscita a zero innescando commutazioni successive in tutto l’anello. In uscita da un generico inverter avremo un’onda quadra con periodo T.

Si supponga adesso che, all’istante zero, l’uscita della nand abbia una transizione high-low. Se ogni porta introduce un ritardo τ, dopo N volte τ mi ritroverò tale transizione in ingresso alla stessa nand, provocando la commutazione low-high in uscita. L’istante T, pari al periodo, in cui si ha di nuovo la transizione di partenza in uscita alla nand, coinciderà dunque con l’intervallo di tempo 2τN.

Per una frequenza di 200 MHz, T vale 5 ns, e si ricava:

2 T = Nτ 5 46.55 2 2 53.7 T ns N ps τ = = = ⋅ (4.1)

Dovendo scegliere per N un numero dispari, si fissa a 47, ovvero il ring oscillator a 200 MHz risulta composto da una nand e da 46 inverter.

La nand, avendo tempi di commutazione diversi, perturberà sensibilmente i fronti sui primi inverter. Il punto più indicato per prelevare il segnale di riferimento senza alterare ulteriormente le prestazioni del circuito è, quindi, in ingresso alla nand. In tale posizione è stata inserita la cella di libreria BU24P, comprendente un buffer, in grado di erogare 24 mA, ed il pad esterno. Nella sua categoria si è scelto il buffer più potente, in modo che i fronti in uscita, utilizzati come riferimento, siano i più ripidi possibile.

La capacità di ingresso di un inverter vale

2

( ) (15 30) 0.3 4.54 61.29

inv

in n p ox

C = W +W ⋅ ⋅L C = + µm⋅ µm⋅ fF µm = fF (4.2) mentre la capacità di ingresso della cella BU24P vale 37fF. Per evitare che quest’ultima vada a caricare eccessivamente l’ultimo inverter dell’anello, degradando i fronti, si è fatto precedere a tale cella un altro buffer più piccolo. E’ stata usata la cella di libreria BU2, avente capacità in ingresso di circa 4 fF ed in grado di pilotare il carico a valle.

In figura 4.10 è riportato lo schematico completo del ring oscillator a 200 MHz. Per simularlo in condizioni quasi reali, in uscita al pad è stato inserito un carico equivalente al sistema di misura, consistente in una resistenza da 1 kΩ ed una capacità da 2 pF.

Figura 4.10: schematico del

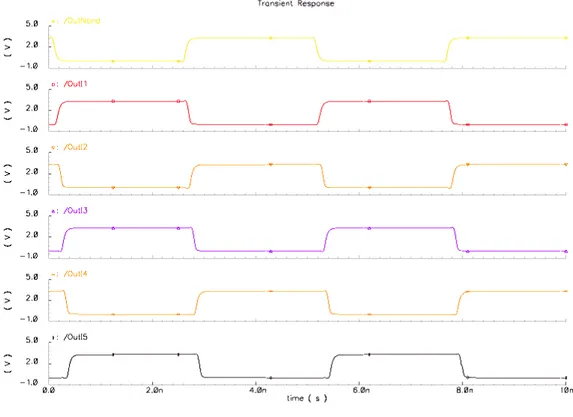

In figura 4.11 si osservano gli andamenti temporali dell’uscita della nand e dei primi quattro inverter ottenuti dopo 10 ns di simulazione, ovvero dopo circa due periodi dell’oscillazione.

Figura 4.11: andamento delle tensioni di uscita per le prime sei porte del ring oscillator 200 MHz.

In tabella 4.1 sono dati alcuni risultati delle simulazioni, ottenuti dapprima con la vista schematica e poi con quella estratta dal layout, al variare dei parametri di processo: in condizioni tipiche, worst speed e worst power. I valori riportati inizialmente si riferiscono ai ritardi porta-porta per la nand e per i primi quattro inverter. Si nota che la nand ha tempi di commutazione più lenti, ma, sul quinto inverter, la riduzione della pendenza dei fronti e l’aumento del tempo di ritardo sono già stati recuperati: i valori tfall,trise riportati per I5, quindi, si manterranno anche per gli inverter successivi. In basso alla tabella sono riportati frequenza e periodo. I dati più vicini alla realtà sono quelli ricavati dalle simulazioni extracted, e, se si vanno a confrontare con quelli ottenuti dallo schematic, si osserva un sensibile decremento dei vari tempi di ritardo e commutazione. In particolare, il

periodo T di oscillazione, in condizioni TM, passa da 5.119 ns a 5.074 ns, in cui il contributo principale è dovuto ad una maggiore velocità della nand. Questo grazie ad una riduzione delle capacità di drain e di source passando dalla vista schematica a quella layout. La frequenza del ring oscillator in condizioni tipiche risulta dunque di 197.07 MHz e, al variare dei parametri di processo potrà oscillare nel range:

130.06MHz≤ =f 197.07MHz≤319.11MHz SCHEMATIC EXTRACTED TM WS WP TM WS WP NAND..I1 (ps) 69.01 101.6 41.93 63.34 93.16 38.87 I1…I2 (ps) 53.5 84.62 33.01 53.25 83.92 32.96 I2…I3 (ps) 54.78 80.16 33.6 54.6 79.92 33.51 I3…I4 (ps) 52.84 82.92 32.82 52.78 82.79 32.79 I4…I5 (ps) 54.56 79.86 33.48 54.47 79.72 33.43 Tfall I5 (ps) 73.21 104.2 51.11 73.09 103.90 51.02 Trise I5 (ps) 110.10 152.10 75.08 109.90 151.80 74.95 Tfall nand (ps) 155.7 224.7 106.5 120.9 171.8 86.02 Trise nand (ps) 137.50 194.60 91.13 108.40 149.05 74.33 4rise..5fall (ps) 52.85 82.89 32.83 52.78 82.79 32.80 4fall…5rise(ps) 54.56 79.87 33.48 54.47 79.72 33.44 T (ns) 5.119 7.760 3.160 5.074 7.690 3.130 f (MHz) 195.34 128.86 316.56 197.07 130.06 319.11

Tabella 4.1: alcuni valori dei tempi di ritardo e di commutazione per le prime porte dell’anello

ricavati dalle simulazioni al variare dei parametri di processo.

Nel layout, per compattare la struttura, gli inverter sono stati disposti secondo quattro file parallele intervallate dalle metal di alimentazione. Queste ultime hanno larghezza di 20 µm, in modo da poter sopportare una corrente ben al di sopra di quella media assorbita dal ring, e per stabilizzare la tensione di

alimentazione per effetto capacitivo. In figura 4.12 si osserva il layout del ring descritto, non è ancora completo perché mancano i pad per il testing con EBT, di cui si parlerà più avanti. Il layout effettivo è riportato nelle tavole finali.

4.5 Ring Oscillator 700 MHz

Per fissare il numero di elementi dell’anello si procede come prima, partendo dalla conoscenza del ritardo medio porta-porta e del periodo voluto, T ≅1.429ns.

2 T = Nτ 1.429 13.3 2 2 53.7 T ns N ps τ = = = ⋅ (4.3) Si realizza dunque il ring con 12 inverter più una nand; anche qui il segnale di riferimento viene prelevato da uno dei due ingressi della nand, mentre l’altro serve come segnale di enable. Per rispettare il vincolo dei 200 MHz, come frequenza massima in ingresso alla scheda di acquisizione, è stato inoltre necessario introdurre un divisore di frequenza per quattro.

4.5.1 Divisore di frequenza per quattro

Questo oggetto è stato realizzato impiegando standard cell disponibili nelle librerie di questa tecnologia. Dapprima è stato disegnato lo schematico di un flip-flop SR sincrono di tipo master-slave, vedi figura 4.13. Questo è tale che, in un ciclo di clock, il master campiona il dato in ingresso sul fronte in salita, mentre lo slave su quello in discesa: il valore in ingresso fissato da set e reset, quindi, passerà in uscita solo dopo un ciclo completo di clock.

Figura 4.13: flip-flop SR master-slave.

Montando tale circuito come in figura 4.14 si ottiene un flip-flop di tipo T. La porta XOR ha la funzione di riportare in ingresso al flip-flop SR il valore dell’uscita Q, o il valore Q negato, a seconda che il segnale di Enable sia uno zero

o un uno logico. Se fissiamo, dunque, Enable a livello alto, quello che accade è che, alla fine di ogni ciclo di clock, l’uscita cambierà il suo stato: se su CK si applica una frequenza f , si otterrà su Q un segnale a frequenza 0 f0 2, ovvero si tratta di un divisore di frequenza per 2. Mettendo in cascata due di questi oggetti si realizza, quindi, un divisore di frequenza per 4, vedi figura 4.15.

Figura 4.14: flip-flop T.

Figura 4.15: divisore di frequenza per quattro.

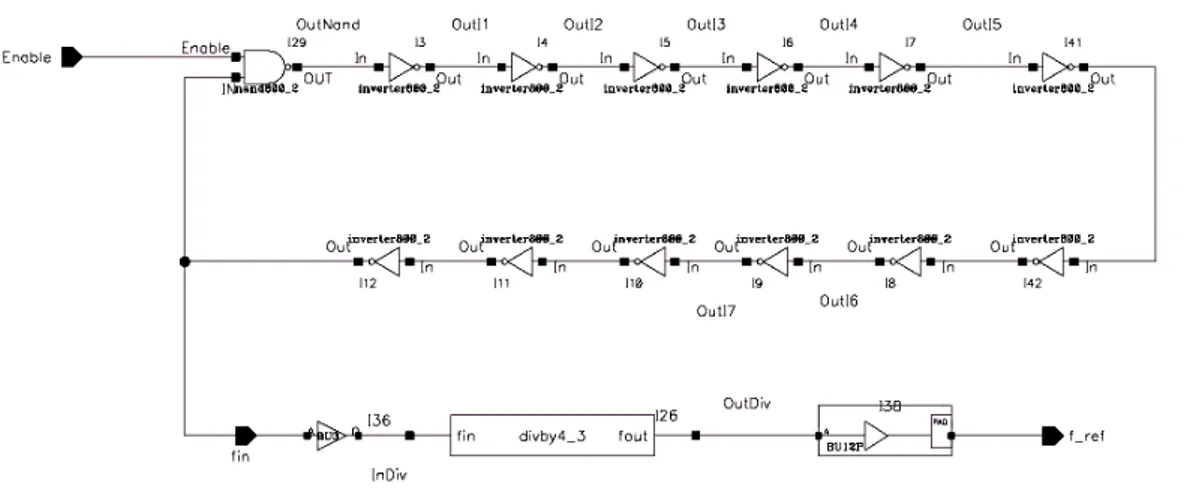

4.5.2 Schematico completo del Ring Oscillator 700 MHz

Il divisore di frequenza è stato posizionato sul ramo che collega l’ultimo inverter alla nand. Anche in questo caso, poiché la Cin =21fFdel divisore perturberebbe i tempi di commutazione e la frequenza di oscillazione, si è inserito il buffer BU3 di libreria, avente capacità di ingresso di 4.5 fF.

Come buffer più pad di uscita è stata usata nuovamente la cella BU24P, in modo da avere transizioni rapide sulla frequenza di riferimento. Lo schematico completo è riportato in figura 4.16.

Figura 4.16: schematico del ring oscillator a 700 MHz.

Nella tabella 4.2 sono dati i valori di frequenza e periodo ottenuti dalle simulazioni nelle varie condizioni di lavoro. La frequenza di oscillazione, in condizioni tipiche, risulta di 700.5 MHz, questa verrà divisa per quattro e, in uscita al pad, varrà 175.13 MHz, a cui corrisponde un periodo di 5.7 ns.

SCHEMATIC EXTRACTED

TM WS WP TM WS WP

T 1.467 ns 2.226 ns 903.9 ps 1.427 ns 2.163 ns 881.59 ps f 681.7MHz 449.3MHz 1.106GHz 700.5MHz 462.4MHz 1.134GHz

Tabella 4.2: valori di frequenza e periodo ricavati dalle simulazioni del ring oscillator a 700 MHz.

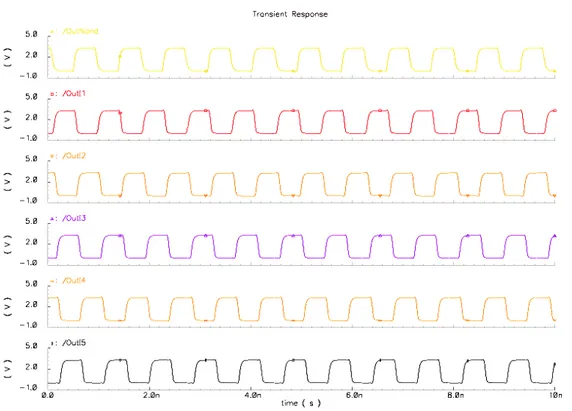

Nelle figure seguenti vengono riportati gli andamenti di alcune tensioni ottenuti dalle simulazioni, in particolare, in figura 4.17, si osserva il propagarsi delle commutazioni nelle prime sei porte dell’anello, mentre, in figura 4.18, sono dati gli andamenti delle tensioni sul ramo di uscita. Nella seconda si può apprezzare il funzionamento del divisore di frequenza e la riduzione del tempo di transizione sui fronti in uscita da parte del buffer BU24P.

Figura 4.17: andamento delle tensioni di uscita per le prime sei porte del ring oscillator 700 MHz.

Il layout della parte full-custom è stato realizzato in maniera simile a quello del ring oscillator precedente, affiancando due file di inverter, vedi figura 4.19; la parte semi-custom, ovvero il divisore di frequenza e le altre celle di libreria, verrà inserita successivamente in automatico con il tool Cell Ensemble. Il layout completo è riportato nelle tavole finali.

Figura 4.18: andamento delle tensioni sul ramo di uscita del ring oscillator 700 MHz; nell’ordine

raffigurato: in ingresso alla cella BU3, in ingresso al divisore, in uscita al divisore, sul pad di uscita.

4.6 Ring Oscillator con carico programmabile

Nei ring precedenti, le misure effettuate con lo SPAD daranno le forme d’onda ottiche viste nel capitolo 2, dalle quali è possibile ricavare informazioni riguardo a ritardi, frequenza e tempi di commutazione. Questi ultimi sono proporzionali alla larghezza dell’impulso e sono fissati dalle dimensioni dei dispositivi. Si è pensato, allora, di progettare una struttura dove è possibile fare allargare la campana dell’impulso mediante un controllo esterno, mantenendo tutti gli inverter uguali tra loro.

E’ stato preso, quindi, un ring oscillator a 200 MHz, come quello visto in precedenza, e in due punti differenti sono state inserite due batterie di condensatori, realizzati mediante shunt-capacitor. Le batterie sono composte da più capacità, tutte uguali tra loro, in parallelo e connesse in modo che se ne possa effettuare un controllo digitale dall’esterno. Se, ad esempio, si chiama C la capacità minima che è possibile inserire, le altre più grandi cresceranno secondo le potenze di due, vedi figura 4.20.

Figura 4.20: schema di una batteria di shunt capacitor.

La prima serie di condensatori è costituita da 7 shunt, connessi a formare le capacità C0, 2C0, 4C . Le dimensioni sono tali da consentire un aumento del 0

tempo di commutazione, e di conseguenza della larghezza dell’impulso ottico, con una risoluzione di 5 ps, inserendo soltanto C , e con un allargamento massimo di 0

35 ps; il controllo digitale viene effettuato su tre bit. La seconda batteria, invece, è composta da 15 shunt, montati a costituire i carichi capacitivi C1, 2C1, 4C1,8C1 e

dimensionati in modo tale da introdurre un ritardo minimo di 2 ps, con C1, e

massimo di 30 ps; in questo caso il controllo digitale sarà su quattro bit.

Le due batterie sono state connesse nel ring, rispettivamente, sulle uscite dell’inverter numero 28 e del numero 39, numerandoli a partire dalla nand; vedi

figura 4.21. Così facendo, le capacità di carico su una porta non hanno modo di

influenzare i tempi di commutazione sull’altra, perché è sufficientemente distante, e la pendenza dei fronti ha modo di essere recuperata.

Figura 4.21: batterie di condensatori impiegate e loro connessione nel ring oscillator a 200 MHz.

4.6.1 Funzionamento shunt capacitor

Uno shunt capacitor è costituito da un transistore nMOS con source e drain cortocircuitati tra loro, così facendo risulta accessibile dall’esterno tramite i terminali G e D/S, vedi figura 4.22.

Il terminale D/S viene connesso all’uscita dell’inverter, mentre G serve per il controllo della capacità inserita. Se la tensione sul gate è bassa, il carico sarà costituito dalle capacità di giunzione e di overlap, molto piccole, mentre, quando il livello logico di controllo è alto, verrà aggiunta anche la capacità di canale che risulterà predominante sulle altre; la capacità di gate COX, infatti, è la più elevata che possiamo avere.

Da notare che tale capacità di gate varia con la polarizzazione del dispositivo nelle tre regioni di funzionamento (interdizione, triodo e saturazione) e, poiché il terminale D/S è connesso all’uscita di un inverter, se ne deduce che il livello di capacità inserita non dipenderà soltanto dalla tensione di gate. In particolare, avremo un comportamento diverso sui due fronti, che è bene chiarire per giustificare le scelte fatte.

Si vanno adesso ad esaminare nel dettaglio i vari contributi che costituiscono la capacità vista dal terminale D/S. Innanzitutto, ci sono le capacità di giunzione tra i pozzetti di source e drain verso il substrato, costituite da un termine proporzionale all’area e da un altro proporzionale al perimetro del pozzetto relativo:

BS J S JSW S BD J D JSW D C C A C P C C A C P = + = + (4.4)

Queste capacità sono indipendenti dalla polarizzazione del transistore. C’è poi il contributo della capacità che si vede verso il gate, formata a sua volta da due parti: la capacità di overlap, dovuta ad un allargamento dei pozzetti sotto al polisilicio per effetto della diffusione laterale, e la capacità di canale vera e propria, che dipende dallo strato di inversione e, perciò, dalla polarizzazione.

/ / ( , ) ( , ) canale GS OVGS GS G D S canale GD OVGD GD G D S C C C V V C C C V V = + = + (4.5)

In interdizione, il secondo termine è nullo, in quanto il canale non è formato, mentre in zona triodo avremo tutto lo strato di inversione e si può assumere:

2 OX C W L canale canale GS GD C =C = ⋅ ⋅ (4.6)

Lo shunt capacitor si basa proprio su quest’ultimo contributo, in quanto, quando è presente, prevale nettamente sugli altri.

/ / , 0.5

GS G D S D S T n

V =V −V = −V <V ≅ V (4.7)

In tali condizioni resteranno soltanto i contributi capacitivi delle giunzioni e delle sovrapposizioni gate-pozzetto, trascurabili finché il numero di shunt si mantiene basso. Quando, invece, la tensione V è a livello alto, si avrà un canale G

pienamente formato per:

/

GS G D S Tn

V =V −V >V VD S/ <VDD −VTn (4.8)

Sotto questa condizione, il carico introdotto sarà massimo e dato dall’espressione (4.6), se, invece, VD S/ supera tale livello di tensione, il canale non sarà più formato ed il carico si ridurrà fortemente.

Questo comporta una dissimmetria sui due tipi di transizioni quando VG =VDD: se l’uscita dell’inverter caricato passa dal livello alto al livello basso, per la (4.8) inizialmente il canale non sarà formato, quindi la commutazione sarà sensibilmente più rapida rispetto al caso opposto, in cui il canale è già formato all’inizio della transizione.

Ai nostri scopi, questo effetto può essere considerato trascurabile, sia perché in fase di misurazione si osservano gli nMOS e l’attenzione viene concentrata sulle transizioni high-low, sia perché un eventuale sbilanciamento dei fronti viene recuperato dalle porte a valle.

4.6.2 Realizzazione degli shunt

C0e

C1Primo passo nel dimensionamento degli shunt capacitor è stato quello di dare una stima della capacità che si vogliono realizzare: a questo scopo si è introdotto un carico capacitivo, variabile tra 0 e 40 fF, sull’uscita di un inverter e si è ricavato il valore che introduce il ritardo desiderato sul tempo di fall. Nel primo caso, si è trovato che un aumento del tempo di commutazione high-low di 5 ps è dovuto ad un carico di 11.55 fF. Con quest’ultimo valore è possibile dare una stima dell’area che deve avere lo shunt. Si tratta di una stima grossolana, in quanto il ritardo introdotto da un transistore-condensatore non dipende soltanto dalla sua area, ma anche dalla sua forma e dalle varie resistenze parassite di canale e di gate, di cui estrattore e simulatore non tengono conto. Questo spiega il motivo per cui, per

ottenere un ritardo doppio, sono stati messi due shunt capacitor in parallelo, e così via per gli altri ritardi.

Dividendo il valore della capacità che si vuole ottenere per la C (capacità ox

dell’ossido di gate), si ricava un’area di circa 2.4 µm2. Si tratta adesso di scegliere una forma adatta per riuscire ad avere tale area di canale e di procedere ripetutamente con simulazioni e correzioni sul layout fino al raggiungimento del ritardo desiderato.

Per lo shunt capacitor C è stata scelta la struttura a bottone, riportata in figura 0 4.23, dove il transistore ha gate a forma di striscia quadrata ed è dato dalla

sovrapposizione del poly, in rosso, all’area attiva, in verde.

Figura 4.23: layout del condensatore C0.

Poiché l’estrattore (DIVA) non è in grado di riconoscere questo oggetto, e poiché il simulatore (SPECTRE) non tiene conto delle resistenze parassite di gate e di canale, che ritardano la distribuzione delle cariche sulle armature dello shunt, si deve introdurre un modello equivalente a livello schematico, che è quello osservabile in figura 4.24. Solitamente si usa una catena di nMOS, ma nel caso in esame ne è stato inserito solo uno, perché si vogliono capacità piccole. I terminali di drain e source non possono essere cortocircuitati, perché, così facendo,

scomparirebbe la resistenza di canale, ottenendo un comportamento puramente capacitivo. D’altronde, il simulatore non consente di lasciare uno dei terminale di drain o source flottante e, dato che in entrambi non può scorrere corrente, si connette tale terminale ad una resistenza molto alta, di 1 TΩ.

Le dimensioni del transistor sono state fissate nel seguente modo: la lunghezza è data dalla larghezza della striscia quadrata, ovvero L=0.3 µm, mentre la larghezza è stata calcolata come la media dei perimetri esterno e interno della stessa striscia, W=7.2 µm; l’area di canale risultante è di 2.16 µm2. Per perfezionare ulteriormente il modello prima della simulazione, è necessario modificare il file CDF riguardante la descrizione del nMOS, affinché la capacità di canale venga calcolata correttamente. A questo scopo si azzerano area di drain, perimetro di drain e perimetro di source, mentre l’area di source si fissa a 2.25 µm2.

Figura 4.24: circuito elettrico equivalente dello shunt capacitor C . 0

Per lo shunt capacitor C1, dovendo introdurre un ritardo inferiore, si è impiegato una forma ad L, in quanto consente di realizzare superfici ben più piccole. Il layout di C1 è riportato in figura 4.25. Nello schematico equivalente, di figura

4.26, si è definito un transistore con L=0.3 µm, W=2.8 µm, area di canale di 0.84 2

m

Figura 4.25: layout del condensatore C1.

Figura 4.26: circuito elettrico equivalente dello shunt capacitor C1.

4.6.3 Realizzazione del controllo degli shunt

Per inserire o meno una capacità bisogna, dunque, portare sui gate, di tutti gli shunt di una batteria, una tensione a livello alto o basso e andrà mantenuta costante durante tutta la fase di misurazione.

A questo scopo, sono stati realizzati inizialmente due registri a scorrimento a celle standard, uno a tre bit (Q0, Q1, Q2) e l’altro a quattro (q0, q1, q2, q3), per

controllare le due batterie di condensatori. Un registro è costituito da una catena di flip-flop SR master-slave, dove le uscite Q e Q negato del primo vanno, rispettivamente, su set e reset del successivo, in modo da passargli il dato memorizzato ad ogni nuovo ciclo di clock. Esternamente, devono essere disponibili un ingresso seriale (SI), dove presentare la sequenza di tensioni, ed un ingresso di clock (CK) per poter accedere al registro e caricarlo; l’uscita di ogni flip-flop andrà a pilotare i gate dei vari shunt. Successivamente, risultando il prototipo finale di tipo pad limited, si è preferito realizzare un unico registro a 7 bit, risparmiando così due pad esterni.

Ciascun flip-flop campiona il dato sul master all’arrivo del fronte in salita del clock, e lo passa allo slave su quello in discesa. Per memorizzare tutti e 7 i bit, quindi, serviranno sette cicli completi di clock, trascorsi i quali il segnale CK dovrà essere tenuto basso fino a nuovo aggiornamento del registro.

Il primo dato inserito andrà a caricare l’ultimo flip-flop del registro, i valori devono perciò essere immessi nel seguente ordine: q0 , q1 , q2 , q3 , Q0 , Q1 , Q2. Vedi figura 4.27.

Figura 4.27: registro a scorrimento per il controllo degli shunt capacitor.

4.6.4 Schematico completo

In figura 4.28 è riportato lo schematico della sola parte full custom del circuito, comprendente il ring oscillator da 47 porte e le due batterie di shunt capacitor connesse agli inverter 28 e 39.

Nello schematico complessivo sarà necessario il solito segnale di riferimento, che viene prelevato in uscita all’ultimo inverter dell’anello e portato fuori tramite la

solita cella di libreria BU2, inserita per ridurre il carico visto da tale inverter, seguita dal buffer con pad BU24P.

Le uscite Q2, Q1, Q0, q3, q2, q1, q0 del registro sono state portate ai rispettivi gate dei transistori-condensatori per mezzo dei buffer di libreria BU8, vedi figura

4.29. L’utilizzo di questi ultimi si è reso necessario in quanto, da simulazioni

precedenti, si è visto che venivano indotti degli spike sulle tensioni Qi, qi e questi si ripercuotevano sulle condizioni di lavoro degli shunt, facendo variare i ritardi da quanto progettato.

Figura 4.29: schematico complessivo.

In figura 4.30 si osserva il layout delle due batterie di shunt capacitor, quella costituita da sette capacità C sulla destra e l’altra formata da quindici capacità 0

1

C sulla sinistra. Il layout dell’intera parte full custom è riportato nelle tavole finali.

Figura 4.30: layout delle due batterie di shunt capacitor.

4.6.5 Simulazioni del ring oscillator caricato

In tabella 4.3 sono riportati, al variare della configurazione dei condensatori, i tempi di fall e di rise delle uscite degli inverter 28 e 39 ed i valori di periodo e frequenza in condizioni typical, worst speed e worst power.

Durante queste simulazioni, sono stati calcolati anche i tempi di commutazione relativi agli inverter 27 e 38, precedenti a quelli con gli shunt di carico, e tali valori sono stati confrontati con le transizioni sul decimo inverter. Si è ottenuto che tutti e tre i tempi di fall e di rise coincidono tra loro e valgono circa 73 e 109 ps; questo dimostra come la distanza tra le due batterie di shunt capacitor sia sufficiente a non influenzare reciprocamente le transizioni sui rispettivi inverter.

Capacità inserite Vista Tfall28 Trise28 Tfall39 Trise39 T (ns) F (MHz) 0 1 0C , 0C Schematic TM 81,25 ps 120,6 ps 86,86 ps 128 ps 5,153 194,1 0 1 1C ,1C Schematic TM 86,33 ps 125,6 ps 88,83 ps 129,8 ps 5,162 193,7 0 1 7C ,15C Schematic TM 116,4 ps 157,7 ps 116,1 ps 157,5 ps 5,230 191,2 0 1 0C , 0C Extracted TM 81,07 ps 120,4 ps 86,67 ps 127,7 ps 5,108 195,9 0 1 1C ,1C Extracted TM 86,13 ps 125,4 ps 88,64 ps 129,6 ps 5,117 195,4 0 1 2C , 2C Extracted TM 90,94 ps 130,9 ps 90,57 ps 131,5 ps 5,125 195,1 0 1 4C , 4C Extracted TM 99,99 ps 142,9 ps 94,35 ps 135,6 ps 5,141 194,5 0 1 0C ,8C Extracted TM 81,08 ps 120,4 ps 101,6 ps 144,4 ps 5,126 195,1 0 1 7C ,15C Extracted TM 116,0 ps 157,4 ps 115,8 ps 157,3 ps 5,185 192,9 0 1 0C , 0C Extracted WS 115,5 ps 167,1 ps 123,9 ps 178,6 ps 7,740 129,2 0 1 1C ,1C Extracted WS 122,3 ps 173,5 ps 126,5 ps 180,9 ps 7,753 129,0 0 1 7C ,15C Extracted WS 162,2 ps 214,7 ps 162,0 ps 215,8 ps 7,849 127,4 0 1 0C , 0C Extracted WP 56,59 ps 81,42 ps 60,15 ps 85,55 ps 3,154 317,1 0 1 1C ,1C Extracted WP 60,43 ps 85,15 ps 61,65 ps 86,94 ps 3,16 316,5 0 1 7C ,15C Extracted WP 82,99 ps 109,7 ps 82,39 ps 108,5 ps 3,204 312,1

Osservando i valori delle simulazioni con vista extracted in condizioni tipiche, si nota che il tempo di fall per l’inverter 28 passa da un valore minimo di 81.07 ps ad un valore massimo di 116.0 ps, quando i gate delle capacità sono rispettivamente tutti a 0 V e tutti a VDD. La batteria costituita dalle capacità C 0

può, quindi, introdurre un ritardo massimo di 34.93 ps, con un incremento medio di 4.99 ps. Da notare che, quando ciascun Q è fissato a zero, il tempo di fall i

minimo cresce sensibilmente, di circa 8 ps, rispetto a quello degli altri inverter della catena, questo aumento è proporzionale al numero di shunt capacitor inseriti nella batteria e dipende dalle capacità parassite CP =CJ⋅AS +COVGS. Le simulazioni worst speed hanno dato un aumento massimo del tempo di commutazione high-low di 46.7 ps, con un incremento medio di 6.67 ps, mentre dalle worst power si è ottenuto rispettivamente 26.4 ps e 3.77 ps.

Considerazioni analoghe valgono per l’altra batteria da 15 shunt capacitor C1:

questa, in condizioni tipiche, può aumentare il tempo di fall fino a 29.13 ps con uno step minimo medio di 1.94 ps. Questi valori, in condizioni worst speed, diventato di 38.1 ps e 2.54 ps, mentre, in condizioni worst power, valgono 22.24 ps e 1.48 ps. In figura 4.31 e figura 4.32 sono raffigurati gli andamenti dei tempi di fall e di rise al variare della configurazione del carico per entrambe le batterie.

Ritardi batteria 5 ps 0 20 40 60 80 100 120 140 160 180 0 1 2 3 4 5 6 7 Capacità attivate t (p s ) 28 t_f all 28 t_rise

Figura 4.31: aumento dei tempi di fall e di rise dell’inverter 28 al variare delle capacità C0

Ritardi batteria 2 ps 0 20 40 60 80 100 120 140 160 180 0 2 4 6 8 10 12 14 Capacità attivate t (p s ) 39 t_fall 39 t_rise

Figura 4.32: aumento dei tempi di fall e di rise dell’inverter 39 al variare delle capacità C1

inserite.

Con questa struttura sarà possibile stimare l’allargamento minimo dell’impulso ottico che il tester a elettroluminescenza riesce a rivelare. L’introduzione di un carico capacitivo sull’uscita di una porta, però, causa l’alterazione anche di altre grandezze, per cui potranno essere eseguite misure riguardo a variazione dei tempi di ritardo e della frequenza di oscillazione.

4.7 Circuito impulsatore

4.7.1 Introduzione

Scopo dei primi transistor disegnati era quello di andare a caratterizzarli dal punto di vista ottico, ovvero tracciarne la caratteristica ottica dell’emissione in funzione delle tensioni di polarizzazione VGS,V . La caratterizzazione che si ottiene è in DS

DC, ma si è voluto realizzare una struttura che permetta di descrivere il comportamento di questi mos anche in AC.

Obiettivo è quello di andare a sollecitare due transistor di test con un’onda quadra alla frequenza di 1 GHz; le dimensioni di tali mos sono state fissate a L=0.35 µm e W=10 µm. Per eseguirne una caratterizzazione completa è necessario poter accedere a tutti e tre i terminali di drain, source e gate per variarne la tensione di controllo, di conseguenza anche l’onda quadra dovrà avere un’ampiezza che possa variare nel range 0V – 3.3V .

4.7.2 Controllo dei mos di test

I due transistor che saranno osservati, chiamati M1 ed M2, vengono sollecitati uno sul terminale di gate e l’altro su quello di drain, mentre gli altri terminali sono stati resi disponibili all’esterno per controllarne la polarizzazione. Esternamente si hanno gli ingressi Drain1, Source1, Gate2, Source2 ed i due contatti di substrato Sub1, Sub2 che, per risparmiare un pad, sono stati messi a comune (il numero sul terminale si riferisce a M1 o M2). Si ricordi che è necessario avere i contatti di substrato accessibili all’esterno, in modo da poterne misurare la corrente, che varia insieme all’emissione di fotoni.

Per portare una tensione analogica, compresa tra 0 V e VDD, sul gate di M1 e sul

drain di M2, si sono impiegate due pass-gate, connesse rispettivamente agli ingressi In1 e In2. E’ stato, poi, impiegato un altro ingresso, Pulsed, che consente, se posto a livello basso, di polarizzare i due mos con una tensione continua, quindi le pass-gate resteranno sempre accese. Quando, invece, Pulsed viene fissato a livello alto, si innesca l’oscillazione e le pass-gate verranno accese e spente alla

frequenza di 1 GHz. Di conseguenza, sul gate di M1 e sul drain di M2, si avrà un’onda quadra di ampiezza fissata dalle tensioni presenti su In1 e In2.

4.7.3 Dimensionamento delle pass-gate

La scelta di utilizzare delle pass-gate è dipesa dal fatto che era necessario un interruttore in grado di fare passare entrambi i livelli logici pieni e tutte le tensioni analogiche intermedie. Inoltre, dimensionando opportunamente i due transistor è possibile controllare la resistenza serie equivalente, in modo da adattarla ai nostri scopi.

Figura 4.33: schematico di una generica pas-gate.

In riferimento alla figura 4.33, la resistenza equivalente della pass-gate è data dal parallelo delle resistente del nMOS e del pMOS e può essere espressa nella seguente forma approssimata, ricavata da calcoli antologici:

1 ( ) [ ( ) ( )] eq in p n p Gp Tp n Gn Tn R V β β β V V β V V = ⋅ − − ⋅ + − ⋅ − (4.9)

Questa equazione è stata ricavata nel range (0V, Vdd): si nota subito che, se si pone βn =βp = , si rende tale resistenza indipendente dal livello di tensione che β deve passare ed avrà un andamento circa costante. Per soddisfare tale condizione è stata fissata Wp = ⋅3 Wn. Quando la pass-gate è accesa si ha VGn =VDD =3.3V e

0

Gp

1 ( ) eq DD Tn Tp R V V V β = ⋅ − − (4.10) Se ne deduce che, se si vuole ridurre ulteriormente la resistenza in condizioni on, si deve agire sul fattore n ox

W

C L

β = ⋅µ ⋅ , aumentandolo, ovvero occorre andare ad agire sulle larghezze W dei mosfet.

Si esamina dapprima la pass-gate1, il cui schematico è riportato in figura 4.34.

Figura 4.34: pass-gate1 per il controllo del gate di M1.

Questa preleva la tensione dall’ingresso In1 e, a seconda del suo stato di funzionamento, la porta o meno sull’uscita Out1, la quale è connessa al gate del transistor di test M1. L’accensione è controllata dai segnali GateMn e GateMp, i quali hanno andamento opposto tra loro. Quando la tensione su GateMn è a livello logico alto, e quindi GateMp si trova sul livello basso, la pass-gate è accesa e, poiché il gate di M1 non assorbe corrente, la tensione su In1 la ritrovo identica sul gate. Invertendo contemporaneamente le tensioni su GateMn e GateMp, la

pass-gate verrà spenta. A questo punto, per evitare che il pass-gate di M1 resti flottante per effetto capacitivo, entra in azione un transistore nMOS di pull-down, che, accendendosi al medesimo istante, fa scaricare a massa la capacità di gate e spenge completamente M1. I transistor della pass-gate sono stati scelti tutti e tre con lunghezza minima di 0.3 µm, mentre le larghezze sono state fissate a 10 µm per gli nMOS e 30 µm per il pMOS.

La pass-gate2, riportata in figura 4.35, è collegata all’altro ingresso In2 e, mediante il nodo Out2, porta tale tensione sul drain del mos di test M2. I due transistor di tale pass-gate vengono pilotati dalle stesse tensioni che controllano anche l’altra, per cui le due porte saranno accese e spente in parallelo. In questo caso il mosfet di pull-down può essere tolto, venendo incontro alla necessità di misurare la corrente di drain dall’esterno per metterla in relazione con l’emissione; un eventuale mos avrebbe, infatti, assorbito parte di questa corrente.

Figura 4.35: pass-gate2 per il controllo del drain di M2.

In questo secondo caso le cose funzionano diversamente, perché in condizioni di pass-gate accesa, questa viene attraversata da corrente e si forma un partitore di

tensione tra la resistenza di M2 e la Req data dalla (4.10). Mantenendo le dimensioni della pass-gate1, la tensione sul drain di M2 viene ridotta di un fattore circa 1/2 rispetto a quella presente su In2. Poiché risulta:

2 ds 2 eq ds r Out In R r = ⋅ + (4.11)

per cercare di polarizzare il mos di test con una tensione Out2 il più possibile vicino alla In2, l’unico parametro su cui si può agire è la R , riducendola. eq

Risulta, quindi, necessario aumentare il β, che si traduce in un aumento contemporaneo delle larghezze dei due transistor della pass-gate.

Bisogna, però, tenere presente che, un allargamento delle dimensioni dei mosfet, comporta anche un aumento delle varie capacità, in particolare di quella di gate. Come conseguenza, i tempi di commutazione della pass-gate2 aumentano e l’onda quadra ad 1 GHz viene degradata. Allora, se ci interessa aumentare le W, risulta indispensabile agire anche sul buffer di accensione delle due pass-gate, potenziandolo. Facendo varie simulazioni, si è trovato un compromesso tra dimensioni dei mosfet, tempi di commutazione e struttura del buffer, quest’ultima verrà esaminata più avanti. Per la pass-gate2 sono state, quindi, fissate

30

n

W = µm e Wp =90µm.

4.7.4 Generazione dell’oscillazione

Allo scopo di generare l’oscillazione ad 1 GHz per andare ad accendere/spengere le pass-gate o per tenerle sempre accese, lo schema circuitale più indicato è stato un ring oscillator. Il segnale di ingresso Pulsed, precedentemente citato, non è altro che l’abilitazione in ingresso alla nand: se esso è posto a livello alto si avrà l’oscillazione, quando, invece, viene fissato a zero si tratterà di fare in modo che le tensioni presenti su GateMn e GateMp siano rispettivamente 3.3V e 0V. L’anello è stato realizzato con gli stessi inverter delle strutture precedenti, per cui, noto il periodo che si vuole ottenere, per fissare il numero di elementi dell’anello si procede alla stessa maniera:

2 T = Nτ 1 9.3 2 2 53.7 T ns N ps τ = = = ⋅ (4.12)

Si realizza dunque il ring con 8 inverter più una nand; anche qui servirà un segnale di riferimento, chiamato f_ref, che viene prelevato dall’uscita Ref del settimo inverter del ring. Per rispettare, poi, il vincolo dei 200 MHz, come frequenza massima in ingresso alla scheda di acquisizione, si è impiegato un divisore di frequenza per otto, realizzato semplicemente aggiungendo un flip-flop T al divisore per quattro precedentemente visto, vedi figura 4.36. A questa parte semicustom è stato fatto precedere il solito buffer di libreria BU2, in modo da perturbare il meno possibile l’oscillazione.

Figura 4.36: divisore di frequenza per otto.

4.7.5 Schematico complessivo

Resta da chiarire come si faccia ad accendere e spengere le pass-gate sfruttando l’oscillazione del ring. Poiché i gate delle due porte introducono un carico capacitivo molto elevato, di circa 240 fF, si è impiegato un adeguato buffer, mostrato in figura 4.38. E’ stata prelevata l’uscita (OutRing) del quinto inverter, che in assenza di oscillazione si trova a livello basso, e da qui, con un numero dispari di inverter, si è portato il segnale su GateMn, mentre, con un numero pari, su GateMp. Così facendo, quando Pulsed è a livello basso, ovvero non si ha l’oscillazione, i segnali GateMn e GateMp saranno fissati rispettivamente a 3.3V e 0V, mantenendo le pass-gate sempre accese.

Figura 4.38: buffer di pilotaggio delle passgate.

Il buffer è dunque costituito da una catena di sei inverter scalati tra loro di un fattore circa 2, di cui il primo ha dimensioni minime, per caricare il meno possibile l’anello, ed i primi quattro sono tutti di libreria. Le porte Inv15 e Inv30 sono, invece, full custom e sono composte da transistor nMOS, pMOS di dimensioni 15 µm e 30 µm la prima, 30 µm e 60 µm la seconda. In questo modo, si spezza la capacità totale di ingresso delle due pass-gate in una capacità da circa 60 fF dovuta agli nMOS e pilotata da Inv15, ed un’altra da 180 fF dovuta ai pMOS e pilotata da Inv30. Quando viene abilitata l’oscillazione, portando Pulsed a VDD, questa si propagherà sul buffer, provocando l’accensione e lo spegnimento

delle pass-gate alla stessa frequenza del ring e con tempi di commutazione accettabili, grazie al precedente dimensionamento degli inverter.

Gli schematici dell’intera struttura sono riportati in figura 4.37, per quanto riguarda la sola parte full custom, e in figura 4.39 per lo schematico completo, comprendente, quindi, anche una parte del buffer ed il divisore di frequenza.

Figura 4.39: schematico

completo del circuito impulsatore.

4.7.6 Simulazioni del circuito impulsatore

Le prime simulazioni si sono concentrate sull’andamento della tensione di gate sul mos di test M1. Questo è stato polarizzato con tensioni Vd =3.3V , 0Vs =Vsub = V

ed inizialmente con VG =0V e Pulsed a livello basso. Come si vede dagli andamenti ottenuti dalla simulazione in figura 4.40, all’istante t=2 ns è stata abilitata l’oscillazione portando Pulsed a livello alto, mentre, sull’ingresso In1, è stata applicata una gradinata con step di 250 mV ogni 4 ns e con step finale di 300 mV. Si sono effettuate poi misure sulla tensione Out1 in ingresso al gate di M1: l’andamento risulta un’onda quadra alla frequenza del ring oscillator e con

ampiezza coincidente alla tensione su In1, su tutto il range di tensione compreso tra i due livelli logici pieni.

Figura 4.40: andamento impulsato sul gate di M1.

Per il transistor M1 è stato perciò ottenuto un controllo totale: le tensioni vengono imposte dall’esterno, mentre le correnti di drain e di substrato possono essere misurate per poter compiere una caratterizzazione completa della luminescenza in AC.

La stessa simulazione è stata ripetuta applicando il segnale di ingresso precedente sia su In1 che su In2. Per il dimensionamento delle pass-gate e dei buffer visto in precedenza, l’attenuazione dovuta alla resistenza della pass-gate2 sulla tensione Out2, che pilota il drain di M2, è stata ridotta il più possibile. Da misure effettuate sull’andamento di Out2, si è stimato che l’ampiezza di tale tensione equivale al 76% circa del valore presente su In2, quando l’ingresso è prossimo al livello basso, e passa al 86% circa quando, invece, In2 si avvicina al livello alto. Quindi, mentre su Out1 il livello logico alto passa pienamente, su Out2 si ha che la

tensione massima raggiungibile, quando In2 è fissata a VDD, risulta di 2.94 V; vedi

figura 4.41.

Figura 4.41: andamento impulsato sul gate di M1 e sul drain di M2.

Anche in questo caso, le correnti di substrato e di drain potranno essere misurate dall’esterno: grazie all’assenza del transistore di pull-down, infatti, la corrente che entra da In2 è proprio quella assorbita da M2. La polarizzazione di tale mos può essere controllata per mezzo di tutti i suoi terminali, che sono accessibili dall’esterno, unico “neo” resta il fatto che la tensione sul drain non coinciderà con quella imposta in ingresso. Poiché per eseguire la caratterizzazione ottica è necessario conoscere anche la VDS, è stato inserito un probe pad sul drain di M2, in modo da misurarne il livello di tensione per mezzo dell’EBT.

La simulazione di figura 4.42 riporta gli andamenti delle onde quadre generate al gate di M1 e al drain di M2 per tensioni di ingresso In1 e In2 pari a VDD. Dal funzionamento sotto queste condizioni sono state ricavate informazioni riguardo al duty cicle, che si aggira intorno al 55%, e ai tempi di salita e di discesa, questi

ultimi riportati in tabella 4.4. Per l’onda quadra Out1 si sono ottenuti trise,ffall

confrontabili con quelli degli inverter dei ring oscillator, mentre, per la tensione su Out2, questi tempi sono leggermente superiori a causa delle capacità maggiori della pass-gate2, ma comunque sufficienti per i nostri scopi.

Figura 4.42: simulazione delle tensioni Out1 e Out2 per ingressi fissati a VDD.

SCHEMATIC EXTRACTED

Tensione trise tfall trise tfall

Out1 169,1 ps 71,1 ps 111,9 ps 69,7 ps

Out2 102,4 ps 95,3 ps 130,4 ps 87,8 ps

Tabella 4.4 : tempi di accensione e di spegnimento dei due mos di test.

L’ultima simulazione, di seguito riportata in figura 4.43, è servita per verificare i vincoli di frequenza una volta abilitata l’oscillazione. Il grafico riporta gli andamenti dei segnali Ref, che corrisponde all’uscita del settimo inverter del ring, e f_ref, ottenuto dopo il divisore di frequenza per otto e che servirà come

riferimento. La simulazione è stata eseguita sulla vista extracted e nelle varie condizioni di lavoro: tipical, worst speed, worst power.

Figura 4.43: andamento dell’uscita Ref del settimo inverter del ring oscillator e del segnale f_ref

di riferimento esterno.

In tabella 4.5 si possono leggere i valori di frequenza e periodo per i segnali Ref, f_ref calcolati durante queste simulazioni.

TM WS WP

Tensione T (ns) f (MHz) T (ns) f (MHz) T (ns) f (MHz)

Ref 1,004 995,53 1,52 657,28 0,62 1611

f_ref 8,036 124,44 17,03 58,70 4,96 201,42

4.7.7 Layout del circuito impulsatore

La parte full custom del layout è riportata nelle tavole finali. Questa è formata da due delle solite strisce tipiche dei ring oscillator, alle quali sono state affiancate le due pass-gate e le porte Inv15 e Inv30 del buffer, in modo da compattare la struttura. I mos di test M1, M2 sono stati posizionati in basso a sinistra per isolarli il più possibile dal resto del circuito, evidenziando la loro emissione. I contatti di substrato di questi transistor, poi, sono stati posizionati vicino ai rispettivi canali e lasciati indipendenti dal substrato del resto della struttura, al fine di poterne misurare la debole corrente. Infine, le piste di metal dei terminali di drain e source sono state dimensionati sulla base dei valori di corrente media che le attraversano, ottenuti dalle simulazioni in condizioni worst power e con tensioni di polarizzazione massime.

4.8 Amplificatore operazionale

4.8.1 Realizzazione

Per completare il quadro delle strutture di test, oltre a quelle appena viste, si è pensato ad un circuito puramente analogico, come un amplificatore operazionale. Le misure verranno effettuate sia con la camera CCD, per rivelare i mos in condizioni di emissione, sia con lo SPAD, quest’ultimo verrà puntato sulle varie regioni dell’amplificatore. L’operazionale verrà osservato in condizioni di riposo e, poi, sia ad anello aperto, in funzionamento a comparatore, sia quando è chiuso in reazione e in ingresso si applica un segnale come una sinusoide o una rampa. Quando si effettuano le misure di timing con lo SPAD, come segnale di riferimento potrà essere utilizzato uno dei due ingressi o l’uscita dell’amplificatore.

Per la realizzazione di questa struttura si è pensato ad uno schema circuitale piuttosto semplice a due stadi. Come caratteristiche doveva essere veloce, si è quindi cercato di mantenere tutte le lunghezze di canale minime, e con escursione della tensione di uscita massima, ovvero con Vout variabile su tutto il range

(0,VDD); infine, ci siamo posti come obbiettivo quello di ottenere un guadagno di qualche migliaio.

Gli stadi che si sono impiegati, dopo una bias chain iniziale per la polarizzazione, sono un differenziale di ingresso, seguito da un source comune, per consentire la massima escursione dell’uscita. In un primo momento, si è inserito un stadio differenziale semplice, ma il guadagno ad anello aperto non soddisfaceva le specifiche richieste, per cui è stato sostituito da uno stadio differenziale cascode. L’amplificazione dello stadio differenziale, infatti, è proporzionale alla sua resistenza di uscita e, nei due casi, questa passa dal parallelo tra rdn e rdp a quello tra (gmp⋅rdp)⋅ e (rdp gmn⋅rdn)⋅ . rdn

Lo schematico definitivo è quello di figura 4.44. Per fissare il punto di riposo, si è imposta una tensione di modo comune pari a 1,5 V ed una corrente totale nel differenziale di circa 2 mA.

Figura 4.44: schematico dell’amplificatore operazionale realizzato.

La funzione della bias chain è quella di imporre una corrente sia nello stadio differenziale che in quello di uscita per mezzo di uno specchio multiplo sul pMOS più in alto dei tre transistor della catena. Dimensionando opportunamente i tre transistor, si è, quindi, fissata una corrente nella bias chain di poco inferiore ai 2 mA, e da qui, con uno specchio a pMOS da W=300 µm e L=0.6 µm, si è fissata la

stessa corrente di riposo nel differenziale. I mos di quest’ultimo sono stati dimensionati in modo da trovarsi tutti in condizioni di saturazione con una corrente pari alla metà di quella specchiata.

L’uscita Vd del differenziale va sul traslatore di livello, in cui scorre una corrente imposta dal secondo specchio che sta in rapporto di 1:6 con quella della bias chain, per cui il pMOS in alto sarà di 50 µm, ovvero sei volte più piccolo.

Essendo interessati ad ottenere un’escursione massima per il segnale di uscita, le dimensioni dello stadio finale sono state scelte in modo che, in condizioni di riposo, la Vout sia la metà della tensione di alimentazione, e dunque 1,65 V. I valori di tensioni e correnti a riposo sono osservabili in figura 4.45.

4.8.2 Caratteristiche

Una volta polarizzato l’amplificatore, è stata fatta tracciare al simulatore la risposta in frequenza, per valutarne l’amplificazione. Dalla curva di figura 4.46 si è calcolato un guadagno ad anello aperto di 6352, pari a 76 dB, su una banda di 2,6 MHz.

Figura 4.46: risposta in frequenza dell’amplificatore operazionale.

E’ stata poi fatta tracciare al simulatore la dinamica di uscita, dalla quale è possibile risalire alla regione di linearità. Sui due ingressi non invertente ed invertente sono state applicate due sinusoidi di ampiezza pari ad A/2 e –A/2 rispettivamente, e con frequenza di 5 Hz, a cui corrisponde un periodo T=0,2 s. L’uscita Vout è stata simulata al variare del parametro A nel range (-3 mV , 3 mV) ed è stata tracciato l’andamento dell’ampiezza della sinusoide di uscita in

funzione di A, ottenendo la curva di figura 4.47. Da questa si è ricavata l’ampiezza massima del segnale differenziale per la quale si ha un comportamento lineare dell’amplificatore, e vale circa A =200µV .

Figura 4.47: dinamica di uscita dell’amplificatore operazionale.

A livello di layout, visibile nelle tavole finali, i transistor sono stati disegnati tutti con struttura interdigitata, spezzando un unico grande gate in tanti gate più piccoli in parallelo. Questo è stato fatto per due motivi: compattare la struttura, evitando di avere un aspect ratio troppo basso, e velocizzare le commutazioni dei mos, in quanto su un gate troppo lungo comincia a farsi sentire la resistenza del polisilicio, introducendo un ritardo sulla formazione del canale.

Particolare attenzione è stata posta nella realizzazione degli specchi per la polarizzazione: i tre pMOS sono stati frammentati tutti con gate della stessa lunghezza, in modo da ottenere i primi due esattamente uguali e con il terzo di dimensioni pari ad un sesto del primo. In questo modo si riducono gli errori di matching.

Per quanto riguarda lo stadio differenziale di ingresso, le quattro coppie di mosfet sono state disegnate ognuna con due coppie di transistor in parallelo, di larghezza pari alla metà della larghezza originale. Queste ultime sono state posizionate con configurazione baricentrica, come mostrato in figura 4.48 per una generica coppia di transistori MA, MB, fornendo una simmetria geometrica allo stadio.

La funzione di questa disposizione è quella di ridurre un eventuale offset in ingresso. L’obiettivo è quello di minimizzare l’errore di matching, avvicinando i dispositivi tra loro e rendendoli uguali il più possibile. In questo modo, infatti, i quattro mosfet sono in grado di compensare eventuali variazioni di parametri, come il drogaggio del substrato.