9.1

Introduzione

L’altra via per la realizzazione dell’azionamento ´e la soluzione custom, pro-gettata e sviluppata secondo le necessit´a del committente. Nelle sezioni di questo capitolo si argomenta la scelta dei dispositivi elettronici proposti.

9.2

DSP

´

E l’acronimo inglese di Digital Signal Processor, utilizzato su larga scala in tutte le applicazioni domestiche, industriali e militari. Il suo impiego ha per-messo la forma digitale di televisioni, macchine fotografiche e cellulari. Un attento venditore alla domanda del cliente:’ Perch´e vendete prodotti digita-li’ risponde ’Utilizzano dei DSP, questa ´e la garanzia di una perfetta qualit´a’.

9.2.1 Cosa ´e?

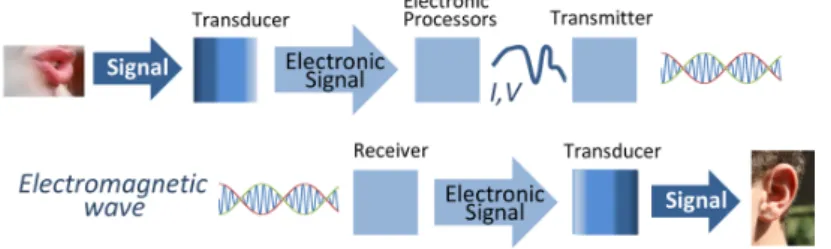

Un DSP1 ´e un rapidissimo computer miniaturizzato in un chip, risulta ot-timizzato per il rilevamento, processo e generazione di segnali reali come voce, video, etc in tempo reale. Tutto questo implementato in un singolo chip delle dimensioni da 0.2 cm2 a 4 cm2.

In contrasto con un microprocessore (termine pi´u di uso comune), il quale tradizionalmente ´e qualcosa di meno potente di un computer e svolge compi-ti ausiliari come il controllo della tascompi-tiera, raffreddamento, etc. Attualmente molti DSPs hanno incorporato delle funzioni che prima erano dei micropro-cessori. La maniera migliore per distinguere l’uni dagli altri ´e quella della distinzione in base al tipo di applicazione. Infatti i DSP lavorano in quelle situazioni dove ´e richiesto un’elevata capacit´a di calcolo a velocit´a elevate.

Figura 9.1: Trattamento digitale del segnale

9.2.2 Cenni Storici

Il DSP nel campo accademico ´e qualcosa di relativamente nuovo, ma in am-bito industriale ´e molto conosciuto.

Lo sviluppo di questo dispositivo ´e iniziato nel 1960, ma era dedicato ad applicazioni particolari dato l’elevato costo. L’impiego industriale inizi´o nel 1970 quando fu reso economicamente vantaggioso il suo impiego. Il lancio del 2920 della Intel fu il punto di svolta per il lancio dei DSP su larga scala. Si trattava di un 40-pin DIP con EPROM, RAM, convertitori A/D e D/A con il quale era possibile per esempio realizzare un modem full-duplex a 1200 bps. Successivamente la Texas Instruments mise sul mercato il TMS32010 successore texano del 2920.

Attualmente il mercato offre DSP con delle prestazioni non paragonabili con il passato, una delle punte di diamante della casa texana ´e il TMS320C66x dotato di multiprocessore, RAM, elevato numero di A/D e D/A con la ca-pacit´a di svolgere calcoli in virgola mobile ad elevate velocit´a.

Il mercato dei DSP ´e il pi´u rilevante in termini di crescita, nel 2013 si ´e avuto un aumento del fatturato del 4%.

9.2.3 Scelta del DSP

Il controllo dell’azionamento deve essere svolto in modo tale da garantire i tempi di risposta previsti. Le operazioni di calcolo necessarie dovranno es-sere svolte con tempistiche tali da non influire sul comportamento dinamico richiesto. Quanto detto si sposa con la definizione di controllo in real-time

2, la Texas Instruments, leader nel settore elettronico, offre sul mercato la

gamma C2000. Si tratta di una categoria di DSP a 32 bit ad elevate presta-zioni progettati per il controllo in real-time. Sia l’hardware che gli algoritmi di calcolo sono stati ottimizzati per avere la massima affidabilit´a, flessibilit´a e velocit´a. L’obiettivo perseguito ´e stato quello di un equilibrio tra costo dell’hardware e capacit´a di calcolo. La serie PICCOLO�´e dedicata alle

ap-2Tempo reale, un termine utilizzato in ambito informatico per indicare quei programmi

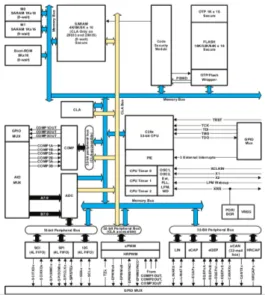

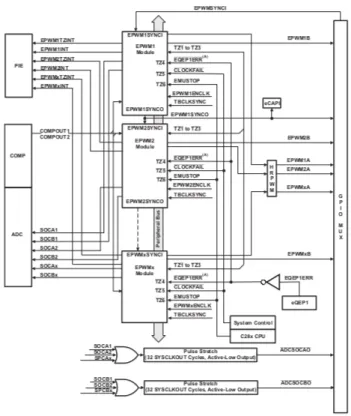

Figura 9.2: Schema funzionale

plicazioni in campo Automotive, PLC, Inverter , LED lighting. Il processo di scelta ha portato ad individuare il TMS320F28035.

9.2.4 Specifiche tecniche

Di seguito si riportano le caratteristiche principali del TMS320F28035, per informazioni pi´u dettagliate si rimanda agli appositi datasheet.

� Frequenza di clock 60-90 Mhz � Memoria flash da 256 kB � 16 ingressi per ADC da 12bit � 14 uscite PWM da 16 bit

� Sottomodulo dedicato all’encoder � Design compatto

� Prezzo economico

In figura 9.2 si riporta lo schema funzionale del DSP ed in figura 9.3 la piedinatura.

Per lo svolgimento dei calcoli matematici si adotta la libreria IQmath appositamente progettata per le applicazioni in real-time. Le funzioni svi-luppate in C/C++ garantiscono le massime velocit´a di calcolo ed allo stesso

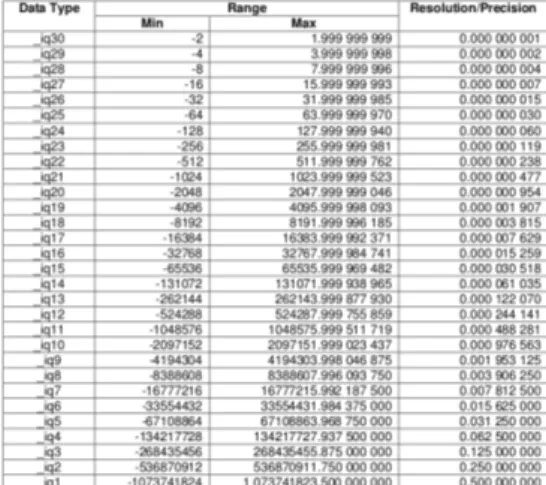

Figura 9.4: Tabella riassuntiva dei dati in formato IQ

Figura 9.5: Kit per applicazioni real-time

tempo precisione ed affidabilit´a. Gli input/output delle funzioni IQmath so-no dati in virgola fissa tipicamente a 32bit con un numero di bit dedicato alla parte frazionaria che varia da 1 a 30. La convenzione della casa produttrice contraddistingue il dato con il prefisso IQ seguito da un numero da 1 a 30. In figura 9.4 si riporta una tabella riassuntiva sul range e la precisione per ogni tipo di dato. La scheda che costituir´a il governo dell’azionamento dovr´a essere corredata con l’apposita elettronica ausiliaria per il pre-trattamento dei segnali, stabilizzazione dell’alimentazione, circuiti di reset e di intervento in caso di guasti. Di seguito si tratter´a le principali problematiche legate alla progettazione del firmware lasciando a futuri approfondimenti il design e dimensionamento della scheda.

9.2.5 Moduli e sottomoduli

Dalla figura 9.2 si nota la struttura modulare del DSP, non si entra nel dettaglio del funzionamento di tutti i moduli presenti, rimandando ai data-sheet. Di seguito si tratta il modulo dedicato alle periferiche in particolare i sottomoduli ADC, ePWM, eQEP e GPIO.

Figura 9.6: Configurazione dei pin per l’ADC

Figura 9.7: Schema elettrico per il campionamento

ADC

In figura 9.6 si riporta la configurazione dei pin per quanto riguarda il con-vertitore analogico digitale. Dalla figura si nota come il costruttore ha di-stinto i canali riservati all’acquisizione simultanea e singola. Per esempio i gli ingressi ADCINA0 e ADCINB0 possono essere campionati in modalit´a simultanea, questo garantisce il pi´u piccolo ritardo possibile tra i due cam-pionamenti. La funzione descritta trova impiego nel campionamento delle correnti, le quali insieme influiscono sulla stima dello stato, per cui devono essere per quanto possibile sincronizzate tra di loro.

Il segnale viene applicato al DSP secondo lo schema in figura 9.7. L’ampiezza del segnale dovr´a essere compatibile con il range dell’ADC, il quale pu´o essere modificato imponendo dall’esterno il valore di VREF LO. In questo elaborato

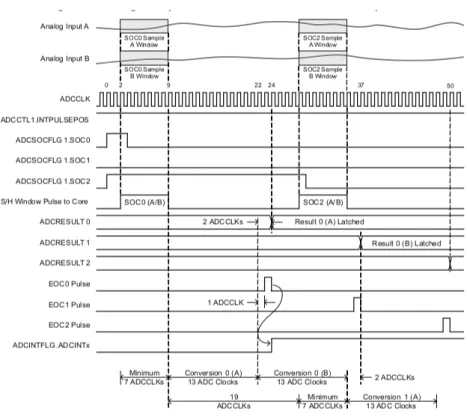

Figura 9.8: Sample time al variare della durata della finestra rilevata dall’ADC si pu´o ricavare il valore digitale campionato con la 9.1.

V alore digitale = 212·Ampiezza segnale

3.3 (9.1)

Il principio di funzionamento si basa sui SOC3. La configurazione del SOC pu´o essere fatta per singolo canale, si pu´o configurare quale evento decide l’inizio della conversione (trigger source), il canale utilizzato e la durata della finestra di conversione. Gli eventi di trigger possono essere:

� Software immediate start � ePWM 1-8

� GPIO XINT2 � CPU Timers 0/1/2 � ADCINT 1/2

Il circuito di misura prevede una resistenza in serie ad ogni gamba dell’inver-ter per il rilievo della c.d.t4, dalla quale risalire alla corrente che la percorre. Questo implica la necessit´a di coordinare il rilievo con i movimenti della val-vola per evitare errori sistematici di misura. Quanto detto pu´o essere svolto con un evento di trigger determinato dall’ ePWM.

L’altra impostazione fondamentale ´e la durata della finestra di conversio-ne. A seconda del circuito che viene connesso al sample and hold, possono cambiare le dinamiche con le quali si apprezza la variazione del segnale. Le ipotesi fatte sull’impianto di misura, privo di elementi reattivi rilevanti, por-ta a concludere che il tempo di trasferimento della carica nel condensatore Ch sar´a relativamente piccolo, si sceglie una finestra da 7 cicli di clock

(AC-QPS=6). In figura 9.8 si riporta il tempo impiegato per rilevare un campione a seconda della finestra. Ultimato il processo di rilevamento, il dato viene convertito ed inviato nell’apposito registro dei risultati a 16 bit di cui solo i primi 12 costituiscono il risultato. Quanto detto fino adesso si riassume in figura 9.2.5 dove sono evidenziate le fasi del processo di acquisizione.

3Starts of conversions 4Caduta di Tensione

Figura 9.9: Registro del risultato

Figura 9.11: Diagramma funzionale per il modulo ePWM ePWM

Il modulo dedicato alle uscite PWM ´e dotato di sette uscite per ognuno dei due canali. Le parti principali di questo modulo sono:

� Timer Base � Counter-compare � Action Qualifier

In figura 9.2.5 si riporta il diagramma funzionale per questo modulo. I principali parametri da configurare sono:

� Valore massimo del dente di sega o triangolare. � Valore di confronto.

� Modalit´a di generazione del PWM.

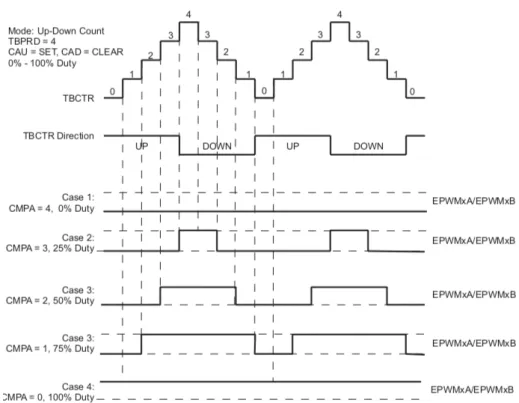

Il principio di funzionamento si basa sul confronto tra il contatore (TBCTR) e un valore di riferimento (CMPA). Quando il registro del contatore contiene

In figura 9.2.5 si riporta un esempio di creazione di un’onda rettangolare phase-correct con duty cycle variabile. Il valore di TBPRD indica il numero massimo che si raggiunge alla fine del conteggio di conseguenza il periodo della portante. Il TBCTR incrementa di un’unit´a ad ogni ciclo di clock. Nel caso in esame si cerca di costruire un segnale con frequenze dell’ordine dei 4 kHz. Nei calcoli che seguono si ipotizza un clock del DSP a 60 Mhz ed una modalit´a Up-Down.

TP W M = 2· (T BP RD + 1) · prescaler · TCLK = 2· (212+ 1)· 2 ·

1 60· 106 =

= 2.7313· 104⇒ fP W M = 3661Hz (9.3)

I valori di prescaler per questo DSP valgono: /1, /2, /4, /8, /16, /32, /64, /128.

Per qualunque altra informazione si rimanda al documento SPRU791F della Texas Instruments.

eQEP

Il modulo eQEP si interfaccia con encoder incrementali lineari o ruotanti e risulta in grado di fornire posizione, direzione e velocit´a della macchina per tutti i sistemi di controllo del movimento.

Nel caso specifico riceve in ingresso i segnali da un encoder incrementa-le in quadratura (figura 9.32). Tipicamente il disco dell’encoder compie una rivoluzione ogni giro del motore, questo significa che esiste una stretta correlazione tra la frequenza dei segnali in ingresso e la velocit´a della mac-china. Quest’ultimi devono essere connessi agli ingressi QEP1A/XCLK e QEP1B/XCLK. In figura 9.2.5 si riporta il digramma a blocchi funzionale del modulo.

Il dato relativo alla posizione viene memorizzato nel registro QPOSCNT, QPOSINIT contiene il valore iniziale mentre attraverso QPOSMAX si im-posta il valore massimo conteggiato dopodich´e si azzera il contatore. In un movimento circolare questo si pu´o assumere ad aver raggiunto i 2π radianti corrispondenti a 0.

Per qualunque altra informazione si rimanda al documento SPRUFK8 della Texas Instruments.

Figura 9.12: Principio di funzionamento del PWM

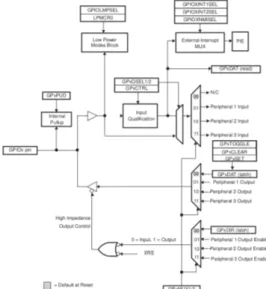

Figura 9.14: Selezione della funzione del generico pin

GPIO

Si utilizza questo modulo per agire sulle porte digitali del DSP, ogni pin ap-partenente al GPIO pu´o operare da ingresso o uscita a seconda di come sono configurati i relativi registri. Il processore supporta 45 GPIO pins, disposti su due porte A e B. Ognuno di questi pin pu´o asservire a pi´u periferiche, cio´o viene gestito da appositi multiplexer, come in figura 9.14. La funzione svolta dal PIN si imposta agendo sul registro GPAMUX1, 2 o GPBMUX1, in tabella 9.15 si riportano tutte le modalit´a di funzionamento dei pin della porta A.

Per quanto riguarda la funzione I/O digitale, si deve agire sui registri GPA-PUD, GPBUD per abilitare o disabilitare il pull-up, su GPADIR e GPBDIR per selezionare la direzione fra input o output. In figura 9.16 e 9.17 si riporta i registri da configurare.

Nel caso si connetta il quadro comandi al DSP sono necessari almeno tre di input ed uno di output, da ricercare inutilizzati. Nella libreria Embedded Coder sono presenti dei blocchi con i quali si pu´o utilizzare le porte I/O del DSP.

9.3

Strumenti utilizzati

Il DSP svolge le operazioni scritte nell’apposito codice, la cui stesura pu´o venire eseguita in almeno due metodi:

Figura 9.15: Multiplexer porta A

Figura 9.16: Configurazione della direzione del pin

2. Architettura del programma.

3. Codifica del programma in linguaggio macchina. 4. Implementazione hardware.

Vista la complessit´a del primo si adopera il metodo Assistito figura 9.3, il quale porta i seguenti benefici:

� I linguaggi di alto livello forniscono tempi di sviluppo molto contenuti. � La distanza concettuale fra l’analisi e l’implementazione si riduce, con conseguente riduzione del rischio di non corretta traduzione delle specifiche in codice.

� Gli errori logici si individuano pi´u facilmente, essendo espressi nella logica del dominio del problema.

� Si evitano per lo pi´u gli errori macchina che sono intercettati e segnalati opportunamente dal linguaggio di alto livello.

� I tempi di esecuzione si migliorano con l’efficienza degli algoritmi non eseguendo velocemente algoritmi inefficienti.

� I profiler forniscono informazioni dettagliate su quali siano i colli di bottiglia, si valuter´a se ´e necessario tradurne o riscriverne quelle parti in linguaggi di programmazione che ne consentano una esecuzione pi´u rapida, avendo gi´a ottenuto e verificato specifiche chiare e certe.

9.3.1 Ambiente Real-Time Workshop

Matlab�Simulink mette a disposizione uno strumento per la compilazione automatica di codice C/C++ direttamente dal diagramma a blocchi. Que-sto permette l’esecuzione di simulazioni nel continuo, discreto e ibrido con la possibilit´a di interconnettere parti hardware allo schema a blocchi. Le principali caratteristiche del Real-Time Workshop sono:

� Rapidit´a di costruzione, debug e implementazione dell’algoritmo pro-gettato.