Capitolo 3

Stadio di potenza

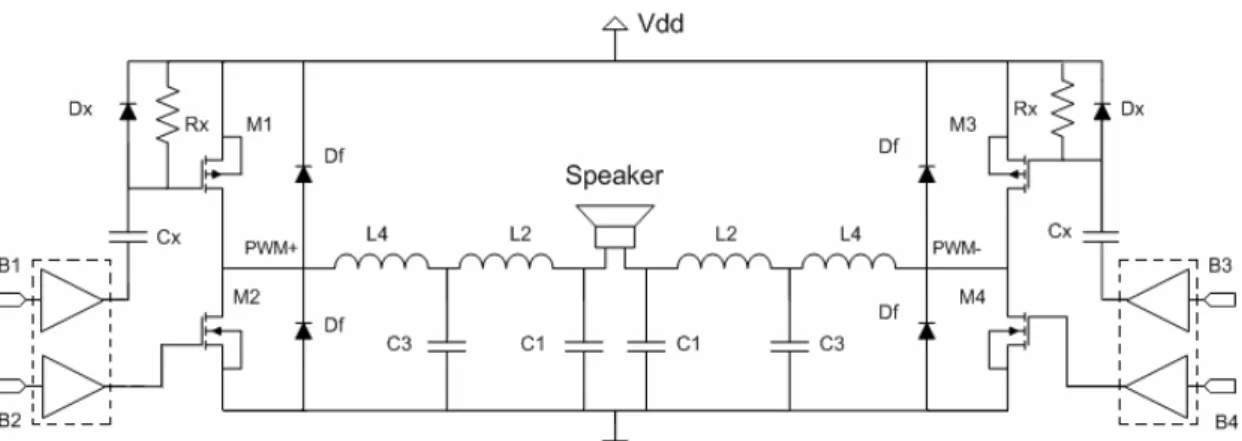

Lo stadio di potenza è la parte dell’amplificatore nella quale avviene la vera e propria amplificazione del segnale. Uno schema molto semplificato dello stadio di potenza, utile per capirne il funzionamento, è il seguente:

Figura 3.1: Modello funzionale dello stadio di potenza

Il meccanismo con cui avviene l’amplificazione del segnale di ingresso è semplice. I transistori di potenza (rappresentati in Figura 3.1 dallo switch) vengono pilotati per mezzo di un segnale PWM che ha dinamica tipicamente di 5 V (o 10 V) e supponendo di volere in uscita una potenza massima di almeno 70 W, lo stadio di amplificazione può essere alimentato (vedi VDC) con una tensione ad esempio di 50 V; essendo le perdite sui

MOSFET molto piccole, in ingresso al filtro passa basso di uscita c’è un segnale modulato ad impulsi di dinamica di poco inferiore a 50 V, ossia 10 (o 5) volte maggiore

di quella del segnale di ingresso.

Ovviamente lo stadio di potenza da noi simulato è più complesso di quello rappresentato in Figura 3.1, ma il principio di funzionamento è praticamente lo stesso. In particolare, allo scopo di evitare la presenza di tensioni di offset sul carico in assenza di segnale audio, abbiamo utilizzato per l’amplificazione uno stadio a “doppio inverter”, formato cioè da due coppie di MOSFET complementari collegate in configurazione Full-Bridge (Figura 3.2); questo tra l’altro garantisce un fattore di amplificazione complessivo pari a 10 con una tensione di alimentazione di soli 25 V, che idealmente permette di avere una potenza massima sul carico di circa 78 W. Le uscite degli inverter sono quindi filtrate passa-basso ed il segnale audio così ricostruito è mandato sul carico (l’altoparlante).

La scelta di utilizzare i MOSFET e non altri tipi di transistori (come i BJT ad esempio) è dovuta alle loro caratteristiche, che li rendono molto più vicini ad uno switch ideale: sono componenti che funzionano con portatori maggioritari e questo minimizza i tempi di commutazione; inoltre la natura resistiva di tali componenti quando sono in conduzione ed in particolare il valore limitato delle RdsON fornisce una buona linearità

ed una bassa impedenza di uscita. Per queste ragioni e per la semplicità di pilotaggio (sono dispositivi comandati in tensione e non in corrente) è quindi ragionevole preferire i MOSFET nella realizzazione dello stadio di potenza degli amplificatori audio.

3.1 Pilotaggio dei transistori

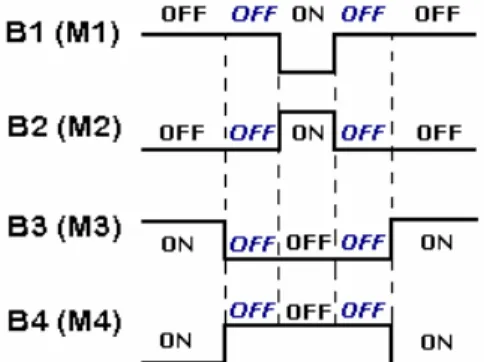

Il pilotaggio dei MOSFET è diverso a seconda se il modulatore è 2-state o 3-state. Facendo riferimento alla Figura 3.2, consideriamo per il momento il primo caso, più semplice: in corrispondenza di un livello alto del segnale PWM generato dal modulatore, M1 e M4 sono spenti (OFF) e M2 e M3 sono in forte conduzione (ON); viceversa, se il segnale PWM assume un livello basso, M2 e M3 sono OFF e M1 e M4 sono ON. Supponiamo ora che il modulatore sia di tipo 3-state; in tal caso, come abbiamo visto in dettaglio nel Capitolo 2, i segnali generati sono due, y1 e y2, e vengono utilizzati entrambi per comandare opportunamente i transistori. In particolare, chiamando Vi il

segnale PCM in ingresso al modulatore e considerando che Nword=128 corrisponda al nostro ‘0’, abbiamo la seguente situazione: quando Vin>0 si usa y1 per modulare accensione e spegnimento di M1 e M2 (come nel caso precedente per M1 e M3), si impone M3 spento e M4 acceso; quando Vin <0 si usa y2 per modulare M3 e M4, imponendo M1 spento e M2 acceso; infine, se Vin =0 si impone M1 e M3 spenti e M2 e M4 accesi, in modo da cortocircuitare il carico. Andando quindi a misurare (PWM+

-PWM-) si vede un segnale “damped ternary modulated”. La tabella seguente riassume

quanto appena detto:

Vin>0 Vin=0 Vin<0 M1(p) modulato (y1) OFF OFF M2(n) modulato (y1) ON ON M3(p) OFF OFF modulato (y2) M4(n) ON ON modulato (y2)

Tabella 3.1: Modo di funzionamento dello stadio di potenza a doppio inverter in un amplificatore

con modulazione PWM tri-state

La tensione minima da applicare ai gate dei transistori a canale n per mandarli in forte conduzione, facendo ad esempio riferimento alla categoria degli OptiMOS della Infineon [23], può essere anche di soli 4.5 V, sia per transistori a canale n che per quelli a canale p. Per quanto riguarda i secondi in particolare va sottolineato che è possibile comandarli con gli stessi livelli di tensione usati per gli nMOS, semplicemente utilizzando un particolare accorgimento circuitale di “traslazione di livello” (vedi Dx ,Rx e Cx in Figura 3.2); in caso contrario, dato che hanno il source collegato all’alimentazione, occorrerebbe una tensione di gate molto alta (di 25 V!) per portarli in interdizione. Vediamo in dettaglio in cosa consiste il circuito suddetto, facendo riferimento al MOSFET a canale p M1 di Figura 3.2: terminato il transitorio iniziale, Vg1 (tensione sul gate di M1) si porta a 25 V e il pMOS è interdetto, essendo Vgs=0; inoltre supponiamo di partire con VB1=0 (VB1 è la tensione sull’ingresso B1). A seguito

della transizione da 0 a 5V di VB1, la tensione sul gate di M1 si porta istantaneamente a

30 V e Dx entra in conduzione; dopo pochi istanti quindi Vg1 si porta a 25 V +Vγ e il

pMOS rimane spento. Supponiamo ora che Vγ sia molto bassa, ad esempio 0.3V e che il pMOS possa andare in forte conduzione con ⏐Vgs⏐≥4.5 V. Sotto queste ipotesi, non appena VB1 passa da 5 a 0 V, Vg1 passa istantaneamente a (25+Vγ)V –5 V, cioè a circa

20.3 V. Ecco che ora la Vgs1 vale –4.7 V, sufficiente a mandare M1 a ON.

Grazie alla circuiteria appena descritta e al corretto dimensionamento dei componenti (valori di Cx e Rx possono essere ad esempio dell’ordine di 0.1 µF e 250 kΩ) è possibile pilotare in modo abbastanza semplice i transistori; negli amplificatori con modulazione PWM a due livelli ad esempio per pilotare M4 e M3 basta utilizzare i segnali invertiti che comandano rispettivamente M1 e M2. Occorre precisare comunque che a seconda della tecnologia utilizzata per sintetizzare la sezione digitale degli amplificatori non è possibile raggiungere dinamiche di 5 V per i segnali di comando dello stadio di potenza. Inoltre per garantire maggior affidabilità nel funzionamento dei transistori spesso si preferisce pilotarli con tensioni bipolari (variabili ad esempio tra –5V e +5V), in modo che la maggiore dinamica permetta di mandarli in una conduzione “più forte”; in tal caso però è necessario usare il circuito “traslatore” (costituito da Cx, Rx e Dx) anche per i MOSFET a canale n. Per adattare il segnale generato dal modulatore digitale alle esigenze dello stadio di potenza e per essere certi di poter riprodurre correttamente impulsi anche di breve durata, solitamente quindi si fa precedere lo stadio di amplificazione da un opportuno stadio di bufferizzazione, caratterizzato da un’impedenza di uscita molto bassa.

Figura 3.2 : Stadio di uscita Full Bridge

3.2 Errori introdotti sul segnale PWM

Il fatto che con M1 o M3 in conduzione l’alimentazione arrivi direttamente in ingresso al filtro passa basso di uscita comporta che eventuali disturbi ad essa sovrapposti li ritroviamo rispettivamente su PWM+ o PWM- (vedi Figura 3.2) e ciò provoca ovviamente degrado del segnale audio di uscita.

In effetti, lo stadio di potenza introduce vari tipi di disturbi, provocati non solo da fluttuazioni dell’alimentazione ma anche da non idealità relative ai MOSFET.

Un altro esempio lo abbiamo già visto a proposito dell’ introduzione degli intervalli di guardia in fase di modulazione e consiste nei tempi di commutazione dei transistori, che non solo sono diversi da zero, ma non sono neppure uguali tra loro.

Prendiamo ora in esame tutte le cause di errore relative allo stadio di potenza, in modo da capire anche quanto sia importante utilizzare, specie negli amplificatori con modulazione PWM a due livelli, un anello di feedback per ridurne al massimo l’influenza sul segnale audio.

Gli errori di cui è affetto il segnale PWM amplificato sono relativi sia alla ampiezza degli impulsi che alla loro durata. Tali errori possono essere quindi divisi in due categorie [6],[14], che riportiamo di seguito insieme alle relative cause principali:

Pulse Timing Errors (PTE)

• Tempi di salita e di discesa non nulli (tr,tf)

• Ritardi di accensione e di spegnimento non nulli (td(on) e td(off)) • Dead Time da noi introdotto

Pulse Amplitude Errors (PAE)

• Fluttuazioni dell’alimentazione

• Impedenza finita (diversa da zero) dei transistori di potenza

3.2.1 Pulse Timing Errors

Con PTE indichiamo gli errori relativi allo spostamento indesiderato degli istanti di commutazione degli impulsi.

Tempi di salita e di discesa

I tempi di salita e di discesa, indicati con tr (rise time) e tf (fall time), sono relativi al tempo che intercorre tra l’istante in cui l’uscita dei MOSFET comincia a cambiare e l’istante in cui la transizione è completata. Questi tempi influenzano sia l’ampiezza che la larghezza degli impulsi e quindi possono essere considerati come PTE ma anche come PAE. L’effetto di questi errori è moderato [14] se paragonato alle altre fonti di disturbo, ma pone comunque un limite alla durata minima dell’impulso riproducibile dallo stadio di amplificazione (Cap.2).

Tempi di ritardo (Delay Times)

Con td(on) e td(off) si indicano i tempi di ritardo nell’accensione (turn-on delay) e nello spegnimento (turn-off delay) di un transistore, ossia quei tempi che intercorrono da quando si ha un cambiamento sul segnale applicato al gate di un MOSFET e l’istante in cui tale cambiamento si riflette sul MOSFET stesso. Questi tempi di ritardo sono dovuti alla presenza di capacitá parassite all’interno dei transistori e dipendono dal tipo di transizione che avviene in ingresso ad essi: td(on) e td(off) cioè sono in genere diversi tra loro. Questi tempi sono compresi tra i 5 ed i 20 ns in transistori veloci a canale n e questi valori in assoluto non portano contributi significativi di distorsione sul segnale di uscita. Il problema è che non solo la loro presenza aumenta la durata minima degli impulsi riproducibili dallo stadio di potenza, ma comporta il pericolo di cortocircuito dell’alimentazione durante le commutazioni, con conseguente sovraccarico dei transistori e notevole abbassamento dell’efficienza dell’amplificatore. Per evitare che si verifichino questi cortocircuiti si utilizza i Dead Time.

Dead Time

Per risolvere il problema del cortocircuito dell’alimentazione si modifica il segnale PWM che pilota i singoli MOSFET in modo da garantire, in corrispondenza di ogni transizione del segnale generato dal modulatore, la presenza di un intervallo in cui entrambi i MOSFET di uno stesso inverter sono spenti (da cui il nome “dead time”, cioè “tempo morto”, o “blanking delay”). Se questo intervallo ha durata maggiore del max(td(on),td(off)), allora siamo certi che non si verificheranno casi di cortocircuito dell’alimentazione. La situazione di conduzione e interdizione dei transistori di potenza in presenza dei Dead Time è rappresentata in Figura 3.3, ove in blu sono indicati gli intervalli di “inattività” dei MOSFET.

Figura 3.3: Comandi di pilotaggio per i MOSFET

Volendo in qualche modo quantificare l’effetto dei Dead Time (DT) sulla distorsione armonica del segnale di uscita, si considera il rapporto αd= td/Tw, ove td è la durata del

Dead Time e Tw è il periodo che intercorre tra un impulso ed il successivo. Approssimando l’andamento della corrente di uscita come sinusoidale e considerando la tensione di alimentazione unitaria, la distorsione armonica causata dal Blanking Delay puó essere scritta come serie di Fourier [14], la cui componente m-sima ha ampiezza: 2 ) 2 sin( 2 ) ( π π α m m m Ad = ⋅ d (3.1) 79

Si ricava così l’espressione della THDd , ossia della distorsione armonica totale provocata

dall’ utilizzo di Dead Time di durata td:

π α π π α α 4 2 2 sin 2 ) , ( max 2 2 d N d d d M i i M THD − ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⋅ ∝

∑

(3.2)ove con M si è indicato l’indice di modulazione (di valore compreso tra 0 e 1) del segnale PWM, che nel caso ideale (tg=0; DT=0) è legato alla durata degli impulsi e al duty cycle secondo le relazioni:

M2L =2×(δmax −δmin) (3.3)

M3L =(δmax −δmin) (3.4)

dove gli indici indicano un segnale PWM a 2 o a tre livelli.

L’espressione di THDd è stata ottenuta facendo un’approssimazione significativa, ossia

che la corrente di uscita sia sinusoidale; in realtà tale corrente è affetta da un ripple legato alla qualità del filtro di uscita e pertanto l’espressione trovata è soltanto parzialmente corretta.

In ogni caso è evidente come la modifica del segnale PWM che viene fatta per generare i Blanking Delay comporti nello spettro la presenza di componenti di rumore che contribuiscono al peggioramento della qualità del suono prodotto dall’amplificatore. Al fine di ottimizzarne le prestazioni è quindi necessario capire quale sia il valore ottimale del Dead Time, sufficiente a evitare il cortocircuito dell’alimentazione dovuto ai tempi di ritardo dei transistori ma al tempo stesso non eccessivo, in modo da non introdurre un’elevata distorsione sul segnale di uscita.

I circuiti che abbiamo utilizzato per la generazione dei DT ed i risultati delle simulazioni fatte al variare della loro entità sono riportati nel prossimo capitolo.

3.2.2 Pulse Amplitude Errors

Con PAE si indicano gli errori relativi all’ampiezza degli impulsi. Tipicamente sono causati da un’alimentazione non ideale e da una resistenza diversa da zero negli inverter che costituiscono lo stadio di potenza.

Disturbi dell’alimentazione

Questi disturbi sono presenti in quanto tipicamente le sorgenti di alimentazione utilizzate negli amplificatori audio hanno una banda molto minore di quella degli stessi amplificatori. Il caso peggiore si ha quando come alimentatore si utilizza un trasformatore con un raddrizzatore a ponte seguito da un condensatore; questo tipo di alimentazione è usato spesso sebbene offra le performance peggiori.

Andiamo ad analizzare analiticamente l’influenza dei disturbi dell’alimentazione sul segnale di uscita [14].

Indichiamo con Vs la tensione di alimentazione, con vsp(t) la perturbazione ad essa

sovrapposta e con vo(t) la tensione di uscita.. Sia poi vr(t) la tensione di controllo

dell’amplificatore, supposta sinusoidale e legata all’indice di modulazione dall’espressione:

(

t Mt

vr( )= cosωr

)

(3.5) In pratica vr(t) è il segnale che determina la durata degli impulsi e che contienel’informazione audio (sinusoidale, di pulsazione ωr).

La tensione di uscita è data da [14]: ) ( ) ( ) ( ) ( 0 t v t Vs v t v t v = r ⋅ + r ⋅ sp (3.6)

Se sviluppiamo vsp(t) con la serie di Fourier:

(

)

∑

= = max 0 cos ) ( M m m m sp t A m t v ω (3.7)si puó riscrivere l’espressione del segnale di uscita:

(

)

[

]

∑

= − + + = max 0 0 cos cos( ) 2 1 ) ( M m m r m r m t m t t m t A M t v ω ω ω ω (3.8)Dalla (3.8) si vede quindi che le componenti della perturbazione sovrapposta all’alimentazione intermodulano con il segnale vr(t). I prodotti di intermodulazione

causati dai disturbi dell’alimentazione sono dati quindi da

) 1 ( 2 2 ) 1 ( ) 2 1 ( 2 ) ( 0 max 1 2 0 max 1 2 A A A M MA M IMD M m m M m m + = + ≈

∑

=∑

= (3.9)L’intermodulazione provocata dalla non idealità dell’alimentazione è piuttosto grande, tanto che difficilmente si riesce a realizzare un buon PMA (Pulse Modulating Amplifier) non reazionato se lo stadio di potenza è alimentato con una tensione non ben regolata. L’influenza delle fluttuazioni dell’alimentazione sul segnale di uscita dell’amplificatore audio è misurata dal PSRR (Power Supply Rejection Ration), un parametro che viene spesso specificato nella descrizione degli amplificatori. Ovviamente nel caso di valori elevati di PSRR, l’unico modo di ottenere una buona qualità audio è utilizzare un’alimentazione costosa.

Impedenza finita dei MOSFET

L’errore introdotto dall’impedenza dei MOSFET è dovuto alla caduta di tensione che provocano quando conducono. L’analisi dell’impedenza degli switch è piuttosto complessa e non è stata presa in esame in dettaglio. Per minimizzare questo tipo di errore occorre scegliere transistori caratterizzati da una RdsON il più bassa possibile.

3.3 Simulazione dello stadio di potenza

Il modello utilizzato per lo stadio di potenza nelle simulazioni con MATLAB ha la struttura di quello già visto precedentemente (Figura 3.2), costituito da due inverter a MOSFET e da un filtro passa basso (Figura 3.4).

Per quanto riguarda i MOSFET, va precisato che i pMOS sono stati simulati con nMOS preceduti da un inverter, ma questo non comporta alcuna conseguenza sulla validità dei risultati trovati.

Figura 3.4: Stadio di potenza e filtraggio realizzato in Simulink

Tipicamente gli altoparlanti hanno un’impedenza nominale di 4 o 8 Ω e noi abbiamo scelto come carico RL il valore più basso dei due, dato che un carico minore permette

valori della corrente di uscita maggiori e quindi dal punto di vista dei disturbi durante le commutazioni dei transistori ci siamo messi nella condizione peggiore. Al Cap.5 poi vedremo anche il risultato di qualche simulazione fatta con un carico da 8 Ω.

Scegliere un carico resistivo è un’approssimazione, dato che l’impedenza di un altoparlante reale non è mai puramente resistiva. Il problema è che varia molto in funzione dei parametri circuitali e delle caratteristiche del segnale audio, e questo rende impossibile utilizzare un modello molto preciso. Un discorso analogo va fatto per l’alimentazione: allo scopo di riprodurne l’impedenza di uscita si è usato una resistenza

(vedi Rsp in Figura 3.4) del valore di 1 mΩ, ma anche questa è un’approssimazione in quanto in realtà avremmo dovuto usare un’impedenza ohmico-induttiva.

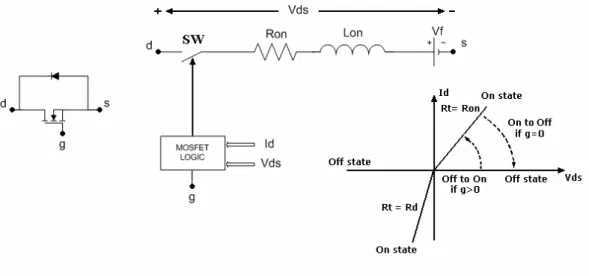

3.3.1 Modello Simulink dei MOSFET

Il modello utilizzato da Simulink per i MOSFET è mostrato in Figura 3.5: il transistore è acceso (ON) quando sul gate viene applicato un segnale positivo e la tensione VDS è

anch’essa positiva; in tal caso il dispositivo presenta una resistenza pari a Rt=Ron, dove Ron (o “RdsON”) rappresenta il valore che tipicamente troviamo sui datasheet e che caratterizza il comportamento dei MOSFET quando sono in conduzione.

Figura 3.5: Modello Simulink dei MOSFET

Un segnale nullo (o meglio non positivo) sul gate comporta invece lo spegnimento (OFF) del transistore, ma solo se la corrente Id è positiva; nel caso infatti che la corrente che lo attraversa sia negativa (ossia fluisce attraverso il diodo parassita posto in parallelo), perché il MOSFET si spenga occorre non soltanto che sul gate il segnale sia nullo, ma anche che il flusso di corrente si interrompa.

A causa della presenza del diodo parassita quindi la resistenza Rt del MOSFET dipende dal verso di percorrenza della corrente che lo attraversa: se la corrente fluisce dal source

al drain (Id<0), significa che in realtà sta attraversando il diodo e pertanto Rt=Rd, dove Rd rappresenta appunto la resistenza interna del diodo. Oltre a Ron e Rd, gli altri parametri che caratterizzano il modello Simulink di un MOSFET sono Lon, Cs e Rs. La Tabella 3.2 riporta quali sono i valori che abbiamo scelto per ognuna delle grandezze che caratterizzano il modello dei transistori.

GRANDEZZA SIMBOLO VALORE on-state resistance Ron 36 mΩ

on-state inductance Lon 10 nH Internal diode resistance Rd 16 mΩ Snubber resistance Rs 10 Ω Snubber capacitance Cs 470 pF Tabella 3.2: Valori dei parametri dei MOSFET utilizzati in fase di simulazione

Ron

I valori scelti per Ron dipendono dai MOSFET che vorremmo utilizzare realmente per l’amplificatore audio; consultando i datasheet di vari OptiMOS della Infineon abbiamo deciso alla fine di utilizzare una Ron pari a 36 mΩ, nonostante si possano trovare facilmente anche MOSFET con valori di Ron inferiori.

Precedenti lavori [10] hanno accertato la quasi totale ininfluenza della Ron sulla THD del segnale di uscita; nonostante ciò abbiamo fatto varie simulazioni variandone il valore nelle quattro architetture prese in esame ed i risultati non sono stati così ottimistici. Come si può vedere nella Tabella 3.3, la modifica di Ron può comportare anche notevoli cambiamenti sulla distorsione del segnale audio; in particolare per AD3, ossia l’amplificatore a catena diretta che utilizza una PWM tri-state, passando da 10 mΩ a 60 mΩ si è riscontrato una variazione della THD del 27% ! Un aspetto interessante da notare è che AD, amplificatore con modulazione PWM a due livelli ma non reazionato, dimostra di essere molto meno sensibile ai cambiamenti di Ron rispetto ad AD3 e

questo fa supporre che anche il tipo di modulazione adoperata influenzi la sensibilità di un amplificatore alle variazioni parametriche dello stadio di potenza.

Ron architettura 10 36 60 AD 0.7320 0.7317 0.6839 AD1 0.3789 0.3965 0.4346 AD2 0.5187 0.5111 0.5201 AD3 0.4595 0.3360 0.3332 Tabella 3.3: Valori di THD% al variare della Ron dei transistori di potenza

(fin=1 kHz, Pout≅70% Poutmax)

Per quanto riguarda l’efficienza degli amplificatori, i risultati delle simulazioni erano prevedibili: ad un aumento della resistenza corrisponde (con qualche eccezione) una diminuzione del rendimento; anche stavolta inoltre le maggiori variazioni sono state rilevate per AD3 (seppure di poco):

Ron architettura 10 36 60 AD 0.9764 0.9663 0.9570 AD1 0.9033 0.8951 0.8870 AD2 0.9579 0.9673 0.9579 AD3 0.9908 0.9793 0.9693 Tabella 3.4: Valori di rendimento al variare della Ron dei transistori di potenza

(fin=1kHz, Pout≅70%Poutmax)

Si osservi comunque che sebbene per AD3 si abbia la maggior diminuzione percentuale di efficienza in corrispondenza dell’aumento della Ron dei MOSFET, i valori restano sempre nettamente più alti di quelli delle altre architetture.

Rd

Rd è la resistenza del diodo parassita che è presente nei MOSFET [26] a causa della loro struttura interna ( Figura 3.6).

Figura 3.6: Diodo parassita in un MOSFET di potenza a canale n

L’estensione dell’area di giunzione di questo diodo comporta elevati valori di “reverse recovery time” (trr) e “reverse recovery current” (Irr) (Figura 3.7), a causa del gran numero di minoritari che devono abbandonare lo strato N- in occasione del passaggio del transistore dalla conduzione allo spegnimento

Figura 3.7: Tempo di recupero di un MOSFET durante la commutazione

Nelle applicazioni ad alta frequenza (come le nostre) si è pertanto costretti a collegare dei diodi raddrizzatori molto veloci (di tipo Schottky) in parallelo ai MOSFET (vedi Df in Figura 3.2), in modo da impedire l’accensione dei diodi parassiti e abbattere così il tempo di recupero dei transistori.

Il valore di Rd lo abbiamo scelto facendo riferimento alle considerazioni riportate in un precedente lavoro sugli amplificatori audio [14], durante il quale è stato utilizzato un modello Simulink dello stadio di potenza.

Come mostrato in Figura 3.4 durante le simulazioni non abbiamo utilizzato alcun diodo in parallelo ai transistori, in quanto l’entità del loro tempo di recupero (10 ns circa) non lo ha reso necessario.

Lon

Per assegnare un valore ragionevole a Lon abbiamo cercato nei datasheet di alcuni MOSFET di potenza il valore delle induttanze di drain e di source (LD e LS), misurate tra

il centro (core) del transistore e l’estremità dei piedini rispettivi, all’esterno del package. Prendendo come riferimento l’IRF530 della Motorola [24], abbiamo scelto una Lon di 10 nH, che corrisponde circa alla somma della LD e della LS.

In fase di simulazione è apparso evidente che il valore Lon è determinante per avere un buon segnale di uscita. Con un ingresso a frequenza 1 KHz abbiamo variato Lon da 10 nH a 1.5 µH; in Figura 3.8 sono riportati i risultati delle simulazioni effettuate con l’amplificatore AD3.

Figura 3.8: Andamento della THD% al variare della Lon dei transistori di potenza

(fin=1kHz, Pout≅70% Poutmax)

Le simulazioni hanno mostrato, per frequenze del segnale di ingresso di 1 kHz, un aumento notevole della THD per valori di Lon maggiori di 500 nH ed in particolare in corrispondenza di 1.25 µH la distorsione superava lo 0.5%.

Questi risultati danno un’idea dell’importanza di una corretta scelta dei parametri del modello Simulink dei MOSFET dello stadio di amplificazione se si vuole che i risultati delle simulazioni rispecchino il più possibile la situazione reale.

Circuiti di snubber

Prendiamo in esame ora le grandezze Cs e Rs (Tabella 3.2); tali parametri sono relativi ad un circuito “di snubber” di tipo RC posto in parallelo ad ogni transistore.

I circuiti di snubber (Figura 3.9) vengono utilizzati in applicazioni switching in cui un transistore si trova a pilotare un elemento induttivo; il loro scopo è quello di controllare le perdite di commutazione. Il problema di fondo è che quando viene interrotta bruscamente la corrente attraverso un’induttanza, si ha a che fare con l’energia che si

trova immagazzinata in essa in quel momento: il campo magnetico non può annullarsi istantaneamente e tende a prolungare lo scorrimento di corrente; questo però è impossibile in quanto il circuito è aperto e quello che si verifica è quindi un aumento sorprendente della tensione ai capi del transistore che funziona come switch.

Figura 3.9: Circuito di snubber RC

In particolare, più rapidamente la corrente viene interrotta e maggiore è il potenziale che si viene a creare, secondo la ben nota relazione

dt

di

L

fem

=

−

(3.10) 89Inoltre in corrispondenza dell’interruzione della corrente in un carico induttivo il campo elettromagnetico nell’induttore può seriamente danneggiare il transistore, in quanto se la frequenza di switching è elevata il sovraccolpo di tensione può attraversare la capacità Cgd che caratterizza ogni MOSFET (Figura 3.10), perforando l’ossido. Un’altra ragione (la prima l’abbiamo vista a proposito dei tempi di recupero) per cui si ricorre spesso a diodi (tipicamente di tipo Schottky) tra source e drain dei transistori di potenza di un amplificatore audio è quindi quella di cortocircuitare le sovratensioni di apertura dei transistori stessi, provocate dal fatto che il filtro rappresenta un carico reattivo.

Figura 3.10: Schema di un MOSFET con le capacità parassite ed il diodo

di protezione in evidenza

In fase di simulazione i dispositivi non possono venire danneggiati e quindi anche per questo l’utilizzo del diodo raddrizzatore di protezione non è stato necessario. Occorre tener presente comunque che nelle realizzazione concrete degli stadi di potenza degli amplificatori audio i diodi in parallelo ai transistori vengono sempre utilizzati.

Questa è la ragione per cui normalmente non si ricorre ai circuiti di snubber, in quanto la loro funzione di protezione è già svolta dai diodi raddrizzatori collegati tra source e drain; inoltre il circuito di snubber ha il difetto di assorbire energia durante l’intero periodo di switching, non soltanto in corrispondenza delle commutazioni, e questo peggiorerebbe le prestazioni dell’amplificatore.

Nel modello Simulink dei MOSFET i circuiti di snubber vengono utilizzati se le simulazioni hanno problemi di convergenza e quindi sono eccessivamente lente. In tal caso la loro introduzione migliora sì la velocità di simulazione, ma ne riduce l’accuratezza, poiché il modello reale dello stadio di potenza non ne prevede la presenza. In Simulink i transistori in conduzione vengono trattati come generatori ideali di corrente e non sono quindi capaci di pilotare un carico serie contenente un induttore puro. Nel nostro caso l’induttore in questione è quello (assunto ideale) del filtro passa-basso di uscita e ponendo Rs infinita, che equivale a scollegare il circuito di snubber, la

simulazione non è che rallenta, non parte. Questo problema può venire alternativamente risolto[14] usando una resistenza Rsim in parallelo all’induttore del filtro, di valore sufficientemente elevato da renderla trascurabile. Essendo tale induttanza di circa 25 µH e scegliendo una Rsim di 1 MΩ, a frequenza 7 kHz la forma d’onda di uscita sarebbe stata notevolmente distorta [14] e solo un valore di 1 GΩ avrebbe risolto il problema; una Rsim così elevata avrebbe comportato però un notevole rallentamento delle simulazioni. Per queste ragioni alla fine abbiamo deciso di ricorrere al circuito di snubber. I valori di default di Rs e Cs sono rispettivamente 10 Ω e 10 nF; un buon compromesso tra la velocità di simulazione e l’accuratezza dei risultati ottenuti è stato raggiunto scegliendo Rs=10 Ω e Cs=470 pF.

3.3.2 Alimentazione dello stadio di potenza

Il modello utilizzato per il circuito di alimentazione dello stadio di uscita comprendeva un generatore di tensione continua del valore di 25 V con in serie una resistenza Rsp che, in base alle considerazioni fatte in [14], è stata scelta da 1 mΩ (vedi Figura 3.4). Allo scopo di valutare l’influenza di variazioni parametriche del circuito di alimentazione sulle prestazioni degli amplificatori, abbiamo modificato ripetutamente la Rsp di AD1 e AD3 ed abbiamo quindi misurato le corrispondenti variazioni della THD del segnale di uscita. I risultati del confronto sono riportati in Figura 3.11.

Gli andamenti mostrano che l’architettura a catena diretta che utilizza una modulazione PWM a tre livelli ha una sensibilità alle variazioni di Rsp molto maggiore rispetto all’amplificatore reazionato con PEDEC: cambiando il valore della resistenza da 1 mΩ a 1 Ω la distorsione armonica percentuale del segnale di uscita (a frequenza 1 kHz) è aumentata da 0.39 a 0.45 (+15%) per AD1 e da 0.336 a 2.53 (7.53 volte maggiore) per AD3. I risultati ottenuti quindi confermano quanto avevamo visto al variare della Ron dei MOSFET, ossia l’importanza della reazione per diminuire la sensibilità dell’amplificatore audio agli errori introdotti dalle variazioni parametriche dei componenti dello stadio di potenza.

Figura 3.11: Distorsione armonica del segnale audio al variare dell’impedenza di uscita

dell’alimentazione (fin=1kHz, Pout≅70% Poutmax).

3.4 Dimensionamento dei MOSFET

Per scegliere dei transistori di potenza adatti allo stadio di amplificazione è necessario innanzitutto accertarsi che siano in grado di sopportare le correnti e le tensioni in gioco nel nostro circuito e che riescano a dissipare potenze sufficientemente elevate.

Nel nostro caso si ricorda che i valori adoperati per l’alimentazione ed il carico erano pari rispettivamente a 25 V e 4 Ω; considerando poi una resistenza Rsp di 1 mΩ ed una RdsON del valore di 36 mΩ per i transistori, il valore della massima corrente che poteva

scorrere attraverso gli inverter in assenza di cortocircuiti dell’alimentazione è dato da:

L ON M R Rsp Rds Vdd Rtot Vdd I + + × = = 2 (3.11)

Per una prima stima della massima tensione che puó esserci ai capi dei singoli transistori di uno stadio di potenza come il nostro, basti pensare che essi funzionano come switch e quindi in entrambi gli inverter del Full Bridge quando uno è acceso l’altro è spento e viceversa; questo comporta (trascurando la resistenza in serie all’alimentazione) una

Vdsmax pari a Vdd. Quanto appena detto però non tiene conto dei fenomeni di

overshooting in corrispondenza degli istanti di commutazione dei transistori; in fase di simulazione abbiamo infatti misurato una Vdsmax di circa 27 V.

A questo punto rimane da vedere come stimare la massima potenza dissipata da ogni MOSFET.

3.4.1 Potenza dissipata dai transistori

Per il calcolo della potenza media dissipata dai transistori [11] occorre tener conto di due componenti: una relativa al passaggio di corrente durante gli intervalli di conduzione (PON), l’altra relativa alle perdite di switching in corrispondenza degli istanti di

commutazione. Questa seconda componente è composta a sua volta da due termini: uno (PRR) che ha a che fare con la “recovery current” (Irr) del diodo parassita del

MOSFET quando si spenge e l’altra (PCOMM) relativa alla corrente che esce dal diodo di

un MOSFET durante l’accensione e che entra nel drain del MOSFET opposto.

Calcolo di PON

Considerando sinusoidale l’andamento della corrente che scorre attraverso un transistore in conduzione ed essendo Vdd la tensione di alimentazione, valgono le seguenti relazioni: 2 2 2 2 M M I Ieff I Ieff = ⇒ = (3.12) ON M ON ON Rds I Rds Ieff P = × = × 2 2 2 (3.13) Calcolo di PCOMM

Facendo riferimento ad un singolo MOSFET, vale che

∫

× × × = × × ×=tcom PWM LOAD COM

COM LOAD PWM COMM dt f Vdd I t t t I Vdd f P 0 (3.14)

ove tCOM è l’intervallo di tempo durante il quale avviene la commutazione e vale approssimativamente il tempo di salita (rise time) nel caso dell’accensione del transistore ed il tempo di discesa (fall time) nel caso dello spegnimento; ILOAD rappresenta il valore

istantaneo della corrente sul carico e lo consideriamo circa costante durante tCOM .

Calcolo di PRR

Per stimare le perdite di recovery facciamo l’ipotesi che la Irr abbia una forma d’onda triangolare con valore di picco IREC. Il tempo durante il quale scorre la corrente inversa di recovery è chiamato tRR e l’energia di recovery JRR. In corrispondenza del

raggiungimento da parte della Irr del suo valore di picco, sul diodo parassita è applicata praticamente la tensione di alimentazione Vdd. Pertanto una stima della JRR è data da:

JRR= (Vdd×IREC ×tRR)/2 (3.15)

Per conoscere le perdite di potenza in un MOSFET dovute al flusso della corrente di recovery, rimane da moltiplicare per la frequenza di switching. Dopo alcuni passaggi, l’espressione (3.15) diventa [11]: 4 2 PWM RR RATE RR f t I Vdd P = × × × (3.16)

dove per definizione

COM LOAD RATE t I dt di I = ≈ (3.17)

Introduciamo ora IAVG, cioè il valor medio del modulo della corrente sul carico;

supponendo che tale corrente abbia andamento sinusoidale, vale che:

π π 2 2 = × × = TOTAL BUS M AVG R V I I (3.18)

Se nella (3.14) sostituiamo la (3.17) e quindi ILOAD2 l’approssimiamo con IAVG2, si ottiene

un’utile stima della PCOMM totale:

RATE AVG PWM RATE LOAD PWM COMM I I Vdd f I I Vdd f P 2 2 2 2× × × = × × × = (3.19)

Calcolo della potenza dissipata da ogni MOSFET

Una stima della potenza dissipata mediamente da un MOSFET in un periodo è quindi data da: ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ × + × × × × × + × = 2 2 2 2 4 2 4 1 2 RATE RR RATE M PWM ON M MOSFET I t I I Vdd f Rds I P π (3.20)

Come avevamo anticipato le perdite di potenza sono date da un termine relativo alla corrente che scorre nei MOSFET quando conducono e da un termine relativo alle perdite di switching. Per avere un’ idea di quanto possa valere PMOSFET abbiamo

supposto di realizzare lo stadio di potenza con quattro MOSFET a canale n; sceltone uno molto veloce [23], abbiamo utilizzato come tCOM il valore peggiore tra il tempo di

salita e quello di discesa ed abbiamo trascurato nella (3.20) il termine con tRR , dato che

QRR era pari a 10 nC e quindi tRR (non riportato) sarebbe stato un valore dell’ordine di

decine di ns.

Vdd RdsON RLOAD Rsp tCOM fPWM

25 V 25 mΩ 4 Ω 1 mΩ 4 ns 352.8 kHz

Tabella 3.5: Valori relativi al nostro modello Simulink dello stadio di potenza

Sostituendo quindi valori riportati nella Tabella 3.5 nelle espressioni precedentemente viste, abbiamo ottenuto i seguenti risultati:

sp LOAD ON M R R Rds Vdd I + + × = 2 =6.17 A s A t I I COM AVG RATE 8 10 82 . 9 ⋅ ≅ ≈ W W PMOSFET ≈(0.476+0.07) ≅0.54

3.4.2 Derating

In fase di progetto la scelta dei MOSFET deve essere fatta assicurandosi che i transistori riescano a sopportare le grandezze elettriche in gioco (tensione, corrente) e a dissipare la potenza necessaria; inoltre occorre fare attenzione che il corretto funzionamento dell’amplificatore sia garantito anche per i valori peggiori (worst) indicati sui datasheet. È una pratica comune scalare (derate) di una certa quantità i massimi valori sopportabili dai transistori [16], in modo da essere veramente certi (maggiore affidabilità) che il circuito che stiamo progettando lavori come previsto e che i MOSFET non si danneggino a causa di qualche fenomeno di overshooting indesiderato.

Generalmente i metodi di derating raccomandati sono:

• Tensione: la massima tensione (impulsi compresi) che puó essere applicata al transistore non deve superare l’ 80% della massima tensione riportata dai datasheet. • Corrente: la massima corrente (impulsi compresi) che puó scorrere nel canale non

deve superare l’ 80% della massima corrente riportata dai datasheet.

• Potenza: la massima potenza dissipata non deve essere maggiore del 50% del valore permesso dalle specifiche in corrispondenza della massima temperatura di funzionamento del dispositivo.

• Temperatura: la massima temperatura operativa di canale non deve superare l’ 80% del valore di Tchmax dichiarato.

È importante sottolineare che sebbene in fase di progetto occorrerebbe considerare i valori di picco anche per la potenza, utilizzando i transistori nel rispetto delle condizioni di derating la potenza dissipata può essere considerata in termini di valori medi.

3.4.3 Scelta dei MOSFET

Precedentemente abbiamo stimato la potenza dissipata mediamente dai transistori considerati [23] per lo stadio di potenza, nell’ ipotesi che fosse costituito da quattro MOSFET a canale n. Noti (Par.3.4.1) anche i valori di Vdsmax (misurato in fase di

simulazione) e di Idsmax(che coincide con quella che abbiamo chiamato IM), possiamo

vedere se nel nostro caso le condizioni imposte dal derating vengono rispettate.

I datasheet del transistore preso in considerazione, il BSO200N03S della Infineon, riportano i seguenti dati:

Vdsmax (V) Idsmax (A) Pdmax (W) Tchmax (°C) θJA (K/W) 30 8.8 2.5 150 50 Tabella 3.6: Valori caratteristici del transistore BSO200N03S

Dove Idsmax è relativa ad una corrente continua (condizione peggiore della nostra).

Applicando l’operazione di derating suggerita al Par.3.4.2, si ha:

Vdsmax (V) Idsmax (A) Pdmax (W) Tchmax (°C) θJA (K/W) 24 7.04 1.25 120 50

Tabella 3.7: Valori caratteristici del transistore BSO200N03S dopo il derating

Dalla Tabella 3.7 si osserva che per il transistore considerato non sarebbe rispettata la condizione per la Vds (Vdsmax(circuitale) < 80%Vdsmax(datasheet)) e questo

provocherebbe una minor affidabilità dell’amplificatore.

Purtroppo però scegliere un componente capace di sopportare tensioni più elevate (come l’ IRF530 della Motorola [24]) comporta non solo RdsON maggiori ma anche

commutazione più lunghe, con conseguente peggioramento delle prestazioni dell’amplificatore in termini rispettivamente di efficienza e distorsione.

Occorre tener presente infatti che la velocità è un requisito fondamentale per i transistori dello stadio di potenza, che sono pilotati da un segnale PWM che ha frequenza elevata (352.8 kHz nel nostro caso); questo provoca numerose commutazioni al secondo per ogni MOSFET ed in particolare per ogni impulso del segnale PWM di comando si hanno due commutazioni per ogni transistore.

Figura 3.12: Forme d’onda reali in ingresso ed in uscita di un inverter a MOSFET

La Figura 3.12 mostra i tempi di commutazione di un MOSFET; a causa della presenza dei tempi di accensione e di spegnimento (ton, toff) c’è la necessità di assicurare che gli impulsi del segnale PWM generato dal modulatore abbiano una larghezza minima, maggiore della somma dei due tempi; solo in questo modo infatti siamo certi che l’inverter non “perda” alcun impulso. Come abbiamo visto nel Capitolo2, per garantire che gli impulsi abbiano una durata minima sufficientemente grande viene utilizzato all’interno del modulatore il Delay Counter, che genera un intervallo di guardia (tg1)

all’inizio di ogni impulso. Sebbene in questo modo si riesca a garantire da parte dei MOSFET la riproduzione di tutti gli impulsi (anche dei più rapidi) generati dal modulatore digitale, il segnale PWM amplificato risulta comunque distorto ed il livello di

distorsione è strettamente legato all’entità dei tempi ton e toff (Figura 3.12).

Ammettendo quindi di voler utilizzare ugualmente i MOSFET che hanno Vdsmax

pari 30 V per la loro maggiore velocità di commutazione, una semplice soluzione per operare in rispetto delle condizioni di derating potrebbe essere quella di diminuire la tensione di alimentazione; in questo modo infatti si riduce il massimo valore di Vds applicato ai transistori, anche se al prezzo di una minore dinamica del segnale di uscita e quindi della massima potenza disponibile (a parità di carico).

3.4.4 Considerazioni termiche

Accertato il rispetto dei vincoli imposti sulle tensioni e sulle correnti in gioco, occorre capire se durante il funzionamento dell’amplificatore possa capitare che la temperatura di canale Tch superi il valore (scalato) di Tchmax.

Sui datasheet viene fornita una curva come quella di Figura 3.13(a), dove TA è la

temperatura ambiente.

Figura 3.13: Andamento della Ptot in funzione di TA per tpulse ≤10 s (a) e modello

termico resistivo del transistore (b)

Prendiamo in considerazione il modello termico rappresentato in Figura 3.13(b), dove TJ è la nostra Tch e le Rth sono le resistenze termiche, anche indicate con θ. In assenza di potenza dissipata e quindi di flusso di calore la temperatura Tch (indicata anche con Tjunction-Tj-) coincide con la temperatura TA e quindi dal grafico riportato si puó

leggere che per il transistore che stiamo considerando TchMAX=150 ºC.

Per valutare se nel nostro caso possa essere raggiunta una temperatuta di giunzione eccessiva per il MOSFET dobbiamo accertarci che valga la seguente relazione:

TA +Pd×θJA <80 Tch% max (3.21)

Sostituendo i valori si ha che:

(25+0.54×50)°C≅52°C <<120°C

Nel caso si ottenesse un valore maggiore della TchMAX (scalata) riportata dai datasheet

significa che per essere sicuri che i MOSFET non si danneggino durante il normale funzionamento dell’amplificatore occorre utilizzare un dissipatore, in modo così da introdurre una θDIS in parallelo alla θCA e abbassare quindi fortemente il valore di θJA.

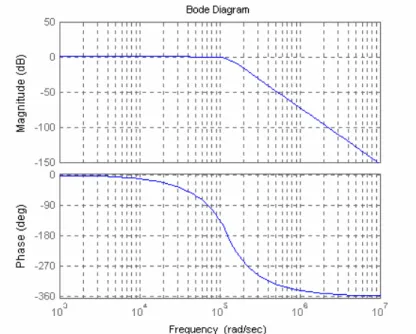

3.5 Filtro di uscita

Il filtro di uscita, come già spiegato nel Cap.2 a proposito del sovracampionamento, serve per ricostruire il segnale audio a partire da quello PWM amplificato dagli inverter a MOSFET. Considerando che il segnale che esce dall’amplificatore viene mandato ad un altoparlante, in teoria il filtro potrebbe anche essere tolto in quanto l’impedenza stessa dell’altoparlante è tale da svolgere una funzione passa-basso. In realtà però l’utilizzo di un filtro progettato in modo opportuno permette di attenuare fortemente il ripple sulla corrente di uscita e di evitare eccessive perdite di energia negli avvolgimenti e nei magneti dell’altoparlante.

Il filtro da noi utilizzato per ricostruire il segnale audio è un filtro di Butterworth del 4° ordine, la cui frequenza di taglio è stata scelta del valore di 20 kHz; in questo modo non solo evitiamo che le componenti spettrali del segnale audio (anche di frequenza elevata) subiscano una eccessiva distorsione di ampiezza e di fase, ma al tempo stesso attenuiamo sufficientemente le componenti indesiderate presenti al di fuori della banda audio.

Al fine di dimensionare correttamente il filtro è necessario conoscere anche il valore della resistenza di carico RL, che nel nostro caso era di 4 Ω.

Per calcolare i valori di induttori e condensatori del filtro di Butterworth è stato quindi sufficiente utilizzare i valori normalizzati della Tabella 3.8, che si riferiscono allo schema circuitale di Figura 3.14.

N C1 L2 C3 L4

2 0.7071 1.4142

3 0.5000 1.3333 1.5000

4 0.3827 1.0824 1.5772 1.5307

Tabella 3.8: Valori normalizzati per i componenti di un filtro di Butterworth di ordine N

Figura 3.14: Schema circuitale di un filtro di Butterworth di ordine 4

Una volta deciso l’ordine del filtro (N=4), sono state utilizzate le seguenti formule di denormalizzazione: T L R coeff L ω ) ( × = ; L T R coeff C × = ω (3.22) dove ωT è la pulsazione di taglio e vale 2πfT.

Imponendo fT=20 kHz, i valori dei componenti, relativamente al circuito di Figura 3.14,

sono:

N C1 (µF) L2 (µH) C3 (µF) L4 (µH)

4 0.7614 34.45 3.138 48.72

Tabella 3.9: Valori dei componenti di un filtro di Butterworth di ordine 4 (fT=20 kHz, RL=4 Ω)

Nel nostro caso però lo stadio di potenza aveva una struttura a Full Bridge (Figura 3.4) e pertanto i valori da utilizzare per condensatori e induttori sono stati rispettivamente il doppio e la metà di quelli riportati in Tabella 3.9:

N C1 (µF) L2 (µH) C3 (µF) L4 (µH)

4 1.523 17.23 6.276 24.36

Tabella 3.10: Valori dei componenti del filtro di Butterworth utilizzato (fT=20 kHz, RL=4 Ω)

Di seguito riportiamo la risposta in frequenza del filtro di uscita, in ampiezza e fase:

Figura 3.15: Risposta in frequenza di un filtro di Butterworth del 4°ordine con fT=20 kHz e RL=4 Ω