4.

VERIFICA.

4.1

INTRODUZIONE.

La descrizione della parte analogica (a radio frequenza) del tag è seguita dalla descrizione del processo che porta a configurare il dispositivo FPGA.

Il funzionamento di un dispositivo FPGA, definito utilizzando il linguaggio di descrizione hardware VHDL è adattato ad una architettura FPGA tramite un tool di electronic design automation usando un processo di sintesi e place & route.

Si possono valutare i risultati di timing analysis, simulazioni ed altri metodi di verifica.

4.2

SEZIONE RF DEL TAG.

Un sistema di identificazione a Radio Frequenza (RFID) è costituito da un lettore e da un transponder, comunemente detto tag, collocato nell’oggetto da identificare. Il sistema opera rispettando i principi dell’accoppiamento induttivo, sia il lettore che il tag sono dunque dotati di elementi di accoppiamento. L’accoppiamento induttivo permette, infatti, il trasferimento di energia dal lettore al tag.

Il lettore, grazie alla propria antenna, genera un campo magnetico. Una parte del flusso di campo magnetico, generato dall’antenna del lettore, si concatena con l’antenna del tag, che si trova ad una certa distanza dal lettore. La mutua induttanza è la misura quantitativa dell’accoppiamento fra i due conduttori.

Fissate le caratteristiche dei due conduttori, vale a dire il raggio della spira e il numero di spire, il coefficiente di accoppiamento dipende unicamente dalla distanza fra i due conduttori.

La legge di Faraday stabilisce che quando il flusso magnetico concatenato con il circuito varia con il tempo, si genera in tale circuito una f.e.m. indotta u uguale, istante per

Se la corrente i1, che scorre nel conduttore 1, varia nel tempo, si genera nello stesso

conduttore un campo magnetico che varia nel tempo dφ

( )

i1 /dt, si avrà cosi una tensione indotta nel conduttore 1 (u1); anche il campo magnetico concatenato con il conduttore 2 varia nel tempo, provocando pertanto una tensione indotta nel conduttore 2 (u2).Si può rappresentare lo schema del circuito elettrico equivalente ai due conduttori mutuamente accoppiati.

Figura 4-1: Accoppiamento fra i conduttori e circuito equivalente

In un sistema RFID ad accoppiamento induttivo L1 è l’induttanza dell’antenna trasmittente del lettore, L2 è l’induttanza dell’antenna del tag, R2 è la resistenza dell’antenna del tag mentre la resistenza di carico RL tiene conto del consumo di corrente dei dati in

memoria.

Un flusso che varia nel tempo nel conduttore 1, a causa dell’accoppiamento mutuo tra i due conduttori, induce una tensione nel conduttore 2.

La tensione indotta nell’antenna del tag è utilizzata come tensione di alimentazione del microchip del tag stesso.

Per migliorare l’efficienza del circuito equivalente precedentemente illustrato si inserisce un condensatore addizionale C2 , in parallelo al tag, in modo da formare con l’induttanza L2 un circuito risonante parallelo, la cui frequenza di risonanza coincide con la frequenza operativa del sistema RFID.

0 f = 2 2 2 1 C L π (4.1)

In realtà il condensatore C2 è dato dal parallelo della capacità C2' e dalla capacità parassita CP del circuito reale, quindi C2 =

(

C2' +CP)

. Nota la capacità parassita CPe la frequenza operativa f , la capacità C2' si trova invertendo la formula di Thomson.' 2 C =

(

)

CP L f 2 2 − 2 1 π (4.2)Si ottiene cosi lo schema del circuito elettrico equivalente al tag reale.

Figura 4-2: Circuito elettrico equivalente del tag reale

2

R è la resistenza dell’antenna del tag e la resistenza di carico RL tiene conto del consumo di corrente dei dati in memoria; L2 e C2 formano un circuito risonante parallelo.

L’aver inserito il condensatore in parallelo al tag, quindi il circuito risonante parallelo, inizialmente non cambia molto le cose, ma quando si arriva alla frequenza di risonanza la tensione sul carico aumenta di un fattore dieci, rispetto al caso in cui è presente la sola antenna del tag; per poi diminuire rapidamente, una volta superata la frequenza di risonanza, scendendo ben al di sotto della tensione sul carico nel caso in cui sia presente la sola antenna del tag.

Q = 2 2 2 2 2 1 1 C L R L C R L + = L R L L R 2 2 2 1 ω ω + (4.3)

Dalla relazione trovata si può dedurre che quando R2 →∞ e RL →∞ il fattore di bontà è basso Q→0, di conseguenza anche la tensione indotta proporzionale al fattore di

bontà sarà bassa; mentre quando R2 →0 e RL >>0, condizione questa corrispondente ad un basso consumo di potenza del microchip del transponder, il fattore di bontà è molto elevato, cosi come la tensione indotta.

Se si fissa la coppia di resistenze R2 e RL, esiste un valore di induttanza del tag che massimizza il fattore di bontà e la tensione indotta; questo effetto può essere sfruttato per ottimizzare il range di energia di un sistema RFID ad accoppiamento induttivo.

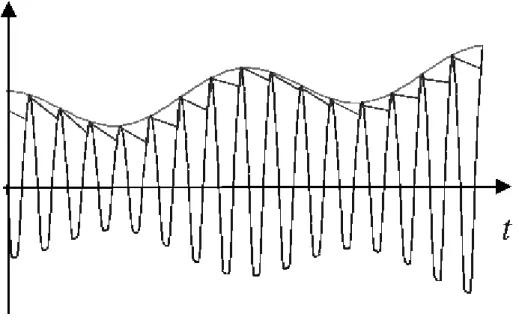

In figura è rappresentato il campo magnetico del tag al variare della frequenza.

Figura 4-3: Campo magnetico in funzione della frequenza di risonanza

Quando la frequenza di trasmissione del lettore coincide con la frequenza di risonanza del tag il campo magnetico assume il valore minimo.

min H = 2 2 0 2 2 2 2 2 2 2 2 2 1 A N C R R L C L R R u L L µ ω + + (4.4)

Si ricorda che R2 e L2 sono rispettivamente resistenza e induttanza dell’antenna del tag, N2 è il numero di spire dell’antenna del tag e A2 è l’area racchiusa da ogni singola spira,

0

ω è la pulsazione di risonanza ed u2 è la tensione indotta sul carico.

Il range di energia massimo del tag è dato dalla distanza fra antenna del tag e antenna del lettore a cui corrisponde la minima tensione di alimentazione u2min richiesta per le operazioni del tag.

Da un punto di vista analitico, considerando il campo magnetico minimo, si ottiene la formula: x = 3 12 2 min 2 1 1 1 2H R R N I − (4.5)

Si prenda ora in considerazione l’antenna del lettore, essa genera un campo magnetico, che si propaga poi nello spazio circostante come campo elettromagnetico.

Si distinguono due casi: il campo vicino, nella zona circostante l’antenna, il campo lontano, nella zona in cui ormai la radiazione elettromagnetica è completamente formata lontano dall’antenna. La distinzione fra i due casi citati dipende dalla distanza che separa la sorgente di irraggiamento dal punto di misura d e dalla lunghezza d’onda λ del segnale

utilizzato.

λ = f

c (4.6) dove =3⋅108

c m/s è la velocità della luce, f è la frequenza calcolata in Hz e λ è la

lunghezza d’onda calcolata in m.

Il limite di separazione fra la zona di campo vicino e la zona di campo lontano è data dal rapporto λ/2π (Fricke et al., 1979).

Un’onda elettromagnetica, una volta creata, si propaga nello spazio circostante trasportando energia, immagazzinata nel campo elettrico E

r

e nel campo magnetico H r

. Mentre nella zona di campo vicino l’ampiezza del campo magnetico ha una dipendenza rispetto alla distanza dalla sorgente che emette la radiazione pari a 1 d/ 3, nella zona di campo

lontano la dipendenza dei campi, elettrico e magnetico, dalla distanza dall’emettitore è pari a

d /

1 .

Un’antenna, che irradia o riceve un’onda elettromagnetica, è ottimizzata per il funzionamento all’interno di un certo range di frequenze.

Il guadagno di un’antenna è il rapporto fra la potenza irradiata da un emettitore isotropo a distanza r e la potenza effettivamente irradiata dall’antenna.

Si consideri un’antenna trasmittente isotropa, che irradia una potenza PT, se la potenza

disponibile per un’antenna ricevente è PR quando l’antenna è a distanza d dall’antenna

trasmittente, allora: T R P P =

(

4 /)

2 λ πd G GT R (4.7)Il rapporto PR /PT dipende dalla quantità d/λ , chiamata distanza efficace, e dai

guadagni delle due antenne.

L’obiettivo che si vuole raggiungere è lo scambio di dati fra lettore e transponder e viceversa, l’informazione è, infatti, trasmessa alternativamente in entrambe le direzioni.

Il segnale a radio frequenza, generato dal lettore, è inviato al tag utilizzando una modulazione di ampiezza, come descritto nel paragrafo 2.4.1. L’ampiezza del segnale utilizzato per la trasmissione (portante) è modulata in maniera proporzionale all’ampiezza del segnale che si intende trasmettere.

Figura 4-4: Segnale modulato

Il tag deve essere dotato di un circuito in grado di demodulare il segnale trasmesso, cioè un circuito che segua le variazioni dell’inviluppo della portante, che rappresenta l’informazione. Il circuito di interesse è un rivelatore di inviluppo, di cui è rappresentato lo schema elettrico nella figura seguente.

Figura 4-5: Schema elettrico di un rivelatore di inviluppo

L’inviluppo viene rivelato tramite la carica e la scarica del condensatore.

Quando il diodo è polarizzato direttamente conduce fino all’istante in cui il condensatore è caricato al valore di picco della relativa semionda. Il valore della tensione ai capi del condensatore supera il valore della tensione di ingresso, il diodo è polarizzato in inversa e si interdice.

Figura 4-6: Rivelatore di inviluppo

Il condensatore si scarica sulla resistenza, che si trova in parallelo ad esso, con costante di tempo τ =R1C1, fino all’istante in cui il diodo riprende a condurre, vale a dire al successivo picco positivo del segnale modulato. La conduzione del diodo permette di ricaricare il condensatore.

La spezzata risulta più o meno evidente in base al valore assunto dalla costante di tempo rispetto al periodo della portante.

Se il condensatore si scarica più velocemente sulla resistenza (costante di tempo molto piccola rispetto al periodo della portante) la spezzata è più accentuata, di conseguenza l’inviluppo non approssima l’informazione originaria in maniera accettabile.

Nel caso in cui la costante di tempo è molto grande rispetto al periodo della portante il condensatore si scarica sulla resistenza meno velocemente, approssimando meglio il segnale modulato. La costante di tempo però non deve superare un valore limite, altrimenti il condensatore non riesce più a scaricarsi con la stessa rapidità con cui decresce l’inviluppo e quindi non riesce a seguirlo.

Affinché il segnale ottenuto, cioè l’inviluppo del segnale trasmesso dal lettore, possa essere trattato, esso deve prima essere trasformato in un’onda quadra, tramite un comparatore.

Ogni volta che il segnale in ingresso al comparatore supera il valore della soglia il comparatore commuta la propria uscita.

Il segnale in uscita dal comparatore, un’onda quadra oscillante fra un valore alto ed un valore basso, non è altro che il segnale di ingresso della parte digitale del tag, cioè quello che abbiamo finora chiamato data_rx.

4.2.1 Clock.

Il tag analizza il segnale con l’ausilio di un particolare segnale, il segnale di clock. Il segnale di clock può essere estratto direttamente dal segnale di ingresso del tag cioè dal segnale trasmesso dal lettore. Il segnale di clock è infatti un’onda quadra, che oscilla fra un valore alto e zero, con frequenza pari alla frequenza della portante del segnale trasmesso dal lettore. Il segnale di clock si ottiene quindi tramite un comparatore che compara il segnale trasmesso dal lettore con un valore di soglia, che in questo caso è zero.

Come previsto dallo Standard ISO 15693 (paragrafo 2.4.1) il segnale trasmesso dal lettore è modulato con modulazione ASK, in particolare il lettore sceglie fra due possibili indici di modulazione 10% o 100%.

Quando l’indice di modulazione è al 10% (vedi Figura 2-2) non si verificano particolari problemi nell’estrarre il segnale di clock dal segnale trasmesso dal lettore.

Quando l’indice di modulazione è al 100% (vedi Figura 2-1), in alcuni intervalli di tempo l’ampiezza del segnale trasmesso dal lettore si riduce notevolmente impedendo la corretta estrazione del segnale di clock dal segnale trasmesso dal lettore.

Per ovviare a questo inconveniente la soluzione adottata è un generatore di clock esterno, che andrà in ingresso alla parte digitale del tag.

4.2.2 Fase di trasmissione.

Nel paragrafo 2.6.2 si descrive il protocollo di trasmissione, che definisce i meccanismi di scambio fra lettore e tag e viceversa.

Il protocollo si basa sul concetto che lettore e tag non possono mai parlare contemporaneamente. Il lettore parla per primo. I tag presenti possono trasmettere solo dopo aver ricevuto e decodificato una istruzione inviata dal lettore.

È per questo che il tag quando riceve il segnale trasmesso dal lettore non deve trasmettere nessuna informazione.

4.3

FITTING DEVICE.

4.3.1 Descrizione di un dispositivo FPGA.

Per realizzare un sistema digitale si possono seguire varie strade: si possono usare circuiti logici integrati standard, circuiti ad elevata flessibilità programmabili dall’utente oppure si possono realizzare circuiti dedicati di tipo ASIC (Application Specific Integrated Circuit). I dispositivi ASIC sono progettati e realizzati per risolvere un problema specifico e sono ottimizzati per l’applicazione considerata. Rispetto agli altri circuiti logici, i dispositivi ASIC hanno sicuramente prestazioni migliori, essi sono infatti più veloci, hanno un ingombro ridotto, dissipano meno potenza ed hanno una maggiore affidabilità, ma hanno costi di realizzazione più elevati e quindi il loro impiego è giustificato solo quando si hanno grandi volumi di produzione.

Un dispositivo programmabile dall’utente però, rispetto ad un circuito logico di tipo ASIC, ha il vantaggio di essere disponibile sul mercato in un tempo inferiore e di essere più economico; inoltre questi circuiti possono essere riprogrammati, è quindi possibile apportare delle modifiche al progetto finale.

Fra i dispositivi logici programmabili PLD (Programmable Logic Devices), i circuiti FPGA (Field-Programmable Gate Array) hanno sicuramente la struttura più flessibile.

Un dispositivo FPGA è un circuito a semiconduttore che contiene sia componenti logici che interconnessioni programmabili. I componenti logici programmabili (o blocchi logici)

Un dispositivo FPGA può rappresentare quindi una qualunque funzione logica.

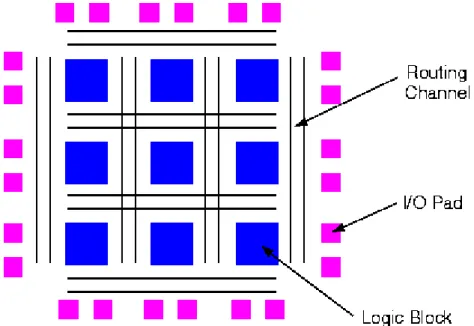

L’architettura elementare tipica di un dispositivo FPGA è caratterizzata da un array di blocchi logici programmabili, che svolgono le varie funzionalità, interconnessi fra loro con connessioni programmabili e da channel routing. La struttura prevede una serie di pad di I/O esterni con posizione fissata, ma con funzionalità programmabile.

Figura 4-7: Struttura di un dispositivo FPGA

Un blocco logico elementare che costituisce un dispositivo FPGA consta di quattro ingressi lookup table (LUT) e un flip-flop. Ai quattro ingressi va aggiunto l’ingresso del segnale di clock, separato dagli altri ingressi.

Figura 4-8: Blocco logico

Ogni ingresso è accessibile da un lato del blocco logico.

Il pin di uscita di ogni blocco logico può essere connesso con ogni filo presente nel canale ad esso adiacente.

Figura 4-9: Architettura di un dispositivo FPGA

Ogni filo collega un unico blocco logico con uno switch box, programmabile.

In realtà FPGA includono moltiplicatori, blocchi DSP generici, processori embedded, memorie embedded e blocchi di I/O ad elevata velocità.

Sulla base di quanto descritto emerge che per bassi e medi volumi di produzione conviene utilizzare dispositivi FPGA. Anche per generare progetti su ASIC tipicamente si realizza un prototipo sub-ottimo su FPGA per effettuare verifiche sulla validità del progetto stesso; una volta concluso si trasferisce sul circuito ASIC per la produzione su larga scala.

4.3.2 Simulazione.

Per definire il funzionamento di una FPGA si usa un linguaggio di descrizione hardware (HDL) o un design schematico. I più comuni linguaggi di descrizione hardware sono il VHDL e il Verilog. Usando un tool di electronic design automation si genera una netlist, che può essere adattata ad una architettura FPGA usando un processo di sintesi e place & route.

Dopo una prima fase di descrizione RTL in VHDL del sistema di identificazione a radio frequenza, ampiamente descritta nel terzo capitolo, si procede con una fase di simulazione.

La simulazione consiste nella creazione di un test bench; si stimola cioè il sistema creando le forme d’onda relative all’informazione che si vuole trasmettere, nel rispetto dello Standard ISO 15693.

Si genera il segnale di start of frame (come descritto nel paragrafo 2.4.3.1) e a seguire i segnali relativi ai dati da trasmettere (come descritto nel paragrafo 2.4.2). In parallelo deve essere presente la procedura che genera il CRC sui dati trasmessi, il CRC trovato fa infatti parte del frame da trasmettere. A questo punto si genera il segnale di end of frame (come descritto nel paragrafo 2.4.3.2).

Si può stimolare il sistema, descritto in VHDL, con tutti i possibili comandi descritti nel protocollo (paragrafo 2.6.9). È possibile cosi verificare il corretto funzionamento del sistema per ogni singolo comando, in base ai dati trasmessi e allo stato interno del tag. Si può inoltre verificare la risposta del sistema, in accordo allo Standard ISO 15693, quando si verificano errori di vario genere.

Si può sfruttare la simulazione passo dopo passo durante la descrizione del sistema in VHDL.

In questo modo si può stimolare il sistema, con i comandi previsti dal protocollo, e verificare la corretta esecuzione dei comandi stessi.

È inoltre possibile verificare il modo in cui risponde il sistema quando si apportano delle modifiche alla descrizione fatta.

4.3.3 Fitting su FPGA.

Dopo la sintesi, in VHDL, si mappa il design in una netlist, la netlist è tradotta in una descrizione gate level ed è ripetuta la simulazione per confermare che la sintesi proceda senza errori. Una volta completato il processo di verifica, il file generato è pronto per configurare il dispositivo FPGA.

Il software utilizzato permette di creare e realizzare architetture FPGA, PLCD e strutture ASIC; supporta le descrizioni hardware VHDL e Verilog del sistema e permette di utilizzare una memoria integrata nell’architettura FPGA.

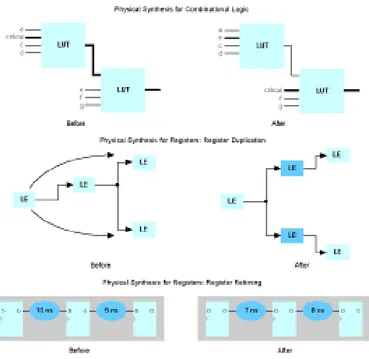

In un flusso di compilazione standard, la sintesi ottimizza la struttura logica di un circuito per quanto riguarda l’area, la velocità, o entrambi e mappa il circuito in un dispositivo specifico primitivo così come elementi logici (LE), memoria, e blocchi primitivi DSP (digital signal processing).

Si può migliorare il passo di sintesi con un ulteriore tool di sintesi avanzato, per l’analisi e l’ottimizzazione di dispositivi logici programmabili, che riduce automaticamente il consumo di potenza e migliora lo sviluppo e l’ottimizzazione delle funzioni che costituiscono i singoli blocchi migliorando l’integrazione e l’ottimizzazione dell’intero sistema.

La compilazione completa comprende il passo di place & route (o device Fitting), che sistema i dispositivi primitivi, specificati nel tool di sintesi, in modo da assicurare che le porzioni critiche di logica siano chiuse insieme e connesse attraverso il percorso più veloce possibile, sono quindi fissati gli “hot spot” critici del sistema per migliorarne le performance.

L’ottimizzazione, tramite opportune selezioni, può cambiare le connessioni degli elementi logici (LE) in modo che la via critica attraversi un minore numero di layer, può

Figura 4-11: Criteri di ottimizzazione

Il software permette di usare automaticamente ogni combinazione di opzioni di sintesi fisiche in modo da trovare la sistemazione ottimale dei componenti per massimizzare le caratteristiche del sistema sull’intera area, ogni design ha infatti le proprie caratteristiche.

4.3.4 Dispositivo EP1C20.

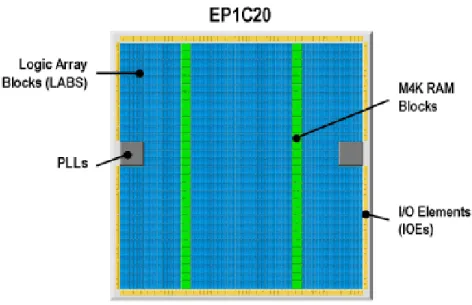

Il dispositivo FPGA utilizzato è un EP1C20F4000C6 Altera della famiglia Cyclone, dispositivo a basso costo molto efficiente e flessibile, il cui schema è rappresentato in figura.

Figura 4-12: Schema del dispositivo FPGA EP1C20 della famiglia Cyclone

Il dispositivo ha una densità di elementi logici di 20060 supporta una varietà di single ended I/O standard e supporti I/O differenziali, ha inoltre due PLL (Phase Locked Loop) e una circuiteria di gestione del clock, per circuiti complessi. Il dispositivo prevede anche memorie integrate e interfacce di memoria esterne.

La memoria integrata, con una capacità totale pari a 294912 bit, è costituita da colonne di blocchi di RAM da 4Kbit, ognuno dei quali ha capacità di trasferimento dei dati di più di 200MHz. Ogni blocco di RAM può implementare vari tipi di memorie true dual-port, simple dual-port, single port RAM, ROM, buffer FIFO, include inoltre il bit di parità per il controllo degli errori.

4.3.5 Risultati.

Al termine del processo di configurazione del dispositivo FPGA, si esegue una analisi delle prestazioni del circuito realizzato per valutarne l’efficienza.

Le prestazioni del dispositivo, in termini di risorse utilizzate e area occupata, possono essere valutate leggendo il file prodotto dalla simulazione.

ci sono in particolare 238 funzioni da zero ingressi, 46 funzioni da un ingresso, 484 funzioni da due ingressi, 1272 funzioni da tre ingressi e 4560 funzioni da quattro ingressi.

Per quanto riguarda la memoria sono utilizzati 35 blocchi di RAM da 4Kbit su un totale di 64 blocchi (pari quindi allo 54%), il numero totale di bit di memoria utilizzati è di 139264 su 294912 (pari al 47%), il numero totale di bit di blocchi di RAM utilizzati è di 161280 su 294912 (pari al 54%).

Il principale criterio di valutazione del circuito realizzato è la velocità di elaborazione. Si determina la massima frequenza di funzionamento del dispositivo, potrebbe infatti esistere al suo interno un percorso nascosto tra due registri maggiore del più lungo percorso tra ingresso ed uscita. La valutazione complessiva della massima frequenza di elaborazione del circuito è di 30,59MHz, compatibile con la frequenza di funzionamento del sistema.