In commercio esistono vari dispositivi per l’acquisizione multicanale da strain gage. Si tratta, però, di oggetti con prezzi eccessivamente elevati per il budget a nostra disposizione, perciò è stato necessario progettare e realizzare un circuito che provvedesse al prelievo e all’elaborazione dei segnali generati dagli estensimetri in seguito all’azione delle forze agenti sui denti del sistema di masticazione durante il suo funzionamento, a partire dal front-end analogico con i sensori fino all’interfacciamento col PC, con una stringente specifica di limitazione dei costi. Inoltre, si è dovuto prevedere anche un sistema per il controllo della valvola di comando del pistone.

In questo capitolo vengono descritti l’architettura e il funzionamento del dispositivo, le fasi di realizzazione e i componenti integrati utilizzati, con particolare attenzione al microcontrollore che gestisce tutto il sistema e il cui firmware verrà descritto nel prossimo capitolo.

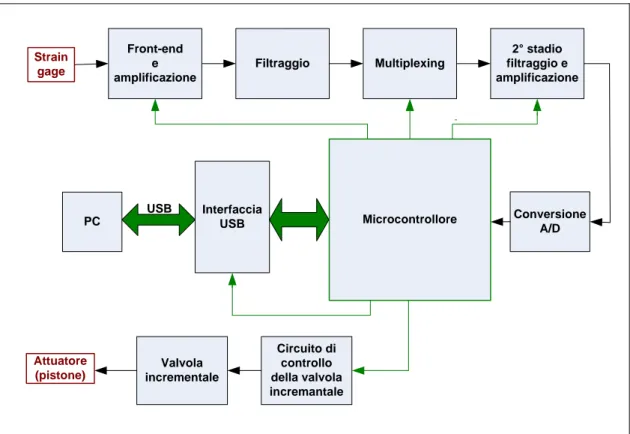

4.1 Diagramma a blocchi

Il circuito realizzato rappresenta un prototipo del dispositivo definitivo e consente l’acquisizione parallela, su due canali, di segnali provenienti da due coppie di estensimetri. Il lavoro di assemblamento dei componenti e di realizzazione e

verifica del programma del microcontrollore è stato svolto presso l’azienda EBB-srl di Calcinaia (PI), dove si intende realizzare il circuito definitivo.

Finora sul prototipo sono state eseguite delle misure sperimentali, e sarà utilizzato sottoposto ad altri test prima di realizzare il circuito definitivo, in modo da rendere possibili eventuali correzioni o miglioramenti.

Front-end e amplificazione Filtraggio 2° stadio filtraggio e amplificazione Multiplexing Microcontrollore Conversione A/D Interfaccia USB PC Circuito di controllo della valvola incremantale Valvola incrementale USB Attuatore (pistone) Strain gage

Figura 4.1: schema a blocchi del sistema realizzato. Il controllo è affidato ad un microcontrollore che gestisce (frecce verdi) la regolazione degli offset degli amplificatori in ingresso, il multiplexer e il guadagno del secondo stadio di amplificazione, oltre al circuito di comando della valvola incrementale e il dispositivo di interfacciamento al PC tramite USB, col quale comunica via bus; inoltre, effettua la conversione A/D del segnale proveniente dai sensori attraverso la catena di elaborazione analogica (frecce nere).

Se dal punto di vista progettuale il sistema definitivo consisterà essenzialmente in una replica del prototipo, vi saranno due differenze dal punto di vista realizzativo: innanzitutto, dovrà avere otto canali invece di due; inoltre, al fine di limitare l’ingombro e ottimizzare la portabilità del dispositivo, verrà realizzato in tecnologia SMD. Questo ha avuto come conseguenza l’aggiunta di un’ulteriore specifica nella

scelta di soluzioni circuitali per il prototipo: si è cercato di utilizzare componenti disponibili anche nel formato SMD, in modo da rendere il circuito realizzato il più possibile affine a quello definitivo.

Entrambi i dispositivi possono essere descritti tramite lo schema a blocchi rappresentato nella figura 4.1.

La parte analogica del sistema consiste, oltre all’alimentazione, in un front-end analogico che effettua anche un’amplificazione, un primo stadio di filtraggio (che, come verrà spiegato in seguito, si può scegliere se utilizzare o meno), un multiplexer e un secondo stadio di filtraggio e di amplificazione a guadagno variabile, che funge anche da adattatore d’impedenza per il convertitore A/D.

Come già accennato,si è scelto di utilizzare un microcontrollore per la gestione dell’intero sistema e un’interfaccia USB per la comunicazione col PC, in modo da rendere il dispositivo indipendente dalla presenza di schede di acquisizione specifiche, ed avere così il massimo grado di flessibilità e portabilità. In particolare, il microcontrollore gestisce l’abilitazione e l’indirizzamento del multiplexer, la regolazione degli offset degli amplificatori in ingresso, il guadagno del secondo stadio di amplificazione e il circuito di controllo della valvola di comando del pistone. Inoltre, effettua la conversione A/D del segnale proveniente dagli strain gage attraverso la catena di elaborazione analogica e controlla il dispositivo che si interfaccia con il PC tramite USB, con il quale comunica attraverso un bus a 8 bit.

4.2 Descrizione dello schema elettrico

In questo paragrafo vengono illustrate fasi di realizzazione, scelta dei componenti e caratteristiche elettriche dei vari sottosistemi che compongono la scheda hardware realizzata: i vari stadi che implementano le funzioni di acquisizione ed elaborazione analogica dei segnali (interfacciamento elettrico con i sensori, multiplexing, filtraggio, amplificazione); l’interfaccia USB per la comunicazione con il PC; il circuito di controllo della tensione in ingresso alla valvola incrementale che comanda

l’attuatore del sistema, ovvero il pistone; il circuito di alimentazione.

Lo schema elettrico completo del dispositivo è riportato in Appendice A.

4.3.1 Front-end e primo stadio di guadagno

Come abbiamo già detto, il sistema di sensori dai quali bisogna acquisire i segnali è costituito da otto coppie di strain gage posizionati su altrettante lamine, in ognuna delle quali uno è posto sulla faccia superiore, l’altro su quella inferiore. Per quanto visto nel capitolo precedente, con questo tipo di configurazione l’ideale è utilizzare, per l’interfacciamento elettrico, un ponte di Wheatstone half-bridged per ognuna delle coppie di estensimetri.

Gli strain gage utilizzati hanno una resistenza nominale di 120 Ω ± 0.15% e un fattore di gage pari a G=2.2. Il completamento del ponte è stato realizzato con due resistenze di precisione, di valore pari a 121 Ω ± 0.1%, per limitare il più possibile l’offset in ingresso al sistema.

Per rendersi conto dell’entità dei segnali in gioco, si può calcolare la massima tensione differenziale ottenibile in ingresso: ricordando che il massimo carico agente sui denti porta ad una deformazione pari a 1370.7 µε e che il ponte viene alimentato a 3 V, dalla (3.14) otteniamo un valore pari a circa 4.5 mV. I segnali da acquisire hanno, quindi, valori piuttosto bassi, considerando in particolare che si possono avere in ingresso dei disturbi con lo stesso ordine di grandezza e che la tensione a modo comune ha un valor medio di 1.5 V (dato dalla metà della tensione di alimentazione degli strain gage). Per questo si è ritenuto necessario utilizzare un amplificatore d’ingresso con prestazioni elevate, per evitare di compromettere irrimediabilmente, con dispositivi magari più economici ma dalle caratteristiche peggiori, la corretta acquisizione dei segnali.

In seguito a queste considerazioni la scelta è stata effettuata nell’ambito degli amplificatori da strumentazione, dispositivi usati diffusamente per questo tipo di applicazioni e, più in generale, per l’interfacciamento con vari tipi di sensori, anche in ambito biomedico.

Inizialmente erano state considerate due possibili soluzioni per il front-end con il ponte di Wheatstone: la prima prevedeva l’utilizzo di un solo amplificatore da strumentazione, posto a valle di un multiplexer differenziale al quale collegare l’uscita del ponte e con il quale selezionare la coppia di strain gage; la seconda soluzione consisteva nell’impiego di un amplificatore per ogni canale, a monte di un multiplexer. Dalle prove sperimentali eseguite per valutare la fattibilità della prima opzione, più economica della seconda ma anche più soggetta ai disturbi, si è potuto notare come l’andamento del segnale rispondesse solo parzialmente alle sollecitazioni applicate ai denti del masticatore. La causa di questo comportamento è da ricercare nel fatto che il segnale, già di per sé debole, viene ulteriormente peggiorato dal rumore introdotto dal multiplexer. Di conseguenza, è stata scelta la seconda opzione.

Le prime misure sono state effettuate utilizzando, come amplificatore da strumentazione, l’AMP-04 dell’Analog Devices, perché già a disposizione in laboratorio. Si tratta però di un componente piuttosto caro, perciò si è deciso di sostituirlo con l’AD620, sempre dell’Analog Devices, che ha prestazioni paragonabili all’AMP-04 ma è più economico.

L’ottimizzazione delle prestazioni del front-end analogico ha permesso, oltre ad avere un segnale più robusto e meno sensibile al rumore, di poter effettuare per il resto del circuito scelte più economiche in termini di configurazione circuitale e di componenti, senza pagare prezzi rilevanti in termini di qualità del segnale, e quindi di prestazioni del circuito stesso. Ad esempio, è stata scelta un’alimentazione singola a 5 V, che limita un po’ le prestazioni degli amplificatori e del multiplexer (vedi [17] e [18]), ma consente un risparmio in termini di componenti e di potenza (vedi paragrafo 4.2.7).

Considerando i bassi valori della tensione differenziale in ingresso, è stato scelto per gli amplificatori da strumentazione un guadagno prossimo a quello massimo; per l’AD620 tale valore è pari a 1000, impostabile con una resistenza esterna di circa 50 Ω (vedi paragrafo 4.4.1). Il problema di questa scelta è che un minimo offset d’ingresso può essere sufficiente per far saturare l’uscita dell’AD620. Pertanto la

soluzione adottata inizialmente per la regolazione dell’offset, ovvero l’utilizzo di un semplice potenziometro variabile, è stata subito abbandonata, perché in caso contrario nel circuito definitivo sarebbe stato necessario calibrare manualmente l’offset di tutti i canali all’inizio di ogni acquisizione. Di conseguenza, si è deciso di utilizzare un potenziometro digitale, l’AD8400 [19], un componente integrato in grado di fornire, tramite un partitore resistivo programmabile da microcontrollore, una tensione variabile praticamente tra 0 e il valore dell’alimentazione (vedi paragrafo 4.4.4). Più precisamente, nel circuito realizzato è stato usato un AD8402, componente con due potenziometri digitali integrati, mentre nel circuito definitivo verranno inseriti due AD8403, ognuno dei quali contiene quattro potenziometri digitali; considerando che il prezzo di un AD8403 e di un AD8400 (composto da un unico potenziometro) è circa lo stesso, in questo modo si riesce a risparmiare notevolmente senza incidere sulle prestazioni del circuito.

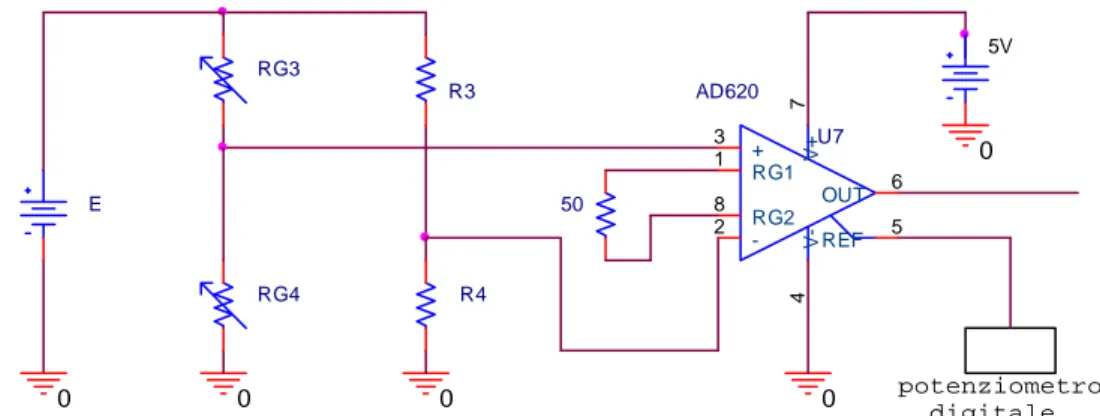

In figura 4.2 è rappresentato lo schema del front-end d’ingresso di un canale.

0 0 R3 50 0 potenziometro digitale 0 5V E RG4 0 RG3 R4 U7 AD620 6 3 2 5 7 4 1 8 OUT + - REF V+ V-RG1 RG2

Figura 4. 2: interfacciamento elettrico con gli strain gage nel circuito realizzato. Per ogni coppia di sensori RG1-RG2 si utilizza un ponte di Wheatstone half-bridged completato con resistenze di precisione di 121 Ω. Le uscite differenziali dei ponti vengono poste direttamente in ingresso ad amplificatori da strumentazione.

4.3.2 Multiplexing

Per la scelta del multiplexer le specifica più rilevante, oltre al prezzo, è stata l’alimentazione.

Infatti si è visto, dai datasheet dei componenti tra i quali è stata effettuata la selezione, che le prestazioni migliorano con l’utilizzo di un’alimentazione duale e con valori vicini a quello massimo utilizzabile con il componente. In questa situazione il valore della resistenza tra ingresso e uscita in funzione della tensione in ingresso si avvicina di più alla situazione ideale, in cui tale resistenza è costante e tendente a zero.

Nella scheda realizzata si utilizza un’alimentazione singola, perciò la scelta ottimale prevedeva l’utilizzo di un multiplexer la cui tensione di alimentazione massima fosse pari a quella del circuito, cioè 5 V. In base a questo è stato scelto l’AD608 dell’Analog Devices [18].

In ogni caso, il valore della resistenza tra ingresso e uscita non influenza eccessivamente il circuito, perché i circuiti a monte e a valle del multiplexer operano anche da adattatori d’impedenza. Questa specifica sarebbe stata rilevante, invece, se avessimo interfacciato un multiplexer differenziale direttamente con il ponte di Wheatstone. In tal caso, inoltre, sarebbero state influenti anche le differenze tra le resistenze di ingresso e uscita dei vari canali.

Altre caratteristiche che spesso influenzano la scelta di un multiplexer analogico, come la differenza tra le resistenze di ingresso e uscita dei vari canali e la frequenza massima, non sono, nel nostro caso, particolarmente stringenti, e comunque vengono abbondantemente soddisfatte dal componente scelto.

4.3.3 Filtraggio

Il segnale in ingresso si trova prevalentemente a frequenze molto basse, paragonabili a quelle della masticazione umana, ovvero da poche frazioni di Hz fino ad un massimo di 4-5 Hz. Si possono però avere delle componenti frequenziali più elevate in corrispondenza, ad esempio, degli istanti in cui il cibo viene spezzato dai denti, che possono fornire informazioni importanti sulle caratteristiche del cibo stesso. D’altronde, una frequenza di taglio troppo alta rischia di rendere il segnale eccessivamente rumoroso.

Sperimentalmente i disturbi a 50 Hz sono risultati particolarmente intensi, probabilmente a causa dell’ambiente di misura non sufficientemente schermato dai campi elettromagnetici e, volendo realizzare un dispositivo utilizzabile in diversi ambienti, non è stato possibile prevedere se il problema si sarebbe ripresentato e in che entità. In seguito a queste considerazioni si è deciso di utilizzare un filtro passa-basso con frequenza minore di 50 Hz.

Per avere un’attenuazione sufficiente a questa frequenza e contemporaneamente una frequenza di taglio non eccessivamente bassa, è necessario prevedere un filtro di ordine piuttosto alto: in commercio esistono componenti integrati che implementano filtri a frequenza programmabile e di vari ordini, con costi accettabili se avessimo potuto usarne uno per tutto il circuito, posto a valle del multiplexer. Questa soluzione ha però un problema che la rende inapplicabile: essendo la frequenza di taglio molto bassa, il filtro risponde molto lentamente alle variazioni a gradino, come possono essere considerate quelle che si hanno nella commutazione da un canale all’altro del multiplexer, pertanto il transitorio necessario al filtro per adeguarsi a tale commutazione rischia di essere più lungo dell’intervallo di tempo di acquisizione da un canale.

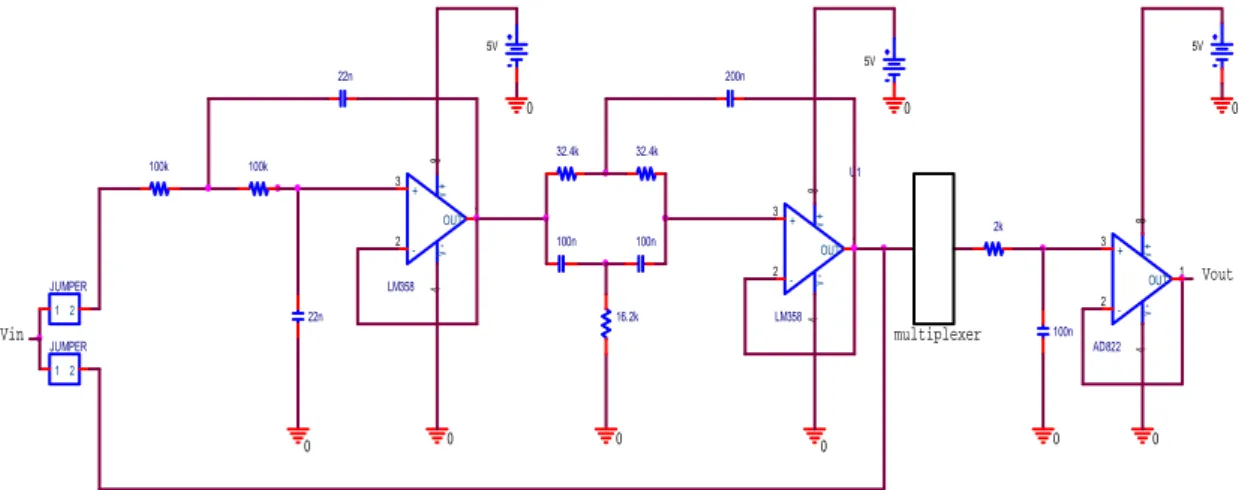

Il problema è stato risolto inserendo in ogni canale, tra l’uscita dell’amplificatore da strumentazione e l’ingresso del multiplexer, un filtro passa-basso del 2° ordine seguito da un notch a 50 Hz, realizzati con l’LM358 [20], un integrato a bassissimo costo della Philips (avente comunque prestazioni sufficienti per questa applicazione) contenente due amplificatori operazionali indipendenti.

Considerando però che, come si è detto sopra, non si può prevedere l’entità del disturbo a 50 Hz al variare dell’ambiente di misura, dobbiamo anche considerare la possibilità che tale disturbo non sia così eccessivamente fastidioso: in tal caso un filtro di questo tipo perderebbe la sua utilità, e per di più, avendo una frequenza di taglio di poche decine di Hz, potrebbe tagliare anche delle informazioni contenute a frequenze un po’ più alte. Pertanto, per consentire a chi effettua le misure di scegliere la soluzione migliore per la situazione contingente, sono stati introdotti nel circuito dei jumper (due per canale), che possono collegare l’uscita dell’AD620 con il filtro

o, in alternativa, direttamente con l’ingresso corrispondente del multiplexer, permettendo, in quest’ultimo caso, di “by-passare” il filtro.

Notiamo che questa scelta impone che il guadagno del filtro sia unitario, altrimenti avremmo amplificazioni diverse nei due casi.

Il filtro passa-basso è stato implementato con una cella di Sallen-Key a guadagno unitario, rappresentata in figura 4.3. La funzione di trasferimento ideale di questa configurazione è data da [21]: 2 0 0 1 1 ) ( ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + + = ω ω s Q s s HLP (4.1) dove 2 1 2 1 0 1 C C R R = ω è la pulsazione di taglio, e

(

1 2)

1 0 1 C R R Q = + ω . 0 R1 0 C2 Vin + -OUT C1 R2Figura 4. 3: cella di Sallen-Key a guadagno unitario.

Per semplicità si è scelto di porre R1 =R2 = R e C1 =C2 =C, ottenendo

RC

1

0 =

ω . Con queste impostazioni otteniamo:

2 0 2 0 1 1 ) ( 1 1 ) ( ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = ⇒ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = ω ω ω ω j j H s s HLP LP (4.2)

Notiamo che si ottiene anche 2 1 2 1 < =

Q , perciò si evita il problema del picco di risonanza in prossimità della frequenza di taglio.

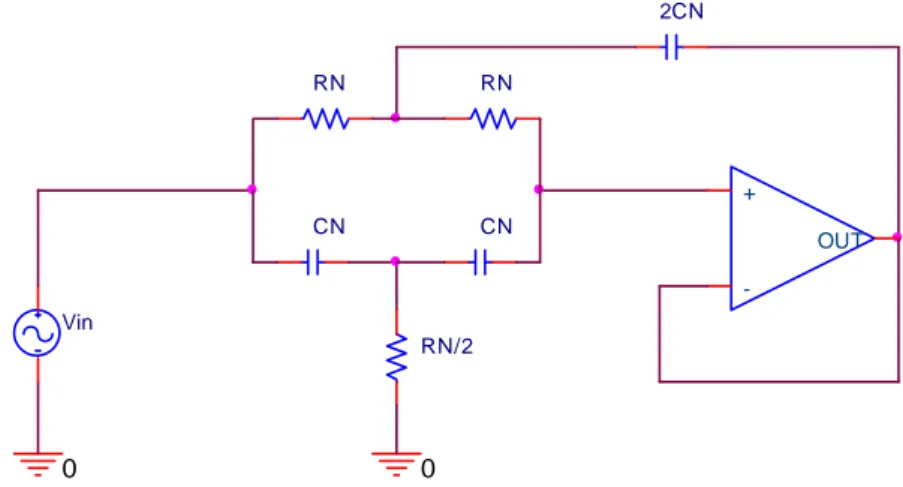

Il filtro notch a guadagno unitario è stato realizzato con la configurazione rappresentata in figura 4.4, avente funzione di trasferimento e risposta in frequenza date da [21]: 2 0 2 2 0 2 2 1 1 ) ( 2 1 1 ) ( ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − = ⇒ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = N oN oN N N oN oN N j j j H s s s s H ω ω ω ω ω ω ω ω ω ω (4.3) dove N N N C R 1 0 = ω è la pulsazione reiettata.

Questo valore non è influenzato in modo significativo né dal collegamento col filtro passa-basso né dai poli dell’operazionale. Pertanto, possiamo imporre che:

Hz C R f N N N N 2 50 1 2 0 0 = π = π = ω (4.4)

In base a questa relazione si possono trovare R e N C (con un grado di libertà). N

I valori commerciali di resistenze e capacità a disposizione con cui ci si avvicina maggiormente a tale frequenza sono R = 32.4 kΩ e N C = 100 nF. N

Per quanto riguarda il limite di banda del filtro complessivo, dato dalla cascata dei due blocchi, è necessario fare alcune considerazioni. Innanzitutto è diverso, ovviamente, da quello del solo filtro passa-basso, a causa della presenza del notch; la pulsazione di taglio ωT è legata comunque a R e C dalla relazione seguente:

2 1 ) ( ) ( T N T = LP j H j H ω ω (4.5)

Sostituendo il valore desiderato di ωT, si potrebbero ricavare R e C (con un grado di libertà). In realtà questo metodo non è praticabile, in quanto la presenza dei poli dell’operazionale fa sì che il valore reale del limite di banda, e la risposta in frequenza del filtro in generale, siano diversi da quelli teorici. Inoltre, è stato considerato che non interessa tanto avere un valore ben determinato della frequenza di taglio, ma piuttosto effettuare la scelta in modo da trovare un compromesso tra un limite di banda troppo basso, con cui si taglierebbe una quantità eccessiva di segnale utile, e il fatto che la reiezione a 50 Hz diminuisce all’avvicinarsi della frequenza di taglio a questo valore. Pertanto sono state effettuare delle simulazioni del filtro complessivo con PSPICE variando i valori di R e C tra quelli commerciali a disposizione, fino a trovare una soluzione ritenuta ottimale ponendo R=100 kΩ e

C=22 nF, con cui si ottiene una frequenza di taglio di circa 18 Hz ed un’attenuazione

a 50 Hz di 37 dB. I risultati delle simulazioni sono stati verificati sperimentalmente.

RN CN 0 CN RN 0 RN/2 Vin 2CN + -OUT

Figura 4. 4: filtro notch.

A questo punto si può notare che se si decidesse di non utilizzare questo filtro, ma di collegare l’uscita dell’amplificatore da strumentazione direttamente all’ingresso del multiplexer, il segnale arriverebbe al convertitore A/D senza essere stato sottoposto ad alcun tipo di filtraggio, con conseguenti problemi di aliasing. Per questo motivo si è deciso di inserire, in uscita dal multiplexer, un altro filtro passa-basso, la cui frequenza di taglio doveva essere tale da consentire una risposta

sufficientemente veloce alle commutazioni dei canali del multiplexer.

Inizialmente si era pensato di utilizzare la stessa configurazione del passa-basso precedente, ovvero una cella di Sallen-Key, con una frequenza di taglio intorno ad 1 kHz, ma dalle simulazioni è risultato che l’andamento della risposta in frequenza a frequenze dell’ordine delle centinaia di kHz presenta un andamento non accettabile (si ha la presenza di un picco), a causa della reazione del condensatore collegato all’uscita che influenza le singolarità dell’operazionale. Questo fenomeno è presente anche nel primo filtro, ma è comunque molto limitato perché la frequenza di taglio è molto minore di quella del secondo filtro. Di conseguenza, si è preferito utilizzare un filtro RC bufferizzato in uscita, ottenuto praticamente eliminando il condensatore collegato all’uscita, nonostante questo comporti una ripidezza minore della risposta in frequenza in prossimità del limite di banda. Quest’ultimo è stato fissato a circa 800 Hz utilizzando una resistenza di 2 kΩ e una capacità di 100 nF, un buon compromesso tra le caratteristiche anti-aliasing e quelle di velocità che il filtro deve avere. U1 LM358 3 2 8 4 1 + -V+ V-OUT 5V JUMPER 1 2 100n LM358 3 2 8 4 1 + -V+ V-OUT multiplexer 0 0 100k 22n 0 16.2k 5V 200n Vout 32.4k 100k 5V 0 0 2k JUMPER 1 2 0 22n 0 Vin 100n AD822 3 2 8 4 1 + -V+ V-OUT 100n 32.4k 0 0

Figura 4. 5: schema del circuito di filtraggio di un canale, formato da un filtro passa-basso e un notch in cascata a monte del multiplexer, ed un secondo filtro passa-basso a valle. A seconda del jumper che viene collegato, il primo stadio di filtraggio può essere inserito o meno. La tensione Vin proviene dall’uscita dell’AD620, mentre Vout va in ingresso al secondo stadio di guadagno.

4.3.4 Secondo

stadio di guadagno

stadio di amplificazione a guadagno variabile, implementato con un amplificatore operazionale in configurazione non invertente in cui una resistenza è sostituita con un potenziometro digitale, che consente di avere una guadagno variabile tra 1 e 26.6 (vedi paragrafo 4.4.4). Considerando che, come abbiamo visto, l’ingresso massimo è di 4.5 mV, con l’amplificazione introdotta dall’AD620 si può arrivare alla tensione di saturazione del filtro anche con un offset molto basso; nonostante questo, la possibilità di aumentare il guadagno è stata introdotta perchè si potrebbero voler eseguire delle sequenze di misure sperimentali in cui gli ingressi sono molto minori del valore massimo (ad esempio, con materiali o cibi molto morbidi), nel qual caso sarebbe auspicabile poter avere un guadagno maggiore.

Sia questo stadio che il filtro precedente sono stati realizzati con un AD822 [22], altro componente integrato contenente due amplificatori operazionali che rispetto all’LM358 garantisce prestazioni migliori, in particolare grazie al fatto che ha la proprietà di essere rail-to-rail.

Vout 0 AD822 3 2 8 4 1 + -V+ V-OUT 0 Vin 3.9k potenziometro digitale 0 5V

Figura 4. 6: schema del secondo stadio di guadagno, costituito da un amplificatore non invertente in cui una resistenza è sostituita da un potenziometro digitale che consente di variare il guadagno. La tensione d’ingresso proviene dall’uscita del secondo filtro, mentre la tensione Vout va in ingresso al convertitore A/D.

In figura 4.7 sono mostrati i risultati della simulazione, eseguita con PSPICE, della risposta in frequenza della tensione in uscita dal secondo stadio di

amplificazione, in funzione di quella in ingresso all’amplificatore da strumentazione. La simulazione è stata ottenuta impostando un guadagno unitario nel secondo stadio di amplificazione e sostituendo il multiplexer con il circuito equivalente RC ottenuto in base ai datasheet. Le due tracce sono state ottenute ponendo il jumper nelle due posizioni.

Figura 4. 7: risposta in frequenza normalizzata della tensione in uscita dal secondo stadio di guadagno in funzione di quella in ingresso all’amplificatore da strumentazione. La traccia inferiore è ottenuta con l’inserimento del primo stadio di filtraggio.

4.3.5 Interfaccia USB

La funzione di interfaccia per la comunicazione USB tra il microcontrollore della scheda e il PC viene svolta da un circuito integrato della Philips, il PDIUSBD12 [23]. Dal punto di vista software, approfondito nel prossimo capitolo, tramite le istruzioni codificate nella memoria di questo componente il firmware del microcontrollore comunica con il programma ad alto livello presente nel PC; da una parte tale programma viene gestito dall’utente, dall’altra si interfaccia con una

struttura software in cui è implementato il controllore di tipo neurale.

Più in dettaglio, i collegamenti presenti tra il microcontrollore e il PDIUSBD12 sono i seguenti (tra parentesi, i nomi dei pin corrispondenti del PDIUSBD12, come indicati in figura 4.20 e descritti nel paragrafo 4.4.5):

• Un bus di comunicazione bidirezionale a 8 bit, sul quale vengono trasmesse le istruzioni e i dati (DATA<0>…DATA<7>);

• Un collegamento tramite il quale il microcontrollore abilita il dispositivo (CS_N);

• Un collegamento sul quale il dispositivo invia al microcontrollore le richieste di interrupt (INT_N);

• Un collegamento il cui valore discrimina la trasmissione di dati sul bus da quella di istruzioni (A0);

• Due collegamenti per indicare l’accesso al bus in lettura e in scrittura (RD_N e WR_N).

Nella scheda realizzata è presente, ovviamente, anche un connettore USB. Questo contiene 4 piedini, ognuno dei quali è connesso ad uno dei fili del cavo collegato al PC. Uno di questi fili è collegato all’alimentazione, presa dal PC, un altro a massa e gli altri due, attraverso i quali viene trasmessa l’informazione, sono collegati al PDIUSBD12 tramite due resistenze da 22 Ω.

4.3.6 Controllo del pistone

Il pistone collegato al sistema di masticazione viene comandato da un’elettrovalvola o valvola incrementale, che riceve in ingresso una tensione e fornisce in uscita una pressione ad essa proporzionale. A sua volta, tale pressione è proporzionale all’angolo di apertura della mandibola, che può quindi essere controllato tramite una regolazione della tensione in ingresso alla valvola.

Nel circuito tale tensione si ottiene grazie ad un altro potenziometro digitale, configurato allo stesso modo di quelli dedicati alla regolazione degli offset

d’ingresso. Ciò che cambia rispetto a questi è la modalità di aggiornamento del valore della tensione: mentre gli offset, una volta regolati, vengono lasciati costanti, la tensione in ingresso alla valvola incrementale deve avere un profilo temporale che riproduca i movimenti della mandibola durante la masticazione. In particolare, in base a quanto visto nel capitolo 1, siamo interessati ad ottenere un andamento sinusoidale di tale tensione.

L’implementazione di questo meccanismo avviene dal PC e non dal firmware del microcontrollore, che contiene soltanto una subroutine per impostare un determinato valore di tensione.

4.3.7 Alimentazione

Inizialmente si era pensato di utilizzare un’alimentazione duale, in modo da ottimizzare le prestazioni del multiplexer e degli amplificatori utilizzati. Alla fine, però, la scelta è caduta su un’alimentazione singola a 5 V, per motivi di risparmio e di semplicità circuitale (giustificata anche, come illustrato nel paragrafo 4.3.1, dall’ottimizzazione del front-end con i sensori). Tale scelta consente di risparmiare i componenti necessari alla generazione della tensione negativa; inoltre, siccome il microcontrollore lavora esclusivamente con questo tipo di alimentazione, si risparmiano anche i componenti che, in caso di utilizzo di un’alimentazione diversa, si sarebbero dovuti utilizzare per adattare il range di variazione dell’uscita analogica in modo che fosse compreso nell’intervallo 0-5 V.

La scheda viene alimentata dalla rete elettrica tramite un trasformatore il cui circuito secondario è collegato ad un ponte di Gretz. L’uscita di questo viene posta in ingresso ad un regolatore del tipo LM7805, che fornisce in uscita una tensione regolata di 5 V con una corrente massima di circa 1 A.

Per quanto riguarda gli strain gage, il costruttore consiglia di utilizzare un’alimentazione singola pari a VSG =3V. Per generare tale tensione è stato utilizzato un diodo zener della serie BZX85.

Per alimentare correttamente il diodo zener è necessario inserire, tra la tensione di alimentazione VDD e il catodo, una resistenza R di valore tale che su di esso passi una corrente pari a quella di funzionamento; il valore minimo di tale corrente, in base ai datasheet [24], è pari a Iz =80mA. La corrente totale sulla resistenza è data dalla somma di questo valore con quello della corrente assorbita dal circuito a valle. Nella scheda realizzata, questo circuito è costituito dai due ponti di Wheatstone posti in parallelo allo zener. Considerando che le correnti in ingresso agli amplificatori da strumentazione sono di vari ordini di grandezza inferiori rispetto a quelle sui ponti di Wheatstone, le resistenze su ogni ramo dei due ponti sono praticamente in serie; di conseguenza, ogni ponte è equivalente ad una resistenza di circa 120 Ω con ai capi una tensione di 3 V, quindi la somma delle correnti sui due ponti è pari a:

mA ISG 50 120 3 120 3 + = = (4.6)

A questo punto il valore della resistenza può essere ricavato facilmente dalla relazione seguente: Ω = Ω + − = + − = 15.38 50 80 3 5 k I I V V R SG Z SG DD (4.7)

Essendo questo il valore massimo, è stata utilizzata una resistenza di 15 Ω. Ovviamente, nel circuito definitivo, il valore della resistenza sarà diverso, in quanto i ponti di Wheatstone saranno otto. Inoltre, probabilmente lo zener verrà sostituito con uno della serie BZX84, perché questi zener, pur avendo un valore minimo di tensione ottenibile di 3.3 V (che è comunque un valore accettabile per gli strain gage), assorbono una corrente molto minore (5-10 mA).

In figura 4.8 è rappresentato lo schema completo del circuito di alimentazione (per semplicità sono stati omessi i vari condensatori).

- + 0 ponti di Wheatstone 5V circuito 7805 3 1 2 VIN VOUT GN D 0 16 3V 0 ZENER K A 220V ˜

Figura 4. 8: schema del circuito di alimentazione.

4.4 Il microcontrollore PIC16F877A

Il PIC 16F877A [25], appartenente alla famiglia PIC (Peripheral Interface

Controller) della Microchip Technology, è un microcontrollore integrato, ovvero un

dispositivo contenente tutti i componenti necessari per lo sviluppo completo di un sistema elettronico digitale programmabile. La famiglia PIC comprende un elevato numero di microcontrollori, che si differenziano tra di loro per caratteristiche come il numero di porte di I/O, il tipo e la grandezza della memoria, il numero di bit dei bus e la presenza o meno, al proprio interno, di periferiche o altri circuiti che migliorano l’efficienza e la flessibilità del dispositivo ma non sono fondamentali nell’architettura di un microcontrollore, come i comparatori analogici e i convertitori A/D.

Il PIC16F877A è un oggetto piuttosto complesso, una cui trattazione completa, per la quale si rimanda a [25], esula dagli scopi di questo lavoro. Pertanto, nei paragrafi seguenti ci limiteremo a descriverne l’architettura generale e ad approfondire le funzionalità principali utilizzate per la nostra applicazione e per le quali questo dispositivo è stato scelto.

4.3.1 Architettura

Computing), ovvero ha un numero relativamente ridotto di istruzioni (35 per

l’esattezza). La sua architettura, mostrata in figura 4.9, è di tipo Harvard, con la memoria e il bus per i dati separati dalla memoria e dal bus di programma. In particolare, mentre il bus per i dati è a 8 bit, quello per le istruzioni è a 14 bit, ed è dimensionato in modo da poter prelevare ogni istruzione con un solo accesso alla memoria di programma. Inoltre, questa struttura permette l’esecuzione di un’istruzione contemporaneamente al prelievo di quella successiva; si hanno, pertanto, due livelli di pipeline.

Nella figura 4.9 si possono riconoscere i blocchi principali del microcontrollore:

•

i pin esterni, organizzati in 5 porte di I/O;•

la ALU (Arithmetic Logic Unit), che svolge le funzioni di calcolo ed elaborazione dei dati durante l’esecuzione del programma;•

il bus di programma e il bus dati;•

la memoria di programma (Flash Program Memory), la memoria dati e una terza memoria, la Data EEPROM;•

alcuni registri particolari, come il program counter, lo Status Register e l’accumulatore W, e la pila a otto livelli (8 level stack);•

il circuito di connessione al programmatore e all’oscillatore al quarzo esterno (al centro);•

i vari timer: Watch Dog Timer (WDT), Timer0, Timer1, Timer2;•

un convertitore A/D a 10 bit;•

altre periferiche, come il comparatore analogico e la porta seriale sincrona.4.3.2 Organizzazione della memoria

Come abbiamo visto, nel PIC16F877A si trovano tre blocchi di memoria: la memoria di programma, la memoria dati e la data EEPROM.

La memoria di programma (Flash Program Memory) è una EEPROM composta da 8k parole di 14 bit, suddivisa in 4 pagine da 2k locazioni ciascuna. Un program

counter a 13 bit contiene, durante l’esecuzione del programma, l’indirizzo

dell’istruzione successiva, che viene incrementato automaticamente. Se avviene una chiamata ad un sottoprogramma o una richiesta di interruzione, nel program counter viene inserito l’indirizzo della prima istruzione della subroutine, mentre quello che avrebbe dovuto essere l’indirizzo dell’istruzione successiva viene memorizzato in uno Stack Register; questo ha 8 locazioni accessibili con la tecnica LIFO (Last In, First Out), pertanto è possibile annidare fino a 8 chiamate a subroutine.

La memoria dati (RAM File Registers) è una RAM statica formata da quattro banchi di 128 byte ciascuno, in ognuno dei quali le locazioni inferiori sono occupate dagli Special Function Register (SFR), mentre quelle superiori costituiscono i

General Purpose Registers (GPR). L’organizzazione della memoria è rappresentata

in figura 4.10.

Gli SFR sono dei registri utilizzati dalla CPU o dalle periferiche per il controllo e la gestione delle operazioni che il dispositivo deve eseguire; pertanto, ogni locazione di memoria (1 byte) costituisce un registro dedicato ad una funzione specifica. Tra i registri più importanti, alcuni dei quali sono replicati in tutti i banchi di memoria, vi sono:

• Lo Status Register, che contiene i bit che selezionano i banchi della memoria dati, i flag che indicano lo stato aritmetico della ALU e quelli per lo stato di RESET del dispositivo;

• Il registro OPTION_REG, che contiene bit per il controllo delle interruzioni esterne, dei pull-up della PORTB e del prescaler del TIMER0 e del WDT; • Il registro INTCON, che contiene vari flag per la gestione delle interruzioni; • Il registro PCLATH, tramite i quale si può selezionare la pagina della

memoria di programma a cui accedere;

• I registri FSR (File Select Register) e INTN, che permettono di accedere alla memoria tramite indirizzamento indiretto. Più in particolare, ogni operazione di lettura o scrittura sul registro INTN, che in realtà non è un registro fisico, viene eseguita sulla locazione di memoria il cui indirizzo è scritto nell’FSR. C’è poi il registro accumulatore W, la cui peculiarità consiste nel fatto che la ALU vi può accedere direttamente, senza bisogno di fornire alcun indirizzo di memoria.

I GPR, invece, comprendenti in totale 368 byte, possono essere usati per memorizzare dati.

In ogni caso, quando si accede ad un qualunque registro del File Register contenuto in un determinato banco, bisogna accertarsi che i bit di selezione dei

banchi dello Status Register siano impostati per l’accesso a quel banco.

Infine, nel microcontrollore è presente anche una Data EEPROM, che non è mappata nel File Register ma alla quale è possibile accedere tramite indirizzamento indiretto.

Figura 4.10: schema dell’organizzazione della memoria dati del PIC 16F877A. Si può riconoscere la suddivisione in registri generali (GPR) e dedicati a funzioni specifiche (SFR) [25].

4.3.3 Le porte di I/O

Come si può vedere dalla figura 4.9, i pin esterni del microcontrollore (tranne quelli dedicati a funzioni particolari, come l’alimentazione o il collegamento con l’oscillatore al quarzo) sono organizzati in 5 porte: una a 6 bit, tre a 8 bit e una a 3 bit. Si può anche notare che su quasi tutti i pin sono disponibili più funzioni, che tipicamente vengono selezionate in base ad impostazioni dei registri interni ad esse dedicati. Alcuni pin delle porte di I/O, pertanto, sono multiplexati con altre funzionalità relative alle periferiche del dispositivo e in generale, quando una periferica è attiva, i pin ad essa connessi non possono essere utilizzati nelle funzioni di I/O.

In Appendice A è riportata la tabella, tratta da [25], in cui vengono descritte le funzioni di tutti i pin, mentre la piedinatura del PIC16F877A utilizzato per la nostra applicazione (considerando che vi sono varie piedinature disponibili per questo microcontrollore) è rappresentata in figura 4.11.

Il microcontrollore utilizza due registri per la gestione di ognuna delle porte di I/O: i registri PORTA, PORTB, PORTC, PORTD e PORTE, che riportano i valori elettrici delle porte (vedi ancora figura 4.9), e i registri TRISA, TRISB, TRISC, TRISD e TRISE, ognuno associato ad una delle porte e nei quali il valore di ogni bit determina se il pin nella stessa posizione della porta associata è d’ingresso o di uscita. In particolare, se il bit i-esimo del registro TRISn è posto a 1, il pin i-esimo della porta PORTn (indicato con Rni) sarà in ingresso; se è posto a 0, il pin sarà in uscita.

Nella scheda realizzata, le porte di I/O sono state configurate nel modo seguente: • PORTA: il pin RA0, collegato all’uscita del secondo stadio di guadagno,

riceve l’ingresso analogico del microcontrollore; il pin RA4 è collegato ad un pulsante e il pin RA5 ad un led;

• PORTB: il pin RB0 è quello deputato a ricevere in ingresso le interruzioni esterne, pertanto è collegato al pin INT_N del PDIUSBD12 (vedi paragrafo 4.4.5); i pin RB1-RB5 sono collegati ai pin di abilitazione rispettivamente del

multiplexer, del potenziometro di guadagno, dei due potenziometri che regolano gli offset e del dispositivo USB;

• PORTC: RC0 è collegato al pin di abilitazione del potenziometro di controllo della valvola; RC1, RC2 ed RC3 rispettivamente ai pin A0, WR_N e RD_N del PDIUSBD12 (vedi paragrafo 4.4.5); RC5, RC6 ed RC7 rispettivamente ai pin di reset, di clock e di ingresso dei potenziometri digitali (vedi paragrafo 4.4.4);

• PORTD: è collegata al bus del PDIUSBD12;

• PORTE: è collegata ai tre piedini di indirizzo del multiplexer.

Figura 4. 11: piedinatura del PIC16F877A. Possiamo notare che alla maggior parte dei pin è associata più di una funzione [25].

4.3.4 Il convertitore A/D

canali d’ingresso, posizionati sui pin corrispondenti alle porte PORTA (eccetto il pin RA4) e PORTE (vedi figure 4.10 e 4.11). Nella scheda realizzata si è preferito utilizzare un solo ingresso analogico multiplexato perché utilizzando tutti e 8 i canali d’ingresso analogici avremmo avuto un numero minore di pin del microcontrollore a disposizione per il resto dei collegamenti, e perché in questo modo il sistema realizzato può essere più facilmente generalizzabile per l’acquisizione da un numero maggiore di canali.

I registri dedicati alla conversione A/D sono quattro:

• ADRESH e ADRESL, in cui vengono posti, con allineamento a destra o a sinistra, i 10 bit che costituiscono il risultato della conversione;

• ADCON0, che gestisce l’abilitazione e il clock del convertitore e il multiplexing dei canali, e indica se c’è una conversione in corso;

• ADCON1, che configura le funzioni delle porte PORTA e PORTE, determina l’allineamento del risultato della conversione nei registri ADRESH e ADRESL, e gestisce anch’esso il clock del convertitore.

L’acquisizione del segnale convertito può avvenire sia a controllo di programma che tramite interruzione. Nel primo caso (utilizzato nel programma realizzato), per vedere se la conversione è conclusa bisogna controllare il bit del registro ADCON0 che indica lo stato della conversione; nel secondo caso, quando una conversione termina viene mandata una richiesta di interruzione, gestita dal registro INTCON.

Il tempo minimo di conversione può essere ricavato dalla formula seguente [25]:

COFF C

AMP

ACQ T T T

T = + + (4.8)

dove: TAMP, pari a 2 µs, è il settling time dell’amplificatore interno del

convertitore; T è il tempo di carica della capacità del convertitore, ed è C

proporzionale alla resistenza esterna vista dal suo ingresso e alla sua resistenza interna, che dipende dal valore di tensione; TCOFF indica la dipendenza dalla

acquisizione, e aumentare quindi la frequenza massima del segnale in ingresso, si deve cercare di avere una resistenza più bassa possibile in uscita alla parte analogica del circuito. In particolare, il costruttore consiglia un valore minore di 2.5 kΩ. Nel nostro caso, l’utilizzo di un amplificatore non invertente come stadio di uscita consente di ottenere una resistenza d’uscita molto bassa, il cui valore preciso, comunque, dipende dal guadagno ed è difficile da valutare a causa della presenza del potenziometro digitale. In ogni caso, in base ai dati forniti in [25] si ottiene una frequenza minima di circa 50 kHz, che è molto maggiore delle frequenze in gioco nella nostra applicazione.

4.4 Altri componenti elettronici integrati

In questo paragrafo descriviamo gli altri componenti elettronici integrati utilizzati nel circuito: l’amplificatore da strumentazione AD620, utilizzato come front-end analogico con gli strain gage; il multiplexer ADG608; gli amplificatori operazionali LM358 e AD822, impiegati rispettivamente a monte e a valle del multiplexer; i potenziometri digitali AD8400/02/03, usati per la regolazione degli offset, del guadagno del secondo stadio e della tensione di controllo del pistone; il PDIUSBD12, che svolge la funzione di interfaccia nella comunicazione tra microcontrollore e PC.

4.4.1 L’amplificatore da strumentazione AD620

Si tratta di un componente utilizzato in svariate applicazioni, in particolare per l’interfacciamento con sistemi di trasduzione.

La piedinatura di questo dispositivo è mostrata in figura 4.12.

Il piedino REF viene collegato ad un potenziometro digitale che, regolando la tensione di riferimento, imposta l’offset in uscita.

piedini RG e calcolandolo in base alla relazione seguente [17]: 1 4 . 49 Ω+ = R k G (4.9)

Il guadagno massimo è pari a 1000, ottenibile ponendo R=49.45 Ω. Impostare un

valore di G elevato è auspicabile, perché al crescere del guadagno migliorano le

prestazioni del componente (ad esempio, il rumore riportato in ingresso diminuisce al crescere del guadagno).

Nel nostro caso, viste le basse tensioni d’ingresso, è stato impostato un guadagno pari a G=989, ottenuto utilizzando una resistenza da 50 Ω.

Figura 4. 12: piedinatura dell’AD620 [17].

Per i nostri scopi, le caratteristiche più rilevanti di questo componente (in particolare dell’AD620A, che è la versione utilizzata nel nostro sistema) sono le seguenti [17]:

• Il CMRR è molto elevato: in corrispondenza del guadagno massimo, pari a G=1000, è compreso tra 110 dB e 130 dB;

• L’impedenza d’ingresso è pari a 10 GΩ;

• La tensione di offset è, per i nostri scopi, abbastanza contenuta: quella d’ingresso ha un valore tipico di 30 µV e uno massimo di 125 µV;

• La corrente di bias è compresa tra 0.5 e 2 nA, quella di offset tra 0.3 e 1 nA, molto minori della corrente che passa sugli strain gage (pari a circa 13.75 mA);

• Il valore picco-picco della tensione di rumore in bassa frequenza (0.1-10 Hz) è di 0.28 µV. Tale dato è interessante perché il sistema di masticazione lavora in questo range di frequenze.

4.4.2 Il multiplexer analogico ADG608

Si tratta di un multiplexer a otto canali, avente il diagramma funzionale e la piedinatura rappresentati in figura 4.13.

Figura 4.13: diagramma funzionale e piedinatura dell’ADG608 [18].

Il piedino EN di abilitazione e i piedini A0, A1 e A2, che rappresentano l’indirizzo del canale attivo secondo la modalità di indirizzamento descritta nella figura 4.14, sono pilotati dal microcontrollore.

Le caratteristiche rilevanti di questo componente sono [18]: • correnti di perdita dell’ordine delle frazioni di nA; • una differenza media tra le resistenze di canale di 5 Ω;

• una capacità d’ingresso di 40 pF e 54 pF con multiplexer spento e acceso; • un andamento della resistenza in funzione della tensione di ingresso, in

corrispondenza di vari valori della tensione di alimentazione, rappresentato in figura 4.15.

Figura 4.15: andamento della resistenza di canale in funzione della tensione d’ingresso con un’alimentazione duale di ±3 V e ±5 V (sopra) e un’alimentazione singola di 3 V e 5 V (sotto) [18].

4.4.3 Gli amplificatori operazionali LM358 e AD822

Sono due integrati contenenti ognuno due amplificatori operazionali indipendenti, con la piedinatura rappresentata in figura 4.16.

Viene utilizzato un LM358 per ogni canale per implementare il filtro passa-basso e il notch, mentre tramite un AD822 è stato realizzato il secondo stadio di filtraggio e di guadagno variabile.

Figura 4. 16: piedinatura dell’LM358 e dell’AD822.

La differenza tra questi due componenti sta nelle prestazioni e nei costi: l’LM358 è un dispositivo a bassissimo costo, pertanto è stato scelto per una funzione per cui servono un numero di componenti pari al numero di canali. Invece, l’AD822 è più caro ma ha prestazioni migliori, in particolare per quanto riguarda la dinamica; infatti, è un dispositivo rail-to-rail, perciò viene impiegato nel secondo stadio di guadagno, dove tale caratteristica risulta importante perché permette di sfruttare tutta o quasi la dinamica del convertitore A/D del microcontrollore (alimentato anch’esso a 5 V).

Altre caratteristiche interessanti dell’AD822 sono [22]: • un offset massimo in ingresso pari a 800 µV;

• stadio d’ingresso a JFET con corrente di bias massima di 25 pA;

• una tensione e una corrente di rumore in ingresso rispettivamente di 2 µV e 18 fA picco-picco alle basse frequenze (0.1-10 Hz).

4.4.4 I potenziometri digitali AD8400/AD8402/AD8403

Questi dispositivi [19] implementano una funzione analoga a quella di un potenziometro o di una resistenza variabile, con la differenza che il valore della resistenza è programmabile in modo digitale tra 256 possibili posizioni. Nel circuito di acquisizione i potenziometri digitali vengono utilizzati per la regolazione degli offset degli amplificatori da strumentazione, per l’impostazione del guadagno del secondo stadio di amplificazione e per la generazione della tensione di controllo della valvola incrementale.

In figura 4.17 sono rappresentate le piedinature dei potenziometri AD8400, AD8402 e AD8403, che contengono rispettivamente una, due e quattro resistenze variabili indipendenti, e lo schema dell’AD8403.

Tra i terminali A e B di ogni canale è presente una resistenza di valore fisso (1 kΩ, 10 kΩ, 50 kΩ o 100 kΩ a seconda del modello specifico), mentre il piedino W è collegato in un punto del resistore determinato da un codice digitale a 8 bit, memorizzato nel registro del canale e precedentemente trasmesso al potenziometro tramite il piedino SDI. Tra un canale e l’altro si ha una tolleranza di matching dell’1%.

In riferimento alla figura 4.17, il piedino /RS (attivo basso) impone il posizionamento dei W a metà scala, in modo che le resistenze tra A e W e quella tra B e W di ogni canale siano uguali. Il piedino /SHDN, anch’esso attivo basso, rende flottanti i piedini A e mette in corto circuito i W con i B di ogni canale, ponendo il potenziometro in una configurazione a consumo minimo di potenza. /CS è il piedino di abilitazione: in seguito al suo passaggio da 1 a 0 si ha l’acquisizione di dati tramite il piedino SDI, come rappresentato dal diagramma di temporizzazione in figura 4.18. I primi due bit trasmessi, A1 e A0, rappresentano l’indirizzo del resistore nel cui registro si intende scrivere un dato; per l’AD8402 deve essere A1=0 (con A0 si discrimina tra i due canali), e per l’AD8400 A1=A0=0. Gli altri otto bit rappresentano il valore Dx da scrivere nel registro del canale selezionato; tale

seguente relazione: W BA WB R R Dx Dx R = ⋅ + 256 ) ( (4.10)

dove RBA è la resistenza nominale tra A e B ed R è la resistenza di contatto del W

terminale B, pari a 50 Ω.

Figura 4. 17: sopra: piedinatura dei potenziometri digitali AD8400, AD8402 e AD8403, contenenti rispettivamente uno, due e quattro resistenze variabili programmabili in modo digitale. Sotto: schema di funzionamento logico dell’AD8403. Per ognuno dei quattro canali, il cui indirizzo è selezionato dal DAC SELECT in base ai valori dei bit A1 e A0, si ha un latch a 8 bit in cui è memorizzato il dato che determina la posizione di W, e quindi le resistenze tra i piedini W e B e tra W ed A di quel canale [19].

Allo stesso modo, considerando che la resistenza tra A e B è fissata, e che anche il terminale A ha una resistenza di contatto di 50 Ω, tra A e W si ha una resistenza pari a: W BA WA R R Dx Dx R = − ⋅ + 256 256 ) ( (4.11)

In figura 4.19 sono rappresentati gli andamenti di R e WB R in funzione del WA

codice memorizzato nel registro corrispondente.

Si può utilizzare un potenziometro digitale per avere una tensione proporzionale ad una tensione di riferimento secondo il codice memorizzato nel registro; ponendo tale tensione di riferimento tra A e B si ottiene sul piedino W una tensione pari a:

B AB W V V Dx Dx V = ⋅ + 256 ) ( (4.12)

dove VB è la tensione presente sul terminale B e VAB è la tensione di riferimento.

Figura 4. 18: diagramma di temporizzazione degli AD840X. In seguito al passaggio da 1 a 0 di /CS, vengono acquisiti e memorizzati sul registro seriale interno i 10 valori binari presenti nel piedino SDI in corrispondenza di altrettanti fronti di salita del clock; i primi due bit corrispondono all’indirizzo del resistore sul cui latch si vuole memorizzare il dato, che è costituito dagli 8 bit successivi [19].

Nel nostro circuito di acquisizione questo metodo è stato utilizzato per la regolazione dell’offset degli amplificatori in ingresso e per generare la tensione di controllo della valvola di comando del pistone, collegando A all’alimentazione, B a

massa e W al piedino di riferimento dell’amplificatore o all’ingresso della valvola. Un'altra possibile configurazione, utilizzata nello stadio di amplificazione del circuito, consente di ottenere un guadagno programmabile, dato dalla relazione:

R R Dx R R R Dx R Dx R G WB BA W ≅ + ⋅ BA + ⋅ + = + = 256 1 256 1 ) ( 1 (4.13)

dove l’ultima eguaglianza è vera se RBA <<R. Questa relazione è verificata nel nostro caso, in quanto è stato posto R=3.9 kΩ. Perciò, considerando che il potenziometro utilizzato ha RBA =100kΩ, si ottiene un guadagno variabile tra 1 e 26.6, con un passo di 0.1.

Figura 4.19: andamento della resistenze tra i terminali W e B (RWB) e tra i terminali W e A (RWA), espresse in percentuale della resistenza nominale tra A e B, in funzione del codice a 8 bit memorizzato nel registro corrispondente [19].

4.4.5 Il PDIUSBD12

È un dispositivo USB integrato utilizzato in sistemi a microcontrollore come interfaccia di comunicazione tra questo e il PC. Possiamo descrivere brevemente le

funzioni dei pin, organizzati secondo la configurazione di figura 4.20 [23].

Figura 4.20: piedinatura del PDIUSBD12 [23].

• DATA<0>…DATA<7>: formano il bus bidirezionale di dati per la comunicazione con il microcontrollore;

• ALE (Address Latch Enable): serve in caso di indirizzamento multiplexato sul bus;

• CS_N (Chip Select): abilita il dispositivo (attivo basso); • SUSPEND: attiva lo stato di “SUSPEND”;

• CLKOUT: eventuale clock esterno;

• INT_N: effettua la richiesta di interrupt al microcontrollore (attivo basso); • RD_N: abilita la lettura del bus DATA<0>…DATA<7> (attivo basso); • WR_N: abilita la scrittura del bus DATA<0>…DATA<7> (attivo basso); • DMREQ, DMACK_N, EOT_N: servono per i trasferimenti a indirizzamento

diretto di memoria (DMA), che noi non utilizziamo;

• RESET_N: attiva il circuito di reset del dispositivo (attivo basso);

• GL_N: si collega ad un led che fornisce un’indicazione dello stato del dispositivo: lampeggia durante la fase di enumerazione e quando si ha

trasferimento di dati sul bus, rimane acceso quando la fase di configurazione termina correttamente e si spegne quando il dispositivo entra nello stato di SUSPEND;

• XTAL_1, XTAL_2: vengono collegati ad un oscillatore al quarzo di 6 MHz; • D+, D-: collegati al connettore USB tramite due resistenze esterne.

Costituiscono la linea di comunicazione con il PC;

• Vout3.3: tensione di 3.3 V regolata;

• A0: bit di indirizzo. Se alto seleziona un’istruzione di comando, se basso la fase di trasferimento dei dati.

• Dal punto di vista del funzionamento interno, il dispositivo è rappresentabile con lo schema a blocchi di figura 4.21. Si possono riconoscere:

• Un transceiver analogico che si collega al connettore USB tramite due resistenze esterne;

• Il regolatore di tensione a 3.3 V;

• Un PLL da 6 MHz a 48 MHz per il cui funzionamento serve solo l’oscillatore esterno da 6 MHz;

• Un circuito per il recupero del segnale di clock (bit clock recovery), tramite

oversampling, dai dati provenienti dall’USB;

• La Serial Interface Engine (SIE), che implementa per via hardware l’intero protocollo USB e che svolge le funzioni di: riconoscimento del pattern di sincronizzazione, conversione parallelo/seriale, bit stuffing/de-stuffing, generazione e controllo del CRC (Cycle Redundancy Check), generazione e verifica del PID (Product IDentificator), generazione e valutazione dell’handshake (vedi capitolo successivo);

• Il SoftConnect, un sistema che permette di gestire l’inizializzazione del sistema tramite il firmware del microcontrollore. Infatti, solitamente nei sistemi USB, al momento del collegamento del cavo, il piedino D+ viene messo alto tramite una resistenza di pull-up di 1.5 kΩ; nel PDIUSBD12 tale resistenza è integrata e non è collegata direttamente all’alimentazione. Per

eseguire tale collegamento esiste una specifica istruzione, tramite la quale il microcontrollore può effettuare l’inizializzazione prima della connessione al cavo USB;

• La MMU (Memory Management Unit) e la RAM integrata, che svolgono la funzione di buffer per adattare la velocità della comunicazione parallela tra microcontrollore e dispositivo a quella con l’USB. In questo modo il microcontrollore può leggere e scrivere dati in protocollo USB alla propria velocità;

• L’interfaccia parallela/DMA, che costituisce il circuito collegato fisicamente al microcontrollore. Dall’esterno è vista come una memoria con un bus a 8 bit e un bit di indirizzamento, che può essere anche multiplexato in quanto si hanno a disposizione due locazioni di memoria. Può gestire anche trasferimenti ad accesso diretto di memoria (DMA).

Figura 4.21: schema a blocchi del PDIUSBD12 [23].

delle quali corrisponde un codice di un byte che deve essere prelevato dal bus, e per ognuna delle quali il dispositivo ha in memoria l’implementazione hardware dell’azione di risposta. Pertanto, per comunicare con il dispositivo (e quindi con il PC), il microcontrollore deve richiamare la parte del proprio firmware contenente l’implementazione dell’istruzione il cui codice è contenuto nel bus. Questo processo avviene in seguito ad una richiesta di interruzione che parte dal PC o dall’utente tramite il programma di interfacciamento ad alto livello (vedi capitolo successivo), viene trasmessa al PDIUSBD12 sotto forma di codice e arriva al microcontrollore tramite il piedino INT_N.

Nel capitolo successivo verranno descritte più in dettaglio sia le modalità in cui avviene questa comunicazione che il firmware del microcontrollore.

![Figura 4. 9: architettura del PIC16F877A [25].](https://thumb-eu.123doks.com/thumbv2/123dokorg/5691629.72618/19.892.187.774.422.1056/figura-architettura-del-pic-f-a.webp)