Capitolo 3 - Progettazione di un’interfaccia

SPI per bus AMBA APB

La figura 3.1 mostra il flusso di progetto seguito.

Le specifiche imponevano di realizzare un’interfaccia SPI, il cui comportamento è descritto nel capitolo 1 e il cui standard è definito in [2], per bus AMBA APB, il cui comportamento è descritto nel capitolo 1 e il cui standard è definito in [1]. L’intera struttura è stata divisa in sottoblocchi più semplici che sono stati descritti in linguaggio VHDL; ogni blocco è stato sottoposto a test per verificarne la corretta funzionalità. In seguito è stato effettuato l’assemblaggio e sono stati eseguiti vari test funzionali sull’intera interfaccia per verificarne la completa compatibilità con gli standard; per la descrizione dei test si rimanda al capitolo 4. Tali test sono stati effettuati successivamente anche per verificare la corretta sintesi e la corretta mappatura su FPGA. Lavorando poi sui parametri di sintesi e di layout si è cercato di ottimizzare le prestazioni in termini di occupazione e velocità, per una stima di tali prestazioni ed un confronto con quelle di interfacce commerciali dello stesso tipo si rimanda al capitolo 4.

3.2 Struttura dell’interfaccia SPI – APB

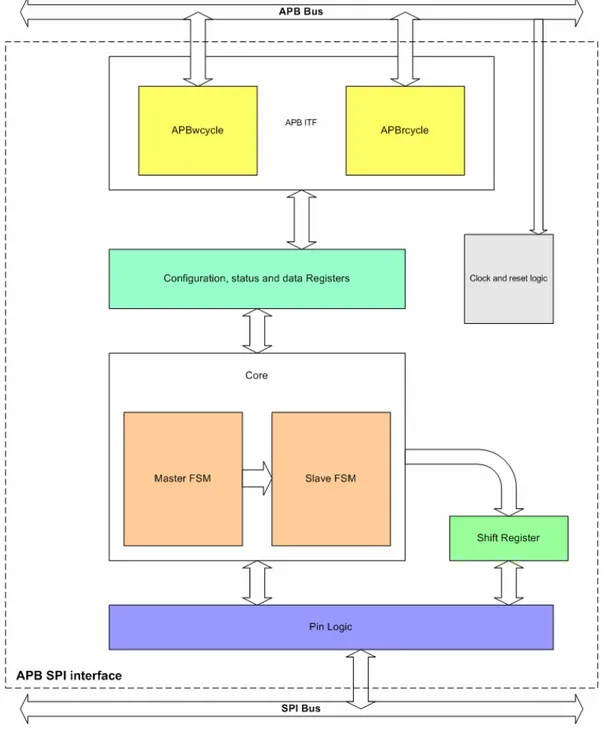

L’interfaccia progettata comunica da un lato con un bus SPI, sia come master che come slave, dall’altro con un bus AMBA APB come slave, secondo gli standard sopra citati. Come master SPI è in grado di pilotare più slave mediante le linee SSn.

Essa è costituita dai seguenti blocchi:

• L’interfaccia APB vera e propria, divisa in due sottoblocchi che controllano scrittura e lettura sui registri interni.

• Una serie di registri di configurazione, dati e controllo.

• Il core vero e proprio costituito da due macchine a stati finiti per il controllo della trasmissione SPI master e di quella slave.

• Un registro di shift parallelo-seriale, seriale-parallelo. • La logica per il controllo dei pin SPI.

• La logica di controllo del clock e del reset dell’intera interfaccia.

I blocchi sono progettati in modo che se si desidera implementare un’interfaccia che operi unicamente come slave si possono non sintetizzare alcune parti variando unicamente il top del progetto e risparmiando in termini di area occupata.

Fig 3.3 Schema a blocchi dell’interfaccia SPI-APB

3.3 Interfaccia AMBA APB

L’interfaccia APB è costituita da due blocchi APBrcycle e APBwcycle che controllano rispettivamente lettura e scrittura del bus APB accedendo direttamente ai registri dell’interfaccia.

3.3.1 Lettura dal bus APB

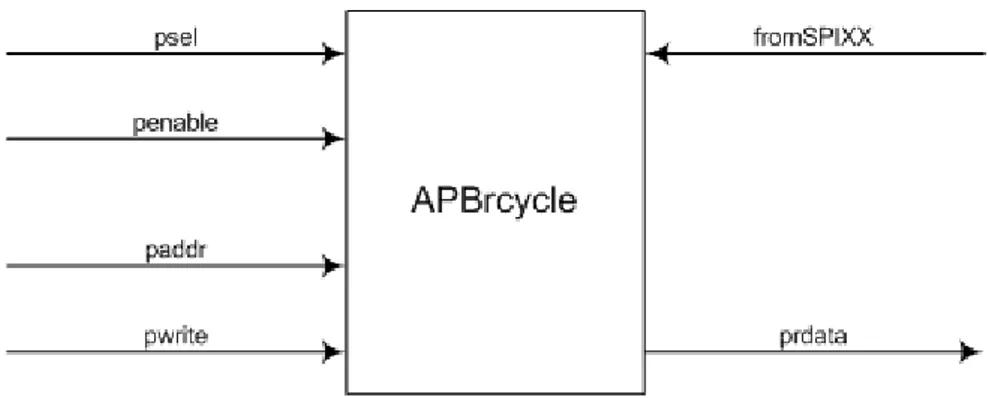

Il blocco che gestisce la lettura dai registri interni dell’interfaccia multiplexa i vari segnali provenienti da essi a seconda degli indirizzi e dei segnali di controllo APB.

Fig 3.4 Ingressi e uscite del blocco APBrcycle

Segnale Direzione Descrizione

Psel, penable, pwrite IN Segnali di abilitazione e controllo del bus APB

Paddr IN Costituito da tre bit rappresenta l’indirizzo interno del registro a cui si vuole accedere

fromSPIXX IN Costituito da sei vettori da 8 bit, ciascuno proveniente dal registro interno corrispondente

Prdata OUT Costituito da 8 bit rappresenta il dato letto dal bus APB

3.3.2 Scrittura sul bus APB

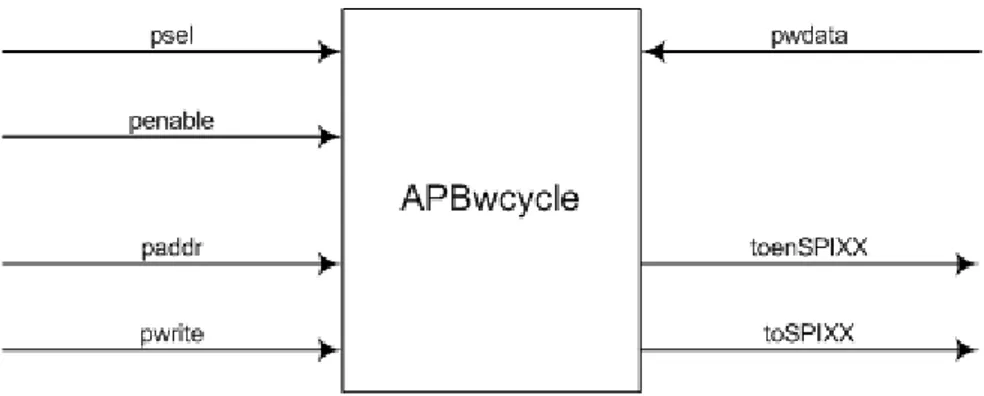

Il blocco che gestisce la scrittura sui registri interni dell’interfaccia non fa che abilitare la scrittura sugli stessi attraverso i segnali toenSPIXX a seconda degli indirizzi e dei segnali di controllo APB.

Fig 3.5 Ingressi e uscite del blocco APBwcycle

Segnale Direzione Descrizione

psel,penable, pwrite IN Segnali di abilitazione e controllo del bus APB Paddr IN Costituito da tre bit rappresenta l’indirizzo

interno del registro a cui si vuole accedere pwdata IN Costituito da 8 bit rappresenta il dato scritto sul

bus APB

toSPIXX OUT Costituito da sei vettori da 8 bit, ciascuno diretto all’ingresso del registro interno corrispondente

toenSPIXX OUT Sei bit ciascuno diretto all’enable del registro interno corrispondente

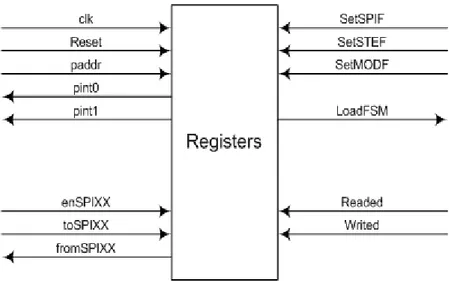

3.4 Registri interni di configurazione, dati e controllo

Il blocco registers contiene i vari registri interni dell’interfaccia che ricalcano quasi completamente quelli descritti nello standard SPI, ad eccezione del registro SPISS, aggiunto per rendere possibile il controllo di più slave SPI contemporaneamente, e di alcuni bit di controllo per la modalità bidirezionale mancanti, dato che tale modalità non è supportata. Tale blocco provvede anche alla gestione dei piedini di interruzione verso il bus AMBA APB e all’aggiornamento dei flag secondo lo standard SPI.

Segnale Direzione Descrizione

Paddr IN Costituito da tre bit rappresenta l’indirizzo interno del registro a cui si vuole accedere

fromSPIXX OUT Costituito da sei vettori da 8 bit, ciascuno proveniente dal registro interno corrispondente

toSPIXX IN Costituito da sei vettori da 8 bit, ciascuno diretto all’ingresso del registro interno corrispondente

enSPIXX IN Sei bit ciascuno diretto all’enable del registro interno corrispondente

pint0, pint1 OUT Piedini di interruzione rispettivamente di buffer dati ricevuti pieno o di errore di mode fault e di buffer di trasmissione vuoto

SetSPIF, SetSPTEF, SetMODF

IN Segnali provenienti dal core per il set dei rispettivi flag

LoadFSM OUT Segnala al core un'avvenuta scrittura nel registro dati

Writed, readed IN Segnali provenienti dall’interfaccia APB indicano una avvenuta scrittura o lettura sui registri interni. Sono usati assieme a paddr per il clear dei flag

La mappa dei registri interni così come la loro funzione ricalca quella indicata nello standard SPI, con alcune eccezioni:

SPICR2 : SPI control register 2

Bit 7 6 5 4 3 2 1 0

R 0 0 0 0 0 0

W no no no MODFEN no no SPISWAI no

La funzione dei singoli bit è quella indicata nello standard ma mancano i campi BIDIROE e SPC0 relativi alla modalità bidirezionale che non è non supportata. SPISS: SPI slave select register

Bit 7 6 5 4 3 2 1 0

R

W SS7 SS6 SS5 SS4 SS3 SS2 SS1 SS0

In modalità master ciascun bit abilita in uscita la linea di selezione dello slave corrispondente, in tal modo è possibile realizzare bus SPI dove si possono selezionare distinguendo fino a 8 slave. In modalità slave solo la linea 0 è attiva come ingresso.

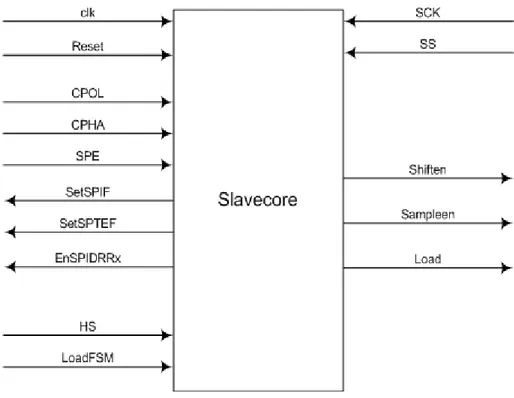

3.5 Core

Il core è costituito da due macchine a stati finiti, realizzate sul modello di Moore; esse sono contenute nei blocchi slavecore e mastercore e controllano rispettivamente lo scambio dati SPI attraverso lo shift register e la generazione dei segnali SCK e SS per la modalità master. E’ stato preferito l’utilizzo di molti stati ognuno con poche operazioni per ridurre la logica combinatoria e migliorare le prestazioni in termini di velocità.

3.5.1 Controllo dello shift register

La macchina a stati finiti che controlla lo shift register riceve in ingresso, oltre ai bit di controllo, il clock SPI di trasmissione SCK e il segnale di selezione slave SS; esso pilota di conseguenza lo shift register caricando parallelamente il dato su di esso, facendolo shiftare serialmente o prelevandolo parallelamente.

Segnale Direzione Descrizione

CPHA, CPOL, SPE IN Bit di controllo del registro di controllo, controllano fase, polarità e stato della trasmissione.

SetSPIF, SetSPTEF OUT Segnali verso il registro di stato per il set dei rispettivi flag

EnSPIDRRx OUT Segnale verso il registro dati per il prelievo del dato parallelo dallo shift register

HS IN Segnale proveniente dal mastercore che indica che sta avvenendo una trasmissione master alla massima velocità

loadFSM IN Segnale di avvenuta scrittura nel registro dati

SCK, SS IN Segnali di sincronismo e selezione provenienti dal master SPI

Shiften, Sampleen, Load

OUT Segnali di controllo dello shift register, rispettivamente: shift, controllo di campionamento ingresso seriale, caricamento parallelo del dato

Stato Descrizione

IDLE La macchina a stati attende un comando di caricamento parallelo del dato nello shif register o l’inizio di una trasmissione SPI LOADING Il dispositivo carica parallelamente il dato dallo SPIDR allo shift

register

SETSPTEF Ha inizio la trasmissione SPI, la macchina setta il flag SPTEF nell’ SPICR1

SHIFT La macchina comanda uno shift allo shift register

SAMPLE La macchina comanda il campionamento del dato seriale allo shift register

AWAITSH Il dispositivo attende di entrare nello stato di shift

AWAITSA Il dispositivo attende di entrare nello stato di sample

UNLOAD Il dato nello shift register viene passato parallelamente al registro SPIDR di ricezione, viene settato il flag SPIF

AWAIT La macchina attende la fine della trasmissione SPI

Tab 3.5 Descrizione degli stati interni del blocco slavecore

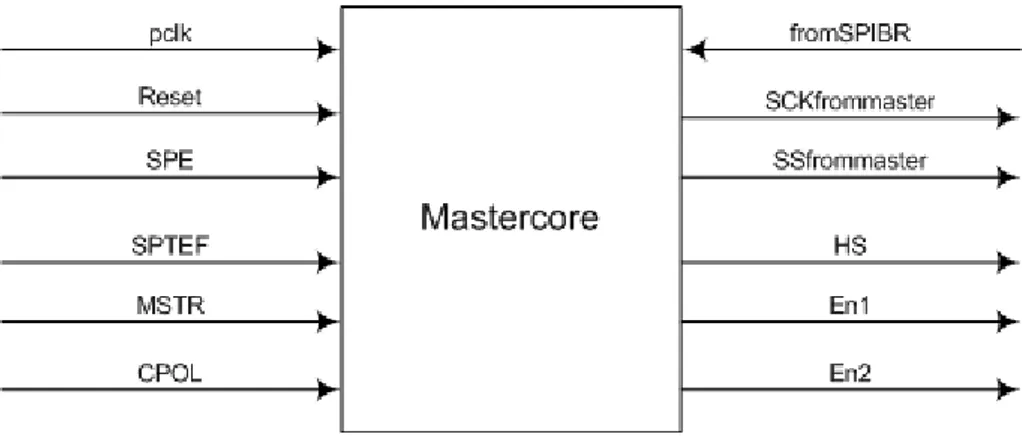

3.5.2 Generazione dei segnali SCK e SS per la modalità master

La macchina a stati finiti che controlla la generazione dei segnali SCK e SS per la modalità master riceve in ingresso oltre ai bit di controllo, i bit indicanti la velocità di trasmissione dal registro di baud rate (SPIBR) e genera di conseguenza i segnali SCK e SS. Per la generazione del segnale SCK il blocco mastercore fa uso di un divisore programmabile di frequenza contenuto nel blocco freq_divider e costituito da un prescaler e da un contatore con flip-flop T in uscita.

Fig 3.8 Ingressi e uscite del blocco mastercore

Segnale Direzione Descrizione

MSTR, CPOL, SPE IN Bit di controllo del registro di controllo, controllano modalità, polarità e stato della trasmissione.

SPTEF IN Flag di buffer di trasmissione vuoto dal registro di stato, indica alla macchina a stati quando far partire una nuova trasmissione master.

fromSPIBR IN Segnale composto da sei bit indicanti la velocità di trasmissione dal registro di baud rate

SCKfrommaster, SSfrommaster

OUT Segnali generati per la trasmissione SPI

En1, En2 OUT Segnali per la sincronizzazione di MOSI con SCK alla logica per il controllo dei pin SPI

HS OUT Segnale che indica allo slavecore che sta

avvenendo una trasmissione master alla massima velocità

Il dispositivo evolve negli stati descritti in tabella 3.7.

Stato Descrizione

IDLE La macchina attende che l’interfaccia sia abilitata come master

WAITTX Il dispositivo attende una scrittura nell’SPIDR per dare inizio alla trasmissione SPI come master

WAITti1,WAITti2 Ha inizio la trasmissione SPI, la macchina attende un idling time minimo nel caso di due trasferimenti consecutivi

WAITtl La macchina attende il leading time minimo (mezzo ciclo di SCK)

TX1,TX2 Il dispositivo si evolve nella trasmissione vera e propria

CNT La macchina incrementta il contatore dei bit trasmessi. Ad otto la trasmissione ha termine

WAITtt La macchina attende il trailing time minimo (mezzo ciclo di SCK) prima di tornare nello stato di IDLE o riiniziare subito una nuova trasmissione

Tab 3.7 Descrizione degli stati interni del blocco mastercore

3.6 Registro di shift parallelo-seriale, seriale-parallelo

Il registro di shift e conversione parallelo-seriale e seriale-parallelo è contenuto nel blocco shift-reg, esso si comporta contemporaneamente da PISO (parallel input - serial output) e da SIPO (serial input - parallel output). Infatti esso carica parallelamente il dato da trasmettere e lo shifta mano a mano sull’uscita seriale; contemporaneamente campiona l’ingresso seriale shiftando il dato all’interno del registro che a fine trasmissione viene passato parallelamente al registro dati.

Fig 3.9 Ingressi e uscite del blocco shiftreg

Segnale Direzione Descrizione

Serialin IN Ingresso dati seriale proveniente dalla logica di controllo dei pin SPI

Serialout OUT Uscita dati seriale verso la logica di controllo dei pin SPI

Parallelin IN Ingresso dati parallelo a 8 bit proveniente dal registro dati

Parallelout OUT Uscita dati parallela a 8 bit verso il registro dati Shiften, Sampleen,

Load

IN Segnali di controllo provenienti dallo slavecore, rispettivamente: shift, controllo di campionamento ingresso seriale, caricamento parallelo del dato

LSBFE IN Bit di controllo dal registro di controllo che indica quale bit va trasmesso per primo se il più o il meno significativo

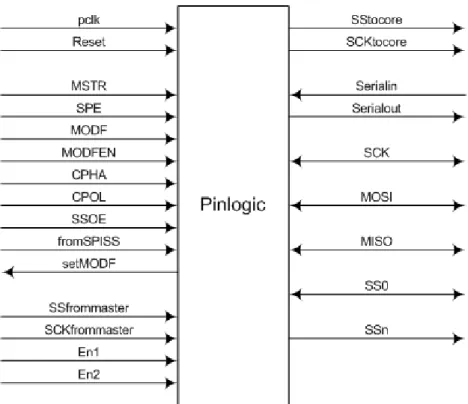

3.7 Logica per il controllo dei pin SPI

La logica per il controllo dei pin SPI, contenuta nel blocco pinlogic, ha il compito di campionare e sincronizzare i dati seriali, di controllare i segnali di abilitazione per le linee bidirezionali e infine multiplexare i segnali SCK e SS a seconda della modalità, master o slave. Inoltre in essa vi è la logica per il controllo dell’errore di mode fault.

Segnale Direzione Descrizione

MSTR, SPE, MODF, MODFEN, CPHA, CPOL, SSOE

IN Bit di controllo provenienti dai registri di controllo

fromSPISS IN Uscita del registro di selezione degli slave per il controllo delle linee SSn

SetMODF OUT Segnale verso il registro di stato per il set del rispettivo flag

SCKfrommaster, SSfrommaster

IN Segnali generati dal mastercore per la trasmissione SPI in modalità master

En1, En2 IN Segnali per la sincronizzazione di MOSI con SCK provenienti dal mastercore

SStocore, SCKtocore OUT Segnali SS e SCK multiplexati a seconda della modalità (master o slave) per il blocco slavecore

Serialin IN Ingresso seriale collegato all’uscita seriale dello shift register per la sincronizzazione Serialout OUT Uscita seriale collegata all’ingresso seriale

dello shift register per la sincronizzazione

SCK, MOSI, MISO, SS0, SSn

INOUT Segnali SPI

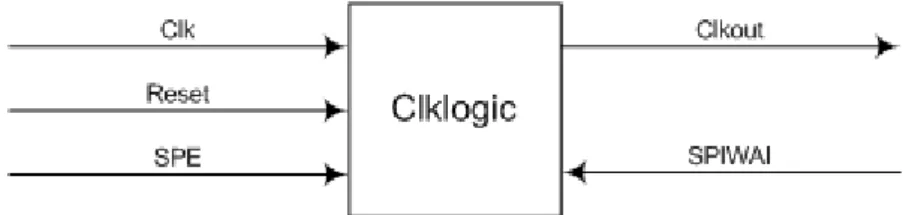

3.8 Logica di controllo del clock e del reset

La logica per il controllo del clock contenuta nel blocco clklogic gestisce la modalità di wait dell’interfaccia disabilitando il clock di alcuni blocchi.

Essa è costituita essenzialmente da una macchina a stati che controlla il segnale di abilitazione del clock. Il cool clock così generato viene inviato a tutti i blocchi tranne che ai registri che servono per riabilitarlo e alla logica per il controllo del reset.

Fig 3.11 Ingressi e uscite del blocco clklogic

Segnale Direzione Descrizione

SPE, SPIWAI IN Bit di controllo del registro di controllo

Clkout OUT Cool clock generato

Tab 3.10 Descrizione degli ingressi e delle uscite del blocco clklogic

Stato Descrizione

RUN Stato di funzionamento normale in cui il cool clock è attivo

OUTDIS Se le uscite SPI vengono disabilitate, tramite il bit SPE nel registro di controllo, la macchina entra in questo stato in cui attende che anche il clock venga disabilitato tramite il bit SPIWAI

STOP La macchina disabilita il cool clock

Tab 3.11 Descrizioni degli stati interni del blocco clklogic

La logica per il controllo del reset non fa che sincronizzare l’uscita dal reset con il clock di sistema, tale reset è poi collegato a tutti i reset dei vari blocchi.