Capitolo 3

Blocchi funzionali

3.1. Introduzione

In questo lavoro di tesi è stato ripreso il progetto dell’interfaccia con il linearizzatore sequenziale con lo scopo di arrivare ad una sua realizzazione su silicio e verificarne il corretto funzionamento in una successiva fase di test. Sono state apportate al circuito piccole modifiche, aggiunti dei blocchi e realizzato il layout dei singoli dispositivi. In particolare sono stati aggiunti dei dispositivi di calibrazione in diversi blocchi circuitali con le seguenti funzioni:

• in ingresso al telescopico per correggere l’offset in ingresso dovuto al

mismatch dei condensatori e all’iniezione di carica degli interruttori; in questo caso la rete di calibrazione è stata progettata in modo che, in

assenza del sensore vero e proprio, potesse comportarsi da dummy sensor e permettere il testing dell’intera interfaccia.

• in ingresso al preamplificatore per regolare il guadagno;

• in ingresso al generatore di tensioni di riferimento per consentire di

spostare le tensioni di vertice;

• in ingresso all’amplificatore a guadagno variabile per regolare la

pendenza dei vari tratti della spezzata che approssima la caratteristica. Un problema che si è incontrato frequentemente è quello dovuto ai difetti degli interruttori, presenti in numero elevato. Si è dovuto tener conto del loro effetto sia nella progettazione dei blocchi di calibrazione che nella realizzazione dei layout dei dispositivi.

3.2. Comportamento non ideale degli

interruttori

Nei circuiti a condensatori commutati bisogna fare particolarmente attenzione ai disturbi e al rumore introdotti dagli interruttori poiché vanno a perturbare la tensione sui condensatori di tenuta. Uno dei principali problemi che affliggono questi circuiti è l’iniezione di carica, dovuta alla carica accumulata nel canale dei mosfet che costituiscono gli interruttori. L’effetto dell’iniezione di carica si presenta quando gli switch tendono a spegnersi, per cui questa carica indesiderata finisce nei condensatori di tenuta compromettendo il corretto funzionamento del circuito.

+ -Vin CH + _ Vout 1

p

Figura 3.1: esempiodell’effetto dell’iniezione di carica.

Se supponiamo che questa carica si divida in parti uguali tra Source e Drain allora la carica che finisce nel condensatore di tenuta CH è

(

)

2 ox GS thn H C WL V V Q − ∆ = (3.1)dove Vthn è la tensione di soglia degli NMOS. Quindi la variazione di tensione in

uscita vale

(

)

2 ox in thn out H C WL Vdd V V V C − − ∆ = − (3.2)Un altro difetto dovuto alla presenza degli interruttori è il clock feedthrough. Per valutane gli effetti consideriamo la figura seguente.

+

-V

inC

H+

_

V

out1

2

C

ox1

2

C

oxFigura 3.2: effetto del clock feedthrough.

Quando il segnale che pilota l’interruttore commuta verso il basso, le capacità parassite del mos formano un partitore di tensione con il condensatore di mantenimento per cui sul nodo di uscita si ha una variazione di tensione pari a

0 0 out H C V Vdd C C ∆ = + (3.3)

dove C0 è la capacità di sovrapposizione tra Gate e Drain/Source e vale 0 ox

C =C W LD⋅ ⋅

e LD è la lunghezza della zona di sovrapposizione fra gate e Drain/Source.

Per ridurre questi disturbi è utile usare transistori piccoli ed evitare quando possibile elevate frequenze di commutazione. Un’altra soluzione è quella di mettere in serie al MOS un dummy-switch, cioè un MOS con source e drain cortocircuitati e pilotato da un segnale in controfase rispetto a quello che controlla il vero interruttore. +

-V

inC

H + _V

out M1 M2 1 p p1 1 1 1 2 W LFigura 3.3:dummy switch per minimizzare l’effetto dell’iniezione di carica.

Se il dummy-switch è tale da avere dimensioni pari alla metà del MOS che lo precede allora, almeno in via del tutto teorica, tutta la carica iniettata verso il condensatore di tenuta finisce nel canale di M2. Tuttavia i complicati meccanismi che regolano l’iniezione di carica fanno sì che una perfetta cancellazione non sia ottenibile.

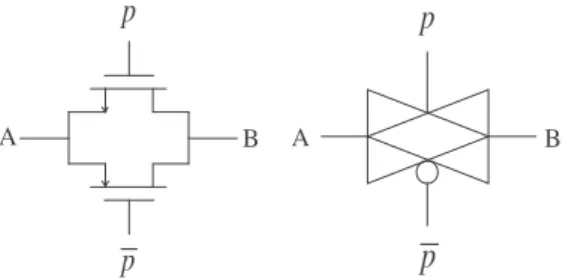

Un'altra tecnica per combattere questi problemi è utilizzare delle pass gate. Questi interruttori, usando due MOS complementari pilotati da segnali opposti, riducono considerevolmente il clock-feedthrough. Le cariche liberate dai due MOS riescono però a compensarsi solo parzialmente dato che non esiste un reale matching tra l’NMOS e il PMOS.

A B A B

p p

p p

Figura 3.4: passgate e suo simbolo.

3.3. Reti di calibrazione

Come spiegato in precedenza le calibrazioni hanno lo scopo di ridurre ulteriormente l’offset, regolare le pendenze della curva che approssima la caratteristica del sensore e spostare le tensioni di rottura. I segnali di uscita dei blocchi a condensatori commutati che realizzano l’interfaccia e il linearizzatore sono tutti proporzionali a rapporti di capacità, ovvero si tratta di segnali del tipo

I out F C V Vi C =

dove con CI si sono indicati i condensatori della maglia di ingresso e con CF i

condensatori di reazione. L’idea è dunque quella di rendere regolabile l’uscita ponendo in parallelo ai condensatori della maglia d’ingresso una rete che equivalga ad un condensatore variabile, regolabile tramite alcuni bit. Prendiamo come esempio il preamplificatore.

IO C IO C F C F C 12 p 12 p 12 p 12 p 3 p + -Vupre C C telescopico Vi p1

Figura 3.4: esempio di calibrazione effettuata sul preamplificatore.

Grazie alla rete di calibrazione, l’amplificazione introdotta dal precedente blocco diventa: 0 I I pre F F C C C A C C + ∆ = = (3.4)

dove CI0 è la parte a valore costante del condensatore della maglia di ingresso e

C è la parte variabile fornita dalla rete di calibrazione.

In alcuni casi, in particolar modo per la correzione dell’offset o per l’implementazione del dummy sensor, è necessario che la rete di calibrazione consenta variazioni anche molto piccole delle capacità. In particolare, nel nostro progetto, è stato fissato un range di variazione di 100 fF e una risoluzione a quattro bit. Tuttavia il processo a nostra disposizione non ci permette di realizzare capacità più piccole di 200 fF, perciò per ottenere la capacità variabile richiesta non è possibile ricorrere a dei condensatori semplicemente posti in parallelo e attivabili singolarmente ma è necessario che la rete di calibrazione introduca dei fattori di divisione in modo da fornire capacità anche dell’ordine dei pF. Nei paragrafi successivi vengono proposte due possibili soluzioni per le reti di calibrazione, partendo da quella con struttura a , più nota in letteratura, per poi arrivare a quella con struttura C_2C da noi utilizzata.

3.1.1 Rete di calibrazione a

Una possibile implementazione per il blocco di calibrazione è quella che utilizza un divisore capacitivo costituito da una rete a come mostrato in Figura 3.5.

0 b C 2 b C 3 b C 2 C 3 C 4 C 1 b C 1 C In Out 0 b 1 b 2 b 3 b 1 N N2

Figura 3.5: rete di calibrazione a a quattro bit.

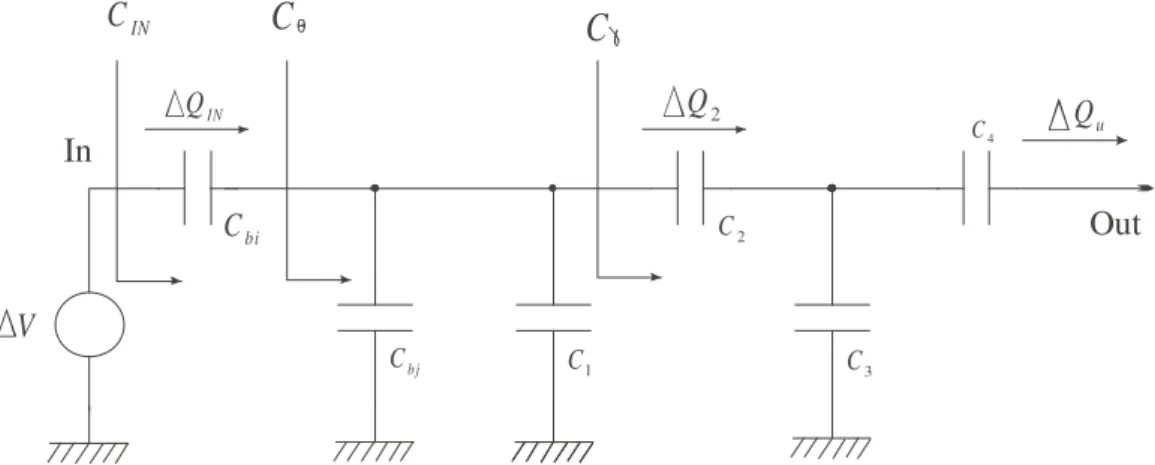

Per valutarne il funzionamento prendiamo in considerazione il circuito di Figura 3.6 dove Cbi rappresenta il generico condensatore che viene collegato alla tensione

di ingresso per bi=1, mentre Cbj rappresenta il condensatore disinserito (bj =0).

bi C C2 3 C 4 C bj C C1 In Out IN C

C

C

u Q 2 Q IN Q VFigura 3.6: schema circuitale per lo studio del funzionamento della rete a .

La rete non rappresenta un vero e proprio condensatore ma si comporterà come tale agli effetti esterni. Data V la tensione applicata in ingresso e Qu la carica presente in uscita, la capacità equivalente è data da

u eq Q C V ∆ = ∆ (3.5)

Riferendoci alla Figura 3.6 si ottengono le seguenti capacità viste:

(

)

2 3 4 2 3 4 C C C C C C C γ + = + +(

)

(

1)

(

2 3 4)

2(

3 4)

2 3 4 1 1 2 3 4 2 3 4 bj bj bj C C C C C C C C C C C C C C C C C C C C C C C θ γ + + + + + + = + + = + + = + + + +(

)

(

)

(

)

(

)

(

)

(

)

1 2 3 4 2 3 4 1 2 3 4 2 3 4 bi bj bi IN bi bi bj C C C C C C C C C C C C C C C C C C C C C C C θ θ + + + + + = = + + + + + + + (3.6) Per calcolare Ceq inizieremo calcolando Qu e procederemo a ritroso per ottenereQu in funzione di V. La variazione di carica in uscita vale

4 2 3 4 u C Q Q C C ∆ = ∆ + (3.7)

dove Q2 è la carica che passa nel condensatore C2 e vale

2 1 IN bj C Q Q C C C γ γ ∆ = ∆ + + (3.8) con ∆QIN =CIN⋅∆ .V

Andando a sostituire l’espressione di Q2 in quella Qu si trova

4 3 4 1 u IN bj C C Q C V C C C C C γ γ ∆ = ∆ + + + (3.9)

Se si svolgono i calcoli si trova

4 3 3 4 1 0 1 1 u bi k k C Q C V C C C C Cγ = ∆ = ⋅ ∆ + + + (3.10)

Andando a generalizzare il risultato si ottiene

(

)

4 3 3 4 1 0 1 1 eq i bi k k C C C C C C C Cγ = = ⋅ ⋅ + + + (3.11)dove con

(

iCbi)

si intende la somma delle sole capacità inserite in ingresso, mentre 3 0 k k C =rappresenta la somma di tutti le capacità selezionabili e pertanto, fissato il numero di bit, è un valore costante.

Se scegliamo le Cbi tali che:

0 0 02 b C =C , 1 1 02 b C =C , 2 2 02 b C =C , 3 3 02 b C =C (3.12) l’espressione di Ceq diventa

(

02)

i eq i i C = b C ⋅α

(3.13)dove è il fattore di divisione ottenuto dividendo una prima volta tramite il partitore capacitivo dato da C3 e C4 e una seconda volta sfruttando le capacità C1e

C2 . L’espressione di è la seguente 4 3 3 4 1 0 1 1 k k C C C C C Cγ

α

= = ⋅ + + + (3.14)Dimensionando opportunamente le capacità C1 , C2 ,C3 e C4 si riescono a

realizzare fattori di divisione molto piccoli. La rete di calibrazione ottenuta è dunque equivalente ad una capacità variabile, il cui valore, selezionabile tramite N bit, varia da un minimo di 0 F ad un massimo di

(

2N −1)

C0⋅α

F , con passo0

C ⋅ . Inoltre è caratterizzata da una capacità vista in ingresso pari a

α

(

)

(

)

(

)

(

)

(

)

(

)

1 2 3 4 2 3 4 3 1 2 3 4 2 3 4 0 bi bj i j IN bk k C C C C C C C C C C C C C C C C C C = + + + + + = + + + + + (3.15)Va notato che, dati i valori delle Cbi riportati nella (3.12), con C0 200 fF, il

termine

(

iCbi)

⋅(

jCbj)

che compare al numeratore può rendere CINparticolarmente elevata per alcune configurazioni di bit, rischiando di caricare eccessivamente in ingresso il blocco che sfrutta la rete di calibrazione. Si può dimostrare che la situazione peggiore si ottiene per la configurazione di bit pari a 1000. Questo difetto della rete a viene affrontato in maniera più approfondita nel paragrafo 3.3.3.

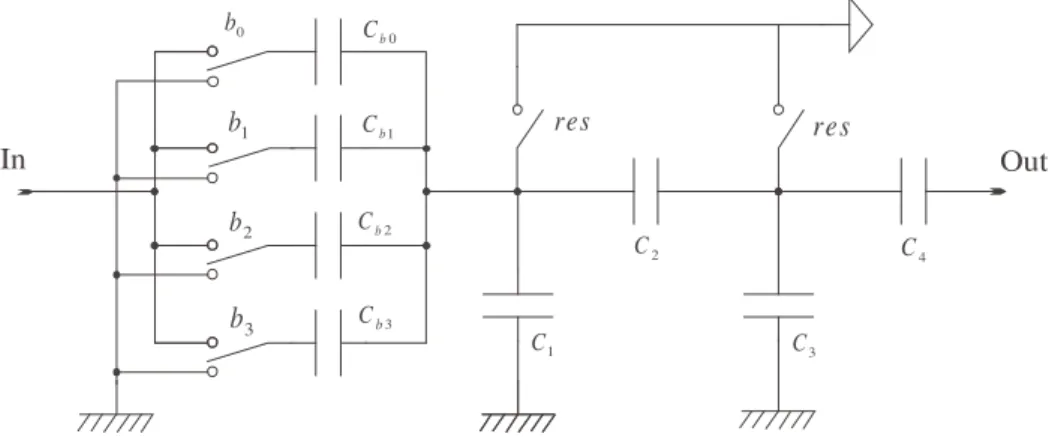

I nodi N1 e N2 sono flottanti perciò sono stati aggiunti degli interruttori sui quei nodi al fine di scaricare i condensatori nella fase di reset della rete. La rete finale è rappresentata di seguito, dove gli interruttori sono stati implementati da passgate di dimensione W = 1.5 m e L = 0.7 m. 0 b C 2 b C 3 b C 2 C 3 C 4 C 1 b C 1 C In Out 0 b 1 b 2 b 3 b res res

Figura 3.7: schema circuitale completo della rete di calibrazione a .

3.1.2 Rete di calibrazione C_2C

Per evitare che l’introduzione delle reti di calibrazione carichi eccessivamente i blocchi in ingresso abbiamo cercato una soluzione che eviti l’uso di capacità elevate e che sia caratterizzata da una capacità vista in ingresso sufficientemente piccola. Un modo per risolvere il problema è dato dalla rete con struttura C_2C sotto rappresentata. 0 b b1 b2 b3 C C C C C C C Vi Vu 2C 2C 2C M 2C C =CMS C =CMD CIN J

Si nota che, fermo il vincolo di C≥200fF , in questo caso vengono impiegate solo capacità molto piccole. Per valutarne il funzionamento facciamo riferimento alla figura 3.8 dove la rete è rappresentata per una risoluzione a 4 bit. Riferendoci al nodo M, in corrispondenza del bit più significativo, si ha che la capacità vista

CMDverso destra e la capacità vista CMSverso sinistra valgono: MD

C =C e CMS =C

Lo stesso risultato si trova per gli altri nodi, per cui la capacità vista dall’ingresso relativo al generico bit j, calcolata con tutti gli altri ingressi collegati a massa, è costituita dalla serie di C e 2C , e vale

2 3

j IN

C = C (3.16)

Per il calcolo di Qu faremo riferimento alla Figura 3.9

1 M

b

-b

MC

C

C

C

Vi

Vu

2C

2C

M2C

Q Q 2 4Q Q 4 Q 2Figura 3.9: schema circuitale per il calcolo della Ceq.

Applichiamo il teorema della sovrapposizione degli effetti e consideriamo inizialmente attivato solo il bit più significativo bM mentre tutti gli altri ingressi

risultano collegati a massa. La carica che scorre nel condensatore C del ramo relativo a bM, è pari a 2

3 i

Q C V

∆ = ∆ e, in corrispondenza del nodo M, si divide esattamente a metà tra il ramo di destra e quello di sinistra; a sua volta la Q/2 del ramo di destra si divide nuovamente a metà prima di arrivare in uscita. Dunque il bit più significativo dà un contributo QM alla carica di uscita pari a

2 1 1

3 4 6

M i i

Q C V C V

I contributi degli altri bit si ricavano applicando lo stesso ragionamento, facendo attenzione a dividere la carica per 2 ad ogni passo che si compie verso il bit meno significativo. Ad esempio i bit M-1 e M-2 danno un contributo alla carica d’uscita pari a ∆QM−1= ∆QM 2 , ∆QM−2 = ∆Q 4 e così via. Sommando i vari contributi si trova la seguente espressione per la carica in uscita:

0 1 2 3 3 2 1 0 1 6 2 2 2 2 u i b b b b Q C V ∆ = ∆ + + + (3.18)

Andando a formalizzare il risultato si trova che la Ceq vale

0 1 1 0 1 1 1 2 2 2 1 6 2 N u N eq N i Q b b b C C V − − − ∆ + + ⋅⋅⋅⋅+ = = ∆ (3.19)

Abbiamo ottenuto una rete che si comporta come una capacità variabile in un range [0, CMAX] con CMAX pari a

1 1 2 1 6 2 N MAX N C = C −− (3.20)

e passo del valore di

1

1 1

6 2N

C C −

∆ = ⋅ (3.21)

Per il calcolo della capacità vista in ingresso CIN consideriamo per semplicità il

caso in cui b2 = = , b3 1 b1= = mostrato in Figura 3.10.b1 0

C C Vi C 2C M C Qi C C C 2C M C Q 2 Q3 Q2 V2 V3 disattivato 2 2 Q22 Q32 +_ +_

Figura 3.10: a sinistra, schema circuitale equivalente per la configurazione b3= b2 =1; a destra, applicazione della sovrapposizione degli effetti.

Nella precedente figura è stato sostituito il resto della rete con le capacità viste. La capacità vista in ingresso sarà

2 3 i IN i i Q Q Q C V V ∆ ∆ + ∆ = = ∆ ∆ (3.22)

Per il calcolo di ∆ si applica il metodo della sovrapposizione degli effetti, perQ3

cui si sdoppia Vi e si fa agire prima V3 e poi V2 (con V3 = V2 = Vi ). Quando agisce V3 e V2 è disattivato si ha

3 3 3 2 3 Q CV ∆ = (3.23)

Viceversa quando agisce V2 e V3 è disattivato si ha 2 2 2 3 2 2 1 4 3 4 Q Q ∆ CV ∆ = − = − ⋅ (3.24) Quindi 3 2 3 3 3 1 2 i Q Q Q CV ∆ = ∆ + ∆ = (3.25)

Ripetendo i calcoli per ∆ in questo caso si trova lo stesso risultato, quindi, perQ2

la configurazione b2 = = , b3 1 CIN = . Dai calcoli effettuati per le altreC

configurazioni di bit si ottiene 5 4

INMAX

C = C, per cui, per C sufficientemente piccolo, la rete di calibrazione C_2C presenta una capacità di ingresso notevolmente ridotta rispetto alla rete precedente. In tabella sono riportati alcuni valori della capacità di ingresso con le rispettive configurazioni.

b3 b2 b1 b0 CIN 1000 2 3 IN C = C 1001 5 4 IN C = C 1110 7 6 IN C = C 1111 5 4 IN C = C

Anche in questo caso è stato necessario aggiungere degli interruttori sui nodi flottanti per poterli scaricare durante la fase di reset . La rete di calibrazione completa è riportata in Figura 3.11

0 b b1 b2 b3 C C C C C C C Vi Vu 2C 2C 2C M 2C

res

Figura 3.11: schema circuitale completo della rete di calibrazione C_2C.

Nella figura precedente i commutatori pilotati dai segnali bi sono stati realizzati con delle passgate, mentre gli interruttori che si occupano di scaricare i condensatori durante la fase di reset sono costituiti da semplici NMOS di dimensioni ridotte. Come viene spiegato in dettaglio nel paragrafo successivo, questa scelta è stata determinata dal fatto che l’utilizzo di passgate introdurrebbe su quei nodi una capacità parassita di giunzione che causerebbe un errore sul segnale di uscita. Sostituendo degli NMOS alle passgate, si dimezza la capacità parassita di giunzione e con questa si dimezza l’errore.

3.1.3 Confronto tra la reti di calibrazione a e C_2C

In questo paragrafo vengono discussi i problemi riscontrati nel linearizzatore sequenziale una volta applicate le reti di calibrazione all’amplificatore a guadagno variabile. Verranno evidenziati i difetti delle reti di calibrazione che causano il mal funzionamento dell’intero circuito e verranno proposte delle soluzioni. Per il dimensionamento delle reti terremo presente che nel nostro progetto è stato fissato un range di variazione per le capacità pari 100fF e una risoluzione a 4 bit.

( ) u V P AGV + trimming U G EN V Vu

Figura 3.12: schema del linearizzatore con AGV dotato di calibrazione utilizzato per un confronto tra le reti di calibrazione.

Prendiamo in considerazione la rete a .

A causa del vincolo sulla capacità minima fisicamente realizzabile pari a 200 fF , per le Cbi si ottengono i seguenti valori:

Cb0 = 200 fF, Cb1 = 400 fF, Cb2 = 800 fF, Cb3 = 1600 fF

per cui si nota che già con soli 4 bit dobbiamo ricorrere a capacità elevate. Con questi valori delle Cbi per ottenere CMAX =

(

2N −1)

C0⋅ =α

100fF, ovvero unpasso ∆ =C C0⋅ =

α

6.7fF , è necessario dimensionare i condensatori in modo che= 0.033. Si ricavano i seguenti valori

C1= 1 pF ; C2= 400 fF ; C3= 500 fF ; C4= 500 fF Data l’espressione della capacità di ingresso:

(

)

(

)

(

)

(

)

(

)

(

)

1 2 3 4 2 3 4 3 1 2 3 4 2 3 4 0 bi bj i j IN bk k C C C C C C C C C C C C C C C C C C = + + + + + = + + + + + (3.26)si deduce che, al variare della configurazione, il termine che compare al numeratore

(

iCbi)

⋅(

jCbj)

può rendere CIN particolarmente elevato comeaccade per la configurazione 1000, dove ad una capacità equivalente di circa 50 fF, corrisponde una capacità di ingresso di circa 1 pF. Perciò nell’amplificatore a guadagno variabile, dove nella maglia di ingresso si hanno quattro coppie di condensatori da calibrare, nel caso peggiore il blocco di calibrazione comporta un incremento della capacità di ingresso di 4pF. In questo caso le simulazioni evidenziano come nel generatore di riferimenti, eccessivamente caricato dalla capacità di ingresso dell’AGV con calibrazione, il segnale di uscita risulti

particolarmente rallentato. Lo stesso accade per il segnale di uscita dell’intero linearizzatore e in condizioni estreme di funzionamento, con la tensione di alimentazione di 2.1 V e la temperatura di 150°C, non raggiunge il valore di regime ed occorre operare a frequenze di clock più basse.

Per risolvere il problema dovuto alla capacità di ingresso elevata è stata introdotta la rete C_2C, caratterizzata da una capacità di ingresso massima pari a 5

4C. Dall’espressione della massima capacità equivalente realizzata dalla rete C_2C

1 1 2 1 6 2 N MAX N C = C −− (3.27)

con CMAX e N stabiliti, si ricava C = 350 fF, che implica una capacità di ingresso

massima pari a 430 fF. Le simulazioni effettuate precedentemente per il linearizzatore con calibrazione , sono state ripetute utilizzando al posto della rete a la rete C_2C in una versione iniziale in cui tutti gli interruttori sono stati realizzati con delle passgate di dimensione pari a W = 1.5 m e L = 0.7 m. In questo caso, grazie alla capacità di ingresso ridotta, i segnali di uscita dei vari blocchi sono risultati andare correttamente a regime per ogni configurazione di bit. Tuttavia si osserva che la tensione di uscita del circuito simulato differisce dal risultato teorico di alcune centinaia di V e l’errore aumenta all’aumentare del dei bit settati.

Per identificare le cause di questi nuovi disturbi si è studiato il comportamento della rete di calibrazione nel semplice circuito a condensatori commutati riportato in figura 3.13 il cui principio di funzionamento è simile a quello dei blocchi del linearizzatore ma per semplicità si sviluppa su due fasi invece che su tre. La tensione di uscita nella fase p2 vale:

in u F C V Vdd C = (3.28) con Cin =C0+ ∆C

F C F C 0 C 0 C Vdd + _Vu 3 p 3 p 12 p 12 p 3 p 3 p 3 p 3 p 12 p 12 p Rete di calibrazione 3 b b2 b1 b rif res0 A B Rete di calibrazione 3 b b2 b1 b rif res0 A B 3 C b 2 C b 1 C b 0 C b 3 pC M V

Figura 3.13 : schema circuitale utilizzato per lo studio dei difetti della rete C_2C. Da una prima simulazione effettuata utilizzando nella rete C_2C solo passgate si ottiene che l’errore commesso sulla tensione di uscita Vu rispetto al valore teorico

è di 380 V per la configurazione di bit 1000 e peggiora all’aumentare dei bit settati. Dato il valore teorico della tensione di uscita Vu ideal_ =180.148mV , un errore di quella entità corrisponde a commettere un errore relativo pari a

_ _ _ 0.2% u ideal u simul u ideal V V V − (3.29)

Questo errore, sebbene si possa recuperare variando la configurazione dei bit, risulta dannoso in quanto è sensibile a variazioni di temperatura e introduce delle non linearità che possono compromettere il corretto funzionamento della rete. Riducendo le passgate alla dimensione minima, pari a W=0.5 m e L=0.7 m, l’errore si riduce ma non a sufficienza. Tali disturbi possono essere causati dall’iniezione di carica, che comunque è solo ridotta dalle passgate e non annullata, oppure dalla presenza delle capacità parassite di giunzione.

Come abbiamo già discusso l’iniezione di carica è dovuta alla carica accumulata nel canale che durante la fase di spegnimento dei MOS viene iniettata nei condensatori di tenuta. Questa carica è direttamente proporzionale all’area WL. Le capacità di giunzione invece sono costituite da due termini, C e JA C ,JP

corrispondenti rispettivamente al “fondo” e alle “pareti”delle diffusioni di drain e di source. Per la capacità tra bulk e drain vale

BD AD PD

C =C +C (3.30)

dove C e AD C sono rispettivamente proporzionali all’area AD e al perimetroPD

PD del pozzetto di drain. Se il pozzetto ha dimensioni LD× , con W pari alleW

larghezza di canale, allora

D

AD L W= ⋅ e PD=2

(

LD+W)

(3.31)quindi la capacità di giunzione è proporzionale alla larghezza di canale W. Le stesse considerazioni valgono per il pozzetto di source.

Per individuare quale dei due effetti fosse predominante è stata ripetuta la stessa simulazione, variando in modo opportuno i parametri delle passgate pilotate dal segnale di reset, e sono stati confrontati i risultati con una prova base. Le tre prove sono le seguenti:

• Prova base: per gli interruttori si usano delle passgate di dimensioni pari

a:

W = 1.5 m L = 0.7 m

• Prova per valutare l’effetto dell’iniezione di carica: dato che questa

dipende dall’area W L⋅ , si va ad aumentare L e si lascia fissa W, in modo

da lasciare invariata la capacità di giunzione rispetto alla prova base e aumentare l’effetto dell’iniezione di carica. Per le passgate si sceglie:

W = 1.5 m L = 1.4 m

• Prova per valutare l’effetto delle capacità parassite: si riduce W

lasciando inalterata l’area W L⋅ . Se il disturbo prevalente è quello dovuto

alla capacità di giunzione si otterrà un miglioramento dell’errore. L’iniezione di carica è la stessa della prova base. Per le passgate si sceglie:

W = 0.7 m L = 1.5 m

Prendendo la prova base come riferimento, si ottiene che la simulazione relativa all’iniezione di carica non fornisce variazioni rilevanti mentre diminuendo la larghezza di canale l’errore si riduce di oltre il 20 %. Le capacità parassite di giunzione creano perciò un disturbo che può compromettere il funzionamento del

circuito. Per chiarire l’effetto delle capacità di giunzione sulla rete C_2C, consideriamo la figura seguente in cui è rappresentato uno dei nodi flottanti che è necessario resattare. M C 2C 2C

Q

iV

C G P C CC G N M C G P C + CC G N _ + _ C 2C 2CQ

iV

res resFigura 3.14 : A sinistra, passgate e capacità parassite di giunzione da questa introdotte; a destra, effetto delle capacità parassite di giunzione.

Siano CGN e CGP rispettivamente le capacità di giunzione del NMOS e PMOS della passgate pilotata dal segnale di reset. Durante la fase di reset il nodo M viene collegato a VCM e le capacità parassite vengono precaricate ad una tensione pari alla tensione di modo comune, per cui

r CGP CM CM V Vdd V V ∆ = − = (3.32) r CGN CM V V ∆ = (3.33)

Nella fase successiva, la fase attiva, sul nodo M si ha una variazione V, quindi

(

)

a CGP CM V Vdd V V ∆ = − + ∆ (3.34) a CGN CM V V V ∆ = + ∆ (3.35)e la variazione di carica indotta nelle capacità parassite è

(

a r)

CGP GP CGP CGP GP Q C V V C V ∆ = ∆ − ∆ = − ∆ (3.36)(

a r)

CGN GN CGN CGN GN Q C V V C V ∆ = ∆ − ∆ = ∆ (3.37)Il flusso di carica è uscente dal nodo per entrambe le capacità, per cui gli effetti si sommano invece che compensarsi. La carica Q che scorre nel condensatore C non si divide esattamente a metà come ipotizzato con gli interruttori ideali, ma una parte di questa finisce nelle capacità di giunzione.

Per ridurre il loro effetto si è pensato di sostituire le passgate con dei semplici transistori NMOS di piccole dimensione W=0.5 m e L=0.7 m; questi peggiorano l’effetto dell’iniezione di carica, che però abbiamo visto non essere molto rilevante, ma ovviamente presentano una capacità parassita pari alla metà di quella delle passgate che utilizzano mos della medesima dimensione. Andando a simulare il circuito con la rete C_2C modificata si ottiene che la tensione di uscita differisce dal valore teorico di soli 80 V, un errore pari esattamente alla metà di quello ottenuto con le passgate di dimensione minima. I risultati ottenuti per la configurazione di bit 1000 con interruttori differenti sono riassunti in tabella.

Tipo di interruttore Scopo di utilizzo Vuideale−Vusimul

Passgate W=1.5 m, L=0.7 m Riferimento per le altre prove 369 V Passgate W=1.5 m, L=1.4 m Verifica l’incidenza dell’iniezione di carica 368 V Passgate W=0.7 m, L=1.5 m

Verifica l’incidenza del

disturbo dovuto alle cap.di giunzione 195 V

Passgate W=0.5 m, L=0.7 m

Riducendo le dimensioni della

passgate si riducono i disturbi 160 V NMOS

W=0.5 m, L=0.7 m

Riduce il disturbo dovuto

alla capacità di giunzione 80 V

In Figura 3.15 è riportato l’andamento del segnale di uscita del generatore di tensioni di riferimento nel caso in cui l’amplificatore a guadagno variabile sfrutti il blocco di calibrazione con reti a e nel caso i cui sfrutti la rete di calibrazione C_2C. Si nota chiaramente come utilizzando la rete C_2C l’uscita del generatore di tensioni di riferimento vada più rapidamente a regime.

Figura 3.15 :confronto tra gli andamenti del segnale di uscita del generatore di tensione di riferimenti nel caso in cui l’AGV sfrutti la rete di calibrazione a o quella C_2C.

3.4. Implementazione del sensore fittizio

Lo scopo di questo lavoro di tesi è quello di terminare il progetto del linearizzatore sequenziale e dell’interfaccia di lettura di un sensore capacitivo, per poter successivamente sottoporre il circuito ad una fase di testing che ne verifichi il funzionamento reale. Per questo motivo è stato necessario realizzare un oggetto che simulasse il comportamento del sensore di pressione della STMicroelettronics. Per quanto detto nel secondo capitolo, il sensore si può considerare costituito da una capacità Cx=C0 + C e da una Cd= C0 aventi un terminale a comune, dove C0 è il valore della capacità del sensore a riposo mentre C è la variazione indotta dalla pressione e corrisponde alla quantità da misurare. Per un sensore con fondoscala di 4 atm, Cx può essere realizzato con una capacità variabile C, il cui range vale [0, 25 fF], in parallelo ad una capacità fissa C0 del valore di192 fF; nel nostro progetto, dato che il segnale di uscita del convertitore capacità-tensione dipende soltanto da C e non da C0 , per quest’ultimo è stato

fissato un valore maggiore di 192 fF, evitando, in questo caso, il problema dovuto alla minima capacità fisicamente realizzabile.

La capacità variabile è stata implementata usando una rete di calibrazione pilotata da 8 bit in modo che, per un range di [0, 25 fF], il passo risulti pari a

min 8 25 0.97 2 1 2 1 MAX N C fF C aF ∆ = = = − − (3.38)

Permettendo che la caratteristica del sensore venga percorsa con buona accuratezza.

Anche in questo caso, per la realizzazione di C non è stato possibile utilizzare la rete di calibrazione a in quanto con 8 bit sarebbero stati necessari dei condensatori Cbi grandi fino a 25,6 pF. Tuttavia anche la rete di calibrazione C_2C, così come è stata presentata nei paragrafi precedenti, è inutilizzabile in quanto, fissato il numero di bit pari a 8, si ha

8 8 1 1 2 1 66.4 6 2 MAX C = C −− ≥ fF (3.39) per C 200 fF.

Per risolvere il problema è stato modificato il circuito in modo da introdurre un’ulteriore fattore di divisione, così da ottenere

8 8 1 1 2 1 1 25 6 2 MAX C C fF D − − = ⋅ = (3.40)

Prendiamo in considerazione la seguente figura dove è rappresentata la parte finale del circuito, riferendoci in particolar modo al ramo relativo al bit più significativo e al partitore capacitivo in uscita.

1 M b -

b

M Vi Vu M 2 2 BC

AC

C CC

C

2C2C

2C

M Q M Q M Q QM 2DPer quanto già spiegato nel precedente paragrafo, il funzionamento del circuito si basa sul fatto che la capacità vista dal nodo M verso l’uscita sia pari a C, ovvero pari al valore della capacità vista dal nodo verso sinistra. Per cui, scegliendo i valori delle capacità CA, CB e CC in modo da verificare quella condizione, si

ottiene che la carica che scorre in C vale 2 3

M i

Q C V

∆ = ∆ (3.41)

mentre in CA scorre QM/2. A questo punto, dimensionando i condensatori come

mostrato per la rete di calibrazione, ovvero 2

A

C = C; CB = ;C CC =C

la carica viene divisa ulteriormente per due, fornendo in uscita

2 1 1

3 2 2

u i

Q C V

∆ = ∆ ⋅ ⋅ (3.42)

Se invece si fissano i valori di CB e CC in modo da ottenere una partizione diversa

da 1/2 e si sceglie CA tale da mantenere la condizione sulla capacità vista dal nodo

M, allora la carica in uscita risulta

2 1 1 3 2 u i Q C V D ∆ = ∆ ⋅ ⋅ (3.43)

dove D è il fattore di divisione introdotto dal partitore capacitivo in uscita e vale

1 B

B C

C

D C= +C (3.44)

L’espressione della capacità equivalente diventa

0 1 1 0 1 1 1 2 2 2 1 1 3 2 N N eq N b b b C C D − − − + + ⋅⋅⋅+ = (3.45)

Nel nostro caso, fissate C, N e CMAX, si ottiene facilmente D

1 1 2 1 3 2 N N MAX C D C − − = ⋅ (3.46)

Per D vale anche l’espressione (3.44), che può essere scritta anche come

1 1 1 B B C C C D C= +C =C+

α

C = +α

(3.47)quindi fissato CB=C si ricava CC =

(

D−1)

C. CA viene dimensionato in modo dagarantire che la capacità vista dal nodo M verso l’uscita sia pari a C, per cui

(

)

A B C VM A B C C C C C C C C C ⋅ + = = + + (3.48) Posta quindi CA = C, si ha(

)

VM C DC C C D Cβ

β

⋅ = = + (3.49) Da cui si ricava 1 D Dβ

= − (3.50)Per implementare il dummy sensor si è scelto di non prendere C della dimensione minima in quanto, come spiegato nel capitolo successivo, i dispositivi di dimensione minima creano maggiori problemi di matching. Fissati dunque

350

C= fF,CMAX =25fF e N=8, per i condensatori CA, CB e CC si ottengono i seguenti valori:

1.12 391.65

A

C = ⋅ =C fF; CB = =C 350fF ; CC =8.29⋅ =C 2.9015pF

Di seguito viene mostrato lo schema circuitale completo della rete di calibrazione adattata per funzionare da sensore fittizio.

Figura 3.17: : schema circuitale completo utilizzato per implementare il dummy sensor. I due condensatori fissi che rappresentano la capacità riposo, introdurranno un offset dovuto ai problemi di matching che non viene cancellato in nessun modo dallo stadio di ingresso. Per eliminare questo difetto e per garantire la simmetria del circuito, la rete di Figura 3.17 viene posta in parallelo a entrambi i condensatori fissi e i bit di pilotaggio cxi e cdi vengono preconfigurati a

10000000. Successivamente, tramite le reti di calibrazione, si provvede ad annullare l’offset dovuto al mismatching dei condensatori della sezione di ingresso, compresi quelli del circuito dell’ICMFB; a questo punto il comportamento del sensore verrà simulato andando ad incrementare la configurazione dei bit cxi e decrementando i bit cdi.

Figura 3.18: realizzazione del dummy sensor.

Nel caso in cui si volessero eseguire dei test del circuito utilizzando il sensore reale della STmicroelettronics, è stato previsto un sistema di switch che permette di escludere i condensatori di valore costante, che costituiscono la Cd e la C0, e consente di sfruttare le reti che implementano il dummy sensor come reti di calibrazione per la correzione dell’offset dell’amplificatore telescopico dovuto al mismatching dei condensatori di feedback e di quelli del ICMFB, e all’iniezione di carica.

3.5. Blocchi funzionali con calibrazione

Per comodità e maggior chiarezza le reti di calibrazione di ciascun blocco funzionale, sono state unite in blocchi di calibrazione. Nella seguente figura è mostrato il blocco di calibrazione del generatore di tensioni di riferimento dove Aip e Bip sono i terminali di ingresso e uscita della rete di calibrazione che va in parallelo al condensatore fisso Ci della maglia di ingresso. I pedici p e n si riferiscono ai terminali non invertenti e invertenti dell’amplificatore; chiaramente, data la simmetria del circuito, le reti di calibrazione relative agli stessi condensatori della parte invertente e non invertente devono essere pilotate dagli stessi bit. Fig ura 3.19 :a sini stra , bloc co di cali bra zion e per il generatore di tensioni di riferimento; a destra, simbolo del blocco di calibrazione .I valori dei condensatori dei blocchi ai quali sono state applicate le reti di calibrazione sono stati calcolati nuovamente in modo che la configurazione di bit 1000, che corrisponde a posizionarsi al centro del range di calibrazione [0, 109.37

fF], fornisse gli stessi segnali di uscita del circuito privo di trimming. Perciò fissando per ogni rete di calibrazione la configurazione 1000, si ottiene l’implementazione della spezzata che approssima la caratteristica del sensore. In questo i condensatori delle maglie di ingresso valgono 1000

1000

i iFIX

C =C + ∆C , dove 1000 58.33

C fF

∆ = è la parte variabile fornita dalla rete C_2C per quella configurazione di bit; e CiFIX è la loro parte fissa calcolata in modo da ottenere i

risultati originari, ricavati per il circuito privo di calibrazione. Perciò, se con il pedice “O” si indicano i valori dei condensatori della rete originaria, i CiFIX

vengono dimensionati in modo che:

1000

iO i

FO F

C C

C = C (3.51)

In tabella sono riportati i nuovi valori dei condensatori fissi, CiFIX

PREAMPLIFICATORE GEN.DI RIFERIMENTI AGV

1 1941.667 C = fF C1=200fF C1=2.117pF 500 F C = fF C2 =216.66fF C2 =237.35fF 3 235.2 C = fF C3 =219fF 4.73222 F C = pF C4 =200fF 1.56245 F C = pF

Nelle figure che seguono sono riportati la rete di linearizzazione completa di tutti i blocchi di calibrazione e la rete globale che utilizza il dummy-sensor al posto del sensore vero della STMicroelettronics.

– B lo cc hi fu nz io na li 93

Figura 3.21: stadio di ingresso con reti di calibrazione e dummy sensor.

3.6. Interfaccia seriale per il pilotaggio delle

reti di calibrazione

Per consentire all’utente di configurare i 4 bit di ciascuna rete di calibrazione, è stata implementata una semplice interfaccia seriale.

W D3 D2 D1 D0 A3 A2 A1 A0

}

}

Al linearizzatore Al convertitore C-V e al dummy-sensor INTERFACCIA SERIALEFigura 3.22 : simbolo dell’interfaccia seriale per il pilotaggio delle reti di calibrazione. L’interfaccia è dotata in ingresso di un segnale per l’abilitazione w, quattro variabili di indirizzo, A3_ A0 ,e altre quattro per i dati, D3_ D0 . Delle 64 uscite a disposizione ne verranno utilizzate 28 per le reti di calibrazione del linearizzatore, 4 per quelle del preamplificatore nel convertitore capacità-tensione, 16 per il dummy sensor e una per l’inclusione o meno del sensore reale.

L’interfaccia è costituita da una memoria 4×16, implementata con 16 registri da 4 bit ciascuno. I registri condividono lo stesso bus dati D3_ D0 e ognuno serve a memorizzare la configurazione di bit di una delle reti di calibrazione. Vengono

indirizzati tramite un decoder 4_to_16 con abilitazione le cui variabili di ingresso coincidono con A3_ A0 e le uscite sono collegate ciascuna al clock di un registro. Il funzionamento è semplice. Inizialmente si impongono i valori di D3_ D0 e A3_ A0 desiderati mantenendo w basso per il tempo necessario affinché i segnali vadano a regime; per cui siamo nella situazione in cui tutti i registri hanno il medesimo ingresso e il decoder ha tutte le uscite nulle. Ogni uscita del decoder corrisponde al segnale di campionamento di uno dei registri, costituito ciascuno da quattro flip-flop con il clock in comune. Quindi , per w=0, i registri sono tutti insensibili agli ingressi D3_ D0 . Quando w va alto, il decoder setta solo l’uscita corrispondente all’indirizzo fissato e il registro indirizzato campiona la variabile D3_ D0 in ingresso. w viene subito riportato basso per evitare che eventuali fluttuazioni dei segnali di ingresso provochino variazioni non volute delle uscite. Ripetendo la procedura si riescono a variare le configurazioni di bit delle varie reti di calibrazione, una dopo l’altra.

Per implementare il decoder 4_to_16 con abilitazione, assente nelle librerie, è stato utilizzata la nota struttura di Figura 3. . Si tratta semplicemente di una barriera di porte AND a cinque ingressi, collegate in modo che ciascuna riconosce una sola configurazione di bit in ingresso; inoltre hanno tutte il terminale e di ingresso in comune utilizzato come abilitazione per il decoder.

e 3 x x2 x1 x0 0 z 1 z 2 z 3 z 4 z 5 z 6 z 7 z 8 z 9 z 10 z 11 z 12 z 13 z 14 z 15 z 3 x x2 x1x0 e 0 z 1 z 2 z 3 z 4 z 5 z 6 z 7 z 8 z 9 z 10 z 11 z 12 z 13 z 14 z 15 z Decoder

Figura 3.23: : schema circuitale del decoder 4_to_16 con abilitazione.

Figura 3.24: schema circuitale completo dell’interfaccia seriale per il pilotaggio delle reti di calibrazione.

3.7. Comparatore

Come già spiegato nel secondo capitolo, il comparatore viene utilizzato nel linearizzatore per discriminare il livello del segnale di ingresso. È costituito da un preamplificatore e un decisore con isteresi in cascata. Il decisore con isteresi fa in modo che l’uscita scatti quando ormai il preamplificatore si è sbilanciato nella direzione corretta. Il funzionamento del comparatore da noi scelto si basa sulla seguente cella: 1

M

M

2M

3 M4 1V

V

2 2I

1I

Figura 3.25 : cella base del comparatore con isteresi. Siano

1 4 A

β β

= =β

β

2 =β

3 =β

B (3.52)1 2 0

I + =I I (3.53)

Per valutarne il funzionamento partiamo dalla condizione: I1= e I0 I2 = . Si ha0 che V2 = e quindi i transistori M0 4 e M2 sono spenti; la I1 scorre tutta in M1 perciò ID1 = = , mentre MI1 I0 3 lavora in zona triodo. M1 si trova in saturazione,

quindi vale 0 1 1 2 2 Tn Tn A A I I V V V

β

β

= + = + (3.54)Supponiamo di dimensionare A in modo tale che

0 1 2 2 MAX Tn Tn A I V V V

β

= + ≤ (3.55)Se a questo punto andiamo ad aumentare progressivamente I2 a scapito di I1 , si

osserva che V2 comincia a crescere mentre V1 diminuisce. Quando si raggiunge la

condizione V2 =VTn, M2 si accende e si innesca una reazione positiva: ID2 porta via

corrente da M1 , V1 si abbassa, ID3 diminuisce e, di conseguenza, aumenta V2 e

così via fino a che M4 si porta in saturazione. Dunque la cella si porta velocemente nella situazione opposta con V1= e V0 2 alto. Questo accade solo se è verificato

1

A

β

> .Calcoliamo il valore del rapporto I2 / I1 per il quale inizia la commutazione. Per

2 Tn

V =V anche VD3 =VTn mentre per la tensione di gate si ha VG3 = <V1 2VTn,

quindi

3 3 3

G Tn Tn D G Tn

V −V ≤V V ≥V −V (3.56)

Dall’equazione precedente si deduce che quando inizia la commutazione M3 è in saturazione. Inoltre per V2 =VTn si ha ID2 =ID4 = , allora 0 I1 =ID1 e I2 =ID3. Dato che M1 e M3 sono in saturazione con la stessa VGS vale

3 3 2 1 1 1 D B D A I I I I

β

β

β

β

= = (3.57)questo punto possiamo distinguere due casi: CASO 1:

β

B >β

A V1, V2 V1 V2 Vtn I2 I0 I /20Figura 3. 26: andamento delle tensioni all’aumentare di I2

Facendo aumentare I2 , V2 e V1 si scambiano. Dai calcoli appena fatti, si ha che

2 1 1 B A I I

β

β

= > (3.58)allora il valore della I2 per cui si ha la commutazione è 2 0

2

I I > . Andiamo ora a diminuire I2.

V1, V2 Vtn I2 I0 I /20 V1 V2

Figura 3.27: andamento delle tensioni per I2 che diminuisce.

V2 e V1 si scambiano nuovamente. Questa volta però, se calcoliamo il valore della

corrente I2 per la quale ha inizio la commutazione, troviamo

1 2 1 B A I I

β

β

= > (3.59)perciò, nella fase di discesa, V2 e V1 si scambiano per 2 0

2 I I < . Allora per B 1 A

β

β

> otteniamo isteresi. CASO 2:β

B ≤β

AAndando a ripetere i ragionamenti del caso precedente, questa volta otteniamo un andamento senza isteresi.

V1, V2 Vtn I2 I0 I /20 V1 V2

Si può dimostrare che B 1

A

β

β

> significaβ

A > , che implica una reazione1positiva con instabilità.

Sfruttando la cella appena descritta è possibile realizzare un comparatore con isteresi: OTA modificato.

0 I 0 I 1 V V2 out V 1 M M2 3 M M4 M5 M6 11 M 21 M M22 12 M 13 M M23

Figura 3. 29: schema circuitale di un comparatore con isteresi.

Dallo studio della cella base, abbiamo visto che la soglia di commutazione alta si trova per 2 1 B A I I

β

β

= (3.60)Andando a sostituire la relazione precedente in I1+ = si trovaI2 I0

1 B 1 0 A I

β

I Iβ

+ = (3.61) da cui 0 1 1 B A I Iβ

β

= + ; 0 2 1 B A B A I Iβ

β

β

β

= + (3.62)2 1 0 1 1 B A m d B A g v I I I

β

β

β

β

− = − = + (3.63)da cui si ricava la seguente espressione per la soglia più alta:

0 1 1 B A dH B m A I V g

β

β

β

β

− = ⋅ + (3.64)Si nota inoltre che

0 2 D

GS T

m m

I I V V

g = g = − (3.65)

che sostituita nell’espressione di V forniscedH

(

)

1 1 B A dH GS T B A V V Vβ

β

β

β

− = − + (3.65)Per la simmetria del circuito, la soglia più bassa sarà: VdL = −VdH.

L’isteresi totale ha un’ampiezza di

(

)

1 2 1 B A H dH dL GS T B A V V V V Vβ

β

β

β

− = − = − + (3.66)Il comparatore appena descritto è quello che è stato impiegato nel linearizzatore, andando perciò ha sostituire il comparatore precedentemente utilizzato e rappresentato nella figura seguente .

0 I V1 M1 M2 3 M M4 M5 M6 11 M 21 M 13 M M23 12 M 22 M 51 M 52 M M53 54 M 55 M 56 M 57 M 58 M Vu 2 V

Figura 3.30: comparatore con isteresi con buffer d’uscita.

Il comparatore di figura utilizza come blocco decisore la stessa cella con isteresi. In questo caso, però, le correnti dello stadio di preamplificazione differenziale vengono specchiate nella cella e non fatte entrare direttamente in questa come accade nel comparatore precedente descritto. Il circuito d’uscita, usato da buffer, è un amplificatore differenziale che si autopolarizza.

La prima soluzione è stata preferita a questa in quanto ha una struttura più semplice e un consumo più basso. Nella seconda, infatti, si hanno dei rami in più, dovuti alla presenza dello specchio che collega preamplificatore e decisore, in cui scorre una corrente pari a quella di polarizzazione. Dato che il basso consumo è uno dei principali requisiti per il nostro progetto, il secondo comparatore è stato scartato. Bisogna però notare che collegare direttamente la cella di decisione alla coppia differenziale di ingresso può essere rischioso a causa dell’effetto del

kick-back noise. Questo effetto è dovuto alle capacità parassite che creano un

accoppiamento capacitivo tra il decisore e gli ingressi, per cui le rapide variazioni di tensione che si hanno durante le commutazioni, rischiano di far scattare nuovamente il comparatore o nel caso peggiore possono farlo iniziare ad oscillare. Tuttavia nel nostro progetto le due soglie non devono essere estremamente vicine e il segnale di uscita del comparatore non viene campionato immediatamente , quindi questo rischio non si presenta.

Per il nostro comparatore è stato perciò scelto il circuito di Figura 3.29, il quale è stato dimensionato imponendo nell’equazione (3.66)

30

H