Capitolo 4

Controlli reazionati per amplificatori audio

Nel capitolo precedente abbiamo visto come lo stadio di potenza possa introdurre numerosi errori sul segnale PWM, provocando così una distorsione dell’informazione trasportata (il segnale audio). Per ovviare ai limiti di linearità dello stadio di amplificazione e quindi migliorare la qualità audio, si è soliti introdurre un anello di feedback.

Delle architetture da noi prese in esame ce ne sono due reazionate e due a catena diretta; le reazioni utilizzate sono una digitale e l’altra analogica e sono presenti entrambe in amplificatori che utilizzano una PWM a due livelli.

4.1 Reazione digitale

Abbiamo già visto nel Capitolo 3 la necessità di introdurre dei tempi morti (“dead time” o “blanking delay”) nei segnali PWM che pilotano i transistori di potenza., così da evitare il cortocircuito dell’alimentazione durante le commutazioni, che porterebbe ad una forte diminuzione dell’efficienza dell’amplificatore.

La reazione digitale da noi utilizzata è basata sulla generazione di un Dead Time di durata variabile [9], dipendente dal segnale di uscita. Vediamo quindi come funziona un generatore di Dead Time non reazionato in modo poi da capire meglio come vanno le cose in presenza di una reazione.

4.1.1 Generatore di Dead Time

Prendiamo in considerazione uno dei due inverter del nostro stadio di potenza, costituito da 2 MOSFET complementari collegati in serie tra loro e fatti andare in conduzione in maniera alternata, in accordo all’andamento del segnale PWM generato dal modulatore.

Figura 4.1: Inverter a MOSFET dello stadio di potenza

In particolare: quando il pMOS è ON, l’ nMOS è OFF e l’uscita è a livello alto, in quanto cortocircuitata con l’alimentazione; viceversa, quando il pMOS è OFF , l’nMOS è ON e l’uscita è a livello basso perché cortocircuitata a massa. Sembrerebbe che per un corretto pilotaggio della struttura ad “Half Bridge” di Figura 4.1 basti utilizzare B1 e B2 uguali, essendo i MOS complementari tra loro, ma non è così. Supponiamo infatti di voler commutare l’uscita da alta a bassa: occorre spegnere il MOS di tipo p, che era acceso, e accendere l’altro, che era spento. Se i due MOSFET fossero pilotati utilizzando lo stesso segnale, durante il passaggio (non istantaneo) dei transistori da uno stato all’altro si potrebbe verificare una situazione in cui entrambi i MOSFET sono in conduzione: basterebbe infatti che l’accensione del MOS di tipo n fosse più rapida dello spegnimento del MOS di tipo p. Ciò provocherebbe un cortocircuito dell’alimentazione, che si tradurrebbe non solo in un forte dispendio energetico, ma anche nella possibile fusione delle giunzioni a causa dell’elevata corrente che attraverserebbe i transistori.

Tutto questo a causa del fatto che la commutazione dei MOSFET non è istantanea, ma necessita di decine di nanosecondi.

Bisogna quindi fare in modo che tra lo spegnimento del MOS superiore e l’accensione di quello inferiore (e viceversa) ci siano dei “tempi morti” in cui entrambi i transistori sono spenti; questi intervalli vengono realizzati generando opportunamente i segnali di pilotaggio B1 e B2, che non possono dunque essere uguali tra loro.

Figura 4.2: Comandi di pilotaggio di M1 e M2 che garantiscono dei tempi morti

Grazie ai Dead Time si assicura così un funzionamento definito “Break-Before-Make”(BBM), in cui prima di far andare ON un transistore si fanno andare OFF entrambi; se gli intervalli introdotti sono sufficientemente elevati, ciò impedisce che si verifichi un cortocircuito dell’alimentazione durante le commutazioni.

Esistono diverse tecniche per ricavare i segnali B1 e B2 a partire dal segnale PWM generato dal modulatore. Quella utilizzata da noi è mostrata in Figura 4.3, ove con Td si indica il Dead Time:

Figura 4.3: Generazione Dead Time

Assegnando un ‘1’ logico al livello alto di tensione ed uno ‘0’ logico a quello basso, si verifica facilmente che per generare B1 e B2 basta implementare le seguenti relazioni:

2 1 2 1 1 S S S S B = ⋅ = + (4.1) B2=S1⋅S2 (4.2)

dove S1 e S2 sono i segnali ottenuti traslando rispettivamente di Td e di 2⋅Td il segnale PWM invertito (ossia il complementare).

Una volta generati B1 e B2, per pilotare correttamente lo stadio di uscita occorre tener conto della modulazione che viene utilizzata: ipotizzando un Full Bridge con MOSFET complementari, nel caso della PWM a due livelli è sufficiente pilotare M1, M2, M3 e M4 rispettivamente con 1B , 2B , 2B , 1B ; nel caso della PWM tri-state invece le cose sono più complicate e la tecnica utilizzata per comandare i transistori è riassunta nella Tabella seguente, in coerenza con quanto già spiegato nel Cap.3:

Vin>0 Vin=0 Vin<0 G1(p) B1 (y1) HIGH (M1 OFF) HIGH (M1 OFF)

G2(n) B2 (y1) HIGH (M2 ON) HIGH (M2 ON)

G3(p) HIGH (M3 OFF) HIGH (M3 OFF) B1 (y2)

G4(n) HIGH (M4 ON) HIGH (M4 ON) B2 (y2)

Tabella 4.1: Comandi per i MOSFET dello stadio di potenza

Tra parentesi tonde in minuscolo abbiamo indicato quale segnale tra y1 e y2 deve essere mandato in ingresso al generatore di Dead Time; tra parentesi tonde in maiuscolo abbiamo indicato invece quale deve essere lo stato del transistore i-simo, pilotato dal segnale proveniente dall’ingresso Gi.

In Figura 4.4 riportiamo infine gli schemi dei modelli Simulink utilizzati in fase di simulazione per comandare lo stadio di potenza degli amplificatori a catena diretta (AD e AD3).

Figura 4.4: Circuiti di comando per lo stadio di potenza utilizzati nel modello Simulink, relativi (a) all’architettura non reazionata che utilizza una PWM a due livelli (AD) e (b) a quella che utilizza una PWM tri-state (AD3)

4.1.2 Dead Time Compensator (DTC)

Andiamo ora a veder come vengono generati i Dead Time nell’amplificatore che utilizza il controllo reazionato digitale (AD2).

Figura 4.5: Impulsi di comando e corrispondenti impulsi in uscita

Prendiamo in considerazione la Figura 4.5, dove gli andamenti tratteggiati sono relativi agli impulsi privi di DT e quelli continui sono quelli desiderati; in pratica è come se il

fronte di discesa del singolo impulso negativo applicato su B1 fosse ritardato di un tempo Td e lo stesso dicasi per il fronte di salita dell’impulso applicato su B2.

Purtroppo l’inserimento dei tempi morti provoca, com’è facilmente comprensibile osservando in Figura 4.5 il segnale PWM amplificato Vout (linee continue), distorsione del segnale di uscita, dato che la durata degli impulsi del segnale generato dal modulatore viene modificata. Dal momento che l’utilizzo dei DT avviene per ogni commutazione, il loro effetto dannoso complessivo può risultare rilevante, specie se il segnale generato dal modulatore ha una frequenza piuttosto elevata (come nel nostro caso, che vale 352.8 kHz). Quanto appena descritto è noto come “dead time effect”[9].

Il blocco che vogliamo introdurre tra il modulatore e lo stadio di potenza non deve quindi soltanto generare due segnali B1 e B2 tali da garantire la presenza dei tempi morti, ma deve fare in modo che quei segnali abbiano caratteristiche tali da minimizzare la distorsione introdotta sul segnale di uscita. Per capire come devono essere i segnali di comando è utile osservare ancora una volta Figura 4.5, che mostra Vout (intesa come la tensione di Drain-Source di M2 o M4) quando i>0 (la corrente scorre verso il carico) o i<0 : a causa della presenza dei diodi in parallelo ai MOSFET, il segnale PWM di uscita devia rispetto alla forma d’onda ideale della quantità tratteggiata, in funzione quindi del verso della corrente. Durante i DT entrambi i transistori cessano di condurre, ma la corrente continua a circolare attraverso i diodi; tra D1 e D2, quale dei due conduce dipende dalla corrente: quando i>0 conduce D2 e la tensione di uscita durante il DT è a livello basso; viceversa, quando i<0 conduce D1 e la tensione di uscita durante il DT è a livello alto. E’ chiaro quindi che durante i DT la tensione di uscita dipende esclusivamente dalla direzione della corrente sul carico.

Un attento esame (Figura 4.5) rivela che per i>0 la larghezza dell’impulso di uscita è quella del segnale di pilotaggio B1 e che per i<0 la larghezza dell’impulso di uscita è quella del segnale B2.

Questo fa capire come Vout sia determinata in realtà da uno solo dei due segnali di comando, che chiamiamo per questo segnale “attivo”, a differenza dell’altro che è il segnale “inattivo”.

Allo scopo quindi di mantenere la larghezza originaria di ogni impulso, facciamo in modo che il segnale attivo sia sempre uguale al segnale di controllo ideale, cioè privo di

DT (vedi quello tratteggiato in Figura 4.5); il segnale inattivo invece sarà creato opportunamente per garantire la presenza dei tempi morti.

In Figura 4.6 è riportata una porzione del segnale PWM generato dal modulatore; S1 e S2 sono segnali ritardati di Td e 2⋅Td rispettivamente. I segnali che vogliamo in uscita al circuito generatore di Dead Time sono invece B1 e B2 e si vede facilmente che il segnale attivo (che è B2 per i<0 e B1 per i>0) è la replica di S1, mentre S2 viene usato per generare il segnale inattivo; tra le due coppie (B1,B2) di segnali di comando mostrate, quella da usare dipende dal verso della corrente.

Figura 4.6 : Forme d'onda per la compensazione del “dead time effect” : Tp>2Td (a) ; Tp<2Td (b)

La tensione di uscita seguirà quindi il segnale S1, che è semplicemente la replica del segnale di ingresso (o meglio il suo complementare) ritardata di Td; la presenza di questo ritardo non comporta alcuna conseguenza sul segnale di uscita.

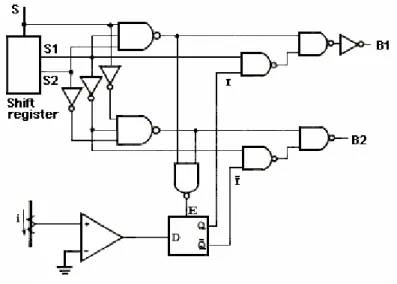

L’implementazione circuitale è ottenibile combinando il segnale di ingresso (che chiameremo S) ed i segnali traslati S1 e S2 con I, con cui indichiamo una variabile booleana che vale 1 o 0 a seconda rispettivamente se i>0 oppure i<0.

Considerando tutti i casi possibili, si arriva alle seguenti relazioni:

2 1 1 1 I S I S S S B = ⋅ + ⋅ ⋅ ⋅ (4.3) B2=I⋅S1+I⋅S⋅S1⋅S2 (4.4) 109

Per un ottimo funzionamento di quello che chiameremo “Dead Time Compensator” (DTC), occorre però tener conto di un problema: supponiamo che i<0 e (S,S1,S2)=(1,1,1); se i cambia verso durante il DT, B2 (=‘1’) commuta istantaneamente e B1(=‘1’) cambia stato alla fine dell’intervallo, ossia dopo un tempo Tx<Td rispetto alla commutazione di B2:

Figura 4.7: Commutazione di i durante un dead time

L’effetto di quanto detto è dunque che B1 va a ‘0’ senza che sia trascorso un intervallo sufficientemente lungo da quando è cambiato B2 (dato che Tx<Td) e ciò può portare all’indesiderato cortocircuito dell’alimentazione. Questa situazione può essere evitata impedendo a I di commutare nei versi indicato dalle frecce di Figura 4.6 negli intervalli relativi a dove sono disegnate: una freccia verticale verso l’alto in un intervallo significa che in tale intervallo bisogna evitare che I commuti da 0 a 1. Ciò è realizzabile permettendo alla variabile logica I di cambiare solo durante gli intervalli in cui (S,S1,S2) valgono (0,1,1) o (1,0,0); per garantire che questo avvenga è sufficiente un flip flop D (Figura 4.8), che blocca il segnale I durante gli intervalli caratterizzati dalla presenza di una freccia.

Un ultima precisazione riguardo la scelta di Td: osservando Figura 4.6(b) si capisce che se la durata Tp dell’impulso proveniente dal modulatore fosse minore di 2⋅Td, nel caso di i<0 B1 resterebbe a zero; ne segue che la scelta della durata dei DT è legata, oltre che ai tempi di ritardo dei transistori, anche alla durata degli intervalli di guardia (tg) introdotti dal modulatore nel segnale PWM.

La Figura 4.8 mostra il circuito reazionato completo che genera il DT; il comparatore in basso serve per valutare il verso della corrente sul carico.

Figura 4.8 : Dead Time compensator

4.1.3 Simulazioni con MATLAB

Affinché si riesca ad evitare il cortocircuito dell’alimentazione durante le commutazioni dei transistori è necessario che Td>max(td(on),td(off)).

Nel realizzare il modello Simulink dello stadio di potenza abbiamo fatto riferimento a MOSFET caratterizzati da td(on) pari a 4.3 ns e td(off) pari a 17 ns [23] e pertanto abbiamo simulato l’ effetto di “disallineamento” temporale delle risposte dei transistori introducendo dei ritardi del valore di 20 ns in ingresso ai transistori M1 e M3.

Per impedire il cortocircuito dell’alimentazione sicuramente occorreva scegliere dei valori di Td che fossero maggiori di 20 ns, ma per sapere quale fosse il valore ottimale che garantisse le migliori prestazioni degli amplificatori studiati abbiamo fatto diverse simulazioni, variando l’entità del Dead Time.

In Figura 4.9 sono mostrati gli andamenti di THD% e di rendimento per gli amplificatori AD e AD3, al variare di Td.

Come ci aspettavamo per Td al di sotto dei 20 ns si osserva in entrambi i casi una grande diminuzione di efficienza, a causa del cortocircuito dell’alimentazione; per Td maggiore di 40 ns il rendimento è a livelli massimi e varia ben poco al variare del Dead Time.

Figura 4.9: Valori di THD% e di rendimento al variare del Dead Time, per AD e AD3

Per quanto riguarda la distorsione, abbiamo rilevato (Figura 4.9) andamenti molto diversi tra AD e AD2, che utilizzano una PWM a due livelli, e AD3, che usa la PWM tri-state (si ricorda che AD1 era privo di DT).

Per i primi la distorsione assume valori minimi in assenza di DT e cresce quasi proporzionalmente con esso; per AD3 invece i valori migliori di Td sono compresi tra 45 ns e 70 ns e la THD minima si ha in corrispondenza di 70 ns circa.

Il fatto che la THD aumentasse per valori elevati di Td in parte ce lo aspettavamo, dato che non sono più verificate le relazioni

Tpulsemin>Td per AD, AD3 (4.5)

Tpulsemin>2⋅Td per AD2 (4.6)

le quali garantiscono che in fase di generazione del Dead Time non venga perso alcun impulso; in caso contrario si ha una perdita di informazione e quindi una distorsione del segnale.

Un particolare interessante è l’aumento di THD in AD3 in corrispondenza di valori di Td inferiori a 40 ns: questo significa che nell’amplificatore tri-state quando la diminuzione della durata del DT è eccessiva, la perdita di efficienza è accompagnata da una degenerazione del segnale di uscita.

architettura tg (ns) Td (ns)

AD,AD2 74 22 AD1 74 - AD3 43 70

Tabella 4.2: Valori di intervalli di guardia e di Dead Time scelti per le diverse architetture

In Tabella 4.2 sono riportati i valori di Td e di tg relativamente alle diverse architetture simulate; tali valori garantivano le prestazioni migliori a parità di stadio di potenza.

4.2 Controllo reazionato analogico

Quello che abbiamo visto nel paragrafo precedente era in pratica un controllo reazionato digitale ad un bit, in quanto il DTC generava una coppia di segnali (B1,B2) oppure un’altra a seconda del “segno” I assunto dalla corrente sul carico.

Com’è facilmente intuibile, questo tipo di controllo non è molto potente, ma oltre ad essere facilmente implementabile usa una tecnologia completamente digitale e per questo è adatto ad essere utilizzato in un amplificatore come il nostro.

Volendo realizzare un controllo reazionato più preciso, il fatto di avere un amplificatore digitale complica un po’ le cose. Per assicurarsi che il segnale di uscita sia (quasi) uguale a quello di partenza (fattore di amplificazione a parte), occorrerebbe infatti prelevare il segnale audio amplificato (che è analogico) e convertirlo in forma digitale per confrontarlo col segnale PCM in ingresso all’amplificatore (Figura 4.10).

Seppure abbastanza efficace, questo approccio è limitato dai requisiti che deve avere il convertitore A/D presente nell’anello di reazione. Un’alternativa molto valida è quella di basare il processo di correzione dell’errore sul confronto tra il segnale PWM generato dal modulatore e quello amplificato presente in ingresso al filtro passa basso dello stadio di potenza.

Figura 4.10 : Schema a blocchi classico di un amplificatore digitale reazionato

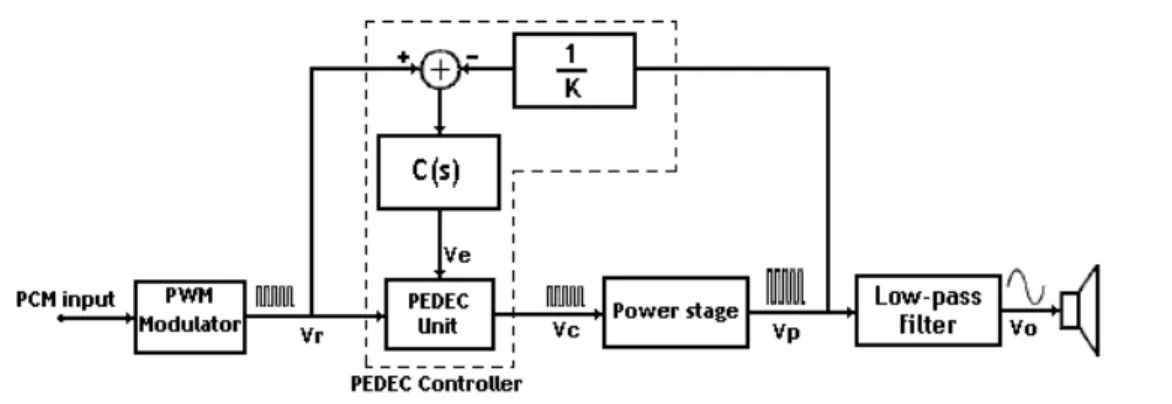

Un metodo di controllo che utilizza questa idea è il PEDEC (Pulse Edge Delay Error Correction)[6]. Alla base di questa tecnica ci sono due osservazioni importanti:

• il modulatore digitale genera un segnale PWM di ottima qualità e che quindi può essere utilizzato come riferimento per il sistema di controllo.

• tutte le sorgenti di errore presenti nello stadio di potenza possono essere corrette per mezzo di un intelligente re-timing degli impulsi del segnale generato dal modulatore.

Figura 4.11 : Amplificatore digitale con PEDEC

Il principio di funzionamento del PEDEC è abbastanza semplice: considerando che in uscita il segnale utile viene ottenuto da quello modulato ad impulsi tramite un filtraggio passa-basso (l’informazione è contenuta nel valore medio), la perfetta riproduzione del segnale audio si ottiene garantendo che l’area del segnale PWM, in un periodo, sia immune dai disturbi; questo significa che ad esempio una diminuzione della tensione di alimentazione durante un periodo deve essere compensata da un allargamento dell’impulso e viceversa un aumento della tensione di alimentazione durante un periodo

deve essere compensata da una riduzione della larghezza dell’impulso presente in quello stesso periodo.

Lo schema da considerare è mostrato in Figura 4.11. Il sistema di controllo è composto dalla PEDEC Unit e dal blocco di Error Processing; i segnali utilizzati per la correzione degli impulsi sono Vr, Vc,Ve e Vp. Con Vr indichiamo la forma d’onda di riferimento, ossia quella generata dal modulatore (descritto nel Cap.2); Vc è la forma d’onda PWM corretta dalla PEDEC Unit in base al valore di Ve, che è il segnale di errore che controlla il “pulse re-timing”; Vp è il segnale modulato ad impulsi amplificato dallo stadio a doppio inverter (Figura 4.12).

Il blocco di Error Processing confronta Vr con il segnale in uscita allo stadio di potenza (Vp) opportunamente scalato del fattore di amplificazione; quindi genera il segnale di errore Ve per la PEDEC Unit.

Diversi approcci per la correzione degli impulsi sono utilizzabili, ma il più efficace è quello che coinvolge entrambi i fronti di ogni impulso, quello di salita e quello di discesa; la tecnica di correzione usata dal blocco di Error Processing da noi studiato è di questo tipo.

Supponiamo che la PEDEC Unit modifichi la larghezza degli impulsi di una quantità ∆tW proporzionale al segnale Ve proveniente dal blocco di Error Processing; sotto tale

ipotesi si ha: ∆tw =kw⋅Ve (4.7) ossia w e w k dV dt = (4.8)

Ipotizziamo che il segnale Vc in uscita dalla PEDEC Unit vari tra +VcM e –VcM e che

quello in ingresso sia compreso tra –VrM e +VrM; vedremo in seguito che per la PEDEC

Unit avere un segnale bipolare in ingresso ne facilita l’implementazione.

Cerchiamo la relazione tra ∆tw e la variazione del valore medio del segnale Vc; mediando

su un periodo di switching Ts, si ottiene:

M w M Ts tw Ts d tw Ts d Vc t Ts Vc dt dt Ts c V ⎟⎟⋅ = ⋅∆ ⋅ ⎠ ⎞ ⎜⎜ ⎝ ⎛ ⋅ − + ⋅ = ∆

∫

∫

∆ + ⋅ ∆ + ⋅ 2 ) 1 ( 1 1 ~ 0 (4.9)ove ‘d’ è il duty cycle del segnale PWM nel periodo considerato. Ne segue:

M w Vc Ts dt c V d~ = 2 ⋅ (4.10)

Si arriva così a calcolare KPEDEC, cioè la funzione fondamentale di controllo della

PEDEC Unit; è definita come la derivata del valore medio del segnale di uscita al PEDEC rispetto a Ve:

PEDEC kw VcM Ts dVe c V d K = = 2 ⋅ ⋅ ~ (4.11)

Come mostra l’espressione appena trovata, la funzione di controllo è in pratica un guadagno lineare e questo semplifica molto il progetto del sistema reazionato.

Lo schema a blocchi scelto per l’implementazione della tecnica PEDEC è quello proposto da K.Nielsen[6]:

Figura 4.12 : Amplificatore digitale con PEDEC (schema completo)

Il maggiore vantaggio di questo controllo reazionato è che è un buonissimo compromesso tra semplicità di implementazione e buona capacità di correzione degli errori introdotti nel segnale PWM dallo stadio di potenza.

Si osservi come il segnale audio rimanga digitale o comunque impulsivo attraverso tutto l’amplificatore.

4.2.1 PEDEC Unit

La realizzazione della PEDEC Unit prevede la presenza all’interno del blocco di un circuito in grado di generare a partire da Vr un segnale Vi come quello di Figura 4.13; Vi

viene poi confrontato con Ve e da tale confronto viene prodotto Vc.

Figura 4.13 : Double-pulse edge delay correction (in funzione di Ve)

Un’attenta analisi degli andamenti di Figura 4.13 mostra che un’inevitabile limitazione di questo approccio è che la PEDEC Unit causa un ritardo temporale di t0/2 in assenza di

correzione (vedi Ve=0) e perciò il range di correzione della larghezza di impulso è

limitato a t0. Questo in realtà non è un grosso problema dato che in effetti le correzioni

necessarie per il segnale PWM non sono di grossa entità.

In funzione di Ve, i casi da considerare sono sostanzialmente tre: - Ve =0: l’impulso ha stessa larghezza, ma è ritardato di t0/2 - Ve<0: la larghezza dell’impulso diminuisce

- Ve>0: la larghezza dell’impulso aumenta

Analizziamo in dettaglio il tipo di correzione a “doppio fronte” proposto; con tw

abbiamo indicato la larghezza dell’ impulso generato dal modulatore, con e i fronti del segnale PWM dopo la correzione, con t

l tˆ tˆr

0 la durata della rampa prodotta

dall’integratore all’ interno della PEDEC Unit; con VI il massimo valore di Vi.

Valgono le seguenti relazioni:

I l l V Ve t t t t 2 2 ˆ = + 0 + 0 (4.12) I r r V Ve t t t t 2 2 ˆ = + 0 − 0 (4.13) I w l r w V Ve t t t t tˆ =ˆ −ˆ = − 0 (4.14) da cui si ricava : 0 t tw = ∆ se (Ve>VI) I w V Ve t t = 0 ∆ se (−VI <Ve<VI) 0 t tw =− ∆ se (Ve<VI) (4.15)

In altre parole, kw definita precedentemente (4.8) vale:

I w w V t dVe dt k = = 0 (4.16)

e quindi dalla (4.11), nell’ipotesi di VcM= VI:

Ts t dVe c V d KPEDEC 2 0 ~ ⋅ = = (4.17)

Bisogna tener presente che per un funzionamento corretto della PEDEC Unit proposta è necessario (vedi Figura 4.14) che gli impulsi abbiano una larghezza minima maggiore o uguale a t0. Questo è garantito dal modulatore (Cap.2), che inserisce degli intervalli di

guardia tg all’inizio e alla fine di ogni periodo di switching; in questo modo ogni impulso del segnale PWM ha una durata minima pari a tg1 ed una massima pari a (Tword-tg2), ove tg1 e tg2 sono teoricamente uguali.

Figura 4.14 : Comportamento del circuito con impulso di larghezza minima

Nella scelta finale degli intervalli di guardia per AD1 abbiamo dovuto tener conto quindi anche del fatto che minore era tg1 e minore sarebbe stato t0, che corrisponde alla massima correzione fattibile sul segnale PWM da parte della PEDEC Unit.

La nostra scelta è stata quella di utilizzare un intervallo di guardia di 70 ns; in fase di progettazione del PEDEC è stato necessario quindi fare in modo che t0 fosse minore o

al limite uguale a questo valore e nel modello Simulink abbiamo usato t0 pari a 60 ns.

Una volta scelto questo valore, abbiamo implementato la funzione di correzione degli impulsi descritta fino ad ora per via analitica.

In definitiva la PEDEC Unit consiste in un integratore con saturazione seguito da un comparatore; l’integratore deve fornire le rampe del segnale Vi in salita e in discesa (vedi Figura 4.13) e pertanto occorre che in ingresso riceva un segnale Vr a doppia polarità: se infatti Vr variasse da 0 a 5 V e non da –2.5V a 2.5V, l’integratore fornirebbe una rampa in salita in corrispondenza del livello alto di Vr, ma rimarrebbe costante quando Vr=0 ed otterremmo così un segnale a gradinata. Ecco quindi che se Vr arriva da un circuito digitale- come nel nostro caso - è necessario utilizzare un traslatore di livello in ingresso alla PEDEC Unit (Figura 4.15).

Figura 4.15 : Schema a blocchi della PEDEC Unit

4.2.2 Error processing

Analizzato in dettaglio il funzionamento della PEDEC Unit, rimane da studiare il blocco di Error Processing, ossia quello che produce il segnale Ve. Le principali funzioni da esso svolte sono tre: attenua di un fattore K il segnale PWM proveniente dall’uscita dello stadio di potenza, lo confronta con il segnale di riferimento (Vr) proveniente dal modulatore e produce il segnale Ve per mezzo di un filtraggio passa basso.

Attenuazione

Per quanto riguarda l’attenuazione del segnale di uscita, può essere realizzata semplicemente tramite un amplificatore operazionale con guadagno 1/K, ove K è un

fattore di attenuazione che deve permettere di ridurre la dinamica del segnale PWM Vp fino al valore della dinamica di Vr (Figura 4.12). Nel nostro caso la tensione di alimentazione Vdd dello stadio di amplificazione valeva 25 V e sia i segnali di comando dei transistori che Vr avevano dinamica pari a 5 V. Indicando con KP il fattore di

guadagno dello stadio a MOSFET e ricordando che il segnale prelevato dall’uscita variava tra +25 V e –25 V (la configurazione adoperata era di tipo Full-Bridge) nel nostro caso K=KP=10.

Filtraggio

Il filtro, come già accennato, svolge una funzione passa basso; la funzione di trasferimento da noi utilizzata è quella proposta da Nielsen [6], che prevede la presenza di uno zero e 3 poli:

) 1 )( 1 )( 1 ( ) 1 ( ) ( 3 2 1 1 + + + + = s s s s Kc s C P P P Z τ τ τ τ (4.18)

Lo schema completo del modello linearizzato del sistema reazionato di correzione da noi utilizzato è quindi il seguente:

Figura 4.16: Modello linearizzato del sistema di controllo con PEDEC

Si tenga presente che il modello di Figura 4.16 fa riferimento alle variazioni del valore medio dei segnali PWM (vedi V~r,V~c,V~p) perché il metodo di correzione PEDEC è

basato sulla modifica della durata degli impulsi in modo da mantenere la loro area (e quindi il valore medio del segnale) immune dai disturbi introdotti dallo stadio di potenza. A questo punto determinare la funzione di trasferimento del sistema a catena aperta L(s) è immediato: ⋅ = = K K KcK s C K K K s L( ) P PEDEC ( ) P PEDEC ) 1 )( 1 )( 1 ( 1 3 2 1 1 + + + + s s s s P P P Z τ τ τ τ (4.19)

Dall’espressione di L(s) si ricava facilmente la “funzione di sensitività” S(s):

(

1)(

1) (

1)

1 1 1 ) ( 3 2 1 1 + + + + + ⋅ + = s s s s K K KcK s S P P P Z PEDEC P τ τ τ τ (4.20)che esprime la riduzione della sensitività del sistema agli elementi dello stadio di potenza (lineari e non lineari) secondo la relazione:

) ( ) , ( ) ( α α α αH s S s SKP S = (4.21)

dove α indica un effetto di “non idealità” (come rumore, distorsione o perturbazioni sovrapposte all’alimentazione), KP è il guadagno dello stadio di potenza (influenzato da α) e H è la funzione di trasferimento del sistema reazionato complessivo (comprendente lo stadio di amplificazione). L’espressione di H(s) si ricava dal modello di Figura 4.16:

) ( 1 ] 1 ) ( [ ) ( 1 ) ( 1 ) ( ) ( s L K s C K s L K s L K K s C s H P PEDEC P P PEDEC + + = + + + = (4.22)

Si osservi che andando a sostituire le espressioni di C(s) e L(s) in H(s) si ottiene, per K=KP, che

[

]

K K s C K s C K s H PEDEC PEDEC = + + = ) ( 1 1 ) ( ) ( (4.23)ossia la funzione di trasferimento del sistema di controllo è una costante pari al guadagno dello stadio di amplificazione. Questo significa che in teoria il valore medio del segnale PWM generato dal modulatore non viene modificato in alcun modo dal PEDEC, ma al tempo stesso il segnale di uscita dell’amplificatore è meno sensibile ai disturbi introdotti dallo stadio di potenza.

Questa particolare caratteristica del sistema di controllo proposto dipende dal fatto che il segnale di riferimento Vr viene utilizzato sia per generare il segnale di errore Ve, sia (per mezzo di Vi) il segnale “corretto” Vc; a questo proposito si parla di “dual input topology”.

Indichiamo con fu la frequenza di guadagno unitario del sistema a catena aperta,

normalizzata rispetto alla banda dell’amplificatore fb che nel nostro caso vale 20 kHz.

Per ottenere un miglioramento rilevante del segnale audio di uscita entro la banda audio, la fu dovrebbe avere un valore compreso tra 5 e 10 [6].

Una volta scelti i valori di t0 e fb, la posizione dei poli e degli zeri del filtro C(s)

contenuto nel blocco di Error Processing (Figura 4.12) è stata fissata in base ai valori riportati in [6] e riassunti nella Tabella 4.3. La Tabella 4.4 mostra il valore di ogni parametro usato nel nostro modello Simulink del PEDEC.

Parametro Valore

normalizzato Commento

ωu 5 Minimo valore raccomandato per la frequenza di guadagno unitario

ωp1 0.4 Polo del filtro

ωp2 0.4 Polo del filtro

ωp3 2ωu Polo del filtro

ωz1 ωu /2 Zero del filtro

Tabella 4.3: Valori normalizzati delle frequenze che caratterizzano il PEDEC

Parametro Valore Commento

fb 20 kHz Banda dell’amplificatore K,KP 10 Guadagno dello stadio di potenza

Kc 450 Guadagno del filtro t0 60 ns Massimo intervallo di correzione

τP1, τP2 19.89 µs Polo del filtro

τP3 795,77 ns Polo del filtro τz1 3.183 µs Zero del filtro

Tabella 4.4: Valori dei parametri usati nel modello Simulink del PEDEC

A proposito di t0, occorre precisare che la scelta non è stata semplice in quanto legata,

come visto precedentemente, alla durata dell’impulso più breve del segnale PWM. Nel Cap.2 abbiamo visto che aumentare troppo tg1 significa non solo diminuire la dinamica

del segnale audio di uscita, ma anche aumentare il valore di THD; nella progettazione del PEDEC però un valore basso di tg1 comporta un valore altrettanto basso di t0 e quindi di KPEDEC(vedi(4.17)), con conseguente diminuzione del “potere correttivo” del

controllo reazionato. Con le scelte fatte (tg1=70ns, t0 =60 ns, KPEDEC =0.042) abbiamo

cercato quindi di raggiungere un compromesso tra le due esigenze. Il modello Simulink del PEDEC è riportato in Figura 4.17.

4.2.3 Introduzione del Dead Time

Nell’amplificatore AD1 il generatore di Dead Time non è stato utilizzato, in quanto il controllo reazionato con PEDEC non ne permetteva una semplice introduzione. Il problema risiede nella natura stessa della generazione di DT, che prevede l’utilizzo del segnale PWM fornito dal modulatore per la creazione di due segnali di comando (B1 e B2) dello stadio di potenza. Inserire un generatore di DT all’interno del PEDEC avrebbe significato falsare la correzione apportata dal controllo reazionato, perdendone l’efficacia. D’altro canto, inserire il DT a monte del PEDEC non era possibile, poiché per sua natura il PEDEC funziona con un solo segnale PWM, mentre il circuito di DT

ne produce due; anche applicando la reazione a B1 (o a B2) avremmo avuto il problema del prelievo di segnale dallo stadio di potenza per il confronto col segnale di riferimento (B1 o B2 appunto).

Per queste ragioni abbiamo deciso di non utilizzare alcun DT, in modo sia da verificare l’efficacia del controllo reazionato, sia da analizzare le conseguenze dell’assenza di un generatore di DT in un amplificatore audio. Dopo quanto già detto sull’utilità dei Blanking Delay, in AD1 ci aspettavamo ovviamente un forte calo dell’efficienza rispetto alle altre architetture, a causa del verificarsi di cortocircuiti dell’alimentazione in corrispondenza degli istanti di commutazione; i risultati (Cap.5) hanno confermato le nostre aspettative.

Figura 4.17: Modello Simulink del PEDEC