Capitolo 3

Riferimento di tensione in tecnologia CMOS 90 nm

Specifiche di progetto

Il riferimento di tensione è un circuito integrato realizzato in tecnologia CMOS 90 nm, utilizza solo MOSFET ed è pensato per applicazioni a bassissimo consumo di potenza. Vediamo in dettaglio le specifiche che deve soddisfare:

• Bassa tensione d’alimentazione ≤ 1 V • Basso consumo di potenza <1 μW • Completa integrabilità

• Ridotta occupazione dell’area occupata sul chip • Bassa sensibilità di linea LS (pochi mV/V)

• Basso coefficiente di temperatura TC (poche decine di ppm)

Abbiamo visto nel primo capitolo i limiti dei riferimenti di tensione a band-gap ed alcune soluzioni presenti in letteratura che cercano di superarli. Questi si basano essenzialmente sul principio di compensazione, ovvero sulla somma di due termini in uscita che dipendono in maniera opposta dalla temperatura in modo da annullarne gli effetti. In particolare si genera una corrente PTAT che viene iniettata in un carico attivo per ottenere in uscita la somma della corrente PTAT stessa e di un termine NTAT (per esempio la tensione di soglia di un MOSFET). Così facendo otterremo una tensione d’uscita molto stabile con la temperatura. Vediamo l’architettura del riferimento di tensione.

Architettura riferimento di tensione

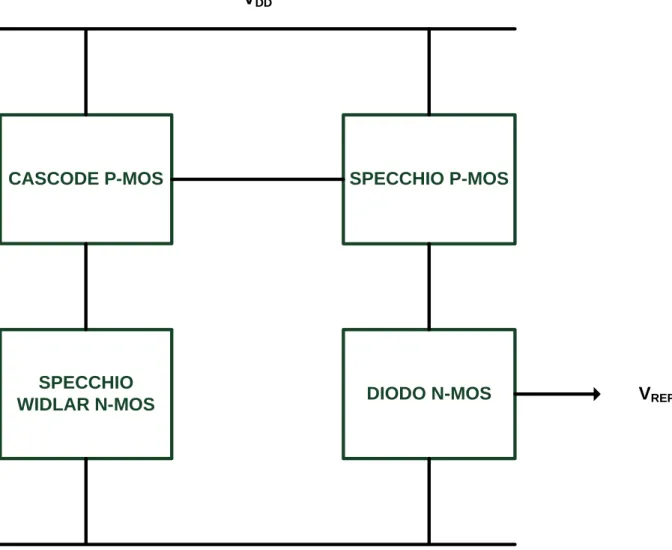

L’architettura del riferimento è quella di figura 3.1. Il circuito consiste in un generatore di corrente costituito da uno specchio di corrente Widlar n-mos e di uno specchio cascode p-mos. La corrente generata viene specchiata e iniettata in un n-mos montato a diodo.

SPECCHIO WIDLAR N-MOS

CASCODE P-MOS SPECCHIO P-MOS

DIODO N-MOS

VDD

GND

VREF

Figura 3.1: Architettura riferimento di tensione.

Specchio di corrente Widlar n-mos

Il primo problema da risolvere è stato quello di generare una corrente quasi indipendente dalla variazione della tensione d’alimentazione così che risultasse tale anche la tensione d’uscita del riferimento. Non è stato possibile utilizzare uno specchio semplice in quanto la resistenza d’uscita differenziale sarebbe stata troppo bassa. Infatti se i transistori lavorano in saturazione, questa è data da:

Rout = (3.1) rd

dove r è la resistenza tra drain e source del transistore. Per aumentarne il valore abbiamo d aggiunto una resistenza R sul source di un transistore in modo da ottenere: s

Rout=Rs +rd

(

1+gmRs)

(3.2)Inoltre, avendo i transistori tensioni di soglia molto basse, è stato possibile utilizzare uno specchio Widlar cascode (figura 3.2) che ci ha permesso di avere una resistenza d’uscita ancora più alta senza avere un’eccessiva riduzione della dinamica del circuito. La resistenza d’uscita risulta così:

Rout=Rvd2 +rd4

(

1+gm4Rvd2)

(3.3)con Rvd2 dato da:

R

sM

1M

3M

4M

2I

1I

2Figura 3.2: Specchio cascode Widlar n-mos.

Tutti i transistori lavorano in saturazione, M1 e M2 sono a canale lungo (10 μm) per

minimizzare l’effetto di modulazione della lunghezza di canale. Possiamo scrivere:

Vgs1 =Vgs2 +RsI2 (3.5) Ricavando le V dalla (2.10): gs 1 1 1 1 1 1 th bulk dsat sat ox gs V A V v c W I V = + + (3.6)

2 2 2 2 2 2 th bulk dsat sat ox gs V A V v c W I V = + +

con V ,th Abulk, Vdsat date rispettivamente da (2.2), (2.7), (2.11). Lo specchio cascode p-mos (figura 3.3), assicura l’uguaglianza delle correnti nei due rami quando varia la tensione di alimentazione (I1 = I2 =I) . Sostituendo le (3.6) nella (3.5):

V V A V A V R I W W v c I s dsat bulk dsat bulk th th sat ox = − + − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − 1 2 1 1 2 2 2 1 1 1 (3.7) ricavando I : sat ox s dsat bulk dsat bulk th th v c W W R V A V A V V I ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − − + − = 2 1 2 2 1 1 2 1 1 1 (3.8)

Abbiamo scelto un valore di Rs=1.2MΩ in modo da avere una corrente di polarizzazione bassa di circa 48.74 nA. La resistenza sarà realizzata in silicio altamente resistivo (HIPO) perché non occupi un’area troppo grande rispetto a quella occupata dall’intero circuito. I valori diW1, W2 sono stati scelti tali da far lavorare tutti i transistori in saturazione e di

ottenere una corrente di polarizzazione che non dipenda troppo dalle variazioni dell’alimentazione. Il dimensionamento completo dello specchio di corrente è riportato nella tabella 3.1.

COMPONENTE VALORE M1 W=0.14 μm L=10 μm M2 W=1.1 μm L=10 μm M3 W=0.36 μm L=3 μm M4 W=0.36μm L=3 μm Rs 1.2 MΩ

Tabella 3.1: Dimensionamento dello specchio cascode Widlar n-mos.

Specchio di corrente Cascode p-mos

Lo specchio cascode come visto, consente di avere la stessa corrente nei due rami del circuito anche per variazioni della tensione d’alimentazione. Questo si ottiene grazie ai transistori

7

M , M che impongono l’uguaglianza della 8 V dei transistori ds M , 5 M . I transistori devono 6

lavorare in saturazione ed avere dimensioni tali che:

6 6 5 5 8 8 7 7 L W L W L W L W = (3.9)

COMPONENTE VALORE M5 W=0.36 μm L=3 μm M6 W=0.36 μm L=3 μm M7 W=0.36 μm L=3 μm M8 W=0.36 μm L=3 μm Tabella 3.2: Dimensionamento dello specchio cascode p-mos.

Anche in questo caso utilizzando un cascode abbiamo una perdita di dinamica. La tensione d’alimentazione minima che occorre affinché tutti i transistori del generatore di corrente lavorino in saturazione è data da:

(

gs th)

pgsn V V V

Vmin ≥2 +2 −

Supponendo che i valori di V siano di circa 100mV maggiori di gs V , otteniamo una th Vmin

d’alimentazione di circa 1V.

V

DDM

8M

7M

6M

5I

I

Figura 3.3: Specchio cascode p-mos.

Specchio d’uscita e carico attivo

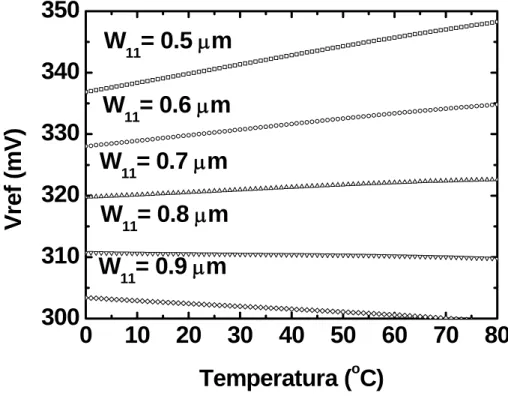

Il circuito d’uscita del riferimento di tensione consiste in uno specchio p-mos e in un n-mos montato a diodo (figura 3.4). I dispositivi sono a canale lungo (10 μm) e lavorano in saturazione. La corrente generata PTAT viene specchiata dai p-mos M , 9 M e iniettata 10 inM11 . La larghezza diM11 in uscita, come vedremo in seguito, è stata ottenuta calcolando il

valore ottimo che annulla la derivata della tensione di riferimento rispetto alla temperatura. Questo valore stimato analiticamente è di circa 0.7 μm, un’attenta simulazione parametrica in Cadence, fornisce il valore ottimo di 0.785 μm. Il dimensionamento del circuito di uscita sarà quindi quello mostrato nella tabella 3.3.

COMPONENTE VALORE M9 W=2.43 μm L=10 μm M10 W=0.7 μm L=10 μm M11 W=0.785 μm L=10 μm Tabella 3.3: Dimensionamento del circuito d’uscita.

M

9M

10V

DDM

8M

6M

11I

I

outV

REFRicaviamo il valore della corrente d’uscita Iout:

Iout =W9coxvsat

(

Vgst9 −Abulk9Vdsat9)

(3.10)(

8 8 8)

8

8 I W coxvsat Vgst Abulk Vdsat

I = = −

Inoltre invertendo la seconda equazione:

8 8 8 8 9 8 bulk dsat th sat ox gs gs A V V v c W I V V = = + + (3.11)

e sostituendo nella prima equazione:

(

8 8 9 9 8 9)

9 8 9 9 9 9 8 8 8 8 9 th th dsat bulk dsat bulk sat ox dsat bulk th th dsat bulk sat ox sat ox out V V V A V A v c W I W W V A V V V A v c W I v c W I − + − + = = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − + + = (3.12)La corrente in uscita vale circa 153.73 nA. In figura 3.5 è mostrato l’andamento della Iout in funzione della variazione della tensione d’alimentazione quando quest’ultima varia da 1 a 2.5 volt. Per una variazione di un volt, la corrente varia di 0.356 nA (0.23%).

1.0

1.5

2.0

2.5

153.7

153.8

153.9

154.0

154.1

154.2

154.3

Iout

(

n

A

)

Vdd (V)

Figura 3.5: Andamento della corrente d’uscita in funzione dell’alimentazione.

Ricaviamo la tensione d’uscita:

11 11 11 11 11 th bulk dsat sat ox out gs ref V A V v c W I V V = = + + (3.13)

Calcolo del coefficiente di temperatura della tensione d’uscita

Il valore della tensione d’uscita è stato precedentemente calcolato supponendo nota la larghezza di canale W11. La larghezza di canale ottima è quella che annulla la derivata della

tensione d’uscita rispetto alla temperatura. Nell’espressione della Vref , i termini che dipendono dalla temperatura sono Iout, vsat, Vth11, Vdsat11. I termini vsat e Vth11 sono noti (2.16,

2.18), rimangono da caratterizzare Iout e Vdsat11. L’andamento della Iout in funzione della temperatura è quello riportato in figura 3.6.

0

10

20

30

40

50

60

70

80

120

130

140

150

160

170

180

190

200

Iout (nA

)

Temperatura (

oC)

Figura 3.6: Andamento della corrente d’uscita in funzione della temperatura.

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + = 1 0 0 T T I Iout ϑ (3.14) con I0 =Iout

( )

T0 =151.991nA, T0 =298,15K , ϑ =239.696nA.Rimane da caratterizzare il comportamento in temperatura del termine Abulk11 dsatV 11 della (3.13). Abbiamo visto nel capitolo 2 l’andamento di Abulk per un n-mos a canale lungo in funzione della tensione di overdrive Vgst =Vgs −Vth. Possiamo supporre che questa tensione valga circa 50 ÷ 150 mV, in quanto da un lato vogliamo che i transistor lavorino con una V gs superiore di almeno 50 mV alla tensione di soglia per garantirne il funzionamento in saturazione, dall’altro vogliamo una tensione d’alimentazione che non superi 1 V. Con questa condizione 127Abulk =1. . Il termine Abulk11 dsatV 11 ha l’andamento di figura 3.7.

0

50

100

150

200

0

50

100

150

200

AbVdsat

Vgst (mV)

Nell’intervallo di tensione in cui Vgst vale 50 ÷ 150 mV l’andamento di Abulk11 dsatV 11 è approssimabile con la retta:

Abulk11Vdsat11=βVgst (3.15) 9994 . 0 = β L’espressione (3.13) diventa:

(

)

11 11 11 1 th sat ox out gs ref V v c W I V V + − = = β (3.16)ed esplicitando le dipendenze dalla temperatura:

( )

( )

( ) (

( )

)

( )

(

)

⎟⎟⎠ ⎞ ⎜⎜ ⎝ ⎛ − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + + + + − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + = = + − ⋅ = = 1 1 1 1 1 0 2 1 1 0 0 0 11 0 0 11 11 11 T T V K L K K V T T A v c W T T I T V T v c W T I T V T V bseff t eff l t t th T sat ox th sat ox out gs ref β ϑ β (3.17)

(

)

(

)

(

)

( )

(

)

0 1 2 11 0 0 0 11 0 0 11 0 1 1 1 1 1 T K T v c W T T T I A c W T T A v c W T T V t sat ox T ox T sat ox ref + + − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + − + ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − − = ∂ ∂ β ϑ β β ϑ (3.18) ponendo =0 ∂ ∂ T Vref si ottiene il valore di W11:(

( )

( )

)

(

)

(

( )

)

2 1 11 1 c v T K T I A T v W sat ox t T sat β ϑ − + − = (3.19) per T = la (3.19) diventa: T0(

)

(

)

2 0 1 0 0 11 1 ox sat t T sat v c K I A v W β ϑ − + − = (3.20)Sostituendo i valori si ottiene W11 =0.7μm.

Il valore ottimo di W11è confermato anche dalla simulazione parametrica che abbiamo

0

10

20

30

40

50

60

70

80

300

310

320

330

340

350

W

11= 0.9

μ

m

W

11= 0.8

μ

m

W

11= 0.7

μ

m

W

11= 0.6

μ

m

W

11= 0.5

μ

m

Vr

ef (m

V)

Temperatura (

oC)

Figura 3.8: Andamento di Vref in funzione della temperatura per varie larghezze W11.

VDD M8 M7 M6 M5 I I Rs M1 M3 M4 M2 I I M9 M10 M11 Iout Iout Vref

Regolatore di tensione

Il riferimento di tensione di figura 3.9 è stato utilizzato per realizzare un regolatore di tensione in tecnologia CMOS 90 nm. Il regolatore è costituito da un amplificatore differenziale che confronta la tensione d’uscita del riferimento con la tensione d’uscita del regolatore e produce un segnale che pilota il gate di un transistore n-mos in modo da mantenere costante la tensione d’uscita e pari a quella del riferimento (figura 3.10).

-+

Vref Vdd Vreg Rl MuFigura 3.10: Architettura regolatore di tensione.

Amplificatore differenziale con carico attivo

L’amplificatore differenziale del regolatore è a p-mos con un carico attivo formato da uno specchio cascode n-mos (figura 3.11).

V

DDVref

Vreg

V

G19I18

M12

M13

M14

M15

M17

M16

M18

Figura 3.11: Amplificatore differenziale p-mos del regolatore di tensione.

L’amplificatore differenziale non è in grado di attenuare le variazioni della corrente di polarizzazione causate dalle variazioni della tensione d’alimentazione. Infatti l’effetto di questa variazione sulla tensione d’uscita del regolatore è dato da [11]:

m l mu mu m dp dn l mu l mu dp dn reg g R g g g r r R g R g r r I V 1 1 2 1 1 2 18 ≅ + + + ≅ Δ Δ (3.21)

dove r è la resistenza tra drain e source dei p-mos e,dp rdn =rd15 +rd13+gm15rd15rd13 la resistenza vista dal drain di M , 15 g la transconduttanza dei p-mos dell’amplificatore m differenziale, g la transconduttanza del n-mos d’uscita del regolatore, u R la resistenza in l uscita. Essendo la corrente di polarizzazione molto bassa, lo è anche g e quindi la tensione m d’uscita del regolatore dipende fortemente dalla corrente di polarizzazione. Per questo motivo l’amplificatore è polarizzato specchiando la Iout (quasi indipendente dall’alimentazione) con

18

M .

La tensione d’uscita del regolatore dipende dalla tensione d’alimentazione secondo la [11]:

du mu dp dn m m dp dn du l mu du l dd reg r g r r g g r r r Rl R g r R V V 2 1 2 1 1 ≅ + + + ≅ Δ Δ (3.22)

dove gmu è la transconduttanza del n-mos d’uscita e r la sua resistenza drain-source. Per du minimizzare la (3.22), gmurdudeve essere grande, quindi il mos n d’uscita deve essere a canale largo. Inoltre deve essere grande il guadagno dell’amplificatore differenziale e quindi i transistori M e 16 M sono a canale lungo. Il dimensionamento completo del regolatore di 17 tensione è riportato nella tabella 3.4.

COMPONENTE VALORE M12 W=0.12 μm L=10 μm M13 W=0.12 μm L=10 μm M14 W=0.12 μm L=10 μm M15 W=0.12 μm L=10 μm M16 W=0.12 μm L=10 μm M17 W=0.12 μm L=10 μm M18 W=0.4 μm L=10 μm Mu W=10 μm L=0.12 μm Rl 1.2 MΩ

Layout del regolatore di tensione

Il circuito è stato realizzato su un’area rettangolare di circa 0.016 mm2 utilizzando due livelli di metal. Gran parte dello spazio è occupato dalle due resistenze da 1.2 MΩ che sono visibili solo parzialmente in figura 3.12.