Capitolo 2

Tecnologia CMOS 90 nanometri e modello approssimato BSIM3V3

Ambiente di progetto

La progettazione di circuiti integrati viene svolta con l’ausilio di strumenti CAD che consentono di sviluppare le varie fasi di progetto dalla descrizione elettrica (schematic) del circuito fino a quella fisica (layout) e di verificare attraverso simulazioni se il comportamento del circuito è quello richiesto dalle specifiche.

In questo lavoro di tesi è stato utilizzato il simulatore Cadence Design Framework.

Gli strumenti che ha a disposizione sono SPECTRE per le simulazioni circuitali e VIRTUOSO per la definizione dello schematic e del layout. Il simulatore deve essere preparato con l’installazione di librerie costituenti il design-kit che adattano l’ambiente di progetto allo specifico processo con cui verrà fabbricato il circuito. Il design kit viene quindi fornito dall’industria che realizzerà il chip. Quello che verrà utilizzato si riferisce alla tecnologia CMOS 090 fornita da STMicroelectronics. Andiamo ad analizzare brevemente le caratteristiche di questa tecnologia.

Tecnologia CMOS 090

Il processo presenta le seguenti caratteristiche principali [9]:

• Lunghezza effettiva di gate di 65 nm • Transistori con doppia tensione di soglia • Doppio ossido di gate

• 7 livelli di metallizzazione • Basse costanti dielettriche (<3) • Tripla Well

• SRAM ad alta densità

I dispositivi per la progettazione analogica sono caratterizzati nella libreria cmos 090.

Oltre a transistori con tensione di soglia standard (SVT) ed alta (HVT) sono presenti anche transistori con bassa tensione di soglia (LVT). Questi sono transistori ad ossido sottile (16 A), adatti per tensioni d’alimentazione nominale di 1 V, ma sopportano una tensione massima di 1.1 V. Per tensioni nominali più alte (1.8 V, 2.5 V, 3.3 V) vengono forniti 3 tipi di transistori ad ossido spesso (28 A, 50 A, 65 A). Oltre ai suddetti transistori sono presenti nella libreria diodi, resistori diffusi, in metallo e polisilicio, capacità. Il processo supporta anche resistori realizzati in polisilicio ad alta resistività (HIPO) per resistenze di valore elevato (alcuni MΩ). Non sono previste induttanze.

Modello BSIM3V3 approssimato

Il simulatore deve includere files (models) che contengono una descrizione del comportamento fisico dei dispositivi. Esistono diversi livelli di complessità crescente per tener conto in modo più preciso e dettagliato possibile di tutti i parametri fisici che caratterizzano il dispositivo. SPECTRE utilizza per le simulazioni il modello BSIM3V3 [10]. A partire da tale modello cercheremo di ricavare dell’equazioni approssimate più semplici da gestire analiticamente in modo da utilizzarle dove possibile, per ricavare le grandezze d’interesse.

Tensione di soglia

L’espressione della tensione di soglia riportata nel manuale BSIM3V3 considera numerosi effetti fisici quali drogaggio non uniforme, effetto di canale corto, effetto di canale stretto ed è la seguente:

(

)

(

)

(

)

(

ta tab bseff)

ds to eff sub to eff sub s bi t eff VT t eff VT VT s bi tw eff eff w VT tw eff eff w Vt w VT s eff ox bseff s eff ox bseff s ox ox th V V E E l L D l L D V l L D l L D D V l L W D l L W D D W W T V K K L Nlx K V K Vth V + ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − Φ − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − Φ − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − Φ + + + Φ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + + − Φ ⋅ + = 0 1 1 0 1 0 0 0 3 3 1 10 0 exp 2 2 exp exp 2 2 exp ' exp 2 2 ' exp ' 1 (2.1) con: s th ox th V K V 0 = 0 − 1⋅ Φ oxm ox ox T T K K1 = 1⋅ oxm ox ox T T K K2 = 2⋅I parametri sono estratti con un valore di T pari a quello nominale ox Toxm.

La relazione presenta numerosi parametri che dipendono dal processo e disponibili nella model fornita dal costruttore. Presteremo maggiore attenzione a quelli riguardanti i

transistori lvt (nlvt, plvt) in quanto siamo interessati ad una progettazione ‘low-power’ e di conseguenza a basse tensioni di alimentazione (intorno ad 1V). Le specifiche di progetto prevedono la realizzazione di un riferimento di tensione con bassa sensibilità di linea (Line

Sensitivity). Per tale motivo, come vedremo meglio in seguito, non utilizzeremo transistori

con lunghezza di canale minima (0.10 μm). Questo permette di poter trascurare i termini che dipendono da Leffcon un esponenziale negativo ed il termine con Leff al denominatore. La

tensione di soglia e’data da:

(

)

(

)

0 3 3 2 1 0 ' W W T V K K V K V K V V eff s ox bseff b bs s bseff s th th + Φ + + − Φ − − Φ + = (2.2) con: ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = Φ i ch b s N N q T K ln 2 bseffV è la polarizzazione del substrato, Weff' la larghezza effettiva di canale,

K J Kb 23 10 38 . 1 ⋅ −

= la costante di Boltzmann , q=1.6⋅10−19C la carica dell’elettrone,

K

T =298.15 la temperatura ambiente, T0x =1.95⋅10−9m lo spessore dell’ossido, Φ il s

potenziale superficiale, =1.269⋅1010 −3

cm

Ni la concentrazione dei portatori nel silicio

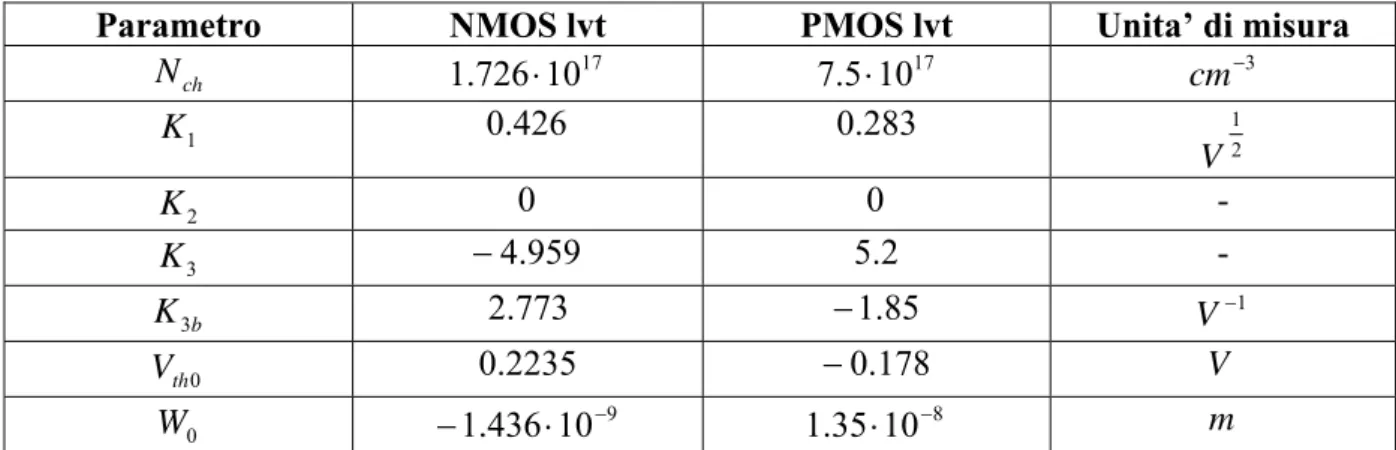

intrinseco. I parametri che variano a seconda del tipo transistore lvt sono riportati nella tabella1.

Parametro NMOS lvt PMOS lvt Unita’ di misura ch N 1.726⋅1017 7.5⋅1017 −3 cm 1 K 0.426 0.283 2 1 V 2 K 0 0 - 3 K −4.959 5.2 - b K3 2.773 −1.85 V−1 0 th V 0.2235 −0.178 V 0 W −1.436⋅10−9 1.35⋅10−8 m

Tabella 2.1: Parametri per la determinazione della tensione di soglia dei MOSFET lvt.

Mobilità

Per la mobilità utilizzeremo l’espressione mobMod=2 del manuale:

(

)

2 0 1 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + + = ox gst b ox gst bseff c a eff T V U T V V U U μ μ (2.3)dove Vgst =Vgs −Vthè la tensione di ‘overdrive’.

ponendo

(

)

ox bseff c a T V U U + =θ e trascurando il termine dipendente da 2

gst

V per piccoli overdrive

si ottiene:

(

)

th gs eff V V − + = θ μ μ 1 0 (2.4) I parametri U per NMOS e PMOS lvt sono riportati nella tabella 2. iParametro NMOS lvt PMOS lvt Unità di misura a U −460⋅10−12 1.2⋅10−10 m/V b U 1.8⋅10−18 1.04⋅10−18 m2/V2 c U −260⋅10−12 −9⋅10−11 m/V2 Tabella 2.2: Parametri per la determinazione della mobilità dei MOSFET lvt.

Velocità dei portatori di carica

L’equazione usata dal modello per la velocità dei portatori di carica è la seguente:

sat E E< ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + = sat eff E E E v 1 μ (2.5) sat E E> vsat v= sat

E corrisponde al campo elettrico al quale la velocità dei portatori satura:

eff sat sat v E μ 2 = (2.6) sat

v vale 163000 m/s per gli NMOS e 83200 m/s per i PMOS.

Corrente di drain in zona triodo

L’espressione approssimata della corrente di drain in zona triodo è stata ricavata

L E V V A V L W c R V V A V L E V L W c I sat ds ds bulk gst ox eff ds ds ds bulk gst sat ds ox eff ds + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − + = 1 2 1 2 1 1 μ μ (2.7) ds

R è la resistenza tra drain e source , 0 0.0177 2

m F t c ox ox ox = = ε ε (εox =3.9, m F 12 0 8.85 10 − ⋅ = ε ).

Considerando Rds=0, EsatL>>Vds, e sostituendo l’espressione diμeff(2.4), l’espressione di

ds I diventa:

(

)

th gs ds ds bulk th gs ds V V V V A V V K I − + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − − = θ 1 2 (2.8) L W c K =μ0 ox bulkA tiene conto del ‘bulk charge effect’ e vale:

bseff eff dep j eff gsteff gs dep j eff eff bseff s ox KetaV B W B X X Leff L V A X X L L A V K Abulk + ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ + + ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + − + − Φ + = 1 1 . . 2 1 2 2 1 1 ' 0 2 0 1

(

)

ch bseff s si dep qN V X = 2ε Φ −I parametri sperimentali della relazione sono riportati nella tabella seguente:

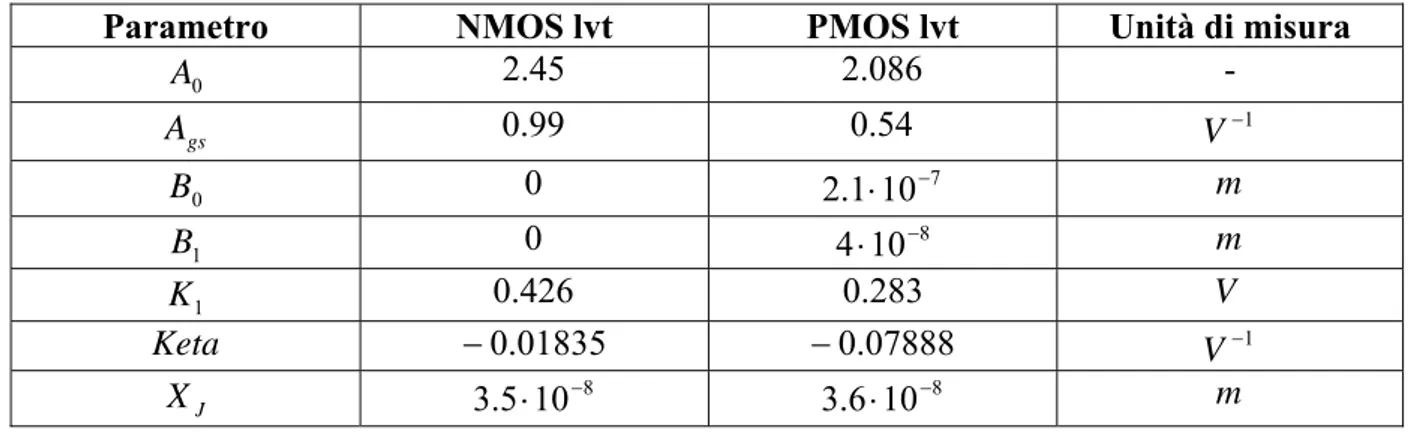

Parametro NMOS lvt PMOS lvt Unità di misura

0 A 2.45 2.086 - gs A 0.99 0.54 V−1 0 B 0 2.1⋅10−7 m 1 B 0 4⋅10−8 m 1 K 0.426 0.283 V Keta −0.01835 −0.07888 −1 V J X 3.5⋅10−8 3.6⋅10−8 m

Tabella 2.3: Parametri per la determinazione di Abulk dei MOSFET lvt.

Per gli NMOS Abulk è circa unitario per lunghezze piccole. Nelle figure 2.1,2.2, si mostrano

gli andamenti di Abulk perL=10μm e Vbseff =0.

0

50

100

150

200

1.1264

1.1266

1.1268

1.1270

1.1272

1.1274

1.1276

1.1278

Ab

u

lk

Vgs-Vth (mV)

0

50

100

150

200

1.06

1.08

1.10

1.12

1.14

1.16

1.18

1.20

1.22

1.24

1.26

W=10

μm

W=1

μm

W=0.12

μm

Ab

u

lk

Vgs-Vth (mV)

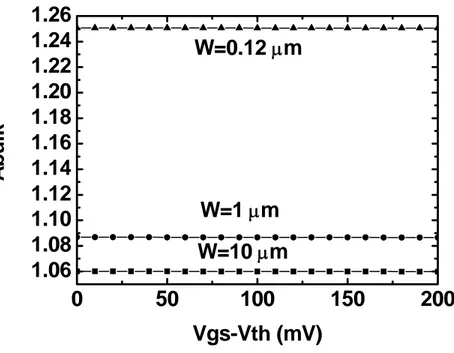

Figura 2.2: Abulk di un PMOS lvt con L=10 μm e varie larghezze.

Corrente di drain in saturazione

Anche in questo caso, consideremo il caso Rds =0, quindi l’espressione della corrente di

drain in saturazione risulta:

Ids =WCox

(

Vgst −AbulkVdsat)

vsat (2.10) con:(

(

)

)

th gs sat bulk th gs sat dsat V V L E A V V L E V − + − = (2.11) eff sat sat v E μ 2 =dipendente da V tramite un coefficiente ds λ :

Ids =Wcoxvsat

(

Vgst −AbulkVdsat)

(

1+λVds)

(2.12)L’andamento di Vdsat è mostrato in figura 2.3.

0

50

100

150

200

0

50

100

150

200

Vdsat (mV)

Vgs-Vth (mV)

Figura 2.3: Vdsat di un NMOS lvt con L=10 μm, W=0.12 μm.

Corrente sottosoglia

L’espressione della corrente di drain sottosoglia riportata dal BSIM3V3 è:

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − = t off th gs t ds s ds nv V V V v V I I 0 1 exp exp (2.13)

mV q

KT

vt = =26 è la tensione termica per T =298.15K, Voff ≈−0.1V e’ la tensione di

offset e determina la corrente di drain per Vgs=0.

s ch si t s N q v L W I Φ = 2 2 0 0 ε μ , 1η > è un

fattore di non idealità.

Se Vds ≥100mV , exp ⎟⎟→0 ⎠ ⎞ ⎜⎜ ⎝ ⎛ − t ds v V , quindi: ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − = t off th gs s ds nv V V V I I 0exp (2.14)

Transconduttanza

La transconduttanza è espressa da k Vds gs ds m V I g = ∂ ∂ = .Sostituendo la (2.11) nella (2.10) e derivando:

(

)

2 2 2 gst sat bulk gst gst sat bulk sat ox m V L E A V LV E A v WC g + + = (2.15)Dipendenza delle grandezze dalla temperatura

Vediamo adesso quali sono le grandezze che dipendono dalla temperatura e in che modo:

• Tensione di soglia

( )

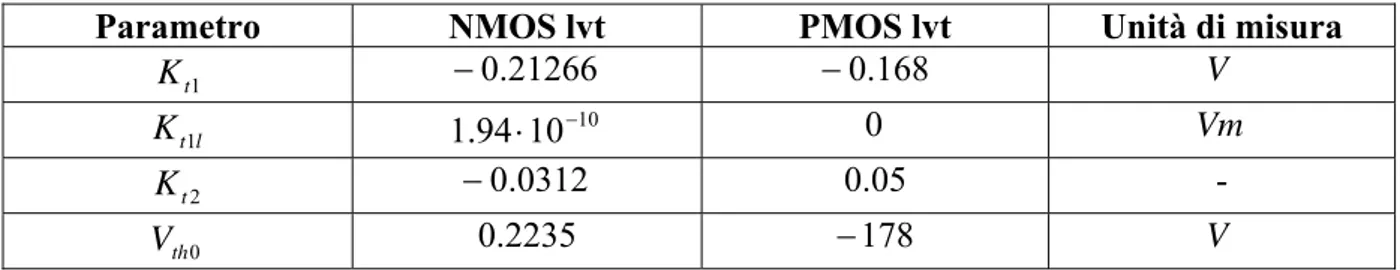

⎟⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + + ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + = t bseff eff l t t th th K V L K K T T V T V 1 1 2 0 0 1 (2.16)dove i parametri sono quelli della tabella 2.4

Parametro NMOS lvt PMOS lvt Unità di misura

1 t K −0.21266 −0.168 V l t K1 1.94⋅10−10 0 Vm 2 t K −0.0312 0.05 - 0 th V 0.2235 −178 V

Tabella 2.4: Parametri per la determinazione della dipendenza della tensione di soglia dalla temperatura.

• Mobilità

( )

ute T T T ⎟⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ = 0 0 μ μ (2.17) 8036 . 1 − = uten ; utep=−0.622• Velocità di saturazione dei portatori di carica

⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − − = 1 0 0 T T A v vsat sat T (2.18) s m ATn =32600 ; s m ATp =16000

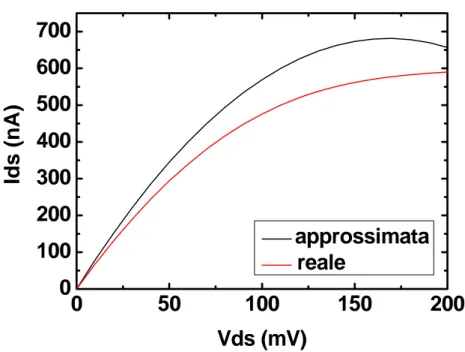

Confronto tra le caratteristiche reali e quelle approssimate

Le caratteristiche reali sono state ricavate dal simulatore, importate in matlab e confrontate con quelle approssimate. I risultati ottenuti sono quelli mostrati nelle figure 2.4÷2.19. Le caratteristiche sono state graficate per Vgs=0.3V, Vgs=0.4V , per dispositivi nlvt con

dato dal valore approssimato di Vdssat =Vgs −Vth. Le tensioni di soglia, calcolate con la (2.2),

sono Vth1 ≈150mV, Vth2 ≈210mV.

Zona triodo

L’espressione che utilizza il simulatore per la corrente di drain in zona triodo e’ la (2.8), in matlab e’ stata utilizzata quella approssimata (2.9).

0

20

40

60

80

100 120 140

0

10

20

30

40

50

Ids

(nA)

Vds (mV)

approssimata

reale

0

20

40

60

80

100

0

20

40

60

80

100

120

140

160

Ids (nA)

Vds (mV)

approssimata

reale

Figura 2.5: Corrente di drain in zona triodo per Vgs=0.3 V, L=10 μm, W=1 μm.

0

50

100

150

200

250

0

20

40

60

80

100

120

140

Ids

(nA)

Vds (mV)

approssimata

reale

0

50

100

150

200

0

100

200

300

400

500

600

700

Ids (nA)

Vds (mV)

approssimata

reale

Figura 2.7: Corrente di drain in zona triodo per Vgs=0.4 V, L=10 μm, W=1 μm.

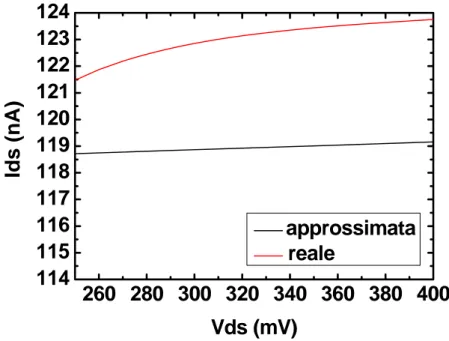

Saturazione

L’espressione utilizzata dal simulatore e’ la (2.6.11) del manuale BSIM3V3, quella approssimata la (2.12) con i valori di Vdsat e di vsat dati dalle (2.11).

150

200

250

300

350

400

41

42

43

44

45

46

47

48

49

Ids (nA)

Vds (mV)

approssimata

reale

Figura 2.8: Corrente di drain in saturazione per Vgs=0.3 V, L=10 μm, W=0.12 μm.200

250

300

350

400

140

145

150

155

160

165

170

Ids (nA)

Vds (mV)

approssimata

reale

260 280 300 320 340 360 380 400

114

115

116

117

118

119

120

121

122

123

124

Ids (nA)

Vds (mV)

approssimata

reale

Figura 2.10: Corrente di drain in saturazione per Vgs=0.4 V, L=10 μm, W=0.12 μm.

200

250

300

350

400

560

580

600

620

640

660

680

700

Ids

(nA

)

Vds (mV)

approssimata

reale

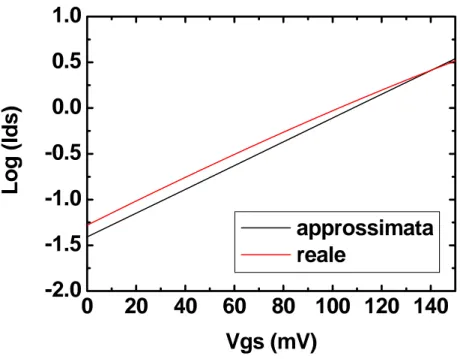

Sottosoglia

La corrente sottosoglia è stata calcolata con Vds=0.2V per dispositivi nlvt con

m

L=10μ , W1 =0.12μm, W2 =1μm. Il grafico è stato normalizzato ad 1 nA e tracciato in scala semilogaritmica. L’espressione reale e’la (2.13), quella approssimata la (2.14).

0

20

40

60

80 100 120 140

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

Log (

Ids)

Vgs (mV)

approssimata

reale

0

50

100

150

200

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

1.5

2.0

Log (

Ids)

Vgs (mV)

approssimata

reale

Figura 2.13: Corrente sottosoglia per Vds=0.2 V, L=10 μm, W=1 μm.

Transcaratteristica

Il confronto tra l’andamento reale e quello approssimato è stato ottenuto utilizzato l’espressione della corrente in zona triodo per l’intervallo di V per cui gs Vds <Vgs −Vth quella in saturazione per l’intervallo di V per cui gs Vds >Vgs −Vth. In saturazione, la transcaratteristica è stata normalizzata ad 1 nA e rappresentata in scala semilogaritmica.

160

200

240

280

320

-1

0

1

2

3

Log (Ids)

Vgs (mV)

approssimata

reale

Figura 2.14: Transcaratteristica in saturazione per Vds=0.2 V, L=10 μm, W=0.12 μm.

220

260

300

340

380

0

1

2

3

4

Log (Ids)

Vgs (mV)

approssimata

reale

360 380 400 420 440 460 480 500

60

80

100

120

140

160

180

200

220

Ids (nA)

Vgs (mV)

approssimata

reale

Figura 2.16: Transcaratteristica in zona triodo per Vds=0.2 V, L=10 μm, W=0.12 μm.

420

440

460

480

500

600

700

800

900

1000

1100

1200

1300

1400

Ids (nA)

Vgs (mV)

approssimata

reale

Transconduttanza

La trasconduttanza e’ espressa da

k Vds gs ds m V I g = ∂ ∂ = .

160

200

240

280

320

0

100

200

300

400

500

600

700

800

gm

(

nS)

Vgs (mV)

approssimata

reale

Figura 2.18: Transconduttanza per Vds=0.2 V, L=10 μm, W=0.12 μm.

0

1000

2000

3000

4000

5000

6000

7000

gm (nS)

approssimata

reale

Analisi dei risultati

Nell’analisi dei risultati, l’approssimazione effettuata sarà ritenuta valida quando l’errore relativo percentuale introdotto risulta minore del 20%. L’errore relativo percentuale è stato calcolato come: (2.19) 100 % ⋅ − = sim sim app X X X err

dove Xapp è la quantità approssimata, Xsim quella simulata in Cadence. L’errore introdotto

nell’approssimazione in zona triodo e in saturazione e’ minore del 20% già per larghezze minime, lo stesso vale per la transcaratteristica in zona triodo. Per la transcaratteristica in saturazione, per la transconduttanza e la corrente sottosoglia invece l’errore e’ minore del 20% solo per intervalli limitati della V . gs