3. La scheda di sviluppo e la partizione

del progetto.

3.1. Introduzione.

Dalle specifiche definite nel capitolo precedente deriva che la scheda di sviluppo per il Data-Processing deve avere le seguenti caratteristiche:

• Una grande disponibilità di logica programmabile, per implementare soprattutto contatori e registri di ausilio.

• Una buona capacità di elaborazione aritmetica, utile alla generazione della sinusoide e al calcolo del segnale di curvatura, che comprende una operazione di divisione aritmetica.

• La possibilità di gestire il protocollo di comunicazione IEEE1394 (Firewire).

• Una notevole quantità di memoria, in cui creare strutture nelle quali inserire i dati da comunicare al computer remoto, in modo da poter garantire che nessun dato vada perso in eventuali intervalli di tempo in cui il computer non riesca ad acquisire in tempo reale.

Queste necessità hanno portato alla scelta di utilizzare, come cuore della Data-Processing board, una scheda assemblata e venduta dalla ditta tedesca Orsys, la C6713Compac, sulla quale implementare la maggior parte delle funzionalità richieste. Essa infatti risponde alle aspettative sopra elencate in quanto dotata di un elaboratore DSP, di memorie, di due porte firewire e di logica programmabile.

board, per questo sono state previste altre schede ausiliarie, ad essa connesse. La prima è di esclusivo supporto alla C6713, per quel che concerne l’alimentazione e la comunicazione seriale, le altre costituiscono l’interfaccia con la Detection Board e la membrana per focalizzare il fronte luminoso incidente. L’unione di queste schede, costituirà l’intero sistema di Data-Processing. Queste schede di ausilio saranno brevemente descritte a livello funzionale nel terzo paragrafo. Infine nel quarto ed ultimo paragrafo si effettuerà la partizione di massima del progetto della Data-Processing Board prima tra hardware e software, quindi tra le varie schede hardware ed infine tra le risorse disponibili all’interno della scheda Orsys C6713 Compact.

3.2.

La scheda Orsys Micro-Line

®C6713

Compact

Questa scheda assemblata e venduta dalla ditta tedesca Orsys è una scheda di elaborazione dati, basata su DSP, ad elevate prestazioni e monta, in particolare:

• Un FPGA Xilinx Virtex-II dalla complessità di 1Mgate, sulla quale implementare le funzioni logiche programmabili.

• Un DSP floating point Texas Instruments TMS320C6713, con clock di 225MHz, con grande potenza di calcolo (1800MIPS o 1350MFLOPS), e 256k di RAM interna.

• Un chipset per la comunicazione via IEEE1394, che gestisce due porte Firewire.

• Una gran quantità di memoria esterna, sotto forma di Flash EPROM (32Mbyte, organizzata a 16 bit) e SDRAM (64Mbyte, organizzata a 32 bit).

Inoltre la scheda può vantare dimensioni contenute, che ne agevolano l’inserimento nei diversi sistemi di osservazione astronomica.

Figura 3.1: la scheda Orsys C6713Compact. Vedi bibliografia [60].

Per lo sviluppo, il debug e la programmazione della scheda sono stati necessari come minimi tool aggiuntivi:

• Un PC per lo sviluppo.

• Un emulatore JTAG, come lo XDS510PP Plus della Spectrum Digital Inc. da noi scelto.

• Il sistema di sviluppo Code Composer Studio distribuito dalla Texsas Instruments Inc. , per la programmazione del software del DSP.

• Il software Project Navigator distribuito dalla Xilinx per la programmazione dello FPGA.

• Il software Active-HDL distribuito dalla ALDEC Inc. per le simulazioni timing del progetto.

3.2.1.

Struttura hardware e connettori

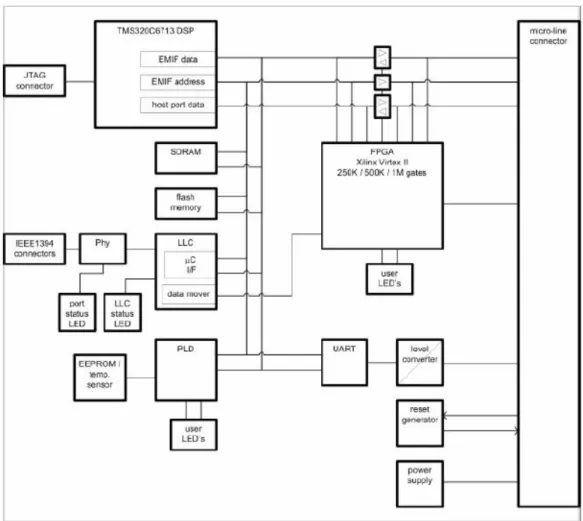

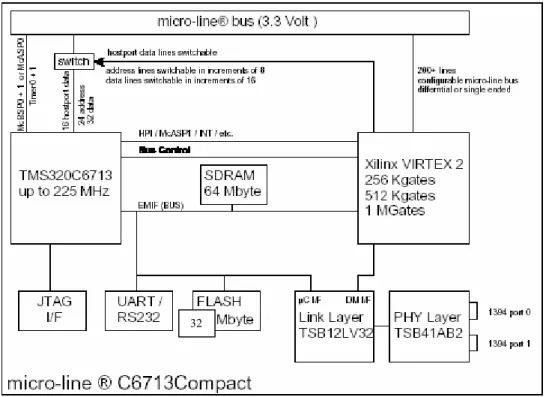

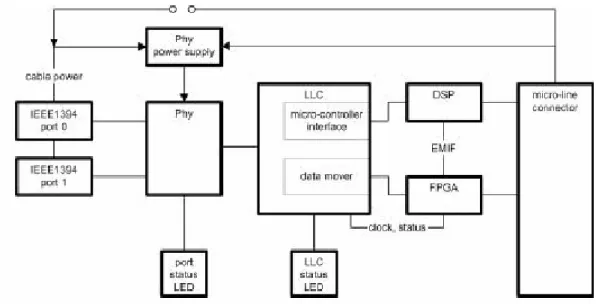

Un diagramma a blocchi della struttura complessiva della scheda è mostrato in figura 3.2, mentre nelle successive immagini, 3.3 e 3.4, sono mostrate le proiezioni schematiche delle due facce della board.

Figura 3.2: Diagramma a blocchi sintetico della scheda Orsys C6713Compact.

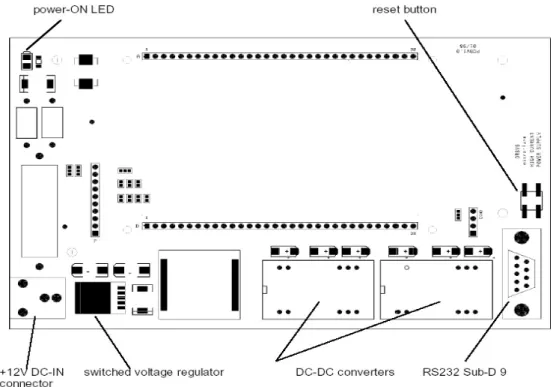

Figura 3.3: Lato componenti della scheda Orsys C6713Compact.

3.2.1.1. Connettore micro-line®

Il connettore principale della board è il micro-line®, diviso a sua volta in 6 gruppi di 32 pin, 2 di 8 pin e 3 di 4 pin. Esso è realizzato in modo da poter impilare l’una sull’altra, molto facilmente, schede dotate dello stesso standard: è il caso, ad esempio, della power supply board utilizzata, che viene posta immediatamente al di sotto della C6713, alla quale è connessa tramite il connettore micro-line.

In generale i segnali legati al connettore micro-line possono essere suddivisi in tre gruppi principali:

• Power supply.

• Segnali di interfaccia col DSP o con la board. • Segnali direttamente legati allo FPGA.

Esiste uno standard micro-line che attribuisce ad ogni pin del connettore un compito ed un collegamento specifico, tuttavia queste connessioni possono essere quasi completamente riconfigurate dall’utente, secondo le esigenze specifiche. Ad esempio, nel collegamento standard la maggior parte dei pin vengono riservati all’accesso al DSP, mentre nell’utilizzo che si farà di questa scheda per scopi astronomici gran parte dei pin dovranno essere utilizzati come ingressi diretti allo FPGA, per il conteggio dei fotoni.

3.2.1.2. Connettore JTAG

Il connettore JTAG viene usato durante lo sviluppo delle applicazioni, ed è associato alle interfacce JTAG di DSP e FPGA; pertanto è usato sia nella fase di debugging, sia per il download di applicazioni nel DSP, sia per il salvataggio nella

L’interfaccia JTAG del DSP è utilizzabile assieme ad un emulatore JTAG e al sistema di sviluppo Code Composer Studio.

Per quel che riguarda lo FPGA, durante lo sviluppo del progetto è possibile tramite il JTAG scaricare velocemente il codice in essa, per testarlo direttamente. Nell’utilizzo finale dell’applicazione il codice sarà invece salvato nella memoria flash, e caricato sullo FPGA tramite il DSP.

3.2.1.3. Connettore IEEE1394

La scheda C6713Compact ha due connettori IEEE1394, che possono essere usati tramite cavi standard a 6 pin. Nell’applicazione legata al progetto SPADA tale interfaccia permetterà la comunicazione con l’host computer, sia in upload sia in download.

Appare importante anche il fatto che vi siano due connettori IEEE1394, e non uno solo. Ciò permetterà infatti, in futuro, di poter inserire facilmente la scheda in una rete Firewire più complessa del solo nucleo host computer e Data Processing Board, nel caso ve ne sia l’esigenza.

3.2.2.

Componenti Hardware e Interfacce

3.2.2.1. FPGA

particolare esiste la possibilità di legare molti dei pin di ingresso/uscita dello FPGA a quelli del connettore micro-line e all’interfaccia del DSP.

Più in dettaglio lo FPGA ha accesso al:

• DSP EMIF (External Memory InterFace): bus dati, bus indirizzi, segnali di controllo.

• Pin del connettore micro-line.

• Data mover port del Link Layer Controller (LLC) per l’interfaccia IEEE1394.

• Periferiche del DSP: HPI, McASP, GPIO ecc. • Bus driver control (data, address, HPI data). • Interfaccia JTAG.

• 2 interruzioni del DSP, la INT_4 e la INT_5. • 2 LED.

La figura 3.5 mostra uno schema di alcune possibili connessioni per lo FPGA; si noti che sono in commercio anche schede C6713Compact con FPGA di complessità minore di 1MGate, e in figura sono evidenziate le possibilità di connessione per ciascuna versione della board: naturalmente, la maggiore versatilità si ottiene con le schede che montano FPGA più complesse. Proprio questa alta flessibilità, assieme alla possibilità di avere più logica programmabile disponibile, ha portato alla scelta della versione della C6713Compact con FPGA più complessa.

Gli utilizzi indicati in parentesi accanto ai gruppi di pin del connettore micro-line sono quelli definiti dallo standard, ma completamente riconfigurabili.

Figura 3.5: possibilità principali di connessione per lo FPGA

3.2.2.2. Interfaccia IEEE1394

La C6713Compact utilizza come chipset per l’interfaccia IEEE1394 il Link Layer Controller (LLC) Texas Instruments TSB12LV32, ed il Physical layer transceiver (Phy) TSB41AB2.

Il chipset (il cui schema è mostrato nella figura 3.6) contempla:

• Una comunicazione ad un massimo di 400Mbit/s, in accordo col protocollo IEEE1394.

• Due vie indipendenti all’interno dell’LLC: la “micro-controller interface”, collegata al DSP, e la “data mover port”, collegata allo FPGA.

• Due connettori di uscita distinti, previsti anche nella possibilità di connessione all’interno di reti senza l’utilizzo di hub.

Figura 3.6:Schema a blocchi del chipset per la comunicazione IEEE1394.

Per le operazioni IEEE1394, un software per la transazione dati gira sul DSP e accede all’LLC attraverso la micro-controller interface. Alternativamente tramite la via “data mover”, connessa al solo FPGA, si può dirigere lo stream di dati verso il DSP o verso il connettore micro-line attraverso una programmazione dedicata effettuata dall’utente. Il Link Layer Controller può generare interruzioni, che sono portate a destinazione attraverso il PLD.

L’alimentazione del Physical layer transceiver, diversa da quella del resto della scheda, è fornita dalla power supply board. Alternativamente è possibile configurare la scheda in modo che la stessa connessione IEEE1394 provveda a tale alimentazione.

3.2.2.3. Memoria esterna (SDRAM)

La C6713Compact utilizza una memoria esterna SDRAM da 64Mbyte, organizzata a 32 bit. Essa costituisce un valido appoggio per la memorizzazione dei dati, soprattutto in applicazioni di imaging, come quelle di carattere astronomico che si vogliono realizzare.

L’accesso alla memoria esterna avviene tramite l’EMIF clock, a 90MHz. Paragonata alla memoria interna del DSP, questa appare quindi più lenta, inoltre la stessa EMIF può essere condivisa con altre risorse, come la UART. Quindi, per quel che riguarda l’utilizzo del DSP in operazioni che richiedono elevate velocità, è consigliabile l’uso della memoria interna sia come registro d’appoggio per i dati, sia per il salvataggio del codice di programma, almeno finché questo risulta possibile.

3.2.2.4. Memoria Flash

La C6713Compact utilizza una memoria flash EEPROM Am29LV256 a 32Mbyte (organizzata a 16 bit), per la memorizzazione non volatile di codice, applicativo per il DSP e di programmazione per lo FPGA.

Al reset o all’accensione, il boot loader interno del DSP carica il primo Kbyte contenuto in memoria flash, partendo dall’indirizzo 0, e lo esegue. Normalmente in questo segmento di codice è contenuta la direttiva di effettuare un secondary boot loader, per caricare il resto dell’applicazione, solitamente molto più grande di 1 Kbyte.

La memoria flash viene logicamente suddivisa in 32 segmenti di 1Mbyte ciascuno. Essi sono accessibili in modo mutuamente esclusivo: i 5 bit più

significativi del registro FSR del PLD controllano quale segmento della memoria flash sia correntemente accessibile.

3.2.2.5. Interfaccia UART / RS-232

L’interfaccia RS-232 è realizzata tramite il dispositivo UART Texas Instruments TL16C550, connesso al line driver RS-232. Tale interfaccia è comunemente usata come forma generica di comunicazione, ad esempio per trasmettere ad un host computer risultati di misurazioni, oppure come connessione a periferiche remote. Nel caso del progetto SPADA, la RS-232 sarà un’interfaccia per la comunicazione con la Detection Board, mentre in fase di testing può risultare utile come output per le informazioni di debug.

L’interfaccia consiste nei segnali TxD (Transmit Data), RxD (Receive Data), RTS (Request To Send) e CTS (Clear To Send). Questi segnali sono disponibili anche su pin dedicati del connettore micro-line.

La UART può generare delle interruzioni che vengono mandate al PLD.

3.2.2.6. Il DSP e le sue periferiche

Il DSP utilizzato è il TMS320C6713 della Texas Instruments basato su una architettura avanzata che lo rende eccellente per applicazioni multi funzione e multi canale. Lavora a 225 MHz, svolgendo fino a 1350 milioni di operazioni floating-point per secondo (MFLOPS), o 1800 milioni di istruzioni per secondo (MIPS).

La C6713 usa una architettura basata su cache a due livelli il primo di 4K-Byte e il secondo 256K-Byte di cui 192K Bytes utilizzabili come mapped SRAM.

due Multichannel Audio Serial Ports (McASPs), due Multichannel Buffered Serial Ports (McBSPs), due bus Inter-Integrated Circuit (I2C), un modulo dedicato al

General-Purpose Input/Output (GPIO), due timers, una host-port interface (HPI), un generatore di clock con oscillatore e PLL e una external memory interface (EMIF) capace di interfacciarsi alla SDRAM e a tutte le altre periferiche.

Figura 3.7:Diagramma funzionale a blocchi del processore TMS320C6713. Le principali periferiche verranno ora descritte brevemente: approfondimenti sul loro funzionamento si possono reperire nella documentazione Texas Instruments (vedi bibliografia [43] e [45]).

Bisogna fare particolare attenzione, quando si usano contemporaneamente più periferiche, al fatto che alcune di esse potrebbero condividere dei pin.

3.2.2.6.1. Generatore di clock

Il DSP ha al suo interno un generatore di clock che per mezzo di un oscillatore e di un PLL può effettuare opportune moltiplicazioni e divisioni per fornire specifici clock come quello per il funzionamento dell’EMIF o quello stesso del processore.

3.2.2.6.2. Multi-channel Audio Serial Ports

Le periferiche McASP sono due porte seriali ottimizzate per la gestione di applicazioni audio, anche multi canale. Esse sono contraddistinte dalle sigle McASP0 e McASP1. McASP0 è completamente connessa al bus micro-line, tranne che per la linea AMUTEIN0, connessa allo FPGA. McASP1 è invece connessa al solo FPGA. Si noti come la porta McASP0 possa essere utile in fase di generazione della sinusoide in banda audio, nell’ambito del progetto SPADA. Per ulteriori dettagli vedi bibliografia [50].

3.2.2.6.3. External Memory Interface (EMIF)

L’EMIF è l’interfaccia principale verso tutte le periferiche. Essa ha accesso a: • Memoria esterna (SDRAM e flash)

• Periferiche on-board: UART, LLC e PLD. • Tutte le periferiche interne del DSP

• Connettore micro-line attraverso bus driver.

3.2.2.6.4. Integrated Circuit (I2C) Interface

Le interfacce I2C del DSP sono due: esse possono essere usate per accedere a

periferiche quali un sensore di temperatura presente anch’esso sulla scheda, EEPROMS, convertitori D/A e A/D. Sulla C6713 è tuttavia disponibile una sola delle due interfacce I2C poiché l’altra è dedicata al GPIO.

3.2.2.6.5. General Purpose Input/Output Peripheral (GPIO)

Sulla C6713Compact, l’uso di tale interfaccia è sconsigliato, in quanto non direttamente connessa al bus micro-line. Tuttavia possono essere utilizzati, come pin dell’interfaccia GPIO, alcuni pin normalmente dedicati agli External Flags (XF), ai McBSP e alle connessioni con pin liberi dello FPGA.

3.2.2.6.6. Multi-Channel Buffered Serial Ports

Vi sono due McBSP indipendenti: ogni porta può comunicare in full duplex, con un data stream continuo fino a 75Mbps. Esse possono essere usate, ad esempio, per la comunicazione tra due processori, o per la connessione con altre periferiche, come codec e convertitori A/D e D/A. Questa porta adotta lo standard delle interfacce seriali sincrone delle famiglie di DSP Texas Instruments TMS320 C2000, C3xxx e C5000, e può essere programmata per divenire compatibile con ogni altra interfaccia sincrona seriale. Essa è costituita dai segnali DRx (data receive), DXx (data transmit), CLKRx (clock receive), CLKXx (clock transmit),

Di default, i segnali delle porte McBSP sono connessi al bus micro-line.

3.2.2.6.7. Timers

Il DSP TMS320C6713 contiene 2 timer indipendenti, a 32 bit. Ognuno di essi ha un pin di ingresso ed uno di uscita. Per maggiore versatilità d’utilizzo essi possono ricevere il clock da una sorgente esterna o da quella interna.

3.2.2.6.8. Host Port Interface (HPI)

Il DSP TMS320C6713 è dotato di una host port a 16 bit, che può essere usata da un host processor per avere accesso diretto alla memoria del DSP: in questo caso l’host accede come master ed il DSP viene visto come slave. L’host processor ed il DSP possono così scambiare dati sia attraverso la memoria interna del DSP, sia attraverso la memoria montata sulla board; l’host avrà inoltre accesso anche ai registri delle periferiche mappati in memoria. La connessione tra l’host e lo spazio di memoria del DSP è assicurata da un meccanismo DMA.

3.2.2.6.9. EDMA

Il DSP TMS320C6713 è dotato di un controller enhanced DMA (EDMA). Esso può essere usato per trasferire dati tra due locazioni qualunque nello spazio di memoria della C6713Compact. Tali trasferimenti dati possono essere sincronizzati dal software o da eventi generati internamente o esternamente alla

operazioni DMA possono essere concatenate, cioè la fine di ogni trasferimento di dati può dare inizio al successivo: ciò costituisce un potente e flessibile modo di svolgere operazioni senza l’intervento della CPU.

Il meccanismo DMA è quello che consente le maggiori prestazioni di velocità all’interno della scheda: il massimo throughput è 225 Mwords per secondo.

3.2.2.7. PLD

Il PLD costituisce la “glue logic” della board: esso permette infatti, tramite i suoi registri, di accedere alle varie parti hardware della scheda e di configurarne alcune opzioni.

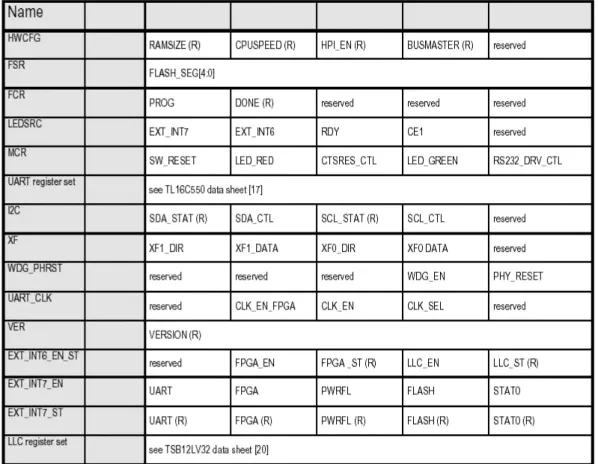

Figura 3.9: i principali registri del PLD.

Fra i registri più importanti, oltre al già citato FSR, è utile evidenziare anche i seguenti:

• HardWare ConFiGuration register (HWCFG): contiene informazioni sulle impostazioni hardware della board: dimensioni della memoria RAM, velocità massima della CPU, abilitazione dell’interfaccia HPI del DSP, funzionamento della C6713Compact in modo master o slave.

• FPGA Control Register (FCR): viene usato dalle applicazioni per caricare codice nello FPGA.

• Module Control Register (MCR): contiene, fra gli altri, un bit per il reset software della board, uno per il controllo dello stato del LED rosso ed uno per quello del LED verde.

• WatchDoG enable and Phy ReSeT register (WDG_PHRST): il bit numero 4, posto ad 1, abilita il meccanismo di watchdog. Il bit numero 3 è usato per resettare il Physical layer transceiver.

• Version Register (VERSION): contiene il codice identificativo della versione della board.

Altri registri controllano varie altre impostazioni possibili per la scheda, tra questi molto importante è quello riguardante il routing dei segnali di interruzione che permettono ai dispositivi della scheda o ad eventuali periferiche esterne di interrompere il programma corrente del DSP e saltare ad una routine di servizio dedicata all’interruzione.

Sulla C6713Compact, due linee di interruzione (EXT_INT6 e EXT_INT7) sono gestite dal PLD e due (EXT_INT4 e EXT_INT5) dallo FPGA. Nella tabella e nella figura 3.10 sono mostrate le possibili fonti di interruzione provenienti dal PLD.

Source DSP interrupt line

LLC interrupt EXT_INT6

LLC STAT0 line EXT_INT7

UART interruptus EXT_INT7

Flash memory ready condition EXT_INT7 FPGA I/O power fail condition EXT_INT7

Figura 3.10: Routing delle interruzioni sulla C6713Compact.

3.2.2.8. EEPROM seriale

E’ presente sulla scheda anche una memoria EEPROM seriale di 256 byte, integrata col sensore di temperatura della board: essa può utilmente contenere il serial number e altri parametri. I driver software per questa memoria sono forniti con la documentazione della C6713Compact. La EEPROM è connessa al PLD tramite un’interfaccia I2C, e vi si può accedere tramite l’ I2C bus control register.

3.2.2.9. Sensore di temperatura

La scheda C6713Compact contiene un sensore che permette di misurare la sua temperatura durante l’utilizzo, con un range tra -55 e +125 gradi Celsius e la risoluzione di un grado. Se la board opera in un ambiente in cui è esposta ad alte temperature, il sensore può divenire indispensabile ad evitare condizioni di rischio. La temperatura interna della CPU è al massimo di circa 15 gradi superiore

a quella misurata dal sensore. I driver software per il sensore sono forniti con la documentazione della C6713Compact.

Il sensore è connesso al PLD tramite l’interfaccia I2C e vi si può accedere tramite

il bus control register.

3.2.2.10. Generatore di reset e Watchdog

Il generatore di reset della C6713Compact genera un impulso di reset nel caso si presentino uno o più dei seguenti casi:

• Accensione.

• Reset software (attraverso il module control register). • Pin /RESETIN attivo.

• Discesa di una tensione d’alimentazione sotto il limite minimo. • Azzeramento del Watchdog timer del reset generator, se attivo. • Linea CTS attiva e configurata come reset function.

Durante l’impulso di reset vengono rese attive le due uscite RESETOUT e /RESETOUT. Il generatore di reset è dotato, come accennato, di un timer di Watchdog che causa un reset della scheda se non è periodicamente, a sua volta, resettato dal software. Questo meccanismo può essere utilmente sfruttato nella comunicazione tra la Data-Processing Board e la Detection Board come meccanismo di sicurezza.

Il Watchdog Timer è di default disabilitato: per attivarlo basterà porre ad 1 il bit numero 4 del registro di configurazione WDG_PHRST del PLD.

3.2.2.11. External Flags (XF signals)

La scheda C6713Compact presenta due pin dedicati ad applicazioni generiche, che possono essere impostati come ingressi od uscite. In entrambi i casi, la lettura di tali segnali, o la loro scrittura, avviene tramite il registro XF del PLD.

Esempi di applicazione classici riguardano la gestione di una linea di controllo verso un dispositivo esterno: se configurati come uscite daranno ad esso dei segnali di sincronizzazione o controllo, se configurati come ingressi ne rileveranno lo stato.

3.2.2.12. LED

Sulla scheda C6713Compact sono montati sei LED, suddivisi in tre gruppi: • Due LED programmabili dall’utente, controllati dal PLD, che possono

essere utilizzati dalle applicazioni software per mostrare determinati eventi o stati.

• Due LED programmabili dall’utente controllati dallo FPGA, con funzioni definite dal design dello FPGA stesso.

• Due LED di stato legati all’interfaccia IEEE1394: il primo è giallo e si accende se il Phy è correttamente alimentato e connesso ad un'altra periferica IEEE1394; il secondo è verde e di default indica che nel registro FIFO di ricezione, all’interno del LLC, sono presenti dei dati da acquisire.

3.3. Schede

ausiliarie.

Per quanto la scheda vista sia molto potente non tutte le funzioni di sistema possono essere svolte da questa board, per questo sono state previste altre schede ausiliarie, ad essa connessa che sono:

• La scheda di alimentazione e comunicazione seriale di supporto alla C6713.

• La scheda dei ricevitori differenziali. • La scheda relativa alla generazione audio. • La scheda dei generici I/O.

• La scheda di back pannel e lo chassis.

L’unione di queste schede, costituirà l’intero sistema di Data-Processing. Le funzioni svolte da queste schede di ausilio sono brevemente descritte nei successivi paragrafi; per maggiori dettagli sulla loro progettazione si fa riferimento alla bibliografia [18].

3.3.1.

Scheda di alimentazione

Questa scheda è di esclusivo supporto alla C6713, per quel che concerne l’alimentazione e la comunicazione seriale. La Power Supply (PS) Board, è costruita in modo da potersi adattare, in maniera modulare, allo standard dei connettori micro-line. L’alimentazione avviene partendo dalla normale tensione di rete (230V, 50Hz), attraverso un adattatore AC/DC universale con al massimo, in uscita, 12V DC e 9.6VA. A partire da tale tensione continua vengono poi prodotti, tramite un regolatore di tensione switching, i +5V necessari alla C6713Compact

C6713 sono poi generate tutte le tensioni, minori o uguali a 3.3V, necessarie al funzionamento dei diversi componenti hardware che sono in dettaglio:

• 1.26V per il core del processore DSP.

• 3.3V per la maggior parte dei circuiti digitali. • 1.5V per il core dello FPGA.

• 3.3V, 2.5V e 1.8V per le celle di I/O dello FPGA connesse al connettore micro-line. Il valore di default è 3.3V, gli altri due sono impostabili tramite una differente configurazione della scheda.

Vi è poi, a valle del regolatore che fornisce i +5V, un convertitore DC/DC che fornisce le tensioni +15V e -15V, necessarie agli integrati Physical Layer Transceiver per la comunicazione IEEE1394.

La corrente massima erogabile dall’uscita a 5V è 2.5A, molto superiore a quella richiesta dalla sola C6713Compact; del resto la Power Supply è stata pensata proprio come scheda di alimentazione per più board impilate in modo modulare, tramite il connettore standard micro-line. Nel caso della Data-Processing Board del progetto SPADA, tale sovrabbondanza di corrente disponibile potrà essere usata per alimentare gran parte dei dispositivi della scheda audio.

Figura 3.12: La Power Supply Board Orsys: principali dispositivi montati. Come funzioni aggiuntive all’alimentazione sono previste:

• Un pulsante di reset. • Un LED di power-on.

• Un connettore RS-232 SUB-D 9, collegato ad adeguati pin del connettore micro-line, che permette la comunicazione seriale con la scheda C6713Compact.

3.3.2.

Ricevitori differenziali

Questa scheda riceve i segnali provenienti dai sensori SPAD e deve compiere su questi due operazioni: la trasformazione dei segnali da differenziali a unipolari e l’abbassamento del livello di tensione massimo da 5V a 3.3V.

Figura 3.13:Collegamento della scheda dei ricevitori differenziali.

La scelta dei dispositivi in grado di svolgere entrambe le funzioni contemporaneamente, per minimizzare gli ingombri ed i consumi, è ricaduta sugli integrati della famiglia 26LV32. In particolare si è scelto il dispositivo Texas Instruments AM26LV32: esso è costituito da quattro ricevitori differenziali alimentati a 3.3V, quindi con uscite legate a tale tensione, che tuttavia possono sopportare in ingresso tensioni differenziali superiori a 5V. La massima frequenza di utilizzo garantita è di 32MHz, sufficiente al nostro caso , in cui il massimo data rate dei segnali provenienti dagli iAQC è di circa 20MHz.

Per formare la barriera di 60 ricevitori servono 15 dispositivi, a questo punto agli ingressi differenziali si portano direttamente i segnali forniti dalla Detection Board tramite i due connettori SCSI a 68 pin, mentre le uscite vengono portate al connettore micro-line della scheda Orsys tramite un innesto adeguato.

60 Scheda ricevitori differenziali Batteria di 60 ricev . differenziali. OrsysC6713 Detection Board 60 60 FPGA M i c r o l i n e S C S I

Figura 3.14: A sinistra package del dispositivo AM26LV32. A destra schema di utilizzo di un singolo dispositivo con l’uso di una delle due abilitazioni con il segnale di Gate e l’utilizzo di un condensatore per la stabilizzazione della tensione di alimentazione. Vedi anche bibliografia [58].

3.3.3.

Scheda audio

Per la generazione della sinusoide analogica si è scelto di utilizzare un sistema TDAA (True Digital Audio Amplifier), cioè un chip set totalmente digitale dedicato all’amplificazione audio. Il cuore di questa tecnologia brevettata consiste proprio nella conversione del segnale dal formato PCM, Pulse-Code Modulated, a quello PWM, Pulse-Width Modulated: in questo modo il segnale audio può essere mantenuto nel dominio digitale fino al filtro finale e ciò permette di passare agli speaker il segnale audio in alta fedeltà, senza le inevitabili distorsioni introdotte dagli amplificatori analogici.

Figura 3.15: Collegamento della scheda audio.

Abbiamo scelto di utilizzare come modulatore PCM-PWM il TAS50xx della Texas Instruments e come amplificatori in classe D adatti al segnale PWM i TAS51xx visto il costo ridotto di tali dispositivi prodotti in larga scala. Per maggiori dettagli su questi componenti si consulti la bibliografia [56] e [57].

Figura 3.16: Il sistema TDAA proposto da Texas Instruments.

La nostra specifica della frequenza di sinusoide compresa tra 1.5kHz e 3kHz rientra nella banda audio standard trattata dai normali dispositivi commerciali come i TAS50xx e i TAS51xx. Inoltre il segnale modulato PCM richiesto in ingresso dal TAS50xx è ottenibile direttamente in uscita sui piedini della Micro-line per mezzo della periferica audio McAsp del DSP.

Per maggiori dettagli sulla progettazione di questa scheda si faccia riferimento alla bibliografia [18], [55] e [59].

OrsysC6713

Sistema TDAA per la generazione della sinusoide analogica. Membrana nella cavità risonante Scheda audio DSP Mc Asp

3.3.4.

Scheda generici I/O

Questa scheda provvede alla creazione di una serie di 8 connettori SMC, per I/O di tipo generico. Questi infatti sono necessari per ricevere ad esempio i segnali di Gate In e Out e Interlock ecc. Sono stati scelti i connettori coassiali SMC per montaggio su pannello della Radiall mostrati in figura.

Figura 3.17: Connettore coassiale SMC della Radiall

Vengono inoltre utilizzati un banco di buffer sia di ingresso che di uscita per una trasmissione più sicura dei dati. Come buffer di uscita sono stati scelti i Quad Buffer (3 state) 74ABT125 della Philips, mentre come buffer di ingresso sono stati scelti i Quad Buffer (3 state) SN74LVT125D della T.I. entrambi funzionanti a bassa dissipazione e alta velocità.

3.3.5.

Back Pannel e chassis

Il committente (ESO) ha fornito uno chassis della dimensione di 19 pollici, ideale per il montaggio di apparecchiature pesanti o ingombranti, come alimentatori, induttori, trasformatore ecc. La base, i lati e il pannello superiore presentano una serie di fessure che assicurano un'adeguata ventilazione e

epossidica grigio chiaro. Il pannello frontale è in alluminio anodizzato spesso 3 mm con maniglie in dotazione.

Figura 3.18: Il cassetto “rack” di 19 pollici fornito dall’ESO come chassis. All’interno vi devono alloggiare i tre alimentatori necessari alla Data-Processing Board, alla Detection Board ed ai sensori oltre alle schede suddette. A parte la scheda Orsys C6713 tutte le altre schede di ausilio sono realizzate su schede Eurocard; formato standard per essere inserite verticalmente nello chassis. E’ prevista dunque una scheda di back pannel con connettori din sul fondo della scatola che funge sostanzialmente da bus; questa scheda è formata da piste orizzontali cortocircuitate per portare i segnali a tutte le schede che vi si

Le schede disposte verticalmente si innestano sul fondo ai connettori del back pannel e frontalmente presentano i connettori da pannello che escono sullo chassis. L’unica scheda che per dimensioni non arriva sul pannello esterno è la Orsys per la quale sono da prevedere sullo chassis due asole per poter inserire i due connettori Firewire.

3.4.

La partizione del progetto.

Avendo a questo punto chiara l’intera piattaforma di sviluppo del sistema, si può procedere alla partizione del progetto della Data-Processing board tra le varie risorse a disposizione.

3.4.1.

La partizione hardware-software e tra

C6713 Compact e schede di ausilio.

Innanzi tutto la partizione tra hardware, cioè schede vere e proprie, e software del computer remoto è già stata descritta implicitamente nel capitolo 2 dove sono state affidate alla interfaccia software le sole funzioni seguenti:

• Controllo delle impostazioni dell’hardware. • Salvataggio e visualizzazione dei dati acquisiti.

• Eventuali post-elaborazioni solo di carattere statistico o diagnostico. Per quanto riguarda la partizione delle funzioni tra le cinque schede ausiliarie, essa è stata descritta in dettaglio nei paragrafi precedenti. La Power Supply board ha solo una funzione di supporto a livello di alimentazione e di alloggio del pulsante di reset e del connettore RS-232. La scheda audio è atta alla generazione

scheda dei ricevitori differenziali serve per la conversione degli impulsi di ingresso da differenziali, a +5V, ad unipolari, a 3.3V. Le schede di I/O e Back Pannel svolgono la gestione dei generici I/O e delle connessioni.

Per tutto il resto, ovviamente la maggior parte delle funzioni, ci si rivolge alla scheda C6713Compact, in quanto essa è estremamente potente e facilmente programmabile via software.

3.4.2.

La partizione tra le risorse della C6713.

Come evidenziato nel paragrafo 3.2, sulla scheda C6713Compact sono montati numerosi dispositivi. Alcuni, la cui funzione è ben definita ed univoca, come le memorie on-board, la porta di comunicazione seriale RS 232 o il chipset per la comunicazione Firewire, saranno utilizzati in ogni applicazione. Altri invece, come il DSP e lo FPGA, sono strumenti più versatili e in sede di programmazione si possono definire le funzioni da far loro implementare.

Poiché vi sono tre differenti applicazioni da realizzare, la cosa che appare più conveniente è dedicare la grande disponibilità di logica programmabile dello FPGA per implementare soprattutto contatori, registri di ausilio e le funzioni comuni alle tre applicazioni. Vengono lasciate al DSP le elaborazioni di carattere matematico e la gestione di tutte le interfacce necessarie per la configurazione e il trasferimento dei dati in tempo reale, variabili nei tre esperimenti.

Il primo passo è stato individuare, dall’analisi dei tre schemi a blocchi funzionali descritti nel capitolo due, le operazioni comuni e quelle peculiari di ciascuna applicazione.

Per quanto riguarda le operazioni comuni da affidare allo FPGA, in tutti gli esperimenti si deve:

• Ricevere dei parametri di configurazione (anche se diversi di caso in caso); si deve quindi prevedere un registro e un meccanismo di configurazione.

• Gestire i segnali di Interlock e Gate.

• Contare gli impulsi corrispondenti alle incidenze dei fotoni sui 60 rivelatori SPADA; si deve quindi prevedere una batteria di 60 contatori. • Spedirli in uscita periodicamente; si deve quindi contemplare un timer per

contare il tempo con precisione, dei registri per immagazzinare i conteggi e un meccanismo di trasferimento.

• Indicare l’eventuale saturazione di uno dei contatori.

Figura 3.19: Schema delle funzioni che si dovrà svolgere su FPGA.

In realtà anche tutte le comunicazioni per e dalla Detection Board che devono essere comunicate attraverso la porta seriale sono comuni ai tre esperimenti, ma poiché la RS 232 è un interfaccia del DSP e la nostra scheda fa solo da ponte si è deciso di svilupparle al livello del processore per eseguirle in modo più veloce ed efficiente.

FPGA

60 pad on Micro Line Input from Detection Board Gate & Interlock Parametri di Configurazione Batteria di60 contatori Banco di registri di appoggio SMC Connectors Input from and output to DSP Timer Controllo Saturazione Meccanismo di trasferimento e validazione dei dati in ingresso

Al DSP competono molte altre incombenze come:

• Il modo di sincronizzazione del conteggio: in FTI esso dipende esclusivamente dalla durata della finestra temporale, in AO vi deve essere sincronizzazione tra la sinusoide e la finestra di conteggio pari al periodo della sinusoide per un numero impostabile di volte, in LS è importante la sincronizzazione del momento di partenza del conteggio dopo un ritardo fisso generato a partire dall’impulso di trigger proveniente dal laser.

• La gestione dell’interfaccia audio McASP0 per la generazione dei campioni della sinusoide, sia nella AO che nel LS, e l’elaborazione del segnale di curvatura.

• La gestione delle memorie on board (in particolare la SDRAM per la memorizzazione temporanea dei dati di acquisizione).

• La gestione delle interruzioni di programma.

• La gestione dei trasferimenti tramite la porta seriale RS 232.

• La complessa gestione del Firewire per trasferimenti sia asincroni che isocroni che coinvolge l’intera interfaccia IEEE1394 con il Link Layer Controller e il Physical layer transceiver .

DSP

RS 232 Trasferimenti Via RS 232 Passaggio parametri di configurazione Generazione Sinusoide Via McAsp Sincronizzazione dei conteggi F P G A Gestione memorie Trasferimenti FireWire Via IEEE1394 Gestioneinterrupt GestioneEDMA

Inizializzazioni opportune Gestione EMIF Caricamento Codice FPGA IEEE 1394 Ricezione dei conteggi Fro To

• La gestione dei trasferimenti in EDMA e QDMA.

• Tutte le opportune inizializzazioni dei registri delle interfacce e delle periferiche.

• La gestione dell’EMIF e del clock dello FPGA.

• Il passaggio a FPGA dei parametri di ingresso impostabili via software (e differenti per le varie applicazioni).

• Il caricamento della struttura FPGA.

Da questi ultimi tre punti si evince che si è scelto di utilizzare la scheda C6713 nella configurazione con il DSP come master e FPGA come slave. Questa scelta risulta evidente dalla scelta delle operazioni affidate alle due unità; dove la logica programmabile risulta una struttura fissa e con compiti univoci e ripetitivi mentre al DSP sono affidati tutti i restanti compiti di gestione particolare delle interfacce e dei trasferimenti.

![Figura 3.1: la scheda Orsys C6713Compact. Vedi bibliografia [60].](https://thumb-eu.123doks.com/thumbv2/123dokorg/5659899.70998/3.892.179.753.255.598/figura-scheda-orsys-c-compact-vedi-bibliografia.webp)

![Figura 3.7:Diagramma funzionale a blocchi del processore TMS320C6713. Le principali periferiche verranno ora descritte brevemente: approfondimenti sul loro funzionamento si possono reperire nella documentazione Texas Instruments (vedi bibliografia [43]](https://thumb-eu.123doks.com/thumbv2/123dokorg/5659899.70998/13.892.178.757.362.820/funzionale-processore-periferiche-approfondimenti-funzionamento-documentazione-instruments-bibliografia.webp)