UNIVERSITA’ DEGLI STUDI DI PISA

FACOLTA’ DI INGEGNERIA CORSO DI LAUREA IN ELETTRONICA

Tesi di laurea:

Realizzazione di una libreria Standard Cell CMOS per logica

sottosoglia per trasponder RFID

Relatori:

Prof. Giuseppe Iannaccone

Prof. Bruno Neri

Prof. Stefano Di Pascoli

Ing. Giuseppe De Vita

Candidato:

Federico Fiori

Anno Accademico 2003 / 2004

Indice

Introduzione 1

Capitolo 1 6

1.1 Principio di funzionamento della logica sottosoglia ……… 7

1.2 Caratterizzazione delle diverse famiglie logiche in base ai dati ritrovati in letteratura ……… 10

Capitolo 2 18

2.1 Strumenti e regole utilizzate per la realizzazione delle simulazioni ……… 19

2.2 Logica Sub-CMOS ………... 21

2.3 Logica Sub-DTMOS ……… 31

2.4 Logica Sub-pseudo-nMOS ………... 43

2.5 Confronto tra le tre famiglie logiche ……… 50

2.5.1 Analisi di sistemi RING OSCILLATOR realizzati con porte elementari a due ingressi ………. 52

2.5.2 Analisi di sistemi RING OSCILLATOR realizzati con porte elementare a tre ingressi ……….. 57

2.5.3 Analisi di sistemi RING OSCILLATOR realizzati con porte elementari a quattro ingressi ………... 61

Capitolo 3 68

3.1 Scelte di tipo di logica per l’implementazione delle singole porte ……….. 69

3.2 Scelta risolutiva per la realizzazione di un FLIP FLOP D ………... 72

3.3 Dimensionamento delle celle elementari ………. 78

Capitolo 4 79

4.1 Flusso di progetto ………. 80

4.2 Regole seguite per la realizzazione della libreria ………. 81

4.3 Layout delle singole celle ………. 84

4.3.1 Layout dell’ INVERTER ... 85

4.3.2 Layout della porta NAND a 2 ingressi ………... 86

4.3.3 Layout della porta NAND a 3 ingressi ………... 87

4.3.4 Layout della porta NAND a 4 ingressi ………... 88

4.3.5 Layout della porta NOR a 2 ingressi ……….. 89

4.3.6 Layout della porta NOR a 3 ingressi ……….. 90

4.3.7 Layout della porta NOR a 4 ingressi ……….. 91

4.3.8 Layout della porta D FLIP FLOP ………... 92

4.4 Visione Extracted e LVS ………. 95

4.5 Simulazioni post-layout ………... 97

4.5.1 Simulazione post-layout della porta INVERTER ………... 98

4.5.2 Simulazione post-layout della porta NAND a 2 ingressi ……….. 101

4.5.3 Simulazione post-layout della porta NAND a 3 ingressi ……….. 103

4.5.4 Simulazione post-layout della porta NAND a 4 ingressi ……….. 105

4.5.6 Simulazione post-layout della porta NOR a 3 ingressi …………. 109

4.5.7 Simulazione post-layout della porta NOR a 4 ingressi …………. 111

4.5.8 Simulazione post-layout della porta FLIP FLOP D ……….. 113

4.6 Commento alle simulazioni post-layout ………. 116

4.7 Visione Abstract ………. 119

4.8 File per il software Synopsys ………. 122

Conclusioni 125

Introduzione

La necessità di minimizzare la dissipazione di potenza è un aspetto che ha sempre interessato il progettista di sistemi elettronici e tale esigenza ha assunto un’importanza sempre maggiore con l’incremento del numero di applicazioni portatili. A questa ultima categoria appartengono anche i dispositivi RFID ( Radio Frequency IDentification ) che rappresentano il motivo principale per cui abbiamo deciso di sviluppare questo lavoro di tesi.

Tali sistemi assumono un ruolo determinante nelle applicazioni per l’identificazione automatica ( Auto-ID ) in ambito industriale e in particolar modo nel campo della logistica e nei flussi di processo di produzione. Più in generale, le procedure di identificazione automatica sono utilizzate per ricavare informazioni riguardanti beni e materie in transito, ma anche per monitorare gli spostamenti di animali e persone.

Prima di entrare più nel dettaglio del lavoro di tesi, ci è sembrato interessante riportare una breve descrizione del principio di funzionamento di un sistema RFID mettendo in evidenza anche gli elementi essenziali che lo compongono [1].

Un sistema RFID è costituito essenzialmente da due elementi: il reader e il transponder di cui il primo ha lo scopo di monitorare lo spazio che lo circonda alla ricerca del secondo. Per adempiere al suo compito, il reader si compone

essenzialmente di due parti: un’unità a radiofrequenza e una di controllo come viene evidenziato in figura 1.

CONTROL

HF

interface

applicationFigura 1 Schema a blocchi di un reader di un sistema RFID

L’unità a radiofrequenza, in fase di trasmissione, modula l’informazione da trasmettere in modo che il segnale abbia un’energia tale da poter attivare il transponder e in seguito alimentarlo. Viceversa, in ricezione, deve demodulare e inviare l’informazione all’unità di controllo.

Quest’ultima ha essenzialmente il compito di colloquiare con i dispositivi a monte del reader e di controllare la correttezza della comunicazione che avviene con il transponder. Spetta inoltre all’unità di controllo la codifica e la decodifica del segnale messaggio.

Prima di descrivere il principio di funzionamento del sottosistema transponder, riportiamo in figura 2 lo schema a blocchi che ne evidenzia le caratteristiche essenziali

MATCHING NETWORK RECTIFIER MODULATOR DEMODULATOR FINITE STATE MACHINE MEMORY B-PSK MODULATOR

Figura 2 Schema a blocchi del trasponder di un sistema RFID

Questo sottosistema, che solitamente non è dotato di un’alimentazione propria, rimane inattivo fin tanto che non viene investito dal segnale trasmesso dal reader. Infatti, in seguito a questo evento, la corrente indotta ai terminali di antenna viene prelevata e mandata in ingresso al blocco rectifier modulator che ha il compito di raddrizzarla e regolarla in modo da poterla utilizzare successivamente come alimentazione per il sistema complessivo. Una volta attivo, il transponder sfrutta il segnale RF prima per ricavare il periodo del segnale di timing e quindi il messaggio trasmesso. Anche in questo caso ritroviamo una interfaccia a radiofrequenza che nel disegno di figura 2 è stata divisa in più blocchi: matching network, demodulator e B-PSK modulator.

In base alle richieste inviate dal reader, la macchina a stati comanderà opportunamente il modulatore B-PSK dopo aver letto o scritto nella memoria interna al dispositivo.

Come è stato affermato precedentemente, il transponder risulta essere, nella maggior parte dei casi, un sistema passivo. Quindi capiamo l’importanza di dover riuscire a ridurre il più possibile ogni forma di dissipazione di energia.

Di tutto il sistema precedentemente descritto, in questo lavoro di tesi abbiamo focalizzato la nostra attenzione sulla macchina a stati interna al sottosistema transponder. Più precisamente, abbiamo progettato una libreria Standard Cell che verrà utilizzata per la sua sintesi.

Tenendo conto dell’esigenza di dover ridurre il più possibile la dissipazione di energia nell’unità di tempo e che il trasponder può lavorare al limite con un clock di qualche centinaia di KHz, abbiamo effettuato una serie di ricerche in letteratura per capire quale tipo di logica convenisse utilizzare per rispondere completamente alle specifiche di progetto. In seguito allo studio effettuato, abbiamo deciso che per rispettare questi vincoli è sufficiente realizzare la libreria Standard Cell in logica sottosoglia CMOS.

Schema della tesi

Per una migliore comprensione dell’organizzazione del lavoro di tesi, abbiamo deciso di riportare un breve schema dove vengono evidenziati i vari temi che verranno affrontati nei prossimi capitoli.

Nel capitolo 1 inseriremo le motivazioni che ci hanno portato allo studio della logica sottosoglia. In particolare, dopo una breve descrizione del suo principio di funzionamento, riporteremo alcuni risultati presenti in letteratura.

Più precisamente, analizzeremo le prestazioni delle seguenti famiglie logiche:

• Sub-CMOS • Sub-DTMOS • Sub-pseudo-nMOS

Per comprendere quale famiglia logica tra quelle elencate precedentemente ci permetta di rispondere in maniera ottimale alle specifiche di progetto, eseguiremo una serie di simulazioni circuitali e riporteremo i risultati rispettivamente nei

capitolo 2 e capitolo 3. Per realizzare questo studio utilizzeremo i software

SPICE e CADENCE SPECTRE. In particolare, mediante questo ultimo, dimensioneremo le celle elementari che andranno a comporre la libreria Standard Cell.

Nel capitolo 4 passeremo quindi all’implementazione delle singole celle per ciascuna delle quali forniremo una visione schematic, symbolic, layout ed extracted che sfrutteremo per valutare la correttezza del progetto realizzato mediante LVS. Quindi forniremo la visione abstract e verilog necessarie per il PLACEMENT & ROUTING.

Per concludere, è stato creato il file di testo che serve per interfacciare la libreria Standard Cell con il programma di sintesi Synopsys.

Capitolo 1

Prima di passare alla realizzazione della libreria Standard Cell in logica sottosoglia, ci è sembrato doveroso riportare i motivi delle nostre scelte progettuali. Cominceremo questo capitolo inserendo l’espressione che lega la potenza dissipata alle grandezze fisiche del circuito.

Quindi descriveremo il principio di funzionamento dei dispositivi che lavorano in zona sottosoglia.

Infine riporteremo i dati che abbiamo ricavato dall’analisi della letteratura e che ci hanno permesso di capire le prestazioni delle diverse famiglie logiche considerate.

1.1 Principio di funzionamento della logica sottosoglia

Prima di passare alla realizzazione della libreria Standard Cell in logica sottosoglia, ci sembra interessante esprimere i motivi che ci hanno permesso di fare questa scelta.

Ricordiamo che l’obiettivo primario di questo lavoro di tesi è quello di progettare porte elementari (INVERTER, NOR, NAND, etc.) cercando di ridurre il più possibile l’energia dissipata nell’unità di tempo. Per capire come poter rispondere pienamente a questo vincolo di progetto, siamo passati ad analizzare la relazione (1.1) dove viene espresso il legame che intercorre tra la potenza e le altre grandezze fisiche del circuito

V

C

f

P

dd dd 2∝

(1.1)dove rappresenta la potenza dissipata, la capacità di ingresso della porta in esame, la frequenza di lavoro del sistema e la tensione di alimentazione. Da una prima lettura di questa equazione, appare subito evidente la dipendenza quadratica che intercorre tra la potenza dissipata e la tensione di alimentazione. Quindi una diminuzione del valore di questo ultimo parametro permetterebbe di ottenere una riduzione della perdita di energia nell’unità di tempo.

dd

P C

f Vdd

In seguito a questa ultima considerazione ci siamo resi conto che la realizzazione dei sistemi in logica sottosoglia ci permette di rispettare questo vincolo di progetto. Infatti percorrere questa strada significherebbe alimentare le

singole celle con una tensione inferiore a quella di soglia e più precisamente con valori non superiori a 0,6 V.

Un aspetto che sembra contraddire questa scelta è il fatto che le porte realizzate con questo tipo di logica utilizzano come corrente di pilotaggio quella di perdita. Per comprendere meglio quanto appena affermato e in particolare quanto seguirà nei prossimi capitoli, ci sembra opportuno riportare nell’equazione (1.2) l’espressione della corrente che scorre in un transistore ad effetto di campo quando viene alimentato con una tensione inferiore a quella di soglia [2]

⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ ⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛

−

−

−

−

=

I

V

V

V

n

V

V

V

I

t off th gs t ds S ds 01

exp

exp

(1.2)dove rappresenta la tensione di soglia e la tensione di offset che deve essere considerata ogni volta che il dispositivo si trova a lavorare nella zona di

funzionamento sottosoglia. Il termine n rappresenta il coefficiente di sub-threshold swing e risulta essere funzione della lunghezza di canale e della

densità superficiale degli stati. Inoltre, nella equazione (1.2), il termine può essere espresso mediante la relazione sotto riportata (1.3)

th V Voff so I

V

N

q

L

W

I

t s a si S 2 0 02

φ

ε

µ

=

(1.3)dove µ0 rappresenta la mobilità degli elettroni alla temperatura nominale, W e rispettivamente la larghezza e la lunghezza del canale dei transistori, la concentrazione di impurezza, L a N s φ il potenziale superficiale.

Dall’espressione (1.2), si vede come la corrente di perdita sia legata in modo esponenziale alla tensione di gate. Quindi, con una diminuzione del valore di quest’ultima, determiniamo un incremento del tempo di ritardo di commutazione e di conseguenza, tenendo conto della relazione inversa che intercorre tra tempo e frequenza, otteniamo una peggioramento delle prestazioni in termini di velocità rispetto a quando i transistori vengono fatti lavorare nella zona di forte inversione. Tale variazione, comunque, non determina alcun problema al fine della realizzazione del progetto definitivo.

Infatti, come abbiamo affermato in precedenza, siamo interessati ad ottenere frequenze di funzionamento dell’ordine di 1 MHz e al limite di qualche decina di KHz che, come verrà messo in evidenza nei prossimi capitoli, riusciremo ad ottenere senza ulteriori limitazioni.

1.2 Caratterizzazione delle diverse famiglie logiche in base ai

dati ritrovati in letteratura

L’obiettivo di questo lavoro di tesi è quello di progettare una libreria Standard Cell in logica sottosoglia che verrà utilizzata per l’implementazione della macchina a stati interna al transponder del sistema RFID. Per questo motivo abbiamo realizzato una serie di analisi in letteratura ricercando l’esistenza o meno di famiglie logiche che potessero essere utilizzate per rispondere alle specifiche di progetto.

In [3], è stato subito evidenziato il ruolo essenziale che potrebbe assumere la logica Sub-DTMOS per la realizzazione delle celle elementari. Come viene rappresentato nella figura 1.1, un dispositivo DTMOS è caratterizzato dall’avere il terminale di gate direttamente collegato a quello di bulk.

Per realizzare la logica DTMOS è necessario avere a disposizione un processo a tripla well in modo che i substrati di ciascun transistore siano isolati tra di loro.

In questo modo la tensione di substrato si modifica al variare di quella di ingresso determinando quindi una variazione della tensione di soglia per effetto Body come viene riportato nell’equazione (1.4)

⎟ ⎠ ⎞ ⎜ ⎝ ⎛

−

−

+

=

thγ

φ

S bsφ

S thV

V

V

0 (1.4)dove il termine è la tensione di soglia quando la differenza di potenziale tra il terminale di bulk e quello di source ( ) è nulla. Inoltre il termine γ rappresenta il coefficiente di effetto Body che può essere espresso come segue nell’equazione (1.5) 0 th V bs V

C

N

q

ox a siε

γ

=

2

(1.5)Inoltre il termine φs, che compare nell’equazione (1.4), viene esplicitato nella relazione (1.6) ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛

=

k

q

T

N

n

i a B S2

ln

φ

(1.6)dove il termine rappresenta la concentrazione di droganti nel silicio intrinseco, mentre la costante di Boltzmann.

i n

B

k

Dall’analisi della espressione (1.4), notiamo che la tensione di soglia diminuisce con un aumento di quella di ingresso determinando quindi, a parità di

alimentazione, un incremento della corrente rispetto al caso in cui si utilizzi la logica Sub-CMOS. Quest’utlima famiglia logica differisce da una CMOS classica solo per il fatto che i dispositivi sono alimentati con una tensione inferiore a quella di soglia.

Per evidenziare il vantaggio che si può ottenere utilizzando la logica Sub-DTMOS rispetto alla Sub-CMOS, di seguito riportiamo due grafici dove sono rappresentati il tempo di ritardo (figura 1.2) e la potenza dissipata (figura 1.3) da un INVERTER utilizzato per realizzare un sistema RING OSCILLATOR [4].

Tali simulazioni sono state eseguite con l’ausilio del simulatore SPICE utilizzando il processo tecnologico TSMC 0,35 µm a 55ْ C.

Figura 1.2: Tempo di ritardo di un inverter appartenente ad un ring oscillator in funzione della

Figura 1.3: Potenza dissipata da un inverter appartenente ad una ring oscillator in funzione della

tensione di alimentazione Vdd realizzati con la logica Sub-CMOS e Sub-DTMOS (Fig. 11 di [4])

Come appare evidente osservando i grafici sopra riportati, un INVERTER realizzato in logica Sub-DTMOS dissipa una maggiore potenza rispetto ad uno in Sub-CMOS, ma contemporaneamente presenta un minore tempo di ritardo di commutazione.

Complessivamente, per le due famiglie logiche considerate, otteniamo il seguente PDP (Power-Delay-Product) in funzione della tensione di alimentazione (figura 1.4)

Figura 1.4: PDP in un inverter di un ring oscillator in funzione della tensione di alimentazione

realizzati con la logica Sub-CMOS e Sub-DTMOS (Fig. 12 di [4])

Dalla ricerca effettuata in letteratura, si è rivelata interessante anche la famiglia logica Sub-pseudo-nMOS al fine della realizzazione della libreria Standard Cell. La caratteristica principale di questa logica è quella di avere la rete di PULL-UP realizzata con un singolo transistore pMOS che ha il terminale di gate collegato al riferimento. In questo modo, tale dispositivo risulta sempre attivo e si comporta da elemento resistivo.

Per comprendere meglio quanto appena affermato, riportiamo un circuito esplicativo in figura 1.5 dove il riquadro di colore verde rappresenta la rete di pull-down realizzata con transistori MOS di tipo n.

Figura 1.5 Schema di principio di una porta realizzata in logica Sub-Pseudo-NMOS

Nell’articolo [5], sono stati riportati diversi risultati di un confronto tra la logica Sub-CMOS e quella Sub-Pseudo-NMOS ottenuti utilizzando nuovamente il simulatore SPICE e il processo tecnologico TSMC 0,35 µm.

Per entrambe le famiglie logiche, sono state realizzate porte NOR a quattro, otto e sedici ingressi ed un INVERTER. Ciascuna di queste porte sono state utilizzate per realizzare sistemi ring oscillator ed è stato riportato per ciascuno di essi il tempo di ritardo di commutazione e la potenza dissipate ( tabella 1.1 )

Sub-CMOS Sub-Pseudo-NMOS Tipo di

Porta Power (nW) Delay (µs) Power (nW) Delay (µs)

INVERTER 4.886 0.22340 31.86 5.474E-02

NOR-4 6.064 0.8034 31.87 7.054E-02

NOR-8 6.852 1.808 31.87 9.160E-02

NOR-16 7.815 4.482 31.87 0.1337

Tabella 1.1: Confronto tra porte realizzate in logica Sub-CMOS e Sub-Pseudo-NMOS. Le unità

di misura utilizzate sono nW per la potenza dissipata e µs per il tempo di ritardo (Tabella 3 di [5])

In questo articolo è stato effettuato anche un ulteriore studio in cui è stata misurata l’energia dissipata per switching da un INVERTER (figura 1.5) e da una porta NOR a quattro ingressi (figura 1.6) realizzati con la logica Sub-CMOS e Sub-pseudo-nMOS.

Figura 1.5: Confronto tra l’energia dissipata per switching da due inverter realizzati

Figura 1.6: Confronto tra l’energia dissipata per switching da una porta NOR a quattro ingressi

realizzati rispettivamente in tecnologia Sub-CMOS e Sub-Pseudo-NMOS (Fig. 5 di [5])

Dall’analisi di queste ultime figure notiamo come le prestazioni di un INVERTER realizzato con la logica Sub-CMOS siano superiori a quelle ottenute con quella Sub-Pseudo-NMOS.

Capitolo 2

In seguito ai dati ricavati dalla lettura degli articoli considerati, in questo capitolo abbiamo deciso di svolgere uno studio dettagliato di alcune porte elementari realizzate utilizzando le tre famiglie logiche precedentemente menzionate.

Più precisamente, abbiamo cercato di ottimizzare la progettazione delle porte elementari in modo da minimizzare la dissipazione di energia nell’unità di tempo. Nel seguente capitolo verranno quindi discussi i seguenti argomenti:

• Descrizione della logica Sub-CMOS • Descrizione della logica Sub-DTMOS • Descrizione della logica Sub-pseudo-nMOS

• Confronto tra le tre famiglie logiche precedentemente descritte • Confronto tra la logica Sub-CMOS e Sub-pseudo-nMOS

2.1

Strumenti e regole utilizzate per la realizzazione delle

simulazioni

Per la realizzazione delle simulazioni che verranno riportate in questo capitolo, ci

siamo avvalsi del software SPICE utilizzando il processo tecnologico AMS 0.35 µm. Ricordiamo che per questo tipo di tecnologia, le tensioni di soglia

per i transistori di tipo n e p sono rispettivamente 0,4655V e -0,75V. Quindi, per far lavorare i transistori nella zona di funzionamento sottosoglia, abbiamo deciso

di far variare la tensione di alimentazione in un range che va da 0,2 V fino a 0,7 V.

I dispositivi sono stati dimensionati in maniera tale da variare solo la larghezza di canale mentre la lunghezza, dove possibile, è stata mantenuta pari a quella minima consentita e cioè 0,35 µm.

Le regole che ci siamo imposti per considerare valide le forme d’onda di uscita dai sistemi realizzati sono state le seguenti. Si sono supposti corretti tutti quei segnali che presentano valori minimo e massimo rispettivamente inferiore a

4

1 e superiore a 4

3 l’ampiezza della tensione di alimentazione come viene evidenziato in figura 2.1.

Figura 2.1 Rappresentazione dei limiti di accettabilità della forma d’onda di uscita da una porta

2.2 Logica Sub-CMOS

Prima di passare alla progettazione delle celle elementari che andranno a costituire la libreria Standard Cell, abbiamo deciso di evidenziare le caratteristiche fondamentali che contraddistinguono le tre famiglie logiche precedentemente considerate partendo con la Sub-CMOS.

Come abbiamo affermato in precedenza, per far lavorare i transistori MOS nella zona di funzionamento sottosoglia, è sufficiente attribuire valori opportuni alla tensione di alimentazione e, più precisamente, inferiore a quella di soglia. Ricordiamo che tale scelta determina sì una diminuzione della potenza dissipata, ma al contempo anche un aumento del tempo di ritardo di commutazione.

Per comprendere quanto questa scelta influisca sulla massima frequenza di funzionamento del sistema, siamo passati a studiare un circuito realizzato ponendo in cascata quattro INVERTER come mostrato in figura 2.2.

Il sistema viene pilotato con un generatore di segnale ad onda quadra di cui è stata fissata l’ampiezza della tensione picco-picco e posta pari alla massima dinamica consentita. La frequenza, invece, è stata fatta variare fino a che una delle uscite dei quattro INVERTER non rispettava i limiti esposti nel paragrafo precedente. I risultati ottenuti sono riportati in figura 2.3

0.7 1 E + 0 7 1 E + 0 6 2 E + 0 5 2 E + 0 4 1 E + 0 3 20 0 0.6 0.5 0.4 0.3 0.2 Frequenza (Hz) T e nsione di a li m ent a z ione ( V )

Figura 2.3 Range di frequenze (Hz) con cui è possibile pilotare la catena di inverter realizzata

con la logica Sub-CMOS una volta fissata la tensione di alimentazione (V) e indipendentemente dalla larghezza del canale

Come ci aspettavamo, abbiamo ottenuto un’indipendenza della frequenza di lavoro dalle dimensioni assunte dai singoli dispositivi. Infatti attribuendo alla

larghezza di canale dei valori sempre maggiori, determiniamo un aumento sia della corrente di pilotaggio che della capacità di ingresso delle singole porte al punto che la frequenza di lavoro risulta invariata. Per confermare quanto appena affermato, abbiamo realizzato un ulteriore studio utilizzando il circuito riportato in figura 2.4

Figura 2.4 Inverter realizzato in tecnologia CMOS la cui uscita è chiusa su una capacità di

valore fissato

In questo caso abbiamo utilizzato un sistema realizzato con un singolo INVERTER la cui uscita è stata chiusa su un condensatore di valore pari a 2 fF. La porta è stata pilotata con un generatore di segnale ad onda quadra di cui è stata fissata solo l’ampiezza della tensione picco-picco. Al variare della larghezza del canale dei transistori, abbiamo misurato la frequenza massima con cui è possibile pilotare la cella.

0,0 0,7 1,4 2,1 2,8 3,5 4,2 4,9 5,6 6,3 7,0 7,7 8,4 9,1 9,8 10,511,211,912,6 0,0 0,2 0,4 0,6 0,8 1,0 1,2 P e ri odo ( µ s ) Wn ( µm )

Figura 2.5 Andamenti del periodo minimo di lavoro in funzione della larghezza del canale

In base ai risultati riportati in figura 2.5, notiamo che, ponendo sull’uscita dell’INVERTER una capacità di valore fissato, ad un incremento della larghezza del canale dei transistori corrisponde una diminuzione del periodo di oscillazione. In questo modo abbiamo trovato una conferma a quanto affermato nelle pagine precedenti e cioè che variando le larghezze di tutti i transistori del sistema di figura 2.2, non possiamo ottenere una variazione della frequenza in quanto sia le capacità di ingresso delle singole porte che la corrente di pilotaggio variano della stessa ragione.

Fino a questo punto sono state analizzate le prestazioni della logica Sub-CMOS solo in termini di velocità di risposta ad eccitazioni esterne. In realtà noi siamo interessati alla progettazione di un sistema in cui si tende a ridurre il più possibile la dissipazione di energia nell’unità di tempo.

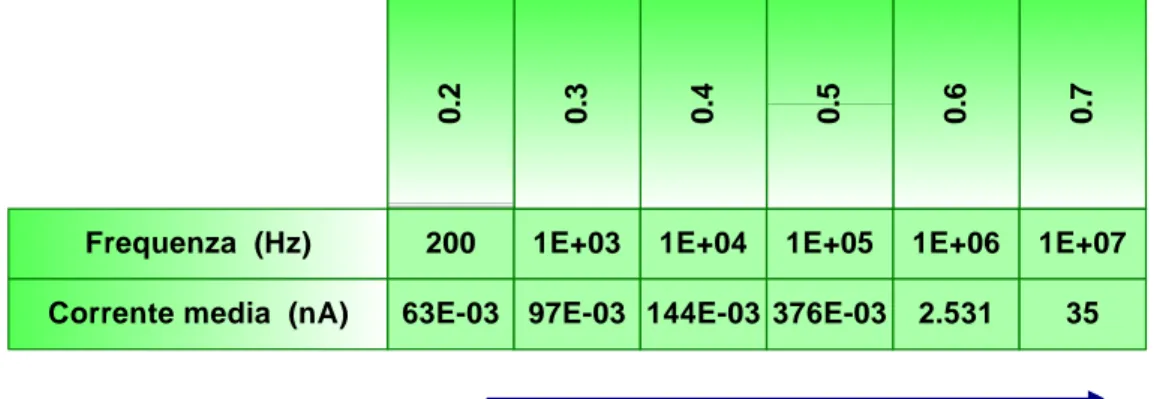

Tenendo quindi conto dell’indipendenza della massima frequenza di funzionamento dalla larghezza di canale, abbiamo attribuito ai transistori del circuito di figura 2.2 le dimensioni minime consentite dal processo. Quindi, abbiamo svolto un’ulteriore analisi che è servita per misurare la corrente media (Tabella 2.1) che scorre nei singoli INVERTER al variare della tensione di alimentazione quando sono pilotati con la massima frequenza di lavoro consentita.

Frequenza (Hz) 0.7 0.6 0.5 0.4 0.3 0.2

Corrente media (nA)

200 1E+03 1E+04 1E+05 1E+06 1E+07 63E-03 97E-03 144E-03 376E-03 2.531 35

Tensione di alimentazione (V)

Tabella 2.1 Corrente media in un inverter realizzato con la logica Sub-CMOS pilotato con la

massima frequenza consentita al variare della tensione di alimentazione

In base a questi risultati, è stata calcolata l’energia dissipata per switching al variare della tensione di alimentazione riportando i risultati in figura 2.6

Vdd (V) E n er gy/ s w it c hi ng (f J) 63 29 5.76 1.88 1.52 2.45 0.5 0.6 0.7 0.4 0.3 0.2

Figura 2.6 Energia dissipata per switching al variare della tensione di alimentazione

In seguito alle ultime simulazioni effettuate sul circuito di figura 2.2 e tenendo di conto che preferibilmente vorremmo ottenere una macchina a stati che lavora con una frequenza di clock pari a 1 MHz, abbiamo deciso che per la realizzazione della libreria Standard Cell in logica Sub-CMOS è sufficiente alimentare le singole celle con una tensione pari a 0,6 V. Tale scelta infatti determina buone prestazioni sia in termini di frequenza di lavoro che di potenza dissipata.

Un ulteriore aspetto che ci sembra interessante affrontare è quello del calcolo del FAN OUT. Più precisamente ci siamo posti come obiettivo quello di ottenerne uno pari a 4.

Quindi, per riuscire a rispondere a questa specifica di progetto, abbiamo eseguito una nuova serie di analisi in cui è stato sfruttato un circuito costituito da un INVERTER la cui uscita è stata chiusa su altre quattro porte identiche alla precedente.

In ingresso a questo sistema è stato posto un generatore di onda quadra il quale è stato dimensionato in maniera tale che l’ampiezza della tensione picco-picco fosse pari a 0.6 V e la frequenza uguale a 1 MHz. La lunghezza di canale dei singoli dispositivi è stata posta pari a 0,35 µm, mentre abbiamo variato la larghezza dei transistori fino a che la forma d’onda di uscita non presentava un valore minimo e massimo rispettivamente inferiore a 14 e superiore a 3 4 la tensione di alimentazione. In seguito a questo studio, abbiamo concluso che le dimensioni da attribuire al transistore di tipo n e p sono rispettivamente pari a 2.8 µm e 8.4 µm.

Fino a questo momento abbiamo realizzato delle analisi in cui i sistemi vengono fatti lavorare alla massima frequenza di funzionamento. In realtà noi siamo interessati ad ottenere una riduzione della dissipazione di potenza senza dover porre molta attenzione alle prestazioni in termini di velocità. Ricordiamo infatti che inizialmente avevamo scelto 10 KHz come limite inferiore della frequenza di lavoro.

Ecco perché abbiamo deciso di svolgere delle nuove simulazioni sul circuito di figura 2.2 per misurare la corrente media che scorre nell’INVERTER quando la frequenza del generatore di onda quadra viene fatta variare tra 10 KHz e 1 MHz mentre la tensione di alimentazione è fissata a 0.6 V. I transistori sono stati dimensionati con le larghezze di canale minime che consentono di ottenere un FAN OUT pari a quattro e i risultati di questa nuova analisi sono riportati in figura 2.7

10000 100000 1000000 0,01 0,1 1 Corre n te medi a (nA) frequenza (Hz)

Figura 2.7 Corrente media che scorre in un inverter realizzato con la logica Sub-CMOS al

variare della frequenza di lavoro quando la tensione di alimentazione è fissata a 0,6 V, Wn=2,8µm e Wp=8,4µm

In seguito a questi ultimi risultati, abbiamo calcolato la potenza dissipata riportando i valori trovati in figura 2.8

10000 100000 1000000 0,01 0,1 1 P o ten z a di ssi pata (nW ) frequenza (Hz)

Figura 2.8 Potenza dissipata da un inverter realizzato con la logica Sub-CMOS al variare della

frequenza, quando la tensione di alimentazione è fissata a 0,6V, Wn= 2,8µm e Wp=8,4µm

Per completare lo studio della logica Sub-CMOS, abbiamo deciso di misurare il contributo apportato dalla potenza statica nel calcolo dell’energia dissipata nell’unità di tempo. Per eseguire questo ultimo tipo di analisi, abbiamo collegato l’ingresso del sistema di figura 2.2 prima al riferimento e in seguito ad un generatore di tensione continua di valore 0,6 V.

Vdd (V) Vin (V) Idd (fA) Pstatica (fW)

0.6 0 53.23 31.938

0.6 0.6 14.23 8.538

Tabella 2.2 Corrente (fA) e potenza statica dissipata (fW) in un inverter realizzato con la logica

Sub-CMOS una volta fissata la tensione di alimentazione a 0,6 V e facendo variare la tensione di ingresso (V)

Quindi, effettuando un confronto tra i risultati riportati nella figura 2.8 e nella tabella 2.2, appare subito evidente che il contributo apportato dalla potenza statica è trascurabile rispetto a quella dinamica. Ecco perché, nelle analisi che seguiranno, possiamo trascurare questo termine senza commettere errori apprezzabili.

2.3 Logica Sub-DTMOS

In base ai risultati ricavati dalla lettura dei diversi articoli presenti in letteratura, ci è sembrato particolarmente interessante passare ad analizzare la famiglia logica Sub-DTMOS perché sembra possedere i requisiti necessari per la realizzazione del nostro progetto.

Prima di cominciare, però, ci preme evidenziare un fatto molto importante sul quale si è sorvolato nei testi presi in considerazione. Da un punto di vista realizzativo, un transistore DTMOS si ottiene collegando direttamente il terminale di gate con quello di bulk rendendo difficoltoso il dimensionamento del sistema. Infatti, è interessante notare che la tensione di ingresso tende a polarizzare direttamente le giunzioni source-substrato e drain-substrato. Se questo accadesse, si otterrebbe un incremento eccessivo della corrente e quindi della potenza dissipata. Ecco perché, nello studio che seguirà, la tensione di alimentazione verrà variata in un range di valori che va da 0.2 V a 0.4 V.

Infine, sempre a causa del collegamento diretto tra il terminale di gate e quello di bulk, in fase realizzativa sarebbe obbligatorio utilizzare una tecnologia tripla well in modo da permettere diverse tensioni di substrato per ciascun dispositivo.

Passiamo quindi ad effettuare una analisi più dettagliata della famiglia logica Sub-DTMOS.

Secondo quanto è stato affermato nei diversi articoli presi in considerazione, il collegamento diretto tra il terminale di gate e quello di bulk comporta un incremento della corrente di pilotaggio determinando un miglioramento delle prestazioni in termini di velocità di commutazione.

Per capire quale sia la massima frequenza con cui è possibile pilotare una porta sintetizzata in logica Sub-DTMOS, partiamo con l’analizzare un circuito realizzato ponendo in cascata quattro INVERTER come viene riportato in figura 2.9

Figura 2.9 Catena di quattro inverter realizzati con la logica Sub-DTMOS

Il sistema è stato pilotato con un generatore di segnale ad onda quadra la cui ampiezza picco-picco è stata posta uguale alla massima dinamica. La frequenza invece è stata fatta variare fino a che le forme d’onda di uscita dai quattro INVERTER non rispettavano più i limiti imposti nel paragrafo 2.1.

0.4 4 E+05 2 E+04 1 E+03 0.3 0.2 Frequenza (Hz) Ten s io ne di al im ent a zi on e ( V )

Figura 2.10 Range di frequenze (Hz) con cui è possibile pilotare un inverter realizzato con la

logica Sub-DTMOS al variare della tensione di alimentazione (V) e indipendentemente dalle dimensioni del canale dei transistori

Come per la logica Sub-CMOS, anche in questo caso abbiamo ottenuto un andamento costante della frequenza al variare della dimensioni del canale dei transistori. Come ci aspettavamo, infatti, incrementando la larghezza di canale, otteniamo sia un aumento della corrente di pilotaggio che della capacità di ingresso delle singole porte al punto che la velocità di commutazione resta costante.

Per confermare quanto appena affermato abbiamo realizzato un’ulteriore analisi nella quale è stato utilizzato un sistema costituito da un singolo INVERTER la cui uscita è stata chiusa su una capacità di valore pari a 2 fF ( figura 2.11 )

OUT 0 V2 V1 C1 2f Q2 MODN Q1 MODP

Figura 2.11 Inverter realizzato con la logica Sub-DTMOS la cui uscita è chiusa su una capacità

di valore 2 fF

Il sistema è stato pilotato con un generatore di segnale ad onda quadra di cui è stata fatta variare la frequenza, mentre il valore dell’ampiezza picco-picco è stata posta pari a 0.4 V.

Per evidenziare quanto è emerso dalla precedente analisi riportiamo in figura 2.12 l’andamento del periodo minimo di oscillazione in funzione della larghezza del canale del transistore.

0 10 20 30 40 50 0 1 2 3 4 5 Peri od o Wn

Figura 2.12 Andamento del periodo minimo (µs) di funzionamento in funzione della larghezza

di canale (µm)

Come possiamo notare dall’analisi di questo grafico, abbiamo ottenuto un andamento crescente della massima frequenza di funzionamento con l’incremento della larghezza del canale. Quindi se aumentiamo le dimensioni dei dispositivi che compongono il sistema di figura 2.9 non possiamo ottenere una variazione della frequenza di pilotaggio perché la capacità di ingresso e la corrente di pilotaggio delle singole porte variano della stessa ragione.

Prima di proseguire facciamo un passo indietro e soffermiamoci sui risultati riportati in figura 2.10. In questo caso possiamo notare che per nessun valore della tensione di alimentazione otteniamo una frequenza di pilotaggio pari a 1 MHz come avveniva nel caso della logica Sub-CMOS. In base a queste ultime considerazioni e non dimenticandoci dei grafici riportati nell’articolo [4] dove gli autori hanno inserito risultati del tutto opposti, abbiamo deciso di effettuare un nuovo tipo di analisi per capire il motivo di tale discordanza.

Per questo motivo abbiamo deciso di utilizzare un sistema RING OSCILLATOR realizzato ponendo in cascata tre INVERTER sintetizzati prima in logica Sub-DTMOS e in un secondo tempo in Sub-CMOS. Per una migliore comprensione del circuito utilizzato riportiamo in figura 2.13 un disegno esplicativo

Figura 2.13 Ring oscillator realizzato ponendo in cascata 3 INVERTER

Tale sistema è stato dimensionato in modo che le singole porte presentassero un FAN OUT pari a 4. Per ottenere ciò, ricordiamo che nel caso della logica Sub-DTMOS, le larghezze di canale dei transistori n e p devono assumere rispettivamente il valore di 11,2 µm e 33,6 µm.

Quindi, al variare della tensione di alimentazione, abbiamo calcolato il tempo di ritardo di commutazione ( figura 2.14 ) e la potenza dissipata ( figura 2.15 ).

0,2 0,3 0,4 0,5 0,6 0,7 10-2 10-1 100 101 102 103 104 D e la y (us) Tensione di alimentazione (V) Sub-CMOS Sub-DTMOS

Figura 2.14 Ritardo di commutazione al variare della tensione di alimentazione per sistemi ring

0,2 0,3 0,4 0,5 0,6 0,7 10-4 10-3 10-2 10-1 100 101 102 103 104 P o ten z a dis s ipa ta (nW ) Tensione di alimentazione (V) Sub-CMOS Sub-DTMOS

Figura 2.15 Potenza dissipata, al variare della tensione di alimentazione da un sistema ring

oscillator realizzato con 3 INVERTER sintetizzati sia in logica Sub-DTMOS e Sub-CMOS

Per concludere l’analisi abbiamo realizzato un ulteriore grafico con il quale abbiamo rappresentato il PDP (Power-Delay-Product) per i sistemi ring oscillator precedentemente considerati. I risultati ottenuti sono riportati in figura 2.16, mentre in figura 2.17 riportiamo nuovamente il grafico presente nell’articolo [4].

0,2 0,3 0,4 0,5 0,6 0,7 100 101 102 103 PD P ( fJ ) Tensione di alimentazione (V) Sub-CMOS Sub-DTMOS

Figura 2.16 Power-Delay-Product per sistemi ring oscillator al variare della tensione di

alimentazione realizzati in logica Sub-CMOS e Sub-DTMOS

Figura 2.17 PDP in un inverter di un ring oscillator in funzione della tensione di alimentazione

Possiamo notare la notevole discrepanza tra i risultati riportati in figura 2.16 e quelli nel grafico 2.17 che mettono in evidenza le peggiori prestazioni che otterremmo se decidessimo di progettare la libreria Standard Cell in logica Sub-DTMOS invece che in Sub-CMOS.

Per completare l’analisi della logica Sub-DTMOS, abbiamo deciso di mettere in evidenza un’ulteriore caratteristica di questa famiglia. Per questo motivo, abbiamo eseguito un altro studio sul circuito di figura 2.9 con il quale mostriamo l’indipendenza della potenza dissipata dalla frequenza di lavoro. Dopo aver fissato la tensione di alimentazione a 0.4 V, abbiamo pilotato il sistema con un generatore di segnale ad onda quadra di cui abbiamo fissato l’ampiezza della tensione picco-picco ponendola uguale alla massima dinamica consentita. La frequenza invece è stata fatta variare tra 10 KHz e 200 KHz ed abbiamo riportato i risultati in figura 2.18 1000 10000 100000 17,02 17,04 17,06 17,08 17,10 17,12 17,14 17,16 17,18 Potenz a di ssi p a ta (nW ) f (Hz)

Figura 2.18 Potenza dissipata da un inverter realizzato in Sub-DTMOS al variare della

Come precedentemente affermato, abbiamo ottenuto in figura 2.18 l’indipendenza della potenza dissipata dalla frequenza di lavoro. Tale andamento può essere spiegato facilmente se, nel sistema di figura 2.9, passiamo a misurare la potenza statica dissipata da ciascuna porta elementare. Per realizzare questo tipo di analisi abbiamo pilotato il circuito con un generatore di tensione continua al quale abbiamo fatto assumere i valori 0.4 e 0 V riportando i risultati in figura 2.4

Vdd (V) Vin (V) Idd (nA) Pstatica (nW)

0.4 0 60 24

0.4 0.4 0.01 0.04

Tabella 2.4 Corrente (nA) e potenza statica dissipata (nW) in un inverter realizzato con la logica

Sub-DTMOS al variare della tensione di ingresso (V) una volta fissata quella di alimentazione (V)

Confrontando questi valori con quelli di figura 2.18, possiamo notare che la potenza dissipata in un INVERTER realizzato con la logica Sub-DTMOS è dovuta essenzialmente alla componente statica. Da notare inoltre la notevole differenza che intercorre tra la potenza statica dissipata quando il sistema viene pilotato con una tensione pari a 0.4 V rispetto a quando l’ingresso è nullo. Tale variazione può essere spiegata facilmente avvalendoci dell’ausilio del circuito riportato in figura 2.19.

Come è stato messo in evidenza, la corrente che scorre nel transistore di tipo p dell’INVERTER i-esimo si richiude verso massa attraverso la giunzione source-substrato del DT-NMOS dell’INVERTER (i+1)-esimo quando in ingresso poniamo una tensione pari a 0 V.

2.4 Logica Sub-pseudo-nMOS

Anche in questo caso, siamo interessati a capire se questa famiglia logica ci consenta di ottenere una libreria Standard Cell in modo da minimizzare la potenza dissipata quando i sistemi sono pilotati con una frequenza dell’ordine di 1 MHz.

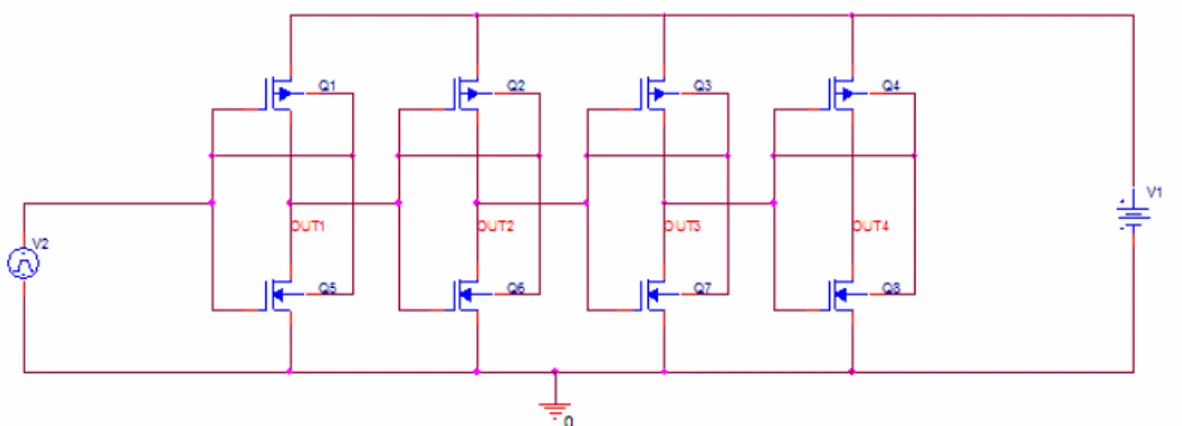

Per vedere come poter rispettare questi vincoli, abbiamo deciso di utilizzare un circuito realizzato ponendo in cascata quattro INVERTER di cui riportiamo lo schema circuitale in figura 2.20

OUT1 OUT2 OUT3 OUT4

0 0 0 0 0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 V1 V2

Figura 2.20 Catena di quattro inverter realizzati con la logica Sub-pseudo-nMOS

Sfruttando questa configurazione, abbiamo realizzato delle prime simulazioni che sono servite per capire quale fosse la frequenza massima di funzionamento del sistema al variare della tensione di alimentazione tra 0.2 V e 0.7 V.

Il circuito è stato pilotato con un generatore di segnale ad onda quadra di cui è stata fatta variare la frequenza mentre l’ampiezza della tensione picco-picco è stata posta uguale alla massima dinamica consentita. I risultati sono riportati in figura 2.21 0.7 1 E+08 1 E+07 1 E+06 1 E+04 2 E+03 200 0.6 0.5 0.4 0.3 0.2 Frequenza (Hz) Tens io n e di al im en ta z ion e (V )

Figura 2.21 Range di frequenze (Hz) con cui è possibile pilotare la catena di inverter realizzata

con la logica Sub-Pseudo-NMOS una volta fissata la tensione di alimentazione (V) e indipendentemente dalla larghezza del canale

Come avevamo già notato nell’analisi delle famiglie logiche Sub-CMOS e Sub-DTMOS, anche in questo caso abbiamo ottenuto un andamento costante della massima frequenza di pilotaggio al variare della larghezza del canale.

In seguito a questi ultimi risultati, è stata calcolata la potenza dissipata da ciascun INVERTER del sistema di figura 2.20 al variare della tensione di alimentazione pilotando il circuito alla massima frequenza (figura 2.21). Prima di ottenere questo risultato, in tabella 2.5 abbiamo riportato la corrente media che scorre in ciascuna cella elementare utilizzando transistori con la larghezza pari a quella minima consentita dalla tecnologia vista l’indipendenza della frequenza di funzionamento dalle dimensioni assunte dai dispositivi.

Frequenza (Hz) 0. 7 0. 6 0. 5 0. 4 0. 3 0. 2

Corrente media (nA)

200 2E+03 1E+05 1E+06 1E+07 1E+08

241E-06 0.005 0.013 2.47 35 312

Tensione di alimentazione (V)

Tabella 2.5 Corrente media (nA) che scorre in un inverter realizzato con la logica

Sub-Pseudo-nMOS una volta fissata la tensione di alimentazione (V) e la frequenza di funzionamento (Hz)

In base ai dati trovati, abbiamo calcolato l’energia dissipata per switching al variare della tensione di alimentazione riportando i risultati in figura 2.22

Vdd (V) Ene rgy/ s w it c h ing (f J ) 0.24 0.8 0.51 1.235 2.1 2.18 0.5 0.6 0.7 0.4 0.3 0.2

Figura 2.22 Energia dissipata per switching al variare della tensione di alimentazione

Analizzando i risultati delle figure 2.21-22 e ricordando che siamo interessati ad ottenere una minimizzazione della energia dissipata nell’unità di tempo quando il sistema viene pilotato con una frequenza dell’ordine di 1 MHz, ci siamo resi conto che per rispondere in maniera corretta alle specifiche di progetto è sufficiente alimentare le singole celle con una tensione pari a 0.5 V.

Utilizzando questa ultima scelta, abbiamo deciso di sfruttare il sistema di figura 2.20 per misurare la potenza dissipata al variare della frequenza di lavoro. Per fare ciò i dispositivi sono stati dimensionati in modo da ottenere un FAN OUT pari a 4 e più precisamente le larghezze dei transistori n e p sono state poste rispettivamente uguali a 2.8 µm e a 10.5 µm. Come segnale di ingresso abbiamo scelto un’onda quadra la cui frequenza è stata fatta variare tra 10 KHz e 1 MHz. In figura 2.23 abbiamo riportato la corrente media che scorre nei singoli transistori.

10000 100000 1000000 16,5 17,0 17,5 18,0 18,5 19,0 C o rre nt e media (n A ) f (Hz)

Figura 2.23 Corrente media che scorre in un inverter realizzato con la logica

Sub-Pseudo-NMOS al variare della frequenza di lavoro quando la tensione di alimentazione è fissata a 0,5 V, Wn=2,8µm e Wp=10,5µm

In base ai dati trovati, abbiamo calcolato la potenza dissipata da un INVERTER realizzato in logica Sub-pseudo-nMOS riportando i risultati in figura 2.24

10000 100000 1000000 8,4 8,6 8,8 9,0 9,2 9,4 9,6 P o tenz a di ssi pata (nW ) f (Hz)

Figura 2.24 Potenza dissipata da un inverter realizzato con la logica Sub-Pseudo-NMOS al

variare della frequenza, quando la tensione di alimentazione è fissata a 0,5V, Wn= 2,8 µm e Wp=10,5 µm

Da un’analisi di queste ultime due figure (2.23-24), notiamo l’indipendenza della potenza dissipata dalla frequenza di lavoro. Il motivo di questo andamento si può spiegare facilmente se passiamo al calcolo della potenza statica dissipata da un singolo INVERTER del sistema di figura 2.20.

Per realizzare questa analisi, abbiamo pilotato il circuito con un generatore di tensione continua al quale abbiamo fatto assumere i valori 0 V e 0,5 V riportando i risultati in tabella 2.6

Vdd (V) Ingresso (V) Corrente (nA) Pstatica (nW)

0.5 0 0.052 0.026

0.5 0.5 33.64 16.8

Tabella 2.6 Corrente e potenza statica dissipata in un inverter realizzato con la logica

Sub-Pseudo-nMOS al variare della tensione di ingresso una volta fissata la tensione di alimentazione

Confrontando questi ultimi valori con quelli riportati in figura 2.24, ci rendiamo conto che la dissipazione di potenza in un sistema realizzato con la logica Sub-Pseudo-nMOS è legata essenzialmente alla componente statica.

Prima di concludere, ci sembra interessante soffermarci sui valori ottenuti per la potenza statica al variare dell’ampiezza della tensione di ingresso. Tale variazione, come viene evidenziato in figura 2.25, è legata al fatto che quando applichiamo un ingresso pari a 0.5 V abbiamo entrambi i transistori in conduzione e quindi il percorso della corrente si richiude verso massa.

0

0

0.5V

Figura 2.25 Andamento della corrente quando l’inverter realizzato con la logica

2.5 Confronto tra le tre famiglie logiche

Una volta descritte le caratteristiche di ciascuna delle 3 famiglie logiche precedentemente considerate, siamo passati a confrontarle per capire quale si dimostrasse più adatta alla progettazione della libreria Standard Cell. Per questo motivo abbiamo deciso di utilizzare dei sistemi RING OSCILLATOR realizzati ponendo in cascata porte elementari dello stesso tipo (NOR, NAND e INVERTER) come viene messo in evidenza in figura 2.26

Figura 2.26 Ring oscillator realizzato con tre porte NOR a tre ingressi

Nell’eseguire questo nuovo studio, abbiamo deciso di adottare la seguente procedura. Prima di tutto sono state ricercate le dimensioni minime da attribuire ai transistori in modo da ottenere sul terminale di uscita (Out) una forma d’onda che avesse l’ampiezza massima e minima rispettivamente superiore ¾ e inferiore a ¼ il valore della tensione di alimentazione ( figura 2.1 ). Di tale segnale è stata quindi misurata la frequenza di lavoro.

In seguito abbiamo cercato di scalare le larghezze e le lunghezze dei transistori in modo che i sistemi realizzati con le stesse celle elementari ma con logica differente presentassero uguale frequenza di funzionamento. Quindi è stata misurata la corrente media che scorre nelle singole porte in modo da poter calcolare la potenza dissipata a parità di prestazioni.

Questo tipo di studio è stato svolto al variare del numero di ingressi. Per quanto riguarda la tensione di alimentazione, abbiamo sfruttato i risultati ottenuti dalle analisi riportate nei paragrafi precedenti. Più precisamente applicheremo nel caso della famiglia logica Sub-DTMOS una tensione pari a 0.4 V, mentre, per le altre due, una uguale a 0.6 V.

2.5.1

Analisi di RING OSCILLATOR realizzati con porte

elementari a due ingressi

In questo paragrafo viene affrontato lo studio di sistemi RING OSCILLATOR realizzati con INVERTER e porte NOR e NAND a due ingressi.

Cominciamo tale analisi riportando i valori che devono essere attribuiti alle larghezze di canale dei singoli transistori per ottenere delle forme d’onda di uscita che rispettino i seguenti limiti: ampiezza massima e minima rispettivamente maggiore di ¾ e minore di ¼ il valore della tensione di alimentazione. I risultati di questo primo studio sono riportati nelle tabelle 2.7-9 in cui abbiamo indicato anche il periodo dell’oscillazione.

Famiglia logica Wn (µm) Wp (µm) Periodo (µs)

Sub-CMOS 1.4 4.2 0.2

Sub-pseudo-nMOS

1.4 4.2 0.04

Sub-DTMOS 22.4 67.2 1.2

Tabella 2.7 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

Famiglia logica Wn (µm) Wp (µm) Periodo (µs) Sub-CMOS 1.4 4.2 0.3 Sub-pseudo-nMOS 1.4 4.2 0.06 Sub-DTMOS 44.8 134.4 3.4

Tabella 2.8 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

realizzato con 3 porte NOR a 2 ingressi

Famiglia logica Wn (µm) Wp (µm) Periodo (µs)

Sub-CMOS 1.4 4.2 0.15

Sub-pseudo-nMOS

1.4 4.2 0.06

Sub-DTMOS 22.4 67.2 2.5

Tabella 2.9 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

realizzato con 3 porte NAND a 2 ingressi

Per comprendere quale famiglia logica rispondesse in maniera ottimale alle nostre esigenze di progetto, abbiamo deciso di eseguire una ulteriore analisi. In particolare, abbiamo cercato di scalare le larghezze e le lunghezze del canale dei transistori in modo che i sistemi realizzati con le stesse celle elementari ma con logica differente presentassero uguale frequenza di funzionamento. Tale

studio però è stato possibile effettuarlo solo per le famiglie Sub-CMOS e Sub-pseudo-nMOS. Per capire il motivo dell’impossibilità di questo tipo di analisi

tre porte NAND a due ingressi. In questo caso, attribuendo a un valore pari a 89.6 µm, il periodo di oscillazione risulta essere pari a 1.24 µs. Se continuiamo ad incrementare il valore delle dimensioni, non riusciamo comunque a scendere sotto la soglia di 1 µs.

n

W

I risultati sono riportati nelle tabelle 2.10-12 per sistemi realizzati utilizzando rispettivamente INVERTER e porte NOR e NAND a due ingressi.

Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.35 0.2 23 13.8 Sub- pseudo-nMos 1.4 2.1 1.05 0.2 19.5 11.7

Tabella 2.10 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di un

sistema realizzato ponendo in cascata 3 INVERTER in modo che le forme d’onda di uscita presentino la stessa frequenza

Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.35 0.3 23 13.8 Sub- pseudo-nMOS 1.4 1.05 0.35 0.3 17.1 10.26

Tabella 2.11 Potenza dissipata (nW), corrente media (nA) e dimensioni dei transistori (µm) nel

caso di ring oscillator realizzato con porte NOR a 2 ingressi in modo che presentino la stessa frequenza di oscillazione Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 2.8 8.4 0.35 0.145 60 36 Sub- pseudo-nMOS 1.4 1.75 0.35 0.14 35.5 21.3

Tabella 2.12 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di ring

oscillator realizzato con porte NAND a 2 ingressi in modo che presentino la stessa frequenza di oscillazione

Quindi, tenendo conto dei risultati riportati nelle tabelle 2.10-12, possiamo affermare che realizzare la libreria Standard Cells in logica Sub-pseudo-nMOS ci

consentirebbe una minore occupazione di area di silicio e una minore dissipazione di potenza a parità di prestazioni.

2.5.2 Analisi di sistemi RING OSCILLATOR realizzati con

porte elementari a tre ingressi

Passiamo adesso ad analizzare i sistemi RING OSCILLATOR realizzati ponendo in cascata porte NOR e NAND a tre ingressi.

Per ottenere i risultati che seguono abbiamo seguito lo schema di analisi utilizzato nel paragrafo precedente. Quindi in primo luogo ci siamo interessati di ricercare le dimensioni minime che permettono di ottenere sul terminale di uscita un’oscillazione che rispetti i limiti rappresentati in figura 2.1.

I risultati ottenuti sono riportati nelle tabelle 2.13-14

Famiglia logica Wn (µm) Wp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.6 18 10.8 Sub- pseudo-nMOS 1.4 4.2 0.08 117 70.2 Sub-DTMOS 89.6 268.8 6 55.5 22.2

Tabella 2.13 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

Famiglia logica Wn (µm) Wp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 2.8 8.4 0.22 28.5 17.1 Sub- pseudo-nMOS 1.4 2.1 0.16 45 27 Sub-DTMOS 44.8 134.4 2.5 11.53 4.612

Tabella 2.14 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

realizzato con porte NAND a 3 ingressi

Anche in questo caso, i sistemi realizzati con la logica Sub-DTMOS sono stati alimentati con una tensione pari a 0.4 V, mentre le altre due famiglie con 0.6 V. Il motivo per cui stiamo effettuando questa serie di simulazioni è essenzialmente quello di avere dei dati numerici che ci consentano di decidere quale logica convenga utilizzare per la realizzazione della libreria Standard Cell.

Per questo motivo abbiamo eseguito delle ulteriori analisi con le quali abbiamo ricercato le dimensioni da attribuire ai dispositivi in modo che i sistemi realizzati con lo stesso tipo di porta elementare, ma con una diversa logica, presentassero la stessa frequenza di oscillazione. Ancora una volta abbiamo potuto fare questo confronto solo tra le famiglie logiche Sub-CMOS e Sub-pseudo-nMOS considerando sistemi RING OSCILLATOR realizzati con porte NOR e NAND a tre ingressi.

I risultati sono riportati nelle tabelle 2.15-16. Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.35 0.6 18 10.8 Sub- pseudo-nMOS 1.4 1.4 0.7 0.6 13.275 7.965

Tabella 2.15 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di ring

oscillator realizzato con porte NOR a 3 ingressi in modo che presentino la stessa frequenza di oscillazione Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 2.8 8.4 0.35 0.22 28.5 17.1 Sub- pseudo-nMOS 1.4 1.4 0.35 0.27 25.4 15.24

Tabella 2.16 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di ring

oscillator realizzato con porte NAND a 3 ingressi in modo che presentino la stessa frequenza di oscillazione

Anche in questo caso abbiamo ottenuto delle prestazioni migliori utilizzando la logica Sub-pseudo-nMOS.

2.5.3 Analisi di sistemi RING OSCILLATOR realizzati con

porte elementari a quattro ingressi

Per completare l’analisi, in questo paragrafo andremo a considerare sistemi RING OSCILLATOR realizzati con porte NOR e NAND a quattro ingressi.

Anche in questo caso il nostro primo obiettivo è stato quello di ricercare le dimensioni minime che ci consentono di ottenere una oscillazione sul segnale di uscita che rispetti le regole riportate in figura 2.1.

I risultati ottenuti sono riportati nelle tabella 2.17-18

Famiglia logica Wn (µm) Wp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 1 8.165 4.899 Sub- pseudo-nMOS 1.4 4.2 0.01 119 71.4 Sub-DTMOS 179 537.6 8.3 92.94 37.176

Tabella 2.17 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

Famiglia logica Wn (µm) Wp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.3 5.759 3.45 Sub- pseudo-nMOS 1.4 2.1 0.2 43.5 26.1 Sub-DTMOS 44.8 134.4 4.4 15.234 6.09

Tabella 2.18 Dimensioni minime e periodo di oscillazione per un montaggio a ring oscillator

realizzato con porte NAND a 4 ingressi

Anche per quanto riguarda questi tipi di porte abbiamo deciso di ricercare le dimensioni minime che devono essere attribuite ai singoli transistori in modo che sistemi realizzati con lo stesso tipo di porte, ma con logica differente, presentino in uscita segnali che oscillano alla stessa frequenza e che rispettano i limiti detti inizialmente. Ancora una volta, ci siamo resi conto che questo tipo di analisi è possibile realizzarla solo per la logica Sub-CMOS e Sub-pseudo-nMOS.

Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 4.2 0.35 1 8.165 4.899 Sub- pseudo-nMOS 1.4 1.4 1.05 0.9 9.81 5.886

Tabella 2.19 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di ring

oscillator realizzato con porte NOR a 4 ingressi in modo che presentino la stessa frequenza di oscillazione Famiglia logica Wn (µm) Wp (µm) Lp (µm) Periodo (µs) Corrente media (nA) Pdd (nW) Sub-CMOS 1.4 3.5 0.35 0.3 5.759 3.45 Sub- pseudo-nMOS 1.4 1.4 0.35 0.34 24.6 14.76

Tabella 2.20 Potenza dissipata, corrente media e dimensioni dei transistori nel caso di ring

oscillator realizzato con porte NAND a 4 ingressi in modo che presentino la stessa frequenza di oscillazione

Con questi ultimi risultati abbiamo messo in evidenza che realizzare le porte a quattro ingressi in logica Sub-CMOS consente di ottenere delle migliori prestazioni in termini di dissipazione di potenza.

2.6 Confronto tra la logica Sub-CMOS e Sub-pseudo-nMOS

In questo paragrafo andremo ad effettuare un confronto tra le famiglie logiche Sub-CMOS e Sub-pseudo-nMOS. In base ai risultati ottenuti nei precedenti paragrafi, abbiamo infatti concluso che progettare la libreria Standard Cell in logica Sub-DTMOS comporterebbe oltre che una maggiore dissipazione di potenza anche peggiori prestazioni in termini di velocità di commutazione. Tutto ciò determinerebbe una maggiore dissipazione di energia nell’unità di tempo e quindi non risulterebbe adatta per la sintesi della macchina a stati interna al transponder del sistema RFID.

Per capire quindi quale famiglia logica, fra quelle rimanenti, convenga utilizzare, siamo passati ad eseguire delle nuove analisi partendo dai risultati riportati nei precedenti paragrafi. In particolare, volendo realizzare porte elementari che lavorano con frequenze dell’ordine di 1 MHz e tenendo conto della dipendenza quadratica della potenza dissipata dalla tensione di alimentazione (relazione 1.1),

abbiamo deciso di realizzare sistemi RING OSCILLATOR in logica Sub-pseudo-nMOS alimentandoli con una tensione pari a 0.5 V. In questo modo

infatti potremmo ottenere una riduzione notevole della energia dissipata nell’unità di tempo.

Quindi siamo passati ad analizzare il comportamento delle porte NOR e NAND a 2, 3 e 4 ingressi. In particolare, abbiamo realizzato dei sistemi RING OSCILLATOR ottenuti ponendo in cascata tre porte elementari dello stesso tipo. Sono state quindi ricercate le dimensioni minime da attribuire ai dispositivi in modo da ottenere una frequenza di oscillazione propria superiore o uguale a

1 MHz. Nel far questo però non ci siamo dimenticati di ricercare la minimizzazione dell’energia dissipata nell’unità di tempo.

I risultati ottenuti sono riportati nella tabella 2.21

Tipo di porta Wn (µm) Wp (µm) Periodo (µs) PDP (fJ) NOR a 2 Ingressi 1.05 2.45 0.88 1.87 NOR a 3 Ingressi 0.7 3.5 0.64 2.21 NOR a 4 Ingressi 1.4 6.3 0.725 4.93 NAND a 2 Ingressi 2.8 4.9 0.8 3.68 NAND a 3 Ingressi 1.75 2.8 1.5 3.45 NAND a 4 Ingressi 2.1 3.5 1.7 5

Tabella 2.21 Dimensioni minime per ottenere la minimizzazione della energia dissipata

nell’unità di tempo una volta fissata la tensione di alimentazione a 0,5V. L’unità di misura del periodo è µsec

Da notare come nel caso di sistemi realizzati con porte NAND a 3 e 4 ingressi, la frequenza di oscillazione libera sia inferiore a 1 MHz. Il motivo di questo risultato è legato al fatto che aumentare il numero degli ingressi significa inserire un nuovo transistore nMOS in serie a quelli già presenti. Quindi collegando assieme tutti i

terminali di gate, otteniamo principalmente un incremento della capacità di ingresso e per questo motivo una riduzione della frequenza di oscillazione libera. Per chiarire quanto appena affermato riportiamo l’espressione della frequenza di taglio:

C

R

f

in v p2

π

1

=

(2.7)dove Rv è la resistenza vista dalla capacità di ingresso Cin.

Quindi, in base ai risultati riportati nella tabella 2.21, abbiamo riscontrato l’impossibilità di realizzare le celle elementari in modo da poterle alimentare tutte con una tensione di alimentazione pari a 0,5 V in modo da ottenere una frequenza di funzionamento pari a 1 MHz.

Per questo motivo abbiamo scalato la tensione di alimentazione ponendola pari a 0,6 V e siamo passati ad analizzare i sistemi RING OSCILLATOR realizzati in logica Sub-CMOS e Sub-pseudo-nMOS per capire quale famiglia logica rispondesse in maniera ottimale alle specifiche di progetto.

Riportiamo nella tabella riassuntiva tabella 2.22 i risultati ottenuti dalle analisi svolte nei paragrafi precedenti

Logica Sub-CMOS Logica Sub-Pseudo-nMOS Tipo Porta Numero ingressi Wn (µm) Wp (µm) Periodo (µs) PDP (fJ) Wn (µm) Wp (µm) Periodo (µs) PDP (fJ) 2 1.4 4.2 0.3 1.67 1.4 4.2 0.06 2.34 3 1.4 4.2 0.6 2.16 1.4 4.2 0.08 1.867 NOR 4 1.4 5.6 0.9 1.867 1.4 4.2 0.01 2.367 2 1.4 4.2 0.15 0.967 1.4 4.2 0.07 2.33 3 2.8 8.4 0.22 1.25 1.4 2.1 0.16 1.44 NAND 4 1.4 4.2 0.3 0.345 1.4 2.1 0.2 1.74

Tabella 2.22 Energia dissipata nell’unità di tempo (fJ) e periodo di oscillazione (µsec) una volta

fissate le dimensioni minime (µm)

Come si può notare da una prima lettura dei risultati riportati in tabella 2.22, la logica Sub-CMOS risulta essere migliore sia da un punto di vista della minimizzazione della energia dissipata nell’unità di tempo che per la velocità di commutazione.

Le peggiori prestazioni della logica Sub-pseudo-nMOS sono legate al fatto che abbiamo dovuto dimensionare i dispositivi in maniera da ottenere una forma d’onda che rispettasse i limiti imposti in figura 2.1. Con tale scelta infatti, ci siamo trovati a dover scegliere la larghezza del canale dei transistori di tipo p in maniera tale da determinare un incremento eccessivo della energia dissipata nell’unità di tempo.

Possiamo quindi concludere che la realizzazione delle celle elementari in logica Sub-CMOS ci permette di ottenere prestazioni migliori.