Capitolo 8

Progetto del Nuovo

Sistema di Accensione

8.1 Introduzione

Dati i buoni risultati ottenuti con il nuovo moltiplicatore (Cap.7), per rendere il sistema più affidabile e quindi poterlo utilizzare per condurre dei test più accurati ed a frequenze più elevate, è stata progettata una nuova versione. L’obbiettivo principale è stato quello di realizzare il sistema su di un’unica PCB evitando i problemi derivanti dalla precedente struttura modulare (Par.5.5).

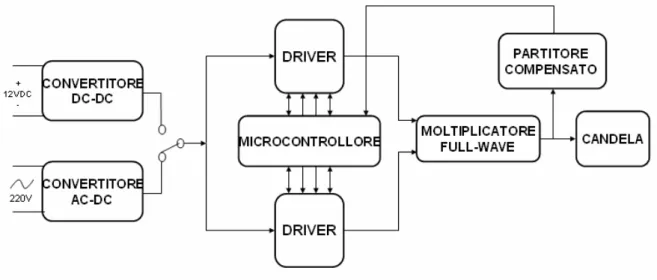

Dallo schema a blocchi di Fig.8.1 è possibile osservare la presenza di alcuni blocchi aggiuntivi rispetto all’architettura precedente (Fig.5.1). In particolare nel primo stadio è possibile utilizzare in maniera alternativa il convertitore AC-DC, già presente nel precedente sistema, ed un convertitore DC-DC. Inoltre è stato introdotto un secondo stadio DRIVER in modo tale da poter pilotare il moltiplicatore anche in configurazione FULL-WAVE.

Infine il partitore resistivo è stato sostituito da un partitore compensato che consente di trascurare gli effetti parassiti e ottenere una risposta in frequenza costante.

Figura 8.1 Schema a Blocchi del Nuovo Sistema di Accensione

8.2 Analisi dei Blocchi del Sistema

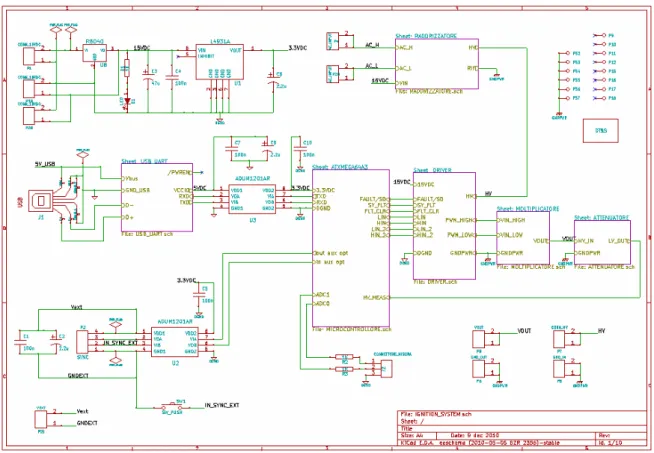

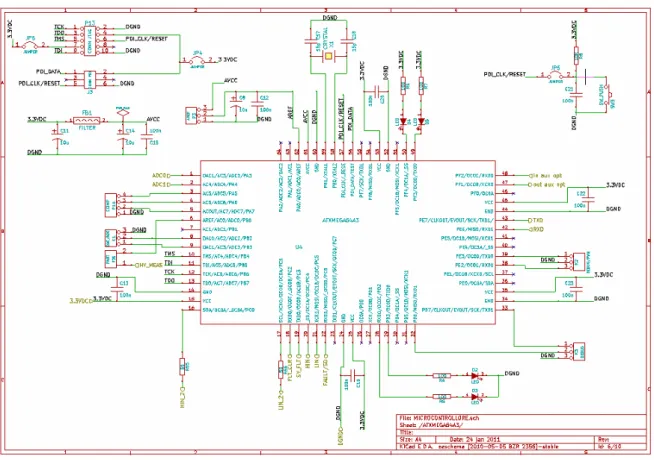

In Fig.8.2 è stato riportato lo schema elettrico del sistema di accensione. I blocchi gerarchici presenti in tale schema saranno analizzati nei paragrafi successivi.

Da fig.8.2 si può osservare la presenza di quattro riferimenti diversi all’interno del circuito: 1. USB - Ground;

2. Digital Ground; 3. Power Ground; 4. Ground Extern.

Il primo rappresenta il riferimento del circuito di interfaccia USB-UART, il quale è isolato dal resto del circuito grazie all’utilizzo dell’isolatore digitale ADUM1201 [20].

Il secondo è il ground della parte digitale del sistema, ovvero del circuito a microcontrollore e della sezione digitale dei due driver.

Il terzo rappresenta invece il riferimento della parte di potenza del e quindi della sezione ad alta tensione dei driver, dell’uscita del raddrizzatore, del moltiplicatore, della candela e del partitore di tensione compensato.

Dato che l’uscita del partitore deve essere connessa all’ADC del microcontrollore per valutare l’andamento della tensione sulla candela, il digital ground ed il power ground

devono inevitabilmente essere connessi insieme, per cui in realtà costituiscono un unico riferimento. Per evitare problemi di crosstalk da impedenza comune la connessione tra i due ground avviene in configurazione parallelo considerando come unico punto di massa il connettore di alimentazione (Par.8.3).

Infine il quarto riferimento è quello del sistema esterno che invierà il segnale di trigger al nostro sistema di accensione. Anche quest’ultimo, come il primo, risulta isolato dal resto del circuito sfruttando l’ADUM1201.

Figura 8.2 Schema Elettrico del Sistema di Accensione

8.2.1 Interfaccia USB-UART

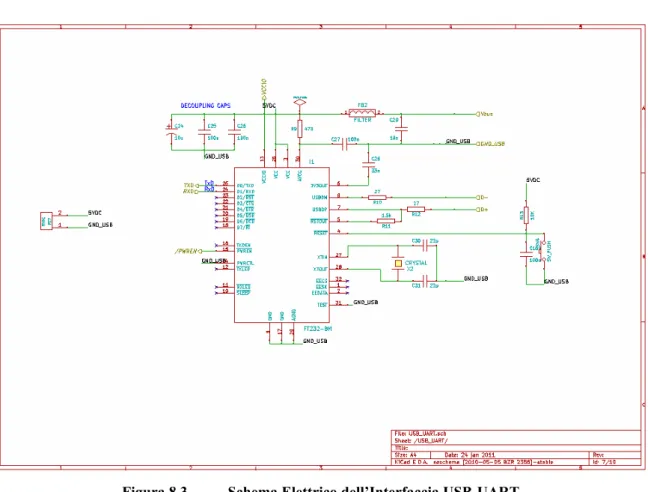

Per consentire la comunicazione tra microcontrollore e PC è stato utilizzato il circuito integrato FTDI232BM, il quale permette con l’aggiunta di pochi componenti di realizzare un’efficiente interfaccia USB-UART e quindi di poter collegare il sistema alla porta USB del PC. Il circuito utilizzato è stato riportato in Fig.8.3 e coincide con quello consigliato nel datasheet del dispositivo [21].

Figura 8.3 Schema Elettrico dell’Interfaccia USB-UART

8.2.2 Alimentazione dei Circuiti Digitali

Nel nostro sistema sono necessarie tre sorgenti di alimentazioni: 1. 5V per alimentare il circuito di interfaccia USB-UART;

2. 10 ÷ 15 V per alimentare i driver, il convertitore DC-DC ed eventuali dispositivi di raffreddamento;

3. 3.3 V per alimentare il microcontrollore.

La prima essendo il circuito di interfaccia USB-UART isolato dal resto del sistema, può essere tranquillamente fornita dalla porta USB del PC.

Per quanto riguarda le altre due si è scelto di utilizzare un'unica sorgente di alimentazione a 12÷15V e da questa ottenere i 3.3V utilizzando il regolatore di tensione L4931CD33 della ST Microelectronics [22].

In Fig.8.2 in alto a sinistra è possibile osservare lo schema del circuito di alimentazione. Si noti che la connessione tra la sorgente di alimentazione ed il sistema non è diretta ma avviene tramite l’RBO40 della ST Microelectronics [23]. Questo dispositivo è in grado di

proteggere il circuito a valle da sovratensioni o da inversione di polarità dell’alimentazione.

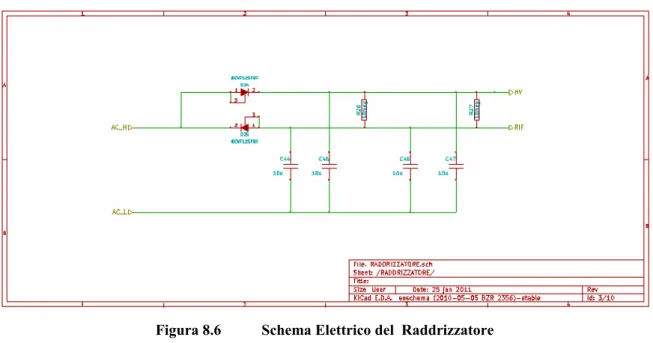

8.2.3 Convertitore AC-DC

Lo scopo di questo blocco è quello di convertire la tensione di rete domestica (220 Veff ) in una tensione continua regolabile nel range 0 ÷ 1200 V. Per fare questo viene utilizzata una coppia di trasformatori ed una coppia di raddrizzatori a singola semionda

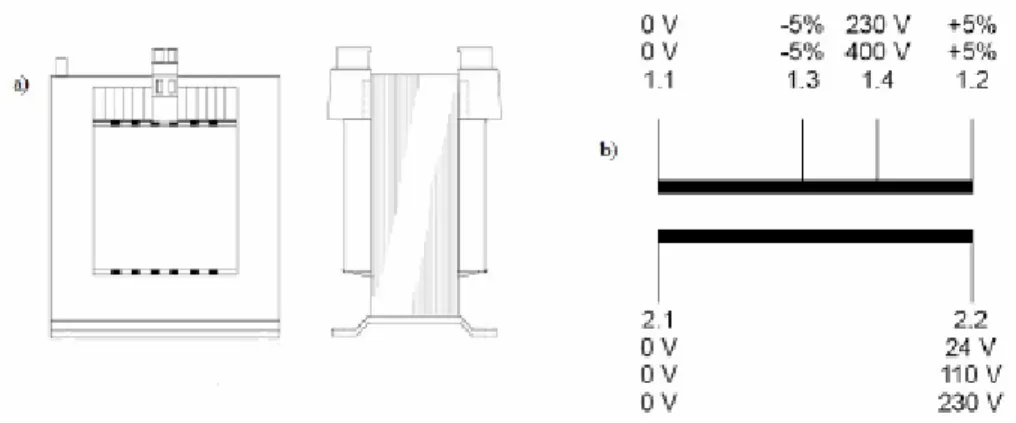

Il primo è un autotrasformatore a rapporto spire variabile (Fig.8.4) che permette di ottenere una tensione sul secondario nel range 0 ÷ 270 Veff [24].

Figura 8.4 a) Struttura dell’autotrasformatore, b) Schema delle connessioni, c) Specifiche

Il secondo trasformatore (Fig.8.5) ha un rapporto spire N2/N1 circa pari a 1,73 e quindi con

una tensione sul primario di 230 Veff consente di ottenere sul secondario una tensione di circa 400 Veff (≈ 600 Vdc) [25].

Infine grazie alla coppia di raddrizzatori a singola semionda, connessi come mostrato in Fig.8.6, è possibile ottenere tra i terminali HV e RIF una tensione continua di ampiezza pari al doppio del valore massimo della tensione in ingresso. Quindi essendo sul secondario del secondo trasformatore VDCmax ≈ 600 V, la tensione massima in uscita dal raddrizzatore sarà circa pari a 1200 V.

Figura 8.6 Schema Elettrico del Raddrizzatore

Parametro importante per la scelta dei diodi è la massima tensione inversa applicabile, nel nostro caso 1200 V. Per questo sono stati scelti i diodi 8EWF12SPBF della Vishay a montaggio superficiale [26], per i quali la massima tensione inversa è pari a 1200 V e la massima corrente è 8 A.

La massima tensione applicabile ai condensatori è invece pari a 600 V, di conseguenza è stato scelto il condensatore da 10 uF della serie MKP 338 4 X2 della BC Components, in grado di sopportare una tensione continua di 630 V [27].

Confrontando Fig.8.6 e Fig.5.2, si nota la presenza di due condensatori aggiuntivi montati in parallelo a quelli già esistenti nella precedente versione. La loro presenza è dovuta al fatto che essendo i due driver distanti nel layout (Fig.8.15, Fig.8.18), le coppie di condensatori disposte vicino ad ognuno di essi, garantiscono dei pozzi di corrente durante le commutazioni del segnale in uscita dai corrispondenti Half-Bridge.

Le resistenze hanno esclusivamente lo scopo di scaricare più rapidamente i condensatori a seguito dello spegnimento del sistema. Osservando Fig.8.6 è chiaro che, considerando spenti entrambe i diodi, tra i terminali HV e RIF si ha una Req = 5MΩ e Ceq = 10 uF.

Quindi la costante di tempo del transitorio di scarica è τ = 50 ms, maggiore del periodo del segnale di ingresso (50 Hz), questo garantisce che la presenza della resistenza non causi un elevato ripple sulla tensione continua d’uscita.

Il dimensionamento e la scelta delle resistenze è stato effettuato tenendo in conto anche della potenza che devono dissipare:

mW R Vdc Pd MAX MAX 144 10 10 1200 6 2 2 = ⋅ = =

La resistenza scelta è CRHV1206AF5M00FKFT, appartenete alla serie CRHV 1206 della Vishay e in grado di dissipare fino a 300 mW [28].

8.2.4 Convertitore DC-DC

La batteria di un motoveicolo o autoveicolo ha una tensione tipicamente compresa nel range 9 ÷ 14 Vdc, di conseguenza per ottenere una tensione di 1200 Vdc è necessario un convertitore di tensione continua (DC_DC). Il guadagno di tensione richiesto è circa pari a 100, per cui per realizzare il convertitore DC_DC, occorre utilizzare trasformatori con rapporto spire N2/N1

≈

100.Trasformatori di questo tipo sono utilizzati tipicamente nei circuiti inverter per lampade fluorescenti a catodo freddo o CCFL e per questo sono spesso chiamati trasformatori CCFL. Queste lampade sono tipicamente utilizzate per illuminare i display LCD e necessitano di una tensione sinusoidale dell’ordine dei KiloVolt per accendersi, successivamente la tensione scende ad un livello più basso. I circuiti utilizzati sono alimentati con tensioni continue nel range 5 ÷ 15 Vdc, a partire dalle quali i CCFL Transformers hanno il compito di generare la tensione di Start delle lampade.

Lo schema elettrico del convertitore DC_DC è riportato in Fig.8.7. Sfruttando l’avvolgimento di feedback del trasformatore è stato realizzato un circuito auto-oscillante, la cui frequenze di oscillazione è determinata dall’induttanza dell’avvolgimento primario (IN_H, IN_L) e dalla capacità connessa ai suoi capi (C167), secondo la relazione:

C L F PRI OSC ⋅ ⋅ ⋅ = π 2 1

Tipicamente si preferisce pilotare i trasformatori CCFL con semplici circuiti auto-oscillanti in quanto il range di frequenze di funzionamento è limitato (40 ÷ 100 kHz ) [38].

Per ottenere una tensione d’uscita variabile, il circuito auto-oscillante viene alimentato utilizzando il regolatore di tensione SPX29302 [37] che partendo dalla sorgente di alimentazione (9 ÷ 15V) permette di ottenere una tensione d’uscita regolabile tra Vref e Vin, con Vref = 1,24V e Vin tensione di alimentazione. Il regolatore è in grado di erogare una corrente massima di 3 A.

Infine a valle del trasformatore abbiamo un raddrizzatore a singola semionda realizzato con gli stessi componenti utilizzati per il raddrizzatore di Fig. 8.6. Notiamo la presenza di due diodi in serie in quanto essendo la massima tensione di uscita del trasformatore pari a 1200 V allora i diodi devono avere una massima tensione inversa di breakdown superiore a 2400 V. Analogamente i condensatori sono connessi in serie per garantire che la massima tensione ai loro capi non sia superiore a 630 V.

Per questa versione sperimentale del sistema i componenti del circuito auto-oscillante sono stati recuperati da un vecchio LCD.

Un problema che potrebbe sorgere utilizzando i trasformatori CCFL è legato alla capacità di compensare la carica persa dai condensatori del raddrizzatore durante una scarica, prima dell’avvento della successiva. Quindi un problema che diventa tanto più critico quanto più aumentano i giri del motore ovvero la frequenza delle scariche. Il problema sta nel fatto che per questi trasformatori tipicamente le massime correnti di uscita non superano le le centinaia di milliAmpere.

Per questo motivo è stata comunque prevista la presenza del convertitore AC-DC, descritto nel precedente paragrafo.

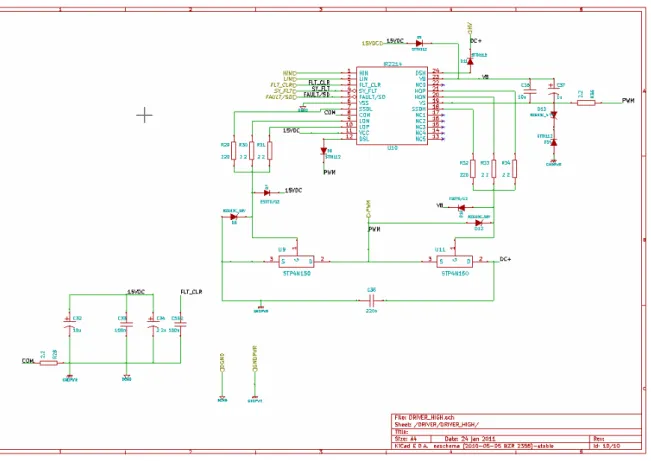

8.2.5 Half-Bridge Driver

I driver pilotando due Half-Bridge a Mosfet , consentono a partire dalla tensione continua generata dal convertitore AC-DC o DC-DC, di ottenere due onde PWM (Pulse-Width

Modulation) in controfase, con le quali è possibile pilotare il moltiplicatore Full-Wave.

Fig.8.8 mostra lo schema elettrico del circuito dell’ Half Bridge Driver.

Figura 8.8 Schema Elettrico del Circuito Driver Half Bridge

Il driver scelto è quello già utilizzato nel vecchio sistema, ossia il IR22141SS [29] della International Rectifier.

Per quanto riguarda la scelta e il dimensionamento dei componenti necessari per il corretto funzionamento di questo driver sono state seguite le linee guida riportate nel datasheet del componente e nelle Application Notes della International Rectifier [30] [31] [32]. Inoltre essendo questo un problema già affrontato nel precedente lavoro di tesi [15], al quale si rimanda per i dettagli, di seguito verrà semplicemente riportata una descrizione del funzionamento del circuito.

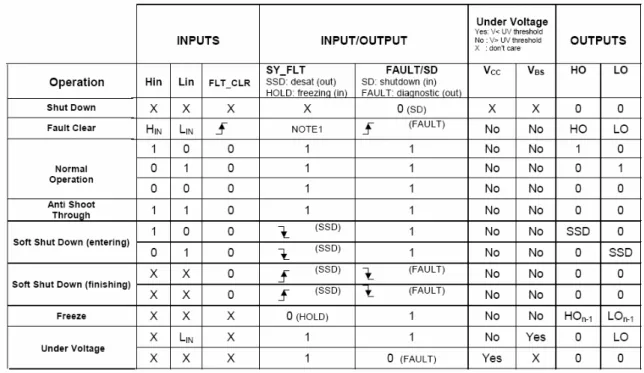

Il driver mette a disposizione cinque pin per il controllo tramite microcontrollore: HIN, LIN, /FAULT/SD, /SYS_FL, FLT_CLR. Sui primi due è necessario inviare le onde PWM che andranno a pilotare gli stadi di uscita del driver, e quindi i Mosfet dell’Half-Bridge. Gli altri tre, eccetto FLT_CLR, sono pin bidirezionali utilizzabili come output per verificare lo stato di funzionamento del driver oppure come input per imporre lo spegnimento del driver o il reset in presenza di un guasto. Fig.8.9 mostra tutte le possibili condizioni di funzionamento del driver.

Figura 8.9 Condizioni di Funzionamento del Driver IR22141

L’ Half-Bridge è realizzato con due Mosfet, i quali devono avere una tensione di Breakdown tra Drain e Source maggiore di 1200 V. Un altro parametro importante è la corrente di picco che il dispositivo può erogare, in quanto questa influirà sulla scelta dei valori delle capacità del primo stadio del moltiplicatore (Par.6.3).

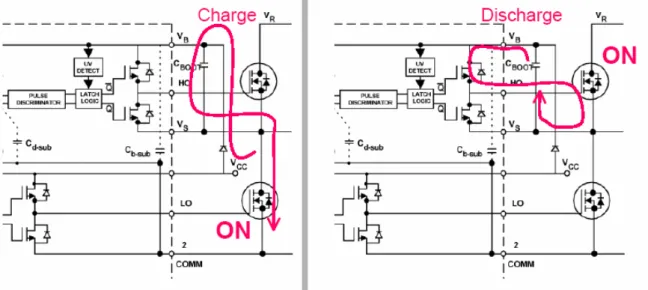

Il Mosfet utilizzato è l’STP4N150 [16], in grado di erogare una corrente continua di 4 A ed una corrente impulsata di 12 A. La massima tensione di Breakdown tra drain e source è pari a 1500 V. Ricordiamo che in un semiponte realizzato con entrambe i mosfet a canale N, affinché l’High Side (Mosfet Superiore) lavori correttamente in zona lineare, durante il periodo in cui è in conduzione, è necessario che la tensione di gate non sia riferita a massa

ma alla tensione di source del mosfet alto (1200 V). Quindi è necessario un traslatore di livello che permetta di ottenere Vg = Vgs + Vs.

Una tecnica molto utilizzata per pilotare gli Half-Bridge è quella di Bootstrap, di cui in Fig.8.10 è stato riportato uno schema di principio nel quale il traslatore di livello è integrato nel driver. Durante il periodo in cui il Low Side (Mosfet Inferiore) è in conduzione, la capacità di bootstrap viene caricata alla tensione Vgs. Dopo lo spegnimento del Low Side, grazie al traslatore di livello ed alla carica accumulata nella capacità di bootstrap è possibile mandare in conduzione l’High Side.

Il driver IR22141 permette l’utilizzo della tecnica di Bootstrap ed è quella adottata nel nostro circuito (Fig.8.8).

Figura 8.10 Pilotaggio dell’High Side con Tecnica di Bootstrap 8.2.6 Microcontrollore

I compiti del microcontrollore (μC) nel nostro sistema sono principalmente quattro: • Gestione della comunicazione con il PC;

• Pilotaggio del Driver;

• Rilevazione del segnale di Trigger proveniente dalla centralina elettronica; • Misura della tensione in uscita dal partitore compensato.

Il microcontrollore che utilizzeremo deve quindi essere dotato di: 1. Modulo USART;

3. Convertitore Analogico Digitale (ADC);

4. Almeno due Moduli per la generazione di forme d’onda per pilotare i due driver. Per quanto riguarda i punti 3 e 4 in realtà non basta che il μC sia dotato di queste periferiche ma è necessario che queste rispettino particolari requisiti.

In particolare i moduli in grado di generare onde PWM devono offrire la possibilità di poter variare la frequenza del segnale almeno nel range 100 kHz ÷ 1 MHz.

Per quanto riguarda l’ADC, invece, è necessario che la frequenza di campionamento del convertitore sia almeno pari ad 1Msample/s ed abbia una risoluzione di almeno 10 bit per poter misurare accuratamente l’andamento della tensione sul partitore compensato.

Infine bisogna considerare i requisiti di memoria richiesti. Per quanto riguarda la memoria flash di programma non ci sono vincoli stringenti, in quanto le operazioni svolte dalla μC non sono tante e quindi è presumibile che il firmware non sia particolarmente complesso. Pensando ad un sistema in grado di generare due scariche in corrispondenza del segnale di trigger inviato dalla centralina ed in grado di comunicare tramite PC se l’accensione è avvenuta correttamente ed in corrispondenza di quale scarica, è chiaro che non ci sono particolari richieste neanche per la memoria dati.

In realtà in fase di debug del sistema può essere utile memorizzare parte della tensione misurata dal μC per poi inviarla al PC su richiesta dell’utente. Inoltre durante il normale funzionamento si potrebbe pensare di memorizzare in un buffer circolare le informazioni relative alle mancate accensioni. In questo modo è possibile connettere il sistema al PC solo per ottenere le informazioni desiderate.

Ovviamente in questo caso il numero di informazioni che possiamo memorizzare è limitato dalla memoria dati del microcontrollore.

Se ad esempio si desidera salvare una finestra temporale della tensione misurata di almeno 10 ms occorre avere a disposizione almeno 10000 locazioni di memoria a 8 bit, ossia 10 kB, considerando che l’ADC campioni 1 Msample/s.

Per i motivi suddetti è stato scelto il microcontrollore ATXMEGA192A3 [33] della serie XMEGA A [34] della ATMEL.

Di seguito viene riportato un elenco di alcune caratteristiche del μC, in particolare quelle di principale interesse per la nostra applicazione:

• 192 kB di Memoria Flash; • 2 kB di EEPROM

• 16 kB SRAM;

• Massima Frequenza di Clock 32 MHz; • Tensione di Alimentazione 3.3 V; • Sette Moduli USART;

• External Interrupt su tutti i pin di I/O;

• Due convertitori ADC con risoluzione a 12 bit e frequenza di campionamento pari a 2 Msps;

• Sette Contatori a 16 bit in grado di genere onde PWM a frequenza massima pari a 5 MHz e Duty Cycle variabile;

• Interfaccia JTAG per il debug e la programmazione del μC; • Interfaccia PDI per il debug e la programmazione del μC;

In Fig.8.11 è mostrato lo schema elettrico della parte del sistema riguardante il microcontrollore. Date le molteplici risorse messe a disposizione dal μC scelto, sono stati previsti dei connettori per permettere l’utilizzo di alcune periferiche che potrebbero essere utili in futuro, tra cui il comparatore analogico, il convertitore digitale analogico (DAC) e un secondo modulo USART.

8.2.7 Moltiplicatore di Tensione

Nel Cap.6 analizzando il funzionamento del moltiplicatore di tensione half-wave si è constatato che le capacità di giunzione dei diodi in polarizzazione inversa sono causa di una riduzione, anche significativa, del guadagno del moltiplicatore. Per risolvere tale problema è stata proposta la soluzione con più diodi in serie. Inoltre è stata anche ricavata una configurazione ottimale per i valori assunti dalle capacità del moltiplicatore al fine di ridurre i tempi di salita della tensione d’uscita. I risultati sperimentali riportati nel Cap.7 hanno confermato quanto appena detto.

In questa nuova versione del sistema di accensione, essendo ancora una versione sperimentale, la progettazione del moltiplicatore è stata pensata principalmente con due scopi:

1. Testare la configurazione half-wave con tre diodi in serie e confrontare i risultati con quelli ottenuti utilizzando il moltiplicatore con due diodi in serie (Fig.);

2. Testare la configurazione Full-Wave.

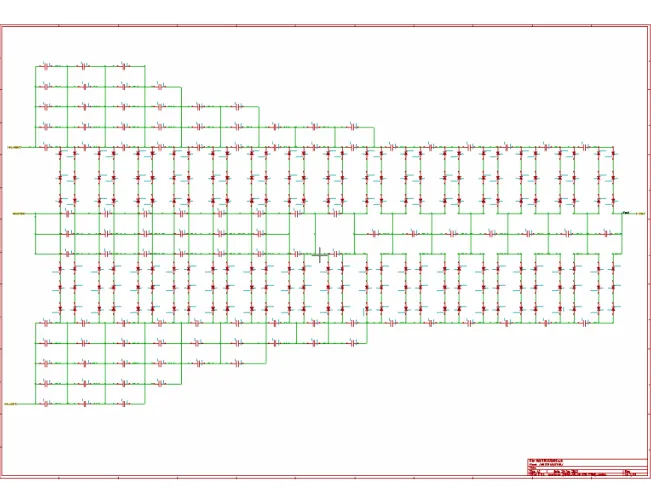

Come si può osservare dallo schema elettrico riportato in Fig.8.12, il moltiplicatore Full-Wave può essere visto come due Half-wave che condividono l’array di condensatori che determinano la tensione d’uscita del moltiplicatore.

Nel Par.6.5 è stato spiegato in maniera molto semplice che la configurazione Full-Wave permette di ridurre i tempi di salita della tensione d’uscita, proprio perchè i condensatori ricevono carica sia in corrispondenza dei gradini positivi che negativi.

Da Fig.8.12 è chiaro che questo vantaggio si paga in termini di maggiore ingombro ed anche di un costo più alto del sistema per l’aumento del numero di componenti necessari. Confrontando le misure sperimentali ottenute con il Full-Wave e quelle ottenute con il Half-wave sarà possibile decidere se l’entità del miglioramento sui tempi di risposta del sistema è tale da rendere il Full-Wave una valida alternativa.

I diodi utilizzati nel moltiplicatore sono sempre gli STTH112 della ST Mricroelectronics [18]. I condensatori sono stati scelti con dielettrico di tipo COG, che garantisce minori perdite rispetto agli altri dielettrici.

Figura 8.12 Schema Elettrico del Moltiplicatore

8.2.8 Partitore Compensato

Dovendo misurare la tensione presente sulla candela tramite l’ADC del microcontrollore, occorre adattare la dinamica di tale tensione a quella del convertitore.

Il μC ATXMEGA192A3 mette a disposizione una tensione di riferimento stabilizzata di 1V. Supponendo che la massima tensione di uscita dal moltiplicatore di tensione sia pari a 15 kV, è necessario realizzare un partitore di tensione con rapporto di partizione 1/15000. Utilizzando un semplice partitore resistivo, è possibile che a causa dei componenti parassiti, dovuti sia alle resistenze che alle connessioni, il segnale in uscita dal partitore non sia una replica fedele del segnale d’ingresso.

Il partitore di tensione compensato, invece, è caratterizzato da una risposta in frequenza costante, quindi è in grado di attenuare il segnale d’ingresso senza modificarne il contenuto frequenziale.

Figura 8.13 Schema Elettrico del Partitore Compensato

Lo schema elettrico del partitore realizzato è mostrato in Fig.8.13. Per analizzare la risposta in frequenza del circuito chiameremo Z1 l’impedenza complessiva tra i nodi HV_IN e LV_OUT, Z2 l’impedenza tra i nodi LV_OUT e GROUND.

La risposta in frequenza è data dalla seguente realzione:

) ( ) ( ) ( ) ( 2 1 2 jw Z jw Z jw Z jw H + =

L’impedenza Z2 è costituita dal parallelo di una resistenza R2 ed un condensatore C2:

2 2 2 2( ) 1 C jwR R jw Z + =

L’impedenza Z1 invece è costituita dalla serie di dieci paralleli tra una resistenza R1 ed un condensatore C1: 1 1 1 1

(

)

10

1

C

jwR

R

jw

Z

+

⋅

=

Quindi la risposta in frequenza sarà:

2 2 2 1 1 1 2 2 2 1 1 10 1 ) ( C jwR R C jwR R C jwR R jw H + + + ⋅ + =

2 1 2

10

)

0

(

R

R

R

H

+

⋅

=

, 1 2 1 10 ) ( C C C H + ⋅ = ∞Imponendo che H(0) = H(∞) si ricava la condizione affinché la risposta in frequenza sia costante: 2 1 1 2 C C R R =

Da Fig.8.13 si osserva che:

R1 = 5 MΩ ; C1 = 100 pF ; R2 = 3.3 kΩ ; C2 = 150 nF e quindi 15000 1 10 10 ) ( 1 2 1 2 1 2 2 1 1 2 ≅ + ⋅ ≅ + ⋅ = = C C C R R R jw H C C R R

In Fig.8.14 è stato riportato l’andamento del reciproco della risposta in frequenza ottenuto simulando il circuito con PSPICE. Nel grafico sono stati marcati i punti a 10 Hz e 1 MHz, si noti che la piccola variazione del rapporto di partizione è dovuta semplicemente all’impossibilità di reperire condensatori e resistenze che verifichino senza approssimazioni le relazioni precedenti.

Per la scelta dei componenti, oltre a rispettare i vincoli già discussi, sono stati seguiti i seguenti criteri:

1. Condensatori

• Massima tensione continua applicabile;

• Valori non inferiori alle decine di picofarad per trascurare gli effetti delle capacità parassite.

2. Resistenze

• Massima Potenza Dissipata;

• Massima Tensione continua applicabile.

Dalle considerazioni fatte è ovvio che tutta la tensione d’ingresso cade praticamente ai capi dell’impedenza Z1. Proprio per questo tale impedenza è stata realizzata dalla serie di dieci resistenze e condensatori in parallelo, in tal modo, supponendo che la tensione si ripartisca equamente, ai capi di ogni parallelo sarà presente una tensione massima di circa 1500 V. Quindi la massima potenza dissipata sulle resistenza sarà circa 450 mW.

• R1 = 5 MΩ, VISHAY TECHNO - CRHV1210AF5M00FKFT - RESISTOR, 5MR, 1210, HI V [27];

• R2 = 3.3 kΩ, PANASONIC - ERJT08J332V - RESISTOR, ANTI PULSE, 1206, 3k3, 5% [39];

• C1 = 100 pF, YAGEO (PHYCOMP) - CC1206JKNPODBN101 - MLCC, 1206, 100PF, 2 kV, NP0, 5% [40];

• C2 = 150 nF, AVX - 12065C154KAT2A - CAPACITOR, 1206, 150 nF, 50V, X7R [41].

•

Figura 8.14 Andamento del Reciproco della Risposta in Frequenza del Partitore Compensato

A basse frequenze l’impedenza del partitore è resistiva, costituita dalla serie delle resistenze. Quindi con i valori scelti si ha Req ≈ 50 MΩ, che rappresenta un carico sufficientemente elevato da non influenzare pesantemente il valore di regime della tensione di uscita del moltiplicatore. A frequenze elevate invece l’impedenza del partitore può considerarsi puramente capacitiva con Ceq ≈ 10 pF, un valore sufficientemente piccolo da poterne trascurare l’effetto sull’andamento della tensione d’uscita.

8.3 Progettazione e Realizzazione del Layout

Il sistema è stato realizzato su PCB a doppia faccia 300x300 mm con le seguenti caratteristiche:

• FR4 1.6 mm; • rame 35 μm;

• finitura superficiale HAL; • fori passanti metallizzati; • solder mask doppia faccia; • serigrafia su entrambe le facce.

Il layout completo è stato riportato in Fig.8.15, nella quale sono stati individuati i vari blocchi del sistema. Fig.8.16 e Fig.8.17 mostrano invece il Top Layer ed il Bottom Layer, rispettivamente. Il software utilizzato è Kicad versione 2005-05-05 BZR2356.

Come già accennato nel Par.8.2.7 è evidente che l’utilizzo del moltiplicatore Full-Wave causa un aumento dell’ingombro su scheda tutt’altro che trascurabile, dovuto non solo al maggior numero di componenti richiesti dal moltiplicatore stesso, ma anche per la necessità di utilizzare un secondo stadio driver e di conseguenza un secondo Half-Bridge. Al fine di ridurre i problemi di interferenze intra-system presenti nel vecchio sistema (Par.5.5), nel progettare il layout si è cercato per quanto possibile di partizionare il circuito, mantenendo separate le zone ad alta tensione ed alta frequenza dalle parti digitali del sistema.

In Fig.8.18 e Fig.8.19 sono state riportate le visualizzazioni 3D di entrambe le facce della scheda finita, ovvero includendo i package dei componenti utilizzati.

Come si può osservare dalle figure suddette, la maggior parte dei componenti soggetti ad elevate tensioni sono stati posizionati sul Bottom Layer, mentre nel top layer sono presenti i componenti digitali. In questo modo oltre a facilitare il debug della logica del sistema, è possibile condurre i vari test sul sistema limitando il rischio di scosse accidentali.

Aver partizionato il sistema offre anche la possibilità di ridurre i disturbi di tipo radiato ed anche di evitare problemi di crosstalk da impedenza comune. Infatti è stato possibile mantenere separate le connessioni di ground della parte riguardante la logica a microcontrollore e la parte ad alta tensione (driver – AC-DC – Moltiplicatore), utilizzando così un unico punto di massa all’interno del sistema in corrispondenza del connettore di alimentazione (Fig.8.15e).

Infine per ridurre i disturbi di tipo radiato sulle apparecchiature elettroniche circostanti (interferenze intersystem), è stato previsto il montaggio di un’apposita scatola di materiale metallico. Tale scatola non include tutto il sistema ma solo la parte interessata da segnali di ampiezza e frequenza elevate (Fig.8.22). La scelta di non schermare l’intero sistema deriva dal fatto che la soluzione di Fig.8.22 permette di ridurre non solo le interferenze sui sistemi circostanti ma anche all’interno del sistema stesso. In tal modo è possibile dapprima accertare la funzionalità del sistema e poi verificare in seguito la presenza di eventuali malfunzionamenti eliminando lo schermo.

Dal layout di Fig.8.16 si osserva che non è stato previsto un piano di massa dal lato opposto al moltiplicatore di tensione. Trattandosi di una vasta area della scheda è ovvio che un piano di massa avrebbe contribuito a ridurre l’entità dei disturbi radiati, però non si deve dimenticare l’effetto delle capacità parassite realizzate con le connessioni dell’altro lato.

Nel Cap.6 analizzando il funzionamento reale del moltiplicatore di tensione, si è visto come a causa delle capacità di giunzioni dei diodi in polarizzazione inversa (trascurabili in molte applicazioni), il guadagno reale del moltiplicatore subiva una significativa riduzione. Quindi il piano di massa non è stato previsto proprio per evitare che l’effetto delle capacità parassite potesse influire sui risultati ottenuti rendendoli non più confrontabili con quelli riportati nel Cap.7.

Per quanto riguarda il dimensionamento e le distanze delle connessioni è stato seguito per quanto possibile lo standard IPC-2221 [42].

Fig.20 e Fig.21 mostrano rispettivamente il Top layer ed il Bottom layer della PCB realizzata.

a

b

Figura 8.15 Layout Completo del Sistema: a) Circuito isolato per il segnale di trigger proveniente dalla centralina, b) Interfaccia USB-UART, c) Circuito digitale a Microcontrollore, d) Partitore di Tensione Compensato, e) Connettore di Alimentazione e circuito di protezione, f) Moltiplicatore di Tensione Full-Wave, g) AC-DC, DC-DC, Driver ed Half-Bridge.

c

d

f

e

Figura 8.18 Visualizzazione 3D del Top Layer

Figura 8.20 TOP Layer della PCB Realizzata