CAPITOLO 3

ANELLI DI SINCRONIZZAZIONE

In questo capitolo viene riportata una trattazione generale sull’importanza del recupero dei sincronismi di frequenza, fase e timing. Analizzeremo, da prima, le problematiche che si possono riscontrare nel caso di un non perfetto recupero dei parametri di sincronizzazione, per poi passare ad uno studio particolare sull’architettura dei circuiti che vengono utilizzati nella maggior parte delle applicazioni.

3.1 Cenni preliminari sui sincronizzatori di portante e di timing

Il compito di un qualsiasi ricevitore è quello di compiere una corretta rivelazione dei simboli d’informazione trasmessi. Per adempire in maniera esatta al suo dovere, bisogna che il ricevitore sia a conoscenza di alcuni parametri del segnale detti di sincronizzazione.

L’argomentazione con cui si cercherà di spiegare la necessità ed il modo di ottenere i sincronismi verrà eseguita nel caso più generale possibile, senza andare nel dettaglio delle architetture adoperate dal sistema GALILEO, che saranno esposte invece nel capitolo 5.

Per effettuare una demodulazione coerente è necessario disporre al ricevitore di una sinusoide con la stessa frequenza e stessa fase della portante del segnale in arrivo.

Solitamente l’oscillazione locale non ha dei riferimenti ideali (coincidenti con quelli della portante) e quindi si rende indispensabile l’utilizzo di sincronizzatori di portante per calcolare e compensare gli errori di fase e frequenza.

Per sistemi che utilizzano segnali con la tecnica Direct Sequence Spread Spectrum si deve inoltre provvedere all’allineamento del codice locale con quello del segnale ricevuto. Imprecisioni sulle stime dei parametri di sincronizzazione possono avere conseguenze gravi sul corretto funzionamento del ricevitore.

Supponiamo ad esempio di aver trasmesso un segnale a RF esprimibile con

0 0

( ) ( ) cos(2 ) ( ) (2 )

RF I Q

r t =r t ⋅ π f t −r t sen⋅ π f t (3.1.1)

il cui inviluppo complesso è dato da

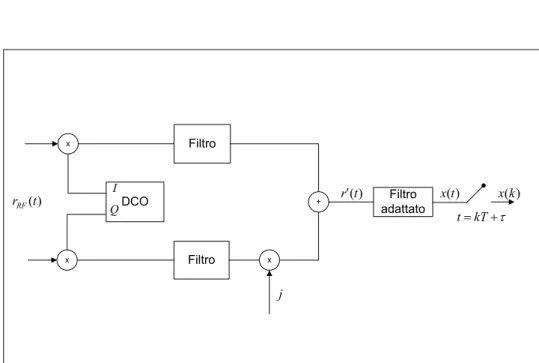

( ) I( ) Q( ) r t =r t + ⋅j r t (3.1.2) Filtro Filtro DCO Filtro adattato I Q ( ) RF r t j ( ) x t t kT= +τ ( ) x k ( ) r t′ x x x +

Figura 3.1.1 Front end ricevitore

Ipotizzando che i riferimenti dell’oscillatore locale non siano esattamente sincroni con la portante, al ricevitore abbiamo

cos(2π f tOL −θ) (3.1.3)

(2 OL )

sen π f t−θ (3.1.4)

in cui si può notare l’offset di frequenza ν = f0− fOL e quello di fase θ . Una volta demodulato, il segnale presenta la seguente forma

L’effetto dell’errore di frequenza e fase sui simboli di modulazione del segnale in banda base ( )r t è quello di una rotazione di un angolo pari a 2πν θt+ .

Nei paragrafi successivi esporremo il funzionamento dei circuiti, atti al calcolo ed al recupero dei vari sincronismi.

3.2 Frequency Lock Loop (FLL

)

Il compito di un sincronizzatore di frequenza ad anello chiuso è quello di fornire una stima che si deve aggiornare ed autocorreggere dell’offset di frequenza tra la portante ed i riferimenti locali del ricevitore e di compensare questo errore.

Nel caso generale di un ricevitore che opera senza informazioni sul timing e con una trasmissione continua di dati non noti, uno schema a blocchi di un FLL (Frequency Lock

Loop) è mostrato in Fig. 3.2.1

FDD x LOOP FILTER NCO ( ) x t ( ) x k′ e k( ) ˆk

υ

k j e− ϕ 1Ts 1Ts =Q T T = tempo segnalazione ( ) x k Figura 3.2.1 FLLQuesto tipo di circuito è largamente utilizzato per un’acquisizione grossolana della frequenza della portante; questo indica che si possono compensare errori anche piuttosto

elevati, lasciando però delle piccole imprecisioni sulla stima (frequency jitter) che verranno recuperate negli stadi successivi del ricevitore con altri tipi di circuiti (ad esempio un PLL del 2° ordine).

Come si intuisce dalla Fig. 3.2.1, il segnale, demodulato e filtrato, viene campionato con una frequenza Q volte superiore alla symbol-rate. Questi campioni del segnale ricevuto vengono corretti in frequenza dall’uscita dell’NCO e mandati in ingresso al FED (Frequency Error Detector) che provvede a generare un segnale errore (e kT dipendente ) dalla differenza tra il valore vero dell’offset di frequenza υ e quello della sua stima al passo corrente ˆυk .

Il segnale errore (e kT viene destinato ad un filtro ricorsivo del primo ordine che ) implementa l’equazione

1

ˆk ˆk e kT( )

ν + =ν − ⋅γ (3.2.1)

in cui γ è un parametro, detto step-size, che consente di controllare l’entità della correzione della stima e di cui ci occuperemo in seguito.

Il segnale in uscita dal filtro entra poi nell’NCO (Numeric Controlled Oscillator) che produce il segnale e−jθk, adibito alla correzione in frequenza del segnale ricevuto, in cui

1 2 ˆ

k k kT

θ =θ − + πν (3.2.2)

Cerchiamo adesso di capire come è possibile ottenere una buona stima di ˆυk tramite il circuito appena descritto.

Supponiamo di staccare dalla Fig. 3.2.1 l’NCO insieme ad il loop filter e di pilotare la correzione di frequenza sui campioni del segnale ricevuto con un esponenziale a frequenza fissa ˆυ come esposto in figura sottostante

FED Media x ( ) x t x k( ) x k′( ) ˆ 2 j T e− πν ( ) e k S f

( )

dFigura 3.2.2 Schema a blocchi per calcolo curva ad S

( )d

S f non è altro che la media del segnale errore (e kT condizionata al valore fissato ˆ) υ dove fd = − è la differenza tra l’offset reale e la sua stima fissata. υ υˆ

In termini matematici

{

ˆ}

( )d ( ) |

S f =E e kT υ (3.2.3)

Si intuisce che (e kT , indipendentemente dall’algoritmo utilizzato per essere generato, ha ) una media che dipende da f che in particolare ha l’andamento generale di figura 3.2.3 d

Essa viene chiamata, per ovvie similitudini grafiche, curva ad S e come si vede passa dall’origine estendendosi su un intervallo fd∈ −

(

F F,)

detto campo d’aggancio delsincronizzatore.

La pendenza attorno all’origine della curva ad S viene indicata con Aυ e può essere relazionata con altri parametri del sistema nel seguente modo

4 update A B T υ υ γ⋅ ≈ (3.2.4)

in cui si nota la presenza della banda d’anello Bυ e del passo d’aggiornamento della stima

update

T .

Ad esempio, per una modulazione BPSK, possiamo scegliere di implementare il segnale errore nel seguente modo

{

2}

( ) ( ) ( 1)

e kT = ℑm x k x k⎡ ⋅ ∗ − ⎤

⎣ ⎦ (3.2.5)

Si dimostra che nell’intorno dell’origine (nel campo d’aggancio) la curva ad S è assimilabile ad una sinusoide con periodo 2f . d

Se adesso chiudiamo l’anello, come in figura (3.2.1), i vari parametri del circuito variano ad ogni istante di aggiornamento della stima e, quindi, la frequenza istantanea dell’NCO è ˆυk e la media del segnale errore è data da S

[

υ υ− ˆk]

, essendo l’errore di stima proprioˆ ( )

d k

f k = − . υ υ

Per un corretto funzionamento dell’FLL bisogna che, dopo un transitorio, il segnale f k d( ) tenda a zero perchè chiaramente questo implicherebbe che la stima dell’offset coincida quasi del tutto con il reale scostamento in frequenza tra portante ed oscillatore locale. Tramite alcuni passaggi matematici che tralasciamo, è possibile scrivere un’espressione ricorsiva dell’errore di stima data da

[

]

( 1) ( ) ( )

d d d

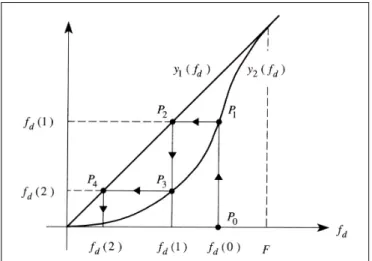

Se ci apprestiamo a graficare la curva data dalla (3.2.6) insieme alla bisettrice del 1° e 3° quadrante ( ( )y fd = fd), come visualizzato in figura (3.2.4), ci accorgiamo immediatamente di come funziona il circuito di sincronizzazione al passare del tempo.

Infatti, ammettendo che l’errore di stima iniziale fd(0) sia all’interno del campo d’aggancio del sincronizzatore, f k tende a decrescere fino ad oscillare intorno allo zero. d( )

Graficamente, questo concetto, è ben visibile andando ad analizzare la traiettoria dei punti P0, P1, P2, .... della figura 3.2.4

Figura 3.2.4 Soluzione grafica dell’equazione 3.2.6

La velocità con cui il sistema riesce ad andare a regime, ovvero quanti passi occorrono per far annullare il segnale f k , viene misurato tramite il tempo d’acquisizione. d( )

Un parametro fondamentale che gestisce e controlla la lunghezza del transitorio è lo step-size.

Ricordando la (3.2.1) e la (3.2.6) sembrerebbe conveniente scegliere un valore di γ elevato poichè, in questo modo, le correzioni ad ogni passo di aggiornamento sarebbero più grandi e si raggiungerebbe velocemente il valore da stimare.

Nella realtà però, la stima, ad esempio di ˆυk, oscilla a regime attorno al valore vero υ e l’entità di queste fluttuazioni cresce all’aumentare dello step-size.

E’ chiaro, dunque, che occorre un compromesso tra acquisizioni rapide e precisione di stima a regime.

Il tempo di acquisizione dipende anche dal valore iniziale dell’errore di stima fd(0) perchè si capisce che il transitorio sarà tanto più lungo tanto più fd(0) è vicino ai bordi della zona d’aggancio (fenomeno dell’hang-up ).

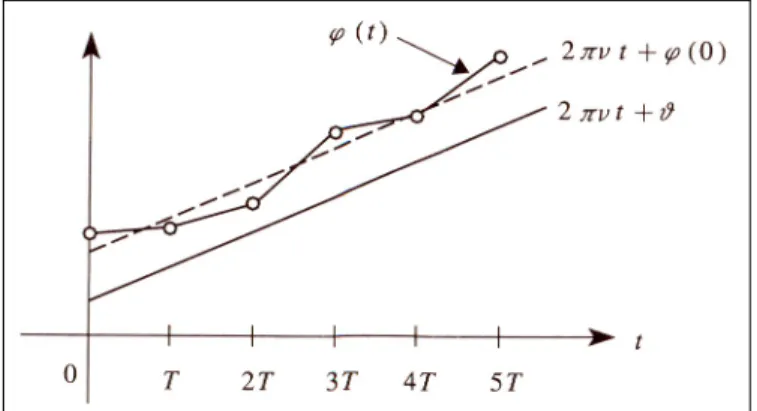

Infine, per comprendere meglio quanto detto finora, possiamo studiare il comportamento della fase generata dall’NCO θk.

Essa, ad ogni istante di update, varia di una quantità pari a 2πυˆkT ; se fosse ˆυk ≡ , la υ fase, al variare del tempo, sarebbe una retta parallela a 2 tπυ che è quella generata

dall’errore reale in frequenza; siccome in pratica la stima ˆυk oscilla attorno al valore υ si ottiene una spezzata che approssima la rampa ideale.

Figura 3.2.5 Andamento della stima di ϕ

3.3 Phase Lock Loop (PLL)

Anche in questo caso cercheremo di effettuare un’analisi del tutto generale di un ricevitore che ha già compensato, con un FLL, l’errore di frequenza e che non conosce i simboli trasmessi.

Sotto queste ipotesi uno schema molto utilizzato per realizzare la stima della fase della portante è il tradizionale PLL (Phase Lock Loop) del secondo ordine come esposto in figura 3.3.1

x Look-up table PED Loop filter Hard decoder ( ) m k ˆ k

θ

ˆ k j e− θ ( ) e k k c ( ) w k Figura 3.3.1 PLLSi tratta di un sistema ad anello chiuso, che prende anche il nome di anello digitale di Costas, il quale permette non solo il recupero della fase della portante, ma anche l’eliminazione di un eventuale piccolo residuo di errore di frequenza tra portante ed oscillatore locale.

Come si vede dalla figura 3.3.1 il segnale ( )m k , che proviene dall’unità di compensazione dell’errore di frequenza, viene moltiplicato per il segnale in uscita dalla look-up table che contiene la stima corrente della fase della portante.

Si genera così il segnale ( )w k che viene spedito ad un decisore hard per fornire la stima del simbolo ˆc . k

Il blocco denominato PED (Phase Error Detector) utilizza ( )w k e ˆc per creare il segnale k errore dato da

{

ˆ}

( ) ( ) k

e k = ℑm w k c⋅ ∗ (3.3.1)

L’equazione (3.3.1) è l’ingresso del filtro ricorsivo che sarà del secondo ordine per aggiustare l’eventuale offset di frequenza residuo all’uscita dell’FLL e che implementa le espressioni

ˆ(k 1) ˆ( )k ( )k

θ + =θ +µ (3.3.2)

(k 1) ( )k (1 ) (e k 1) e k( )

x + x + x + k e

γ

ρ

kµ

ˆ kθ

1 Z− 1 Z−Figura 3.3.2 Schema a blocchi del filtro del 2° ordine

Indicando con B TL update la banda normalizzata d’anello ed assumendo che B TL update 1 si può dimostrare che

2 4 1 4 L update B T ρ ζ = + (3.3.4) 2 2 16 (1 4 ) L update B T A ζ γ ζ = + (3.3.5)

in cui A è la pendenza attorno all’origine della curva ad S, ζ è il loop damping factor (fattore di sovraelongazione) e γ è lo step-size.

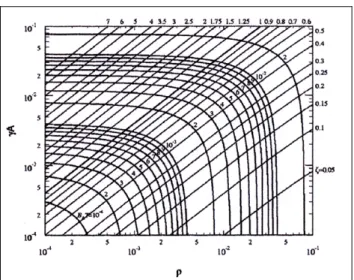

La scelta dei parametri appena mostrati, per una creazione di un modello funzionale del sincronizzatore, può essere fatta attraverso l’esame della figura (3.3.3)

Figura 3.3.3 PLL chart

Fissando un valore di ζ ed uno di B TL update, infatti, si individua un punto sul grafico da cui è possibile ricavarsi il valore dell’ascissa data da ρ e dell’ordinata data da Aγ ; in altri termini la figura (3.3.3) ci permette di ottenere la coppia

(

ρ γ, A)

partendo dalla coppia di valori(

ζ,B TL update)

.Infine, la stima della fase della portante, che si autocorregge nel tempo ad ogni istante di aggiornamento, entra nella look-up table che si costruisce il segnale e−j kθˆ( ) per compensare l’errore di fase nel segnale ( )m k .

Come con l’FLL, per studiare le proprietà di acquisizione dell’anello di Costas si ricorre all’analisi della curva ad S, andando a staccare, nello schema di figura (3.3.1), il filtro e la look-up table ed andando a pilotare il moltiplicatore con un esponenziale a fase fissata. Se indichiamo con ϕ θ θ= − la differenza tra la fase della portante e la sua stima ed ˆ andiamo a mediare il segnale prelevato all’uscita del PED otteniamo la curva ad S definita come

{

}

( ) ( ) |

S ϕ =E e k ϕ (3.3.6)

Se chiudiamo l’anello, i parametri del sistema variano con il tempo ad ogni istante di aggiornamento e si può dimostrare che il segnale differenza può essere implementato come

[

]

(k 1) ( )k S ( )k

ϕ + =ϕ − ⋅γ ϕ (3.3.7)

La (3.3.7) è formalmente identica alla (3.2.6) utilizzata per l’FLL e, quindi, può essere studiata con i metodi utilizzati nel paragrafo 3.2.

Anche ora ci aspettiamo che, partendo da un errore di fase arbitrario (0)ϕ , il segnale ( )ϕ k tenda a zero dopo un certo tempo.

Equivalentemente, affinchè la (3.3.7) abbia una soluzione di equilibrio, occorre che ( ) 0

S ϕ = .

Esiste però una differenza sostanziale tra questo caso e quello esaminato per l’FLL: nel PLL la curva ad S è periodica e quindi può presentare più punti stabili (ovvero più nulli) in regioni diverse da quella d’aggancio.

Il risultato è che la curva ad S, a seconda della modulazione usata, interseca in varie zone l’ascissa, ottenendo così, più punti di equilibrio.

Ad esempio per una BPSK, se andiamo a graficare la (3.3.7) insieme alla bisettrice del 1° e 3° quadrante, abbiamo la situazione mostrata in figura 3.3.4

Figura 3.3.4 Soluzione grafica dell’equazione 3.3.7

Con le medesime considerazioni usate nel sottocapitolo 3.2 possiamo notare che, se l’errore di fase iniziale (0)ϕ ha un valore ,

2

π π

⎤ ⎤

Questo comporterebbe un errore sistematico al decisore sulla scelta dei simboli trasmessi e si dice che il sincronizzatore ha un’ambiguità di fase di π .

Fisicamente l’ambiguità nasce dal fatto che una costellazione BPSK rimane immutata se viene ruotata di π e, quindi, questo fa pensare che un fenomeno analogo possa essere esteso a tutte le costellazioni M-PSK che hanno un’ambiguità di 2 Mπ e a quelle M-QAM che hanno un’ambiguità di

2

π

.

Generalizzando possiamo affermare che i punti di equilibrio stabili sono quelli in cui la pendenza di ( )S ϕ è positiva e dunque si trova che per modulazioni M-PSK abbiamo M punti stabili (M zeri della curva ad S con pendenza positiva) mentre per modulazioni M-QAM abbiamo 4 punti stabili.

Per risolvere le ambiguità di fase che si conseguono utilizzando un sincronizzatore di fase ad anello chiuso possiamo far riferimento a due tecniche.

La prima possibilità è quella di adoperare una parola unica cioè un pacchetto di simboli noti inserito tra i dati trasmessi; in questo modo il ricevitore, che conosce la parola unica, si accorge se c’è stata o meno ambiguità di fase nel momento in cui va ad effettuare la decisione sui simboli.

Un’altra possibilità può essere l’impiego della decodifica differenziale in cui i simboli di modulazione d sono legati a quelli d’informazione k b dalla relazione k

1

k k k

d =d − ⋅ (3.3.8) b

Per quanto riguarda le considerazioni sulla scelta dello step-size e sull’hang-up rimandiamo al paragrafo 3.2 dal momento che le valutazioni fatte per l’FLL valgono nello stesso modo anche per l’anello di Costas.

3.4 Delay Lock Loop (DLL)

Nei sistemi a spettro espanso, come quelli satellitari di posizionamento, è necessario eseguire il tracking del codice ovvero il ricevitore deve essere in grado di costruirsi localmente una replica della sequenza di spreading perfettamente allineata con quella del segnale in arrivo.

In questo modo il sistema può ricavarsi il segnale del singolo utente, distinguendolo dagli altri, e può così effettuare una corretta demodulazione dei simboli di navigazione.

Si capisce dunque l’esigenza di un circuito di sincronizzazione di timing che riesca a stimare il ritardo temporale del segnale al ricevitore e che allinei di conseguenza le repliche del codice dei singoli utenti.

Tale sistema viene implementato da un circuito ad anello chiuso che prende il nome di DLL (Delay Lock Loop) e che ha un’architettura diversa da quella convenzionale per sistemi a banda stretta.

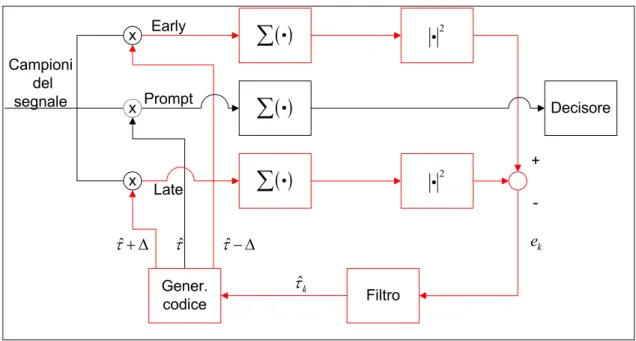

In figura 3.4.1 viene mostrato il diagramma a blocchi

Filtro Decisore ˆ τ ˆ τ+ ∆ τˆ− ∆

( )

∑

i( )

∑

i 2 i 2 i( )

∑

i Early Late Prompt k e ˆk τ x x x Gener. codice + -Campioni del segnaleFigura 3.4.1 DLL non coerente

Il segnale in ingresso al ricevitore viene convertito in banda base e campionato; il flusso di campioni così ottenuto è poi inviato su due rami distinti e moltiplicato per due sequenze di spreading generate localmente.

Quest’ultime sono shiftate volutamente rispetto al codice di riferimento di una quantità indicata con ±∆ , ottenendo rispettivamente il late code ed l’early code.

Il segnale correlato in uscita dal moltiplicatore entra nel sommatore che provvede a fare una media su M campioni.

Indicando con εk =τ τˆk − la differenza tra stima e valor vero del ritardo del segnale ricevuto, la curva ad S del DLL è ricavabile come mostrato nei sottocapitoli precedenti graficando il segnale S

( )

ε così definito( )

{

k|}

S ε =E e ε (3.4.3)

Figura 3.4.2 Curva ad S DLL non coerente

L’errore pilota il filtro del 1° ordine che gestisce l’update della stima del timing tramite l’equazione

1

ˆk ˆk ek

τ + =τ − ⋅ (3.4.1) γ

dove γ è anche ora lo step-size.

Infine il ritardo stimato interagisce con il generatore locale di codice il quale aggiusterà lo shift sulle repliche delle sequenze di spreading sui rami early e late.

Come si può notare dalla figura 3.4.1, esiste anche un terzo ramo detto prompt che non è interessato al calcolo del segnale errore e, quindi, alla stima di ˆτk, ma che viene messo in ingresso ad un decisore a soglia per effettuare la rivelazione dei simboli d’informazione una volta recuperati i sincronismi di fase e frequenza.

Naturalmente, anche in questo caso, affinchè si abbiano delle corrette decisioni, deve passare un certo transitorio in maniera tale che la stima sul ritardo si stabilizzi e oscilli

attorno al valore vero poichè anche il prompt è pilotato dal generatore di codice e quindi da ˆτk.

La durata del tempo d’aggancio del sincronizzatore è tenuta sotto controllo dalla scelta della banda d’anello tramite l’equazione

(

)

2 2 L update A B T A γ γ ⋅ = − ⋅ (3.4.2)dove Tupdate è il passo d’aggiornamento della stima ed A è la pendenza intorno all’origine della curva ad S.

E’ interessante, inoltre, rilevare che un sistema di questo tipo è insensibile ad un eventuale errore sui riferimenti della portante a causa dei moduli quadri presenti nella formula dell’errore e e che dunque non è necessario avere già estratto la stima di fase e k

frequenza della portane. Per tale motivo il DLL presentato è definito non-coerente.

Questo ci permette di utilizzare il DLL prima di aver stimato e recuperato fase e frequenza.