3 Bassa potenza con Synopsys.

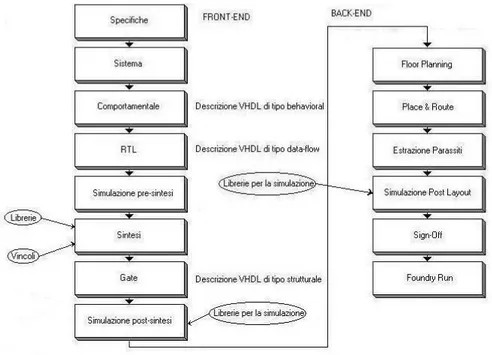

Per far fronte all’aumentare della complessità del progetto di sistemi elettronici sono stati sviluppati dei linguaggi di descrizione hardware (HDL) che servono per descrivere l’architettura e la funzionalità di un qualsiasi circuito elettronico a più alti livelli di astrazione. In progetti complessi, dove spesso cooperano più progettisti, è infatti di grande vantaggio utilizzare un approccio progettuale di tipo top-down, dove si comincia dalle decisioni a livello di architettura generale del sistema, fino al progetto dettagliato delle singole sottoparti. Il VHDL (Very High Speed Integrated Circuit HDL) e il VERILOG sono gli HDL più diffusi attualmente e si sono affermati come standard di livello internazionale. Un possibile diagramma di flusso per la progettazione VHDL può essere così fatto:

Si cerca ora di individuare i livelli ai quali intervenire per ridurre la potenza. Ad ogni livello del flusso, il progettista di sistema deve saper scegliere fra varie soluzioni progettuali quella che più lo soddisfa in termini di potenza, prestazioni, e area. Per far ciò, data la complessità dei circuiti digitali di oggi, diventa indispensabile l’uso di strumenti CAD che riescono a stimare la potenza dissipata ai vari livelli del flusso di progetto, in modo che non ci sia il rischio di dover ritornare troppo indietro nel flusso per apportare eventuali modifiche.

L’ambiente di sviluppo software della Synopsys offre vari strumenti per la progettazione di circuiti digitali integrati tali da coprire i vari passi del progetto [4]. Oltre alle classiche funzioni per la descrizione tramite il linguaggio VHDL, simulazione e sintesi logica, offre anche la possibilità di analizzare le caratteristiche dei circuiti integrati in termini di area, frequenza di lavoro, potenza ecc.

Il tool della Synopsys che comprende le metodologie di analisi e ottimizzazione in potenza per tutto il flusso di progetto (dal RTL-level al gate-level) è il Power Compiler.

3.1 Progettazione low-power con il tool Power Compiler.

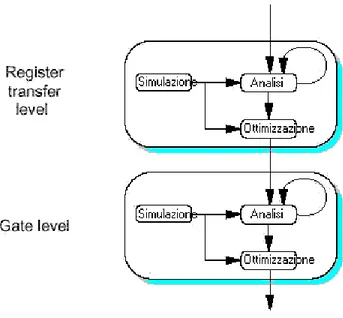

Durante l’intero flusso di progetto che ci porta dal RTL-level fino al gate-level, prima di passare ad un livello di astrazione più basso occorrono i passi di simulazione, analisi e ottimizzazione. Infatti la simulazione fornisce la switching activity da cui i successivi passi di analisi e ottimizzazione traggono le informazioni necessarie per raffinare il progetto prima di passare al livello di astrazione più basso:

Figura 3-2 Flusso per la potenza.

In generale, più è alto il livello di astrazione in cui si opera, maggiore è il risparmio di potenza che si può ottenere. Infatti le scelte fatte ai livelli più alti hanno un impatto maggiore sull’implementazione finale.

La simulazione è eseguita nell’ambiente VSS (VHDL System Simulator), può essere fatta a livello RTL oppure a livello gate e genera un file chiamato “back-annotation file” che contiene le informazioni di switching activity del progetto. Usando il comando “read_saif”, viene letto questo file e vengono annotate le sue informazioni sul progetto RTL o gate -level.

La simulazione RTL ha bisogno di un file in ingresso chiamato “forward-annotation file” che contiene le direttive per determinare quali elementi del progetto devono essere monitorati durante la simulazione.

Anche la simulazione gate-level può utilizzare un forward-annotation file che viene creato col comando lib2saif e contiene informazioni diverse dal caso precedente. Si tratta di informazioni che vengono ricavate dalla libreria tecnologica, ad esempio modelli state-depe ndent e path-dependent delle celle. Esse tengono conto della dipendenza della switching activity dallo stato in cui si trova la cella e dalla differenza dei percorsi logici tra ciascun ingresso e l’uscita della cella.

Poiché molti progettisti usano la simulazione RTL per verificare la funzionalità del progetto prima della sintesi, la cattura della switching activity tramite questa simulazione RTL ci permette di ottenere in modo gratuito dei veloci risultati (anche se poco accurati) e di esplorare i trade -off di progetto (ad es. quale modulo consuma di più, quale consuma di meno ecc.). Più tardi nel flusso di progetto si può sfruttare la maggiore accuratezza della simulazione gate -level che però impiega maggiori tempi di esecuzione. L’analisi della switching activity tramite simulazione gate-level è molto accurata: la potenza media che si ottiene è all’interno del 10-25 % dell’analisi in potenza fatta con un simulatore transistor-level come SPICE. Questa accuratezza dipende dai modelli di simulazione per le interconnessioni, il glitch, i ritardi delle porte ecc.

L’analisi della potenza si può fare a livello RTL oppure a livello gate. L’analisi a livello RTL avviene tramite l’RTL Power Estimator, che utilizza i dati prodotti dalla simulazione RTL e permette un’analisi della potenza molto veloce.

L’analisi a livello gate usa la switching activity prodotta dalla simulazione gate-level, oppure se si vuole un’analisi più veloce si può lanciare una simulazione RTL per catturare la switching activity degli ingressi e delle uscite primarie degli elementi sequenziali e poi il Power Compiler propaga automaticamente l’attività di commutazione nelle porzioni del progetto non annotate.

L’ottimizzazione può essere effettuata a livello RTL usando le tecniche del clock gating e operand isolation, oppure a livello gate che può simultaneamente tener conto dei vincoli di potenza, area e timing.

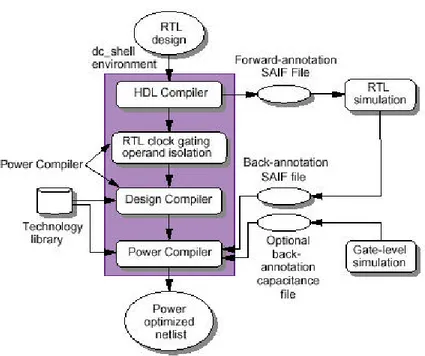

In conclusione, il flusso utilizzato da Synopsys per la potenza è il seguente:

Figura 3-3 Power-Flow di Synopsys.

Come si può notare, la maggior parte dei passi di progettazione avviene all’interno della shell di Design Compiler, invece le simulazioni sono eseguite all’esterno.

L’HDL Compiler converte il progetto in un formato indipendente dalla tecnologia chiamato GTECH design. In questa fase si può decidere se usare un’ottimizzazione di tipo clock gating oppure operand isolation. Dopodichè si può lanciare il comando “rtl2saif” che crea il forward-annotation file di cui si è già parlato sopra e che servirà per la simulazione RTL. Il formato GTECH va in ingresso al Design Compiler. Il Power Compiler e il Design Compiler usano librerie tecnologiche caratterizzate in potenza e lavorano insieme, all’interno dell’ambiente dc_shell per produrre una netlist gate -level ottimizzata in potenza. In particolare un possibile algoritmo è il seguente:

• Si settano i vincoli di timing e area (ma non ancora quelli sulla potenza)

• Viene fatta una prima sintesi del progetto (al cui interno ci sarà della logica aggiuntiva per il clock gating o operand isolation): si otterrà una netlist ottimizzata per timing e area.

• Si usa il comando “read_saif” per annotare su questa netlist le informazioni di switching activity. Queste possono derivare dal back-annotation file della simulazione RTL oppure si può lanciare una simulazione gate -level e usare un altro tipo di back-annotation file (che contiene informazioni aggiuntive) per aumentare l’accuratezza dell’analisi e dell’ottimizzazione.

• Si usano i comandi per l’ottimizzazione gate level (set_max_dinamic_power, set_max_leakage_power).

• Si risintetizza il progetto (si fa una sintesi di tipo incrementale, cioè la netlist già esistente costituisce il punto di partenza per ottimizzare tenendo conto anche dei vincoli sulla potenza).

• Si può usare la simulazione RTL già fatta oppure fare una nuova simulazione gate -level usando la nuova netlist.

• Si usano i comandi read_saif e report_power e si ottiene il risultato finale.

3.2 Modelli utilizzati da Synopsys per il calcolo della

potenza.

Durante l’analisi e l’ottimizzazione in potenza, i tool di Synopsys analizzano o ottimizzano i seguenti tipi di potenza:

La seconda è la potenza dissipata quando il circuito è attivo: ad esempio la tensione può commutare su un nodo in ingresso senza produrre variazioni dell’uscita e ciò comporta ugualmente una dissipazione di potenza. Essa è composta da due componenti: la switching power di cui si è già parlato (vedi Paragrafo 1.1), e l’internal power che è la potenza dissipata all’interno di ogni cella (nella maggior parte delle celle di libreria, la potenza interna è dovuta principalmente alla potenza di cortocircuito e per questo motivo i termini “internal power” e “potenza di cortocircuito” sono spesso considerati sinonimi). Per calcolare i singoli contributi della potenza, Power Compiler usa le informazioni che provengono dalla libreria tecnologica utilizzata e poi valuta delle equazioni.

3.3 Calcolo della potenza di leakage.

La potenza di leakage totale viene calcolata sommando i contributi di leakage di ogni singola cella presente nel progetto:

) ( ) ( _ _ P i P i cells leakage cell total leakage

∑

∀ =Quindi in libreria, per ogni cella è fornito un numero che rappresenta la potenza di leakage dissipata da quella cella. La potenza di leakage di una cella a volte può dipendere dalla sua condizione logica (state-dependent leakage power), di ciò si può tenere conto inserendo una condizione “when” nella libreria tecnologica. Ad esempio se una cella di libreria consuma una potenza di leakage pari a 2 unità quando un suo pin A è al valore logico alto, allora nella libreria tecnologica si scriverà: cell () { ... leakage_power () { when : ”A” ; values (2.0) ;

}

cell_leakage_power : 3.0 ; }

3.4 Calcolo della potenza interna.

La potenza interna di una cella viene calcolata sommando la potenza interna di tutte le uscite e gli ingressi della cella. Nelle librerie tecnologiche si possono trovare delle “internal-power -tables” per modellare la potenza interna su ogni pin della cella di libreria.

Si consideri ad esempio la cella in Figura 3-4:

Figura 3-4 Internal Power Model (Combinational).

Allora la potenza interna totale della cella U1 è così calcolata:

Z Z TR E Pint = × Dove:

Z

E è una funzione della capacità di carico C e della media pesata del L

tempo di transizione degli ingressi (weighted-average-input -transition-time). Quest’ultima quantità viene così calcolata:

∑

∑

= = × = B A i B A i Trans i TR i TRANS i TR WeightAvg , , ) ( ) ( ) ( ) (Dove TRANS(i) è il tempo di transizione dell’ingresso i, TR(i) è il toggle rate (transizioni/sec) dell’ingresso i.

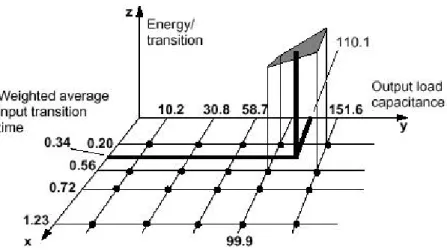

Una volta noti WeightAvg( Trans) e CL, il Power Compiler usa questi due indici per ricavare EZ da una Lookup-Table bidimensionale che ha sull’asse x la variabile WeightAvg(Trans) e sull’asse y la variabile CL. Sull’asse z si ricava il valore di E : Z

Figura 3-5 Lookup-Table per il calcolo di EZ.

Le celle spesso consumano una quantità di potenza interna dipendente dall’ingresso sul quale avviene la commutazione e dallo stato in cui si trova la cella.

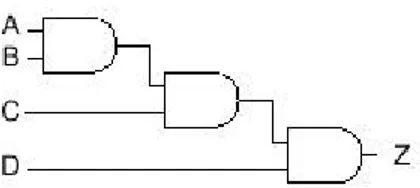

Analizziamo il primo caso (path-dependent internal power): ciò avviene quando le celle sono caratterizzate da più porte di ingresso e parecchi livelli di logica. Ad esempio una AND a 4 ingressi può essere implementata come una cella del tipo:

Figura 3 -6 Esempio di una path-dependent internal power cell.

E’ chiaro che una transizione di Z causata dall’ingresso A consuma più potenza interna di una transizione dovuta all’ingresso D: ciò avviene pe rché A influenza 3 livelli di logica mentre D ne influenza solo 1. Per un calcolo più preciso della potenza interna di questa cella si possono specificare diverse Lookup-Table per l’uscita Z (una per ogni ingresso).

Un esempio di una cella che consuma una potenza interna dipendente dal suo stato logico (state-dependent internal power) è una RAM: infatti a seconda se è in modalità di lettura o scrittura la potenza interna consumata è assai diversa. Anche in questo caso si possono specificare differenti Lookup-Table (una per ogni stato o modalità della cella).

Un altro aspetto di cui si può tener conto è che la potenza interna consumata durante una transizione in salita può essere diversa dalla potenza interna consumata durante una transizione in discesa: per questo motivo il Power Compiler supporta dei modelli in libreria che ci permettono di gestire separatamente i due casi.

3.5 Calcolo della potenza di switching.

La formula utilizzata da Power Compiler per calcolare la potenza di switching è la seguente:

∑

∀ × = ) ( 2 ) 2 ) ( ) ( ( i nets Load dd c i TR i C V PDove CLoad(i) è la capacità totale del nodo i (includendo le capacità parassite, le capacità di gate, le capacità di drain verso il substrato di tutti i pin connessi al nodo i) e

2 ) (i

TR

è il numero di transizioni 0→1 per unità di tempo. Per il calcolo di CLoad(i) vengono usate le informazioni della libreria tecnologica sulle capacità di gate connesse al nodo i, e il wire load model per i nodi connessi al nodo i. Una stima più precisa può essere fatta con un back-annotation delle capacità dopo le fasi di placement & routing.