3 Hardware del tag

3.1 Introduzione

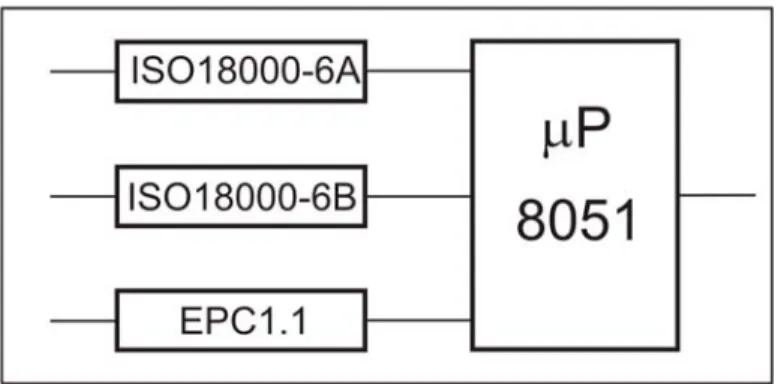

Questa tesi fa parte di un progetto che ha come obiettivo la realizzazione di un ASIC . La CAEN S.p.A, azienda esterna dove ho scelto di svolgere questo lavoro di tesi, vuole implementare un tag che risponda a più protocolli RFID tra i quali l’ ISO18000-6B, ISO18000-6A, EPC 1.19, etc., gestite da un microcontrollore della famiglia 8051 intel, di cui l’azienda stessa possiede un modello VHDL funzionante.

L’obbiettivo finale e quello di avere un tag, compatibile con più standard, in modo tale da poter vendere il prodotto insieme al lettore RFID che CAEN già possiede e coprire una buona parte di mercato relativo a questo nuovo tipo di tecnologia, e successivamente ottimizzarlo ed integrarlo in un progetto ASIC.

Il lavoro di tesi parte dalla progettazione del tag ISO18000-6B, usando il linguaggio VHDL, interfacciamento con il microcontrollore, ed infine collaudo e test a livello prototipale del blocco tag/micro utilizzando un dispositivo a logiche programmabili di tipo FPGA.

In questo capitolo descriveremo l’architettura del tag RFID che risponde alle specifiche del protocollo ISO18000-6B, descritte nel capitolo precedente.

Figura 3.1 Progetto Tag CAEN

3.2 Flusso di progettazione

Lo sviluppo di un sistema parte dalla sua specifica iniziale con l'obiettivo di realizzare fisicamente un dispositivo oppure solo di simularlo o documentarlo. Le attività coinvolte nel progetto dipendono dal tipo di dispositivo, ma si possono individuare delle fasi fondamentali tipiche di tutti i progetti:

Modellazione. Si disegna il sistema costruendone un modello software,

ovvero una sua rappresentazione fatta con opportuni strumenti grafici o linguaggi testuali (il termine disegno viene usato spesso come sinonimo di progettazione e non necessariamente di disegno grafico). Inizialmente il modello può anche essere molto astratto ovvero privo di dettagli sull'implementazione.

Simulazione. Il simulatore, esegue il modello ovvero ne simula il

comportamento affinché il progettista possa verificarne la correttezza. Se l'esito è negativo si torna a correggere il modello nella fase precedente. Se la

modellazione non è orientata alla realizzazione di un dispositivo, ma solo alla documentazione e/o simulazione, il progetto può terminare qui.

Sintesi. Per implementare fisicamente il sistema, è necessario

descriverne la struttura, qualunque sia il tipo di descrizione iniziale fatta. La sintesi traduce il modello in una netlist, che è la rappresentazione diretta in forma di rete di porte logiche. In questa fase il modello, benché simulato correttamente, potrebbe rivelarsi inadeguato, perchè alcuni costrutti del linguaggio utilizzato potrebbero essere non orientati alla sintesi o non supportati dal sintetizzatore.

Implementazione. La netlist viene ulteriormente elaborata, questa volta

allo scopo di produrne un formato che dipende dal tipo di dispositivo da realizzare. Si può intervenire sui dettagli del layout nelle maschere di produzione. Si possono calcolare esattamente i ritardi di propagazione delle linee di interconnessione, per inserirli nel modello ed eseguire una simulazione più completa. Per un ASIC non programmabile, i files risultanti dall'implementazione servono alla foundry che dovrà produrre fisicamente il dispositivo. Per un dispositivo a logiche programmabili, tali files sono utilizzati dal progettista per programmare il dispositivo.

3.3 Strumenti di progetto

Ogni fase della progettazione è supportata da opportuni tools. Gli strumenti di modellazione giocano un ruolo fondamentale, perchè devono essere adeguati alla complessità del sistema da progettare.

Nei progetti che implicano il disegno di dettagli implementativi dei transistors e/o delle celle logiche nelle maschere di produzione, si utilizzano

opportuni strumenti CAD. Nella scala dei livelli di astrazione, questo tipo di descrizione appartiene al livello più basso, il livello fisico.

Gli HDL (Hardware Description Languages) sono linguaggi per descrivere il sistema in forma testuale. Rispetto al disegno schematico, gli HDL permettono di utilizzare anche livelli di astrazione più alti, tipici dei progetti complessi. È anche possibile disegnare diagrammi di macchine a stati, utilizzando direttamente il formalismo grafico, che poi sono tradotti in una forma HDL.

Il primo HDL è stato PALASM (PAL ASseMbler) che serviva a specificare reti logiche per dispositivi programmabili tipo PAL. Un linguaggio simile è ABEL (Advanced Boolean Equation Language). Questi linguaggi permettono di descrivere il sistema attraverso equazioni logiche, tabelle della verità e diagrammi a stati (in forma testuale).

Tra gli HDL, quelli considerati di alto livello, principalmente VHDL e

Verilog, permettono anche rappresentazioni astratte del sistema, e

descrizioni algoritmiche simili a quelle dei linguaggi di programmazione software.

3.4 VHDL

Il VHDL è un linguaggio per la descrizione dell’hardware (un Hardware Description Language), che può essere utilizzato per la documentazione, la simulazione e la sintesi di sistemi digitali. Inizialmente, nei primi anni ’80, lo sviluppo del VHDL è stato supportato dal dipartimento della difesa statunitense, nell’ambito di un progetto denominato VHSIC (Very High Speed Integrated Circuits). VHDL è infatti un acronimo che sta per VHSIC Hardware Description Language. Il linguaggio è nato quindi con lo scopo di

fornire una descrizione non ambigua di un sistema digitale, che può essere interpretato univocamente dai vari progettisti impegnati nello sviluppo del sistema stesso.

Nel 1987 il VHDL è stato adottato come standard dalla IEEE; questa prima release ufficiale del linguaggio è nota come VHDL-87. Nel 1993 lo standard è stato revisionato dalla IEEE e si è giunti così alla versione attuale del linguaggio, nota come VHDL-93, che differisce solo in pochi aspetti dal VHDL-87.

Una delle caratteristiche richieste al VHDL è la possibilità di simulare il sistema descritto, sia a livello funzionale sia portando in conto i ritardi del circuito. Negli anni seguenti, oltre che per la documentazione e la simulazione, il VHDL ha assunto un ruolo sempre più importante nella fase di sintesi dei sistemi digitali. Un programma di sintesi consente, a partire da una descrizione comportamentale di un sistema, di ottenere automaticamente una descrizione del circuito a basso livello mediante una netlist in cui il sistema è descritto come interconnessione di porte logiche elementari appartenenti ad un’opportuna libreria. A partire dalla netlist, utilizzando opportuni programmi di piazzamento e collegamento delle celle (place & route), è possibile completare in maniera quasi del tutto automatica il progetto di un sistema integrato. In questo modo il ciclo di sviluppo di un sistema integrato diviene simile a quello di un programma software in cui si parte da una descrizione in un linguaggio di programmazione (C, PASCAL ecc.) per ottenere, dopo una fase di compilazione, una descrizione in linguaggio macchina.

L’utilizzo di sofisticati programmi di sintesi è stato uno degli strumenti più importanti che ha consentito lo sviluppo di circuiti integrati sempre più complessi, consentendo al progettista di concentrarsi sulla descrizione ad alto livello del sistema, esplorando come le diverse scelte architetturali

implementativi. Il VHDL consente, infatti, di descrivere efficacemente sistemi complessi cui corrispondono netlist di centinaia di migliaia o milioni di porte logiche elementari, così come in un programma software ad alto livello è possibile ottenere facilmente programmi in linguaggio macchina costituiti da milioni di istruzioni elementari a partire da un listato di poche centinaia di righe.. Poiché il VHDL è nato come linguaggio per la documentazione dei sistemi digitali, solo in un secondo momento sono stati introdotti i programmi di sintesi, non deve stupire che non tutti i costrutti del VHDL siano sintetizzabili (ad esempio, le operazioni relative all’accesso su files non possono avere una diretta corrispondenza hardware, anche perché non avrebbe senso).

3.5 Architetture del Tag

Figura 3.2 Schema a blocchi del tag ISO18000-6B

La figura 3.2 mostra lo schema a blocchi del tag ISO18000-6B semipassivo. La parte che verrà descritta in questo capitolo è tutto quello che è delimitato dalla linea tratteggiata come si vede nella suddetta figura, tralasciando tutta la parte di elettronica analogica legata al front-end e RF, e la descrizione del modello VHDL del microcontrollore 8051, di cui la CAEN ha messo a disposizione. Il tag ISO18000-6B comunica con la parte RF attraverso segnali seriali asincroni di I/O line_in e line_out come si vede in figura, mentre l’interfacciamento con il microcontrollore 8051 sarà descritto in seguito.

Il VHDL permette la divisione di un progetto complesso in più blocchi funzionali, in modo tale da organizzare i singoli blocchi per funzioni comuni, dando la possibilità al progettista di pianificare il lavoro in modo

Questa è stata la strada seguita per la progettazione dell’intero sistema. Ogni singolo blocco sarà poi descritto attraverso la macchina a stati che lo costituisce.

I blocchi possono essere così divisi in: Ricevitore;

Trasmettitore;

Controllore (Control Unit);

Macchina a Stati TAG (stati definiti dal protocollo); Interfaccia di collegamento con il micro 8051.

Il sistema è digitale sincrono con segnale di sincronizzazione (clock) pari a 16 MHz, e periodo Tck.pari a 62.5 ns.

Una delle operazioni d’ottimizzazione del progetto in una proiezione di un' implementazione ASIC, sarà quella di scegliere, entro certi limiti, una frequenza più bassa rispetto a quella scelta (da ricordare che più è bassa la , più bassa è la potenza dinamica dissipata, più alta è la durata della batteria del tag), e quindi aumentare le prestazioni del tag semipassivo in termini di durata. Per questo motivo, all’interno del progetto VHDL è stata creata una libreria, che permette di definire delle costanti, tra le quali la frequenza di clock . Quindi è possibile decidere con quale frequenza di sistema, sempre nei limiti concessi, è possibile lavorare.

clk

3.5.1 Il Ricevitore

Figura 3.3 Blocco Ricevitore (top view)

La figura 3.3 mostra quali sono i segnali I/O del blocco Ricevitore. La descrizione di questo blocco sarà fatta attraverso la relativa macchina a stati.

Il segnale trasmesso dal lettore RFID, dopo aver superato il blocco RF, è il segnale line_in. Questo segnale è seriale asincrono, cioè il lettore genera e trasmette al ricevitore un unico segnale su un solo filo. I bit trasmessi, costituenti l’intera trama, si dividono in una parte che serve esclusivamente a sincronizzare il ricevitore, in particolare il campo preambolo, ed una parte che costituisce l’informazione vera. Il ricevitore utilizza il preambolo o per rifasare il proprio clock tramite un circuito PLL (phase lock loop) o per impostare un metodo di campionamento dei bit dell’intera trama, ai fini di estrarre i dati correttamente.

Di solito il PLL è utilizzato per trame lunghe alcuni Kbit, mentre il secondo quando la trama non è troppo lunga.

Nel nostro caso, la lunghezza massima della trama trasmessa è relativa ad un'istruzione WRITE4BYTE, la quale, senza i campi di preambolo e

start_delimiter, è di 17 byte che corrispondono a 136 bit. Questa è una

lunghezza che mi permette di utilizzare un metodo di campionamento dei bit che descriverò in seguito.

Un'unità di misura utile da conoscere quando si lavora con segnali seriali è la velocità di trasmissione, propriamente chiamata bit rate, misurata in

bps (bit per secondo), unità già vista nel capitolo 2, che indica quanti bit al

secondo sono trasmessi lungo la linea. L’inverso del bit rate corrisponde al periodo T, durata di un singolo bit. Per la codifica utilizzata dal sistema Manchester, per ricevere correttamente un bit, dovrò campionare 2 volte all’interno di T, una volta nel primo intervallo T/2, e una seconda volta nel secondo intervallo T/2, poi decodificare il valore corrispondente.

Figura 3.4 Istanti in cui è possibile campionare per codifica Manchester

Sincronizzazione con il segnale line_in per l’estrazione corretta dei dati

Decodifica Manchester e parallelizzazione dati.

Controllo d’integrità dati ricevuti con registro accumulatore CRC.

Figura 3.5 Diagramma di transizione degli stati del blocco ricevitore

Gli stati definiti dal blocco ricevitore sono 7, come mostra la figura 3.4. Lo stato d’inizio della macchina è lo stato READY stato che viene assunto all’accensione del dispositivo o in caso di reset, sincrono e asincrono.

Da notare che quasi tutti gli stati della macchina, identificano i vari campi che uno alla volta vengono ricevuti, per questo sono stati denominati allo stesso modo.

La transizione allo stato successivo avviene quando il registro ad un bit Pre_det_init assume il valore 1; questo registro assume suddetto valore quando il segnale d’ingresso line_in resta attivo alto per un intervallo di tempoΔT =400μs, come specificato nel protocollo.

Per misurare questo intervallo è stato utilizzato un contatore sincrono, registro a n bit, che incrementa di uno ad ogni clock. Il valore Pre_det_init si configura quando il contatore raggiunge il valore intero c=6400, che corrispondono a quante volte il periodo di clock Tck sta all’interno del Δ . T Matematicamente questo valore corrisponde al rapporto

ck

T T

Δ . In verità il contatore conterà fino ad un valore poco più piccolo dell’c calcolato per

passare allo stato successivo. Il registro del contatore sarà almeno di 13 bit (conta fino ad un valore 213− ). 1

Quindi il ricevitore attraverso questo stato si assicura l’inizio di un’interrogazione da parte del lettore, attraverso il campo PREAMBLE_DETECT del frame.

Il passo successivo è quello della ricezione del campo PREAMBOLO, vale a dire il campo definito come la serie di nove ‘0’ in codifica Manchester, che serve come abbiamo detto per il calcolo del bit rate, al fine di campionare i bit successivi.

Figura 3.6 Campo preambolo a 40kbps

Le due possibili velocità di trasmissione seriale, specificate nel protocollo, sono 10 kbps o 40 kbps.

Il metodo utilizzato per la misura di velocità è simile a quella effettuata per il PREAMBLE_DETECT. Prima di descrivere questo metodo introduciamo un sistema che rileva le transizioni di livello del segnale LINE_IN. Questo sistema è composto di un registro a un bit ed una porta logica XOR come da figura 3.6.

L’uscita di questa struttura, ossia della porta XOR, è ‘1’ quando gli ingressi sono diversi (“01”, “10”), ‘0’ altrimenti. Se il line_in cambia

valore, il valore del Riv_tran sarà ‘1’, per la durata di un clock.

La prima transizione del line_in, dopo il PREAMBLE_DETECT, sarà

l'origine del passaggio allo stato successivo: PREAMBLE.

Il calcolo del bit rate è fatto attraverso un contatore che misura la durata di un bit e quindi come prima conterà un numero di all’interno del periodo dello stato mantenuto dal line_in (‘0’ o ‘1’).

ck

T

Questo sarà memorizzato in un registro accumulatore, quando il line_in

transita di livello, e cioè quando il valore del sistema rivelatore di transizione di figura 3.7 assumerà il valore 1. Nello stesso tempo il contatore si azzererà e ritornerà a contare per il bit successivo. Questa operazione verrà effettuata, per essere certi che il calcolo sia corretto e che non ci siano errori, almeno per 4 volte ed i valori assunti dal contatore saranno memorizzati in 4 buffer diversi. Successivamente questi saranno sommati ed il risultato sarà diviso per quattro. Questa operazione altro non è che una media mobile su una finestra di 4 valori:

4 3 0

∑

= i i N iN sono i valori memorizzati all’interno dei 4 buffer.

Viene fatta questa operazione perché i primi bit che arrivano del PREAMBOLO non hanno durata costante (setting time della parte RF del

tag), quindi si fa una media per avere una misura precisa. Dopo i primi quattro bit stabili, il calcolo della media effettuato, con una probabilità elevata, è corretto: sarà circa 200 se il bit rate è di 40kbps, 800 se il bit rate è di 10kbps.

Il passo successivo è quello di individuare il campo START_DELIMITER ed iniziare il campionamento dei bit, conoscendo il bit rate appena calcolato.

Figura 3.8 Istante di trans. di stato a START_DELIMITER

Il primo bit del campo START_DELIMITER è pari ad 1 (questo vale solo per lo Start delimiter 1 e 4, gli altri due sono RFU (Reserved future use)). La condizione per individuare suddetto campo è che il line_in non

transiti di livello, in particolare conservi il valore ‘1’ per un tempo pari a due volte il valore calcolato per la media del bit rate come mostra la figura 3.8. Se ad esempio il bit rate è 40 kbps, il valore del contatore in media come abbiamo detto è 200, il contatore conterà fino a circa 400, quindi significa che è arrivato il primo bit del campo START_DELIMITER. Questa condizione sarà percepita dalla macchina a stati con il settaggio del registro stdel_start, con conseguente passaggio allo stato successivo: START_DELIMITER.

Da questo punto in poi i bit vengono campionati e memorizzati in registri a scorrimento secondo la tipologia S.I.P.O (Serial Input Parallel Output). I

appena saranno campionati. I bit dei dati saranno campionati, e ogni 2 campioni decodificati secondo il sistema Manchester, e memorizzati in registri a scorrimento a 8 bit, e passati al blocco CONTROLLORE.

Il campionamento avviene nel seguente modo: lo shift register che conterrà il valore del campo START_DELIMITER, registro a 11 bit, inizierà lo scorrimento del registro con il valore di default “00000000001”. Questo perché il primo bit non viene campionato, ma comunque è da considerare.

Il secondo bit dello START_DELIMITER sarà campionato dopo un tempo

pari T/4. I bit successivi a questo saranno campionati secondo la seguente modalità:

Ogni bit, seguito da una transizione di livello, sarà campionato a T/4;

I bit, successivi al campionamento dopo la transizione di livello, saranno campionati ad intervalli di tempo pari a T/2.

I bit, una volta campionati, saranno memorizzati serialmente in uno shift register a 11 bit, che scorre i bit da destra verso sinistra, questo in accordo con la trasmissione del bit più significativo (MSB) al meno significativo (LSB).

Tale registro verrà in seguito utilizzato per il calcolo del bit rate di trasmissione della risposta del tag, in accordo con i valori specificati dal protocollo. Il valore di OUT del registro a 2 bit BR_tx indicherà al blocco trasmettitore a che bit rate trasmettere.

Il passaggio al nuovo stato della macchina, e cioè al DATA_STATE, sarà

individuato con il corretto calcolo del campo precedente, impostando il valore del registro interno, stdel_stop, ad 1 bit. A questo punto tutti i bit che

saranno ricevuti, andranno a costituire le informazioni dei campi DATA. Il ricevitore campionerà i bit con lo stesso metodo usato per lo START_DELIMITER, in più, come abbiamo già accennato, prima di essere memorizzati, saranno decodificati e parallelizzati in gruppi da 8 bit, e trasmessi al blocco controllore.

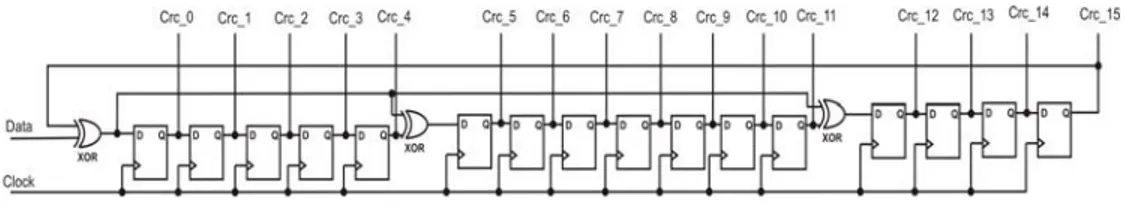

Oltre alle operazioni appena specificate, i bit decodificati saranno utilizzati per il controllo CRC, compresi i bit corrispondenti al valore del campo CRC che transita in coda ai dati trasmessi. Essi, infatti, saranno memorizzati in uno shift register a 16 bit, con una struttura mostrata in figura 3.10

Questo registro sarà settato a “FFFF” ogni qual volta il ricevitore è nello stato ready. A fine trama, quando i bit del campo DATA e campo CRC saranno caricati nel registro a scorrimento mostrato in figura, il contenuto di questo sarà: “1D0F” se non ci sono stati errori nella trasmissione,

Il controllo del CRC avviene tramite un handshake tra il blocco controllore e quello ricevitore. Infatti, è il controllore che sa quando far fare il controllo CRC, avvisando il ricevitore tramite il segnale d’ingresso del blocco crc_q. Il ricevitore passa allo stato CRC_CHECK, e risponde facendo il controllo del registro CRC (verifica se il valore contenuto nel registro corrisponde a “1D0F”). L’esito del controllo lo comunica al controllore settando e mettendo in uscita il valore di un registro interno CRC_flag a 2 bit: se il frame è valido, controllo CRC riuscito, quindi il controllore potrà continuare a fare le sue operazioni, altrimenti il ritornerà allo stato di partenza in caso di controllo CRC non riuscito.

A questo punto il ricevitore passerà nello stato WAIT_FOR_TX, e cioè aspetterà che i blocchi successivi terminino di eseguire le proprie operazioni, e il trasmettitore comunicherà l’avvenuta fine accompagnata con l’ultima trasmissione del bit dell’intera trama di risposta, settando il valore dell’ingresso RXTX_end.

Il ricevitore transiterà nello stato READY, pronto per ricevere una nuova istruzione.

Gli errori in ricezione possono essere individuati anche in uno stadio precedente al controllo CRC. Questi errori sono:

Errore di bit rate: bit rate non corrisponde a uno dei 2 possibili valori 10 kbps o 40 kbps;

Errore del valore START_DELIMITER: non corrisponde ai valori specificati dal protocollo;

Errore d’istruzione: segnalato dal blocco CONTROLLORE, quando l’istruzione ricevuta non è tra le istruzioni possibili.

Se vengono individuati questi errori, si passa dallo stato presente al momento dell’errore, allo stato READY.

3.5.2 Il Controllore

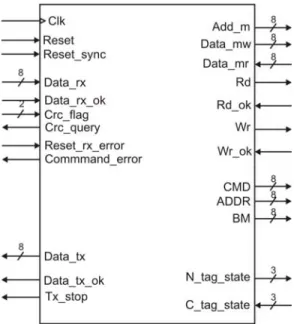

Figura 3.11 Vista Top del blocco controllore

La figura 3.10 mostra quali sono gli I/O del blocco controllore. Possiamo elencare le funzioni principali del blocco controllore:

Eseguire le operazioni relative alle istruzioni trasmesse; Gestire le operazioni di lettura e scrittura nella RAM;

Controllo e sincronizzazione dati in ricezione (RICEVITORE-CONTROLLORE), e dati in trasmissione(CONTROLLORE-TRASMETTITORE)

Parleremo più in dettaglio di queste funzioni, descrivendo la macchina a stati che costituisce il blocco CONTROLLORE. Di seguito viene riportato il diagramma delle transizioni di stato della macchina.

Figura 3.12 Diagramma di transizione degli stati del blocco controllore.

Lo stato di partenza di questa macchina è lo stato READY, stato di partenza che viene assunto all’accensione o in caso di reset sincrono o asincrono. Prima di descrivere la macchina, attraverso i suoi stati, bisogna definire alcuni registri interni che hanno delle funzioni speciali e sono:

COUNT, registro a 8 bit che serve per la procedura di anticollisione

LOCK, registro a 256 bit, che serve per la protezione delle locazioni di memoria (protegge in scrittura le locazione di memoria corrispondenti ai bit settati)

LFSR (Linear-Feedback Shift Register), registro a 64 bit che descriveremo in seguito

La transizione allo stato WAIT_DATA_RX, avviene quando l’ingresso del data_rx_ok è ‘1’. Questo succede quando il primo byte DATA utile è

pronto.

Il primo byte DATA, dopo il campo START DELIMITER, viene trasmesso, dopo essere stato correttamente decodificato, dal RICEVITORE al CONTROLLORE. L’ingresso data_rx_ok è ‘1’ allo stesso istante in cui il

valore dell’ingresso a 8 bit Data_rx, corrispondente ai byte del campo

DATA, è valido. Quindi al clock successivo memorizzo il dato in un registro buffer da un byte.

Il primo byte, che causa il passaggio allo stato successivo del READY, è il byte del campo ISTRUZIONE.

Abbiamo detto nel capitolo 2, che ogni istruzione ha dei parametri diversi, che corrispondono ad una trama di lunghezza diversa. Quindi il primo byte memorizzato dal CONTROLLORE, essendo il codice dell’ISTRUZIONE, è fondamentale per impostare alcuni registri di inizializzazione. Tra questi un registro interno a 5 bit (numero massimo di byte da ricevere è in corrispondenza di una istruzione WRITE4BYTE, 17) che assumerà un valore variabile n, corrispondenti ai byte da attendere,

compreso il campo CRC, relativi all’ISTRUZIONE appena ricevuta. Ad esempio se il comando ricevuto è GROUP_SELECT_EQUAL, il numero di byte da attendere sarà 12, 1 per il BYTE_MASK, 1 per l’ADDRESS, 8

per il WORD_DATA e 2 per il CRC mentre per un comando FAIL o

SUCCESS i byte da attendere saranno 2, solo quelli del CRC.

Quindi nello stato WAIT_DATA_RX, dopo il primo byte valido, il

CONTROLLORE aspetta i byte successivi all’istruzione in registri buffer e li memorizza ogni qual volta che il valore dell’ingresso data_rx_ok è ‘1’.

Una volta che tutti i byte attesi sono stati ricevuti e memorizzati il CONTROLLORE passa automaticamente nello stato successivo

CRC_CONTROLL, invitando il RICEVITORE ad effettuare il controllo del

CRC e settando l’uscita CRC_query. Il RICEVITORE risponde al controllore impostando il valore del registro crc_flag a 2 bit: il CONTROLLORE va nello stato PRE_COMMAND_OP quando il valore crc_flag è “01”, passa nello stato READY se il valore crc_flag è ”10”, ritornando allo stato iniziale.

Figura 3.13 Registro crc_flag

Dopo che ha memorizzato tutti i dati e superato il controllo CRC, il CONTROLLORE inizia a fare le operazioni specificate dal comando.

Il PRE_COMMAND_OP è uno stato della macchina che serve per fare delle operazioni preliminari di alcuni comandi, tipo controllare UID del tag prima di effettuare un’operazione di scrittura o di lettura. Dopo che le operazioni preliminari sono state effettuate, il CONTROLLORE passa nello stato COMMAND_OP, dove esegue l’operazione specificate dal comando.

stato READY segnalando questo risultato al RICEVITORE e al TRASMETTITORE, i quali tornano negli stati iniziali. Nel caso contrario in cui l’operazione è eseguita con successo, i dati della risposta del TAG vengono passati al blocco trasmettitore, pronti per essere trasmessi, ed il CONTROLLORE si riporta nello stato di partenza (READY).

Il registro LOCK è un registro a 256 bit, e serve per proteggere alcune

locazioni di memoria in scrittura, come ad esempio il codice UID (esso infatti risiede nelle prime 8 locazioni di memoria del tag). Se il bit n ([0:255]) del registro è 1, la locazione di memoria corrispondente non sarà accessibile in scrittura (protetta, chiusa) come mostra la figura 3.14.

Figura 3.14 Corrispondenza memoria del tag con registro LOCK

Nel capitolo 2 è descritta la procedura di anticollisione del tag. Abbiamo specificato ad inizio paragrafo la presenza di alcuni registri con funzioni speciali, in particolare il registro LFSR.

Per generare una serie casuale adatta per l’algoritmo di anticollisione, viene impiegata una struttura LFSR. Questo è un circuito in grado di produrre una sequenza pseudocasuale di uni e zeri senza richiedere un ingresso, reso possibile mediante uno shift register opportunamente

retroazionato. La tipologia dello shift register è S.I.S.O.(Serial Input Serial Output), in base al tipo di caricamento dei dati.

In letteratura esistono due strutture tipiche di riferimento:

La prima è di Fibonacci che consiste di un semplice shift register in cui la somma modulo 2 dei vari pesi viene riportata in ingresso. La seconda realizzazione detta di Galois consiste di uno shift register il cui contenuto ad ogni passo è modificato da una somma pesata dello stadio di uscita.

Figura 3.15 Struttura Fibonacci (a), struttura Gailos (b)

Ci sono due sequenze prodotte da ognuno di questi generatori: la più banale è quella ottenuta quando lo stato iniziale dei generatori è zero per tutti i flip-flop, l'altra, quella utile, ha lunghezza 2m-1. Queste due sequenze insieme danno i 2m stati forniti dallo shift register a m bit.

La matematica di questi generatori è equivalente alle operazioni dell'algebra ordinaria applicata a polinomi astratti funzione della variabile X

con coefficienti binari. Ogni sequenza è basata su un “generatore polinomiale”, già visto per il controllo CRC capitolo 1.

G(X) = cmXm + cm-1Xm-1 + cm-2Xm-2 + ... + c2X2+ c1X + c0

I cm coefficienti sono binari e sono i pesi mostrati in figura 3.13. Il

polinomio è detto primitivo se non ha fattori e divide Xr+1 dove r=2m-1. Un polinomio primitivo di grado m deve necessariamente avere g0=gm. Se il

polinomio generato dal LFSR è primitivo allora la sequenza prodotta ha lunghezza massima e pari a 2m-1. Una sequenza di lunghezza massima è talvolta chiamata sequenza-m.

Alcune proprietà delle sequenze-m sono le seguenti:

un registro a m = bit produce una sequenza di periodo 2m

-1; una sequenza-m contiene esattamente 2m

-1 uni e 2m-1-1 zeri; la somma modulo 2 di una sequenza m con un'altra fase della

stessa sequenza m genera una terza fase della sequenza;

una finestra di lunghezza m che scorre una sequenza-m per 2m

-1 posizioni, scandisce ogni possibile numero a m-bit eccetto quelli dati da tutti zeri e tutti uni;

La struttura scelta per il tag è quella di Gailos, con un registro a 64 bit, registro con lunghezza pari al valore dell’UID. Questa scelta è stata fatta in quanto la sequenza generata dal tag, sarà quella a partire dal valore di registro pari proprio al numero UID. Da come è definito questo numero, sono sicuro che la sequenza-m generata sarà diversa per ogni tag, con lunghezza di ripetizione elevata (si ripete dopo 264− ). Il polinomio 1 primitivo utilizzato è stato preso dalla letteratura ed è

Figura 3.16 LFSR a 64 bit

Il registro scorre ogni qualvolta il tag riceve un comando valido.

Il blocco CONTROLLORE è il blocco che gestisce anche gli accessi in lettura e scrittura nella memoria del tag contenuta nel blocco INTERFACCIA tag/m8051. Gli I/O di accesso alla memoria sono mostrati in figura 3.10 e sono:

Address_m, a 8 bit per l’indirizzamento della memoria.

Data_mw, Data_mr a 8 bit e sono i dati in/out rispettivamente. /wr, /rd, abilitazione in scrittura e lettura attivi bassi

Wr_ok, rd_ok, segnali di conferma per la lettura o la scrittura in memoria.

Attenzione particola viene fatta a questi due ultimi segnali: abbiamo scelto questo tipo di interfacciamento con la memoria del tag, per una totale indipendenza nella scelta della memoria da implementare in ASIC di tipo sincrona o asincrona.

Se si sceglie una memoria di tipo sincrona allora questi due segnali saranno sempre attivi alti, se invece si deciderà di utilizzare una memoria asincrona, tramite l’aggiunta di un po’ di logica, grazie a questi due tipi di segnali, il CONTROLLORE comprende se l’operazione di scrittura o di lettura è stata effettuata.

3.5.3 Il Trasmettitore

Figura 3.17 Top view del blocco Trasmettitore

La figura 3.15 mostra il blocco Trasmettitore con i suoi I/O. Le funzioni principali di questo blocco, è quello di trasmettere la risposta del tag. Questo blocco è sincronizzato con gli altri, la trasmissione può essere divisa nei seguenti passaggi, che sono anche le operazioni principali del blocco:

Codifica FM0 dei dati, trasmissione seriale Calcolo CRC

Per la descrizione del blocco, utilizzeremo quella della macchina a stati che lo organizza. Di seguito mostriamo il diagramma di transizione degli stati.

Figura 3.18 Diagramma di transizione di stato del Trasmettitore

Lo stato di partenza della macchina è lo stato READY, stato che viene assunto all’accensione o in caso di reset sincrono o asincrono. Il passaggio allo stato successivo, QUITE_STATE, avviene quando l’ingresso tx_start

del blocco, che è anche ingresso della macchina, assume valore pari a ‘1’. Questo avviene, quando il frame ricevuto dal blocco RICEVITORE è valido. Nello stesso tempo viene memorizzato in un registro a 2 bit, il valore dell’ingresso BR_tx, che è valido dopo che viene ricevuto il campo START_DELIMITER.

Nel QUIET_STATE, la macchina aspetta un tempo pari a 400 μs

conta fino ad un valore 400 10 6400 6 = = − clock T x

n prima di settare il valore del registro ad 1 bit QUIET_TC, e passare allo stato PREAMBLE_TX.

In questo stato il blocco trasmette il PREAMBOLO di ritorno, la serie di bit vista nel capitolo 2. I bit trasmessi comporranno un segnale seriale asincrono come si vede in figura, e la durata di ogni bit sarà stabilita dal bit rate di uscita definito dal BR_tx, in particolare 10kbps se il valore sarà ”01”, 40kbps se il valore sarà “10”.

A fine trasmissione preambolo, il registro preamble_tc si setta, e fa

passare la macchina nello stato TRASMISSION DATA, stato in cui inizia la trasmissione dei dati, e cioè l’informazione vera e propria della risposta del tag. L’ordine di trasmissione è dal bit più significativo a quello meno significativo, per un byte, per una word dal byte MSB al byte LSB. I dati da trasmettere vengono passati dal controllore. Per la verifica d’integrità dei dati, è calcolato il valore CRC a partire dal primo bit del campo dati trasmesso, tramite un registro a scorrimento che ha la stessa struttura del CRC visto nel RICEVITORE. Il calcolo viene così eseguito:

Il registro a 16 bit CRC viene inizializzato al valore “FFFF” ogni volta che si deve trasmettere un dato

I bit che compongono il dato vengono accumulati serialmente nel registro dal primo all’ultimo

Quando arriva l’ultimo bit, il valore calcolato nel registro viene invertito e posto in coda al campo dei dati per la trasmissione Quando tutto il frame è stato trasmesso, e cioè quando il registro data_tx_tc si setta, la macchina si riporta nello stato READY.

Il segnale line_out,è il segnale che andrà collegato sulla parte RF. Questo

realizzare il backscatter: forzerà il valore a 0 quando si vorrà trasmettere un 1, alta impedenza quando si vorrà trasmettere uno 0.

3.5.4 TAG FSM

Questa è la macchina a stati del tag già descritta nel capitolo 2.9.1

3.5.5 Interfaccia tag/m8051

Figura 3.20 Schema a blocchi dell'architettura interna

L'8051 è single-chip progettato e prodotto dalla Intel a partire dal l980, è disponibile sia in versione PMOS che in versione CMOS.

Attualmente la Intel non è l'unico produttore del microcontrollore infatti diverse case costruttrici indipendenti producono sia il modello standard che versioni migliorate con periferiche aggiuntive incorporate (Porte I/O aggiuntive, Watch-Dog, ADC, Driver PWM, interfacce I2C ecc.)

L'8051 è il più diffuso nel mercato mondiale dei microcontrollori (nel 1993 ne sono stati venduti 126 milioni di pezzi) ed è disponibile in più di cento versioni.

Le caratteristiche principali di questo microcontrollore si possono riassumere in:

CPU a 8 bit ottimizzata per le applicazioni di controllo con capacità estesa di elaborazione booleana (su singoli bit);

64 kbyte di max di memoria indirizzabile per i programmi;

64 kbyte di max di memoria indirizzabile per i dati;

4 kbyte di memoria per i programmi interna al chip (ROM nella versione 8051, EPROM nella versione 8751);

128 Byte di memoria RAM per i dati interna al chip;

Generatore di clock incorporato

5 interrupts di cui 2 esterni e tutti con due livelli priorità

2 Timers/Contatori a 16 bit

Porta seriale full-duplex (il Baud Rate è prodotto da uno dei due timer)

In definitiva la famiglia 8052 rappresenta i microcontrollori dall'architettura piu' aperta e "libera" del mercato.

Il blocco descritto in questo paragrafo è l’interfaccia di collegamento tra il tag ed il microcontrollore. Ad esso non viene associata nessuna macchina a stati, ma la descrizione del blocco sarà fatta definendo i sottoblocchi e alcuni dei registri interni con funzioni particolari.

Infatti, in questo blocco risiede la memoria del tag di 2kbyte, organizzata in 256 locazioni da 1 byte ciascuna, ed una FIFO di 10 campi da 8 bit ciascuno. La memoria e la fifo implementata in VHDL sono costituiti da registri: 256 registri da 8 bit per la memoria, 10 registri da 8 bit ciascuno per la FIFO. La memoria è dual port, per permettere l’accesso sia dal tag che dal micro. Nelle prime 8 locazioni di memoria del TAG risiederà il codice identificativo unico (UID) a 64 bit. Il valore scelto per questo tag è un valore casuale, ed è “0101010101010101”.

Il tag comunica con questa attraverso il blocco CONTROLLORE, accedendo in memoria. Questo passa al suddetto blocco anche i valori di COMANDO, BYTE_MASK e ADDRESS, ricevuti con il frame di comando, memorizzandoli nei corrispondenti registri quando l’ingresso frame_ok è attivo alto.

Il microcontrollore vede il tag come una memoria esterna da 512 locazioni da un byte. Le prime 256 locazioni sono le locazioni di memoria previste nell’architettura del tag, le altre corrispondono a 256 registri

COMMAND, contiene il valore del comando ricevuto dal tag con indirizzo 0x101;

ADDRESS, contiene il valore dell’indirizzo di alcuni comandi specificati dal protocollo con indirizzo 0x102;

BYTE_MASK, anche questo valore contiene il BYTE_MASK, parametro tipicamente usato dai comandi di tipo SELETTIVO con indirizzo 0x103.

ST_CTR, registro di controllo all’indirizzo 0x100. Ogni bit del registro di controllo è definito come segue.

Bit 0, Bit 1, Bit 2 sono RFU;

Bit 3: flag FIFO_EN, se settato il micro scrive in FIFO

Bit 4: flag INT_CLR, se è settato disabilita il tag alla richiesta di interruzione.

Bit 5: flag INT_LEVEL/EDGE, se 0 allora la richiesta di interruzione ha una durata pari ad un clock, se 1 l’interruzione mantiene fino a quando il micro non accetta la richiesta d’interruzione.

Bit 6: flag INT_EN, se è settato il tag può fare una richiesta di interruzione tramite INT

Bit 7: flag ISO18KB_EN, è attivo basso quando il micro disabilita il tag.