1

I N T R O D U C T I O N

c o n t e n t s1.1 Overview . . . 1 1.2 Hardware and Software concurrent design . . . 2 1.3 Consortium description . . . 5

1.1

overview

In new space missions, both the scientific and the commercial ones, there is a growing request of on-board numerical compu-tation capability. Indeed manage big data flow makes necessary elaborate the acquired information before sending them to the earth. There are several reasons to manage always bigger data flow, for example due to an improvement of sensors or to im-plement better compression and cryptography algorithms. Key devices in this framework, among others, are the Digital Signal Processors (DSPs).

Unfortunately there is only one device suitable for these ap-plications that can be used by the European Space Agency (ESA) use withoutITAR1

limitation. It is the obsoleteTSC21020 manu-factured by Atmel, its performance are worse than theUSmade

alternatives. This device can reach 40MFLOPSas sustained perfor- MFLOPSis the acronym of Mega FLoating point Operations Per Second

mance instead the American device can reach about 840MFLOPS. In this scenario there are several ways to approach the problem, for example hardening a Commercial Off The Shelf (COTS)DSP

against radiations or making a porting of a commercial DSPto a radiation tolerant ASIC technology. The first one could be a good solution but can not be scaled depending on applications and suffers problems coming from shorter lifetime of ground components with a risk of early obsolescence. The second one is, de facto, impracticable due to the lack of interest of groundDSP

vendors for the small space market considering that technology

1 International Traffic in Arms Regulations are a set ofUSgovernment regulations that control the import and export of defence related articles and services

1.2 hardware and software concurrent design 2

gap between space and ground technologies makes an automatic porting not feasible.

Another option is to develop a newDSPcore with performance

near to 1GFLOPStargeting an European available space technol-ogy such as, for example, Atmel 180 nm. The goal is to design and implement a parametric and scalable (general-purpose)DSP

architecture that can be used for a wide range of application. This project, called “DSPACE”, aims to provide a newDSPcore as an Intellectual Property (IP) macrocell that can be integrated in different technologies and a efficient and reliable Software

De-velopment Environment (SDE) that has to be easily usable. After TheSDEis a tool for end-users to exploit theDSP

the targets will be achieved a demo-board with a commercial

FPGAwill be provided. Moreover will be provided benchmarks to evaluate theDSPperformance in several working conditions.

1.2

hardware and software

concurrent design

It is important to point out the key role of the SDE. In fact the SDEdesign effort is larger than theDSPcore design. There are a lot of reasons because the design of a new SDEfrom the

scratch can not be realistically approached in this background, just think that a complete and matureSDEneeds very long time, its users experiences and feedbacks as well a lot of required funding. Unfortunately commercialSDEcan not be used due to license restrictions.

There are two main ways:

• The first one is to reuse an open source tool-chain2

adding an ad-hoc developed code optimizer layer.

In fig. 1 there is a picture that explains this concept. The

SDE, originally created to work with a groundDSPs, is used to feed, through a code optimizer, a newDSPsuitable for space environment. The areas of the blue blocks give an estimation of the effort needed for each ones. Also the code optimizer has a key role in this work because it is the element that make binary compatible the new space DSP

with the groundDSP. In short words this strategy aims to

2 Tool-chain indicates a collection of instruments that let to produce an executable program starting from an high-level programming language source, such as C. The tool-chain can also include other instrument for verification such as a debugger or a disassembler. In general the tool-chain is the core of aSDE.

Software Development Environment Existing elements Code Optimizer Space DSP Ground DSP Binary compatibility

Figure 1:Possible DSPACE project approaches (the project aim to provide the blue blocks)

reuse as much as possible existing software and to design theDSPcore taking into account these considerations. There are two open source software that can be used, they are:

◦ G21 package

(for Analog DevicesSHARCfamily) ◦ Sourcery CodeBench

(for Texas Instruments TMS320C67x)

The G21 package is older than CodeSorcery, which is re-cently acquired by Mentor Graphics, and even if it is not recently updated theSHARCfamily is analysed because can give insights for a new architecture definition. The Sourcery CodeBench is a more promising solution, for this reason Texas Instruments architecture could be used as DSPACE reference architecture. Both of architectures are analysed in detail in the chapter 2 with focus on the cores. Moreover af-ter the hardware analysis there are other information about respective tool-chains.

• The second one is to develop both the DSP and the soft-ware tools using an high-level description language such

as Language for Instruction Set Architectures (LISA) 2.0. In- LISAmeans Language for Instruction Set Architectures

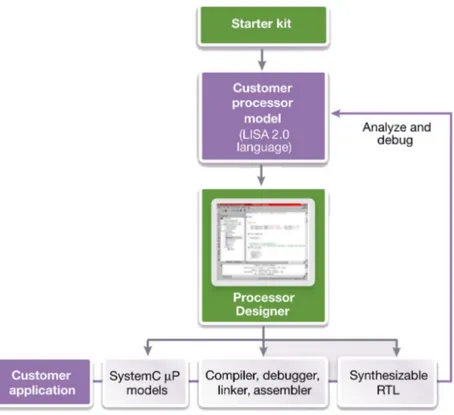

deed Synopsys provides a powerful tool called Processor Designer that allows to produce all necessary items starting from a single description. In fig. 2 there is a picture from the Processor Designer datasheet in which is depicted this flow.

1.2 hardware and software concurrent design 4

The green blocks are provided by Synopsys, the purple blocks are the inputs and the light blocks are the outputs. Although this tool can generate either, the possibility of reuse a part of an open source existing tool-chain is not discarded.

Figure 2:Synopsys Processor Designer work flow

It is important to underline that the above mentioned ap-proaches are not mutually exclusive. In fact it is possible, after the definition of a general architecture, describe the core inLISA

then edit or embed some parts to the output model and create a new tool-chain using a part ofLISAtool-chain and part of existing tone, new software interface levels might be inserted.

1.3

consortium description

This project is developed in an international context by five partners. The partners, in alphabetic order, are:

• The CPR (Consorzio Pisa Ricerche) is a

mixed public-private organization whose main objective is to strengthen connections between research and industry. The microelectronic application division is specialized in advanced microelectronic system design. The members have acquired experience in the analysis, design, simulation, performance and analysis of digital signal processing and communication system.

• The INTECS is an Italian company that is

specialized in software branch. In fact INTECS provides software technologies to support the major European and Italian organizations in design and implementation of ad-vanced systems for defence, space and civilian markets.

• The SITAEL is an Italian enterprise able

to provide design and production service for hight relia-bility space oriented electronics. Their main activities and products are: power supply electronics, cooler drive elec-tronics for cryocoolers, front-end elecelec-tronics, payload data handling and processing units, custom Application Specific Integrated Circuits (ASICs) including front end and ADC,

complexFPGAfitting.

• The Space Applications Services is a

Belgian space technology company whose aim is to develop systems, solutions and products for the aerospace markets and for related industries. The main business lines are: novel space system concept development, human-machine and human-robot interaction systems and products, includ-ing visualization systems, space system operation services, ground facility set up, operations preparation, planning, training and execution.

1.3 consortium description 6

• The RWTH (Rheinisch-Westfälische

Tech-nische Hochschule) Aachen university is a German interna-tional top-ranked technical university. The main mission of its own Institute for Communication Technologies and Em-bedded Systems (ICE) is to contribute to the advancement of embedded systems design.