Tecniche utilizzate per il recupero dello

skew

1.1 Introduzione

Questo capitolo contiene innanzitutto una panoramica riguardante lo skew del clock, le cause che lo generano e le metodologie di correzione note a livello di letteratura. Al termine di ciò viene introdotto il progetto del circuito Deskewer sviluppato in questa tesi, la sua architettura e la strategia di correzione adottata.

1.2 Definizione di skew e cause che lo generano

Il clock è un segnale di sincronizzazione periodico utilizzato come un tempo di riferimento per il trasferimento dei dati nei sistemi digitali sincroni. I dati possono essere trasferiti da un registro presente su un chip ad un registro posto su un altro chip o tra registri appartenenti allo stesso chip. E’ noto che nei sistemi sincroni i segnali che trasportano i dati che arrivano ad un flip-flop devono, in generale, rimanere stabili a partire da tsu prima fino a th dopo l’arrivo

del fronte campionatore del clock, dove tsu e th sono chiamati rispettivamente il

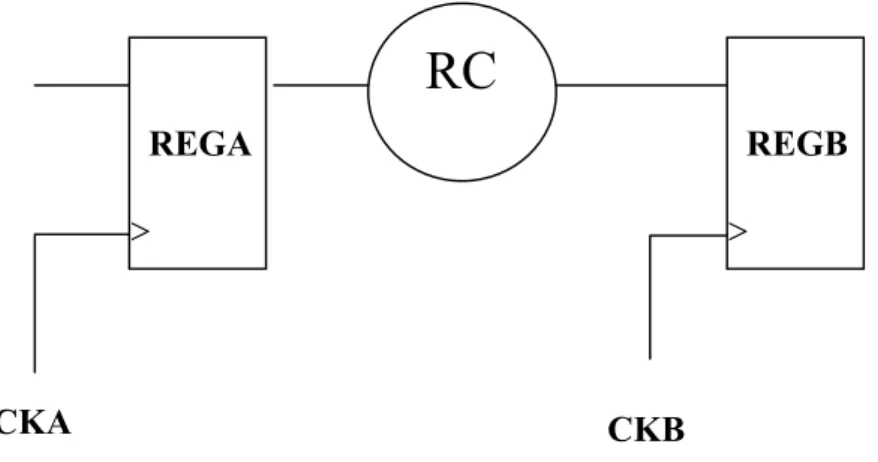

tempo di setup e il tempo di hold. Conseguentemente le reti combinatorie (RC) che producono i dati devono essere progettate in modo da rispettare questi vincoli.

REGB > REGA >

RC

CKA CKBFigura 1.1 Circuito sincrono

La Figura 1.1 mostra una generica configurazione di due registri in un sistema sincrono. Appare chiaro che i vincoli diventano più stringenti se ci sono differenze sull’istante di arrivo dei fronti dei segnali di clock presenti all’ingresso dei diversi flip-flop di un sistema.

Queste differenze sono genericamente riferite con il termine clock skew e sono sempre inevitabilmente presenti. Esse sono dovute a diversi fattori come alla differenza di carico sui diversi segnali di clock, differenze nei ritardi introdotti nei diversi percorsi di clock (anche all’interno dello stesso chip) dalle linee di interconnessione, differenze dovute al mismatch casuale dei parametri dei dispositivi.

Il clock skew è generalmente trascurabile nei sistemi che operano a basse frequenze ma diventa sempre meno trascurabile man mano che la frequenza aumenta. Si capisce quindi che con le elevatissime frequenze di funzionamento che oggi vengono raggiunte nei circuiti integrati (si pensi per esempio ai processori di ultimissima generazione), il problema dello skew del clock riveste oggi grandissima importanza tanto che sono necessarie delle tecniche che consentano di diminuirne l’effetto.

Dalla Figura 1.2 [10] notiamo come all’aumentare della frequenza di lavoro dei processori il clock skew aumenti anche considerato in percentuale sul

periodo del clock. Ciò significa che da un certo punto in poi lo skew non scala perfettamente come la tecnologia.

Figura 1.2 Andamento percentuale del Clock Skew con la frequenza dei processori [10].

Lo skew può essere definito come la massima differenza nei tempi di arrivo del segnale di clock ai flip-flop che sono presenti nel sistema come mostrato in Figura 1.3 (a).

(a) (b)

Le altre cause che producono lo skew sono dovute alle differenze PVT (Process Voltage Temperature) dovuti al processo tecnologico, alla variazione della tensione di alimentazione e della temperatura di funzionamento nei diversi punti del chip o dei diversi chip. Come mostrato in Figura 1.4 [10], l’errore che ha un maggiore peso è quello introdotto dal mismatch dei dispositivi. Le regole da rispettare per l’ottimizzazione del matching dei dispositivi verranno discusse nei paragrafi successivi.

Figura 1.4 Errori dovuti alla temperatura, al carico, all’alimentazione e al processo [10].

Altro fattore da limitare il più possibile è lo Jitter picco-picco introdotto nel segnale che si propaga lungo la rete di distribuzione e per finire, non di minore importanza, è la potenza dissipata dalla rete di distribuzione del clock. Ma queste ultime due problematiche non verranno trattate nell’ambito di questa tesi.

1.3 Regole per ottimizzare il matching dei dispositivi

Il progetto fisico di circuiti integrati richiede l’applicazione di alcune regole per l’ottimizzazione del matching dei dispositivi. In questo paragrafo verranno descritte alcune di queste regole.

Per fare in modo che due dispositivi siano il più possibile identici devono avere:

stessa struttura; stessa temperatura;

stessa forma e dimensione; distanza minima;

geometrie “Common Centroid”; stessa orientazione;

dimensioni non minime.

L’importanza di queste regole dipende dal particolare processo e dispositivo. Analizziamo alcune di queste regole.

Matching: stessa temperatura.

Non ci sono problemi se la dissipazione del chip è trascurabile, altrimenti è necessario piazzare i dispositivi sulle isoterme (cioè su linee alla stessa temperatura) come mostrato in Figura 1.5 dove è possibile notare la sorgente di calore, l’andamento delle isoterme sul chip e la disposizione dei due dispositivi, collocati lungo la stessa isoterma.

Figura 1.5

Matching: stessa forma e dimensione

Tale regola si commenta da sola interpretando la Figura 1.6:

Matching: distanza minima

Questa regola va rispettata per ottenere i vantaggi dalle correlazioni dei parametri di processo, cioè per evitare il mismatch globale dovuto alla variazione di parametri come drogaggio, mobilità, etc, nelle diverse parti del chip. Tale mismatch infatti aumenta con le distanze tra i dispositivi

Matching: stesso orientamento

Mantenere lo stesso orientamento dei dispositivi permette di eliminare le dissimmetrie causate da:

substrato anisotropo;

passi del processo anisotropi; stress dopo il packaging.

Matching: dimensione non minima

Realizzare i singoli dispositivi a dimensione non minima permette di ridurre la deviazione standard dell’errore dovuto al processo tecnologico la quale risulta essere inversamente proporzionale alla radice quadrata dell’area del canale del transistore MOS come descritto di seguito:

( )

L W ≈ 1

δ

σ media statistica sulla lunghezza

( )

W L ≈ 1

δ

σ media statistica sulla larghezza

relativo mismatch: L L W W WL WL σ σ σ = ± ± ± 1 1

con W L WL L W WL W L L W WL WL 1 1 1 1 1 1 1 1 2 2 + = + = + ≈ ± ± σ

Quindi usare W, L il più grandi possibili quando se ne ha la possibilità.

Matching: geometria “Common Centroid”

Consiste nel realizzare i transistori con una struttura a baricentro comune.

Un esempio è mostrato in Figura 1.7 dove è realizzata una coppia differenziale a MOS con struttura “Common Centroid”

Per concludere si può dire che per ottenere un buon matching è necessario rispettare il più possibile le regole sopra menzionate. Inoltre per minimizzare le fluttuazioni casuali è consigliabile lavorare con forme quadrate e quindi con minimo rapporto perimetro su area di canale.

Figura 1.7

1.4 Effetti dovuti alla presenza dello skew in un sistema

sincrono e metodologie per la distribuzione del clock

In sintesi lo skew nei sistemi sincroni consiste nel seguente fenomeno: il clock, propagandosi lungo le linee di trasmissione non arriva contemporaneamente a tutti i registri del circuito causando così o un peggioramento della massima frequenza di funzionamento o nel caso peggiore un

malfunzionamento del sistema stesso. Vediamo più in dettaglio perché succede tutto questo nei due casi.

REGB >

REGA > B A

RC

τ CKB CKAFigura 1.8 Circuito sincrono

Facciamo riferimento al sistema rappresentato in Figura 1.8.

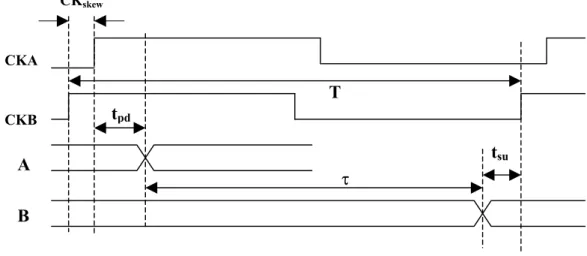

Caso 1: CKA in ritardo rispetto a CKB

CKskew CKB CKA tpd tsu τ T A B

Figura 1.9 Temporizzazione con CKA in ritardo rispetto a CKB

Tminimo = tpd + τ + CKskew + tSU

dove τ è il ritardo introdotto dalla rete combinatoria (RC) e tpd è il tempo di

attraversamento del registro A, come mostrato dalla temporizzazione di

Notiamo che CKskew limita la frequenza massima di funzionamento, infatti la frequenza massima è pari a:

fmassima = 1/Tminimo.

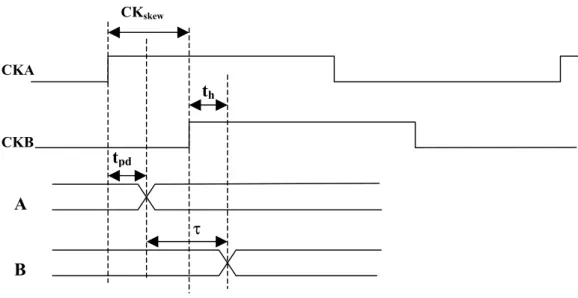

Caso 2: CKB in ritardo rispetto a CKA.

CKskew B A CKB CKA tpd th τ

Figura 1.10 Temporizzazione con CKB in ritardo rispetto a CKA

Deve essere verificato che:

τ + tpd > CKskew + th

dove th è definito tempo di hold (Figura 1.10). Quindi maggiore è il CKskew

maggiori sono le problematiche di violazione del tempo di hold.

Vediamo quali sono i trends per la distribuzione del clock in modo tale da minimizzare lo skew [2].

Nella maggior parte dei sistemi la distribuzione del clock è realizzata ad albero di buffer (clock tree). Le terminazioni dell’albero sono preposte a pilotare un certo gruppo locale di flip-flop. Un albero di distribuzione del clock si dice bilanciato quando i rami dello stesso livello devono pilotare sempre il medesimo carico.

La realizzazione di un clock tree bilanciato è essenziale per il successo di un qualsiasi progetto VLSI. Il ritardo introdotto dai fili di interconnessione è importante come il ritardo introdotto dalle porte logiche.

In un sistema digitale sincrono un segnale di clock globale è usato per fornire informazioni di temporizzazione utili per tutte le operazioni sincrone; la sua funzione è fondamentale a tutte le operazioni del sistema.

La distribuzione ottima di un clock tree bilanciato consiste nel connettere tutte le porte logiche direttamente alla sorgente di clock. Questo però non è quasi mai possibile perché nei sistemi di ultima generazione il numero di porte da pilotare è elevato e questo fa sì che la capacità di carico pilotata dal generatore di clock diventi troppo grossa. Questo comporta un aumento della potenza dissipata e un incertezza nel timing in quanto i parametri relativi ad una corretta temporizzazione potrebbero essere violati.

Analizziamo alcuni algoritmi utilizzati per il progetto della distribuzione del clock. Prima di fare ciò facciamo le seguenti ipotesi :

- la resistenza e la capacità di linea hanno un rapporto di tipo lineare con il ritardo del segnale di clock;

- tutti i buffer sono identici e contribuiscono con lo stesso ritardo.

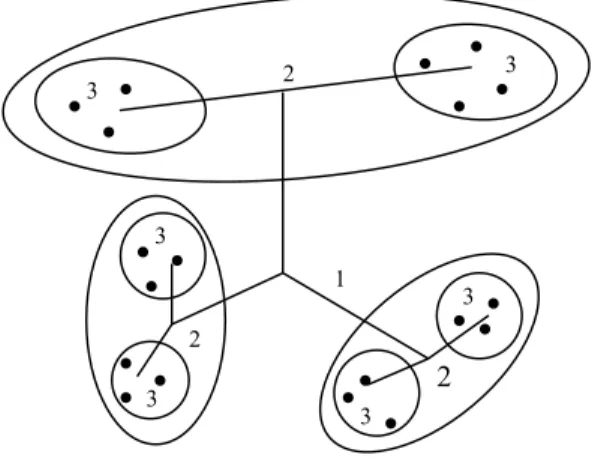

1.4.1 Clustering

Un software utilizzato per il piazzamento di porte logiche posiziona le porte. Porte logiche che soddisfano determinati requisiti relativi all’algoritmo di clustering vengono raggruppate insieme in modo da creare un cluster. Il numero di porte logiche appartenenti ad un cluster e il criterio di raggruppamento sono basati sulla potenza di pilotaggio dei buffer così come sulla velocità che il sistema richiede. Il carico di linea viene bilanciato equalizzando la distanza dal buffer a tutte le porte logiche. In seguito i cluster appartenenti allo stesso livello sono racchiusi da livelli inferiori di cluster. E così via (vedi Figura 1.11).

• • • • • • • 1 2 2 3 • • 3• 3 • •3 • 2 • •3 • • • 3 •

Figura 1.11 Clustering clock tree distribution.

Questo processo continua finchè tutti i buffer dei cluster al livello più basso possono essere guidati da un’ unica sorgente di clock. Questo assicura che il clock skew tra cluster è minimizzato.

Il vantaggio dell’ algoritmo di clustering è la capacità di realizzare un clock skew minimo. Lo svantaggio è che richiede un’elevata potenza di calcolo.

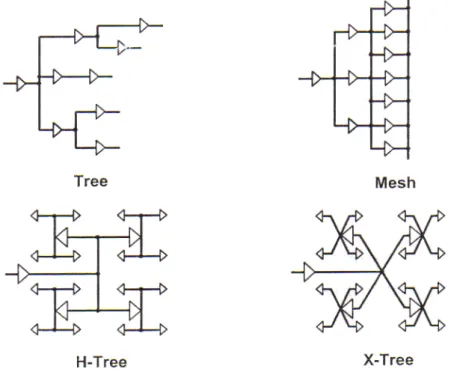

1.4.2 H-Tree

Facciamo una considerazione: se è possibile dividere i registri da pilotare in sottoblocchi identici il clock skew può essere minimizzato. Questa minimizzazione viene fatta distribuendo il segnale di clock in ogni sottoblocco la cui distanza dal nodo di distribuzione del clock è la stessa. Se i segnali di clock sono ugualmente ritardati prima di arrivare ai sottoblocchi, essi saranno perfettamente sincroni.

L’H-Tree può essere diviso ricorsivamente fin quando la tolleranza del clock è raggiunta. La natura simmetrica dell’H-Tree garantisce zero clock skew al centro

di ogni regione, questo implica che tutti i nodi allo stesso livello riceveranno il clock allo stesso istante.

La potenza di tale algoritmo di distribuzione consiste nella sua relativa semplicità di implementazione. Dalla Figura 1.12 notiamo che esistono diverse tipologie di distribuzione del clock ad albero tra cui notiamo una soluzione alternativa all’H-Tree che viene chiamata X-Tree la quale riduce la distanza dal nodo di distribuzione del clock ai vari sottoblocchi. Comunque l’H-Tree rimane una delle tecniche più efficienti.

Figura 1.12 H-Tree clock distribution.

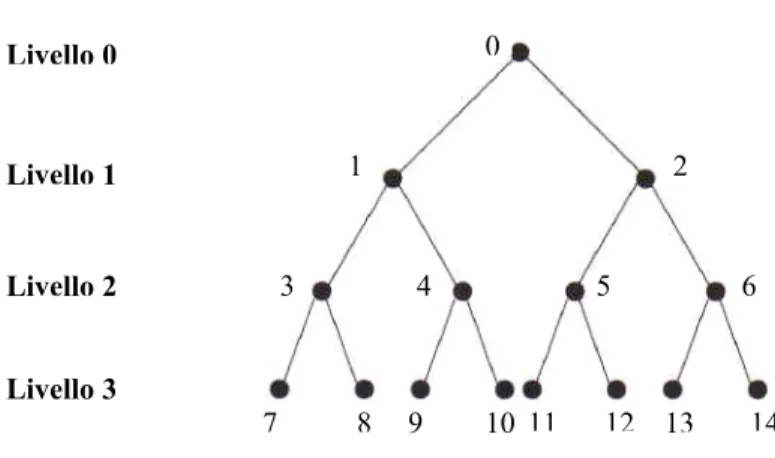

1.4.3 Albero Binario

Tutti i nodi figli appartenenti allo stesso livello hanno la stessa distanza dal nodo radice. Se il periodo di tempo per far arrivare il segnale di clock ad un livello inferiore è identico per ogni nodo figlio allora tutti i nodi figli riceveranno i segnali dal nodo radice allo stesso istante.

La Figura 1.13 mostra un esempio di rete di distribuzione del clock ad Albero Binario. 14 13 12 11 10 7 8 9 4 3 1 2 5 6 0 Livello 3 Livello 2 Livello 1 Livello 0

Figura 1.13 Struttura di una rete di distribuzione del clock ad Albero Binario

1.5 Generazione e sincronizzazione del clock

La quasi totalità dei sistemi oggi sfruttano soluzioni Phase-Locked-Loop

(PLL) o Delay-Locked-Loop (DLL) per la distribuzione e l’equalizzazione del segnale di sincronismo.

Il circuito PLL è un circuito elettronico in cui si utilizza il principio della retroazione negativa per controllare la fase e quindi la frequenza del segnale di uscita. Si tratta in altri termini di un sistema controllato costitutito da: un Phase Detector che costituisce il nodo di confronto; una Charge Pump la quale fornisce l’impulso di tensione che, dopo essere stato opportunamente filtrato, va in ingresso al VCO; il VCO (Voltage Controlled Oscillator) il quale fornisce all’uscita un segnale a frequenza variabile dipendente dall’ampiezza del segnale presente in ingresso; e per finire un Contatore che funziona da divisore di frequenza. Lo schema a blocchi del PLL è mostrato in Figura 1.14. Il DLL, come il PLL, è un circuito elettronico che sfrutta la reazione negativa per il controllo della fase e quindi della frequenza del segnale di uscita. Uno schema a blocchi di

un DLL convenzionale è mostrato in Figura 1.15. Questo circuito contiene una VDCL (Voltage Controlled Delay Line), un Phase Detector, una Charge Pump e un Filtro Passa Basso del primo ordine. La linea di ritardo (VDCL) è costituita da una cascata di stadi di ritardo variabili ed è pilotata da un clock di ingresso di riferimento (clk_ref); il clk_ref e clk_out vanno al Phase Detector che ha il compito di rilevare l’errore di fase. L’uscita del Phase Detector è integrata da una Charge Pump e dal filtro passa basso per determinare la tensione di controllo della VDCL.

Soluzioni di frontiera, che si stanno presentando a livello di ricerca, sono quelle che utilizzano interconnessioni di tipo Wireless e Optical di cui accenneremo il principio di funzionamento in seguito.

Figura 1.14 Schema a blocchi di un PLL [10].

Tornando alle soluzioni che si utilizzano nella pratica [8], gli approcci con DLL si suddividono in:

• Closed-Loop-DLL

Essi impiegano più tempo ad agganciarsi ma in compenso presentano una maggiore robustezza e un continuo aggiustamento del ritardo di fase tra i due segnali.

• Open-Loop-DLL

Essi, rispetto ai DLL ad anello chiuso, hanno il vantaggio di non necessitare del tempo di aggancio ma per contro rinunciano ad un continuo aggiustamento della fase a causa della mancanza di feedback.

I DLL e i PLL [1] sono stati adottati per risolvere, o per lo meno minimizzare il problema dello skew. Se non è richiesta una moltiplicazione di frequenza, i DLL sono da preferirsi dato che sono più stabili e non mostrano la caratteristica di accumulazione dello Jitter come accade nei PLL.

I DLL possono essere classificati in ADLL (Analog-DLL) e DDLL (Digital-DLL). Gli ADLL sono dei DLL che sono controllati con una tensione di tipo analogico mentre i DDLL sono dei DLL controllati con una parola di tipo digitale. Negli ADLL, dato che il ritardo di linea è aggiustato in modo continuo, l’errore statico di fase tra il clock in ingresso e uscita è intrinsecamente più piccolo di quello introdotto dai DDLL. Soluzioni a bassa potenza e piccole aree di chip sono più inclini ad essere realizzate in ADLL. Per contro gli ADLL sono più suscettibili alle variazioni dovute al processo tecnologico e meno immuni al rumore dovuto alla tensione di alimentazione.

Contrariamente i DDLL sono più robusti, meno sensibili al rumore introdotto dalle fluttuazioni del segnale di alimentazione, agli errori di tipo PVT e agli effetti caricanti.

Esistono diverse tecniche e algoritmi per agganciare il clock di riferimento. Alcuni esempi sono: Shift-Register DLL, Up-Down Counter, SAR

(Ricerca Logaritmica) che permette di ridurre il lock time [3], Soluzioni Miste, Spinning Wheel Algorithm (adottato in soluzioni multi-PLL) [4] [9] e per finire una soluzione definita Fast-Locked-Mixed Mode DLL (MMDLL); questa soluzione presenta una parte analogica e una digitale offrendo i vantaggi delle due soluzioni.

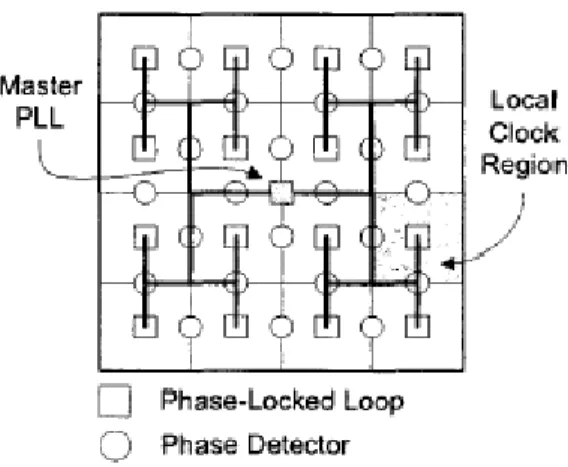

Il rifasamento del segnale di sincronizzazione può essere locale (eseguito nelle regioni più critiche) [5]; in questo caso vengono utilizzati degli Skew Sensor per misurare il ritardo di fase tra le due regioni del Die interessate, per poi correggerlo. Oppure si può adottare una soluzione che prevede un rifasamento globale in tutto il Die usando soluzioni multi-PLL. Questa tecnica consiste nel realizzare un array NxN di PLL che, a partire dal clock di sistema prodotto da un PLL master, equalizzano il segnale nelle varie aree locali di distribuzione rispetto ad un segnale centralizzato. L’architettura di una rete di distribuzione del clock con una soluzione multi-PLL è mostrata in Figura 1.16.

Figura 1.16 Architettura di una rete di distribuzione del clock.

Come detto, elemento fondamentale nel recupero dello skew sono spesso le linee di ritardo variabili. Si distinguono in: linee di ritardo a controllo analogico e linee in cui il ritardo è impostabile attraverso una parola digitale. Queste ultime prendono il nome di DCL (Delay Controlled Line). Sono costituite da celle di ritardo elementari. Tra le soluzioni possibili abbiamo celle a Shunt-Capacitor,

Current-Starved e a Pass-Transistor. Le linee di ritardo costituiscono il cuore di un sistema DLL.

In molte architetture che usano le DCL il ritardo di un singolo elemento determina il massimo skew del clock prodotto. Per ridurre lo skew, il ritardo di ogni elemento della DLL deve essere fatto il più piccolo possibile. Quindi questa soluzione può richiedere molti elementi di ritardo per realizzare nello stesso tempo ampi range di frequenze di lavoro e skew minore [11]. In altre architetture più sofisticate sono stati introdotti meccanismi di regolazione fine tramite i quali è possibile ridurre la risoluzione per la correzione dello skew al di sotto del ritardo di cella [12].

1.6 Le soluzioni del futuro

Tra le soluzioni di frontiera abbiamo accennato alle interconnessioni di tipo Optical [6] per la distribuzione del segnale di clock. Questa soluzione prevede l’integrazione sul Die di guide d’onda per la trasmissione del segnale ottico. La guida per le sue proprietà ci garantisce una larga banda passante. Questa soluzione permette di diminuire la potenza dissipata rispetto alla soluzione classica. L’elemento delicato diventa il ricevitore ottico, il quale costituisce la maggiore sorgente di potenza dissipata in una rete per la distribuzione del segnale di sincronismo con accoppiamento ottico.

Il ricevitore è costituito da un foto rilevatore, un front-end (Transimpedence) e uno stadio di potenza. Il Die è costituito da più livelli di H-Tree i quali dipenderanno dalla profondità di penetrazione del segnale ottico come mostrato in

Figura 1.17.

Le maggiori problematiche che si presentano all’aumentare della frequenza sono:

Stabilità degli stadi di guadagno (Bandwidth);

Capacità di rilevamento (Cdetect) presente sul ricevitore; DSNR (Rapporto Segnale-Rumore Digitale);

Incompatibilità Elettromagnetica.

Vediamo ora in breve in cosa consiste un sistema di interconnessione di tipo Wirless [7]. Esso è costituito da trasmettitori e ricevitori integrati con antenne on-chip che comunicano, attraverso un singolo chip o tra chip diversi, alla velocità della luce attraverso onde elettromagnetiche, come mostrato in Figura 1.18.

Figura 1.18 Illustrazioni concettuali di sistemi (a) intra-chip e (b) inter-chip di connessioni wireless per la distribuzione del segnale di clock

Le interconnessioni wirless possono essere usate sia per i dati che per i segnali di clock. Il segnale viene prodotto on-chip ad una frequenza 8 volte superiore alla frequenza del clock locale e viene applicato ad un’antenna trasmittente che è posizionata in una parte del circuito integrato. Questo segnale è rilevato da un’antenna ricevente anch’essa integrata. Successivamente viene amplificato e opportunamente diviso per ottenere la frequenza del clock locale. Questi segnali di clock sono poi bufferati e distribuiti alla circuiteria adiacente. Alcuni vantaggi che introdurrebbe questo tipo di soluzione sono i seguenti:

I segnali si propagano alla velocità della luce;

Il sistema da integrare diventa più semplice in quanto non è più presente l’albero del clock;

Si liberano fili che possono essere usati per altri scopi; Si riduce: la latenza nel clock tree e il clock skew.

1.7 Soluzione adottata nel nostro studio

La soluzione adottata in questa tesi per il recupero dello skew sfrutta delle linee di ritardo programmabili il cui ritardo è impostabile attraverso una parola digitale. Il problema elementare che abbiamo affrontato è il seguente: supponiamo che il nostro sistema sia abbastanza piccolo da poter essere diviso in due regioni in ognuna delle quali la distribuzione locale del clock non introduce uno skew significativo. Uno skew invece può esistere tra i clock delle due regioni ed è questo skew che deve essere corretto. Supponiamo inoltre di avere a disposizione un unico clock in ingresso per generare i clock delle due regioni. Per generare i clock si usano due linee di ritardo a cui arriva lo stesso segnale di sincronismo; ogni linea è caratterizzata da tre celle di ritardo in ognuna delle quali sono presenti un certo numero di Shunt-Capacitor i quali sono responsabili dei quanti di ritardo elementare.

I vari segnali di clock prodotti vengono prelevati nei punti strategici delle due regioni e riportati in ingresso al Phase-Detector.

Il Phase-Detector avrà il compito di rilevare la presenza di uno sfasamento tra i due segnali. La sua uscita andrà ad un Controllore di Fase, realizzato con un approccio semicustom, il quale genera la parola digitale che pilota la linea di ritardo, introducendo, passo per passo, un certo numero di capacità che faranno sì che al termine della correzione lo skew sia annullato o al limite ridotto a qualche decimo di picosecondo, nel caso ideale.

Il sistema di sincronizzazione progettato per il problema elementare descritto può essere facilmente applicato a sistemi arbitrariamente più complessi una volta che questi siano suddivisi in regioni elementari. I clock delle diverse regioni possono essere equalizzati a due a due.

1.7.1 Architettura

L’architettura utilizzata in questa tesi è del tipo: Dual-Zone Clock

Deskew. I blocchi che la caratterizzano sono : Due Linee di ritardo variabili; Il Phase Detector;

Il Controllore di Fase;

collegati come mostrato in Figura 1.19. Gli elementi di ritardo elementare presenti sulle due linee di ritardo sono realizzati con delle capacità di carico realizzate con degli Shunt-Capacitor. Le capacità sono inserite in maniera totalmente digitale attraverso una parola prodotta dal Controllore di Fase che implementa i due algoritmi di correzione realizzati in questo lavoro di tesi. Il Phase Detector funge da skew sensor rilevando lo sfasamento tra i due segnali di sincronismo e producendo due impulsi che pilotano il Controllore di Fase discriminando tra i due possibili segni dello sfasamento. Il Controllore di Fase riconosce le due possibili configurazioni dello sfasamento e in base a questo produce le parole digitali necessarie per la correzione dello skew.

0 0 E1 E2 C0 B6_1 B6_2 Out_2 Out_1 Clk_1 Path_1 Out 2 Path_2 Out 1 Clk_2 ∆2 ∆1 S1 S2 S1 S2 E1 E2 C0 C9 B0_2 B6_2 E1 E2 C0 C9 B0_1 B6_1 Clk_2 Clk_1 Clk_2 Clk_1 /Trig Trig

Phase Detector

(Skew Sensor)

Controllore

1 1 Clk_sysLINEA 1

LINEA 2

Figura 1.19 Architettura del Dual-Zone Clock Deskew

I segnali presenti nel circuito hanno i seguenti significati:

I segnali di controllo (E1,E2) introducono l’offset sulla Linea_2 e garantiscono l’equalizzazione del ritardo nominale (cioè con capacità di carico disinserite e assenza di offset) tra le due linee. Nei capitoli successivi spiegheremo con più dettaglio il loro utilizzo.

I segnali di controllo (S1,S2) pilotano il Mux a due vie, deviando i segnali in uscita dalle linee in modo tale che il segnale che risulta essere

in anticipo venga pilotato dalla linea in cui è presente l’offset e in cui sono presenti i ritardi differenziali maggiori;

I segnali B0_1…B6_1 pilotano le capacità di bisezione di Linea_1; I segnali B0_2…B6_2 pilotano le capacità di bisezione di Linea_2; I segnali C0…C9 pilotano le capacità differenziali di entrambe le linee; Con ∆1 e ∆2 vengono indicati i ritardi introdotti dalla diversa lunghezza

dei percorsi di interconnessione (path_1, path_2) e dai diversi carichi visti dai relativi percorsi.

1.7.2 Strategia per la correzione

Come è stato già accennato, lo scopo del nostro circuito è quello di riuscire a recuperare lo skew del segnale di clock, introdotto per esempio dalla diversa lunghezza delle piste di interconnessione percorse dal segnale prima di arrivare a sistemi che devono lavorare tra di loro in maniera perfettamente sincrona.

tckA tckB tPDMUX tPDMUX PATH2 PATH1 τnom DCL 2 τnom DCL 1 tck_sys ctr ctr PATHB PATHA tPDB tPDA B A tck1 tPD2 tPD1 EN EN tckB’ tckA’ tck2 1 1 0 0 DCL_2 DCL_1 Figura 1.20

In Figura 1.20 è rappresentato lo schema di principio del sistema di deskewing con tutti i relativi ritardi introdotti dai diversi blocchi. Vediamo di dare una spiegazione più esaustiva di alcuni di questi ritardi. Intanto si deve specificare che i punti A e B rappresentano gli ingressi dei registri a cui arriva il segnale di clock. PATHA e PATHB sono i percorsi che deve compiere il segnale per essere

riportato in ingresso al deskewer e devono essere perfettamente uguali in modo tale che i ritardi da essi introdotti siano esattamente gli stessi (tPDA = tPDB) affinché

non si alteri la misura dello skew. Dove:

tPD1 è il ritardo di propagazione di PATH1.

tPD2 è il ritardo di propagazione di PATH2.

τnom_DCL_1 e τnom_DCL_2 sono i ritardi nominali introdotti rispettivamente

dalle due linee di ritardo DCL_1 e DCL_2 quando tutti i carichi sono disinseriti e in assenza di offset.

Quando le due linee sono scariche allora deve essere verificata la seguente uguaglianza: τnom_DCL_1 = τnom_DCL_2 condizione garantita dal fatto che il layout è

realizzato in maniera perfettamente simmetrica in modo da ridurre il mismatch circuitale.

(

)

(

)

(

)

[

PDMUX PDMUX]

PDMUX B n n DCL nom sys ck ck t ctr t ctr t b b N t t ⋅ + ⋅ + + + ∆ ⋅ + + ⋅ + ∆ ⋅ + + = τ τ − − τ 0 1 1 1 1 _ _ _ 1 2 ....(

)

(

)

(

)

[

PDMUX PDMUX]

PDMUX B n n DCL nom sys ck ck t ctr t ctr t b b N t t ⋅ + + ∆ ⋅ + + + ∆ ⋅ ′ + + ′ ⋅ + ∆ ⋅ + + = − − 0 0 1 1 2 2 _ _ _ 2 2 .... τ τ τ τ (1.1) dove:∆τ0 = (2n-1+ …. +1)·∆τB è l’offset introdotto per poter applicare

correttamente l’algoritmo di Bisezione doppio; N è il numero di capacità differenziali;

ctr è il bit di controllo per l’inserimento dell’offset. Questo segnale di controllo è presente su entrambe le linee in quanto l’offset è introdotto attraverso un Mux a due vie e per rispettare la simmetria richiesta per il corretto funzionamento del Deskewer è stato necessario inserire un Mux

a due vie identico a quello presente sulla linea due in modo da garantire lo stesso tPD ( tempo di propagazione) del Mux su entrambe le linee;

[bn-1 …. b0] e [b’n-1 …. b’0] sono la configurazione di bit della parola

digitale da produrre per impostare il ritardo desiderato;

∆τ1 è il ritardo introdotto da ciascuna capacità differenziale della

DCL_ 1;

∆τ2 è il ritardo introdotto da ciascuna capacità differenziale della

DCL_ 2; ∆τ2 > ∆τ1;

∆τB è il ritardo elementare introdotto dalle capacità per la correzione

effettuata con l’algoritmo di Bisezione; quando si ha:

N =0

[

bn−1....b0]

=[

0....0]

dove n è il numero di pesi ctr=0allora il Deskewer è spento (τnom_DCL_1 = τnom_DCL_2);

tCKA =tCK1 +tPD1

(2.1) tCKB =tCK2+tPD2

Quando il Deskewer è spento e supponiamo ad esempio tPD2 > tPD1 (per simmetria

vale anche nel caso contrario) allora si ha:

(3.1) tskew_iniziale =tCKB −tCKA =tPD2 −tPD1 =tCKB′ −tCKA′

questo è vero poiché PATHA e PATHB sono uguali e quindi tPDA = tPDB.

(

)

[

(

) (

)

]

(

2 1)

0 0 1 1 0 1 1 1 2 _ 2 .... 2 .... PD PD B n n n n finale skew t t ctr b b b b N t − + ∆ ⋅ + + ∆ ⋅ + + ⋅ − ′ + + ′ ⋅ + ∆ − ∆ ⋅ = − − − − τ τ τ τPer effettuare tale correzione si è pensato di utilizzare due algoritmi: quello di Bisezione e quello Differenziale al Nonio, che lavorano tra di loro in modo indipendente.

Il primo passo sarà quello di effettuare una correzione grossolana utilizzando la Bisezione. Su entrambe le linee sono presenti lo stesso numero di capacità che introducono esattamente gli stessi ritardi (stessi pesi). Dopo un certo numero di passi (7 nel nostro caso) si sarà effettuata la prima correzione grossolana dello skew. Con l’algoritmo di bisezione si riesce a recuperare uno skew massimo di 228 ps circa.

Terminato l’algoritmo di bisezione ci ritroviamo con uno skew residuo che avrà un valore massimo di 2 ps. A questo punto si fa partire l’algoritmo differenziale il quale ha il compito di recuperare tale skew residuo. Per la correzione differenziale è importante fare una distinzione tra le due linee. Infatti su ognuna di esse sono introdotte 10 capacità uguali tra loro ma con pesi diversi sulle due linee. Ad ogni passo si introduce una capacità, in modo simmetrico, su ciascuna linea, infatti gli stessi segnali di controllo andranno alle 2 linee. Grazie al fatto che le due capacità introdotte hanno un peso diverso, introducono quindi ritardi diversi, ad ogni passo si recupererà un certo ritardo ∆ che sarà dato dalla differenza dei ritardi introdotti dalle due capacità.

(

∆τ2 −∆τ1)

=∆

Nella correzione differenziale bisogna sottolineare che il numero di passi non sarà necessariamente pari al numero di capacità presenti, in questo caso 10, ma l’algoritmo terminerà quando si verifica un’ inversione di fase rispetto alla situazione di partenza. Si può notare che in questo modo viene sfruttata la differenza tra i ritardi introdotti da una singola capacità. Questo ci consenta di utilizzare capacità ad area maggiore che sono meno soggette a problemi di

mismatch. Comunque, della strategia di correzione adottata si parlerà in modo più approfondito nei capitoli successivi.

Bibliografia

[1] Guang-Kaai Dehng, Student Member, Jyh-Woei Lin and Shen-Iuan Liu, Member, IEEE, “ A

Fast-lock Mixed-mode DLL Using 2-b SAR Algorithm”, IEEE 2001 Custom Inyegrated

Circuits Conference, pp. 489-492.

[2] Kenneth Yip, “Clock Tree Distribution” , IEEE April-May 1997,pp. 11-14.

[3] Guang-Kaai Dehng, Student Member, IEEE, June-Ming Hsu, Ching-Yuan Yang, Student

Member, IEEE, and Shen-Iuan Liu, Member, IEEE, “Clock-deskew Buffer Using a SAR-Controlled Delay-Locked Loop”, IEEE Journa of Solid-State Circuits, vol. 35, no. 8, August

2000, pp. 1128-1136.

[4] Martin Saint-Laurent, Madhavan Swaminathan and James D. Meindl, “On the

Micro-Architectural Impact of Clock Distribution Using Multiple PLLs”, IEEE 2001,pp. 214-220.

[5] S.H.K. Embabi and D.E. Brueske, “Clock Syncronization for WSI Systems”, 1994

International Conference on Wafer Scale Integration, pp. 228-234.

[6] Pawan Kapur and Krishna C. Saraswat, “Power Dissipation in Optical Clock Distribution

Network for High Performance Ics”, IEEE 2002, pp. 151-153.

[7] Brian A. Floyd, Chin-Ming Hung and Kenneth K. O., “Intra-Chip Wireless Interconnected for

Clock Distribution Implamented with Integrated Antennas, Receivers and Transmitters”,

IEEE Journal of Solid-State Circuits, vol. 37, no. 5, May 2002, pp. 543-552.

[8] Tac-Sung Kim, Sung-Ho Wang and Bcomsup Kim, “A Low Jitter Fast Locking Delay Locked

Locked Loop Using Measure and Controll Scheme”, IEEE 2001, pp. 45-50.

[9] Marin Saint-Laurent, Payman Zarkesh-Ha, Madhavan Swaminathan and James D. Meindl,

“Optimal Clock Distribution with an Array of Phase Locked Loops for Multiprocessor Chips”,

IEEE 2001, pp. 454-457.

[10] Stefan Rusu, Senior Principal Engineer Enterprise Processor Division Intel Corporation,

“Trends and Challenges in Clock Generation and Distribution”, ESSDERC ESSCIRC 2002

Satellite Workshop,Florence Italy 27 september 2002, pp.81-103.

[11] Masayuki Miyazaki and Koichiro Ishibashi Central Reaserch Laboratory, Hitachi, Ltd.,

Tokyo, “A 3-Cycle Lock Time Delay-Locked Loop with a Parallel Phase Detector for Low Power Mobile Systems”, IEEE 1999, pp.396-399.

[12] Gary C Moyer, Student Member, IEEE, Mark Clements, Student Member, IEEE, Wentai Liu,

Senior Member, IEEE, Toby Shaffer, Student Member, IEEE and Ralph K. Cavin, III, Fellow, IEEE “The Delay Vernier Pattern Generation Technique”, IEEE journal of solid-state circuits, Vol. 32, NO.4, April 1997.

![Figura 1.3 (a) Definizione di t skew [10] ; (b) Clock tree non sincronizzato.](https://thumb-eu.123doks.com/thumbv2/123dokorg/5635861.69305/3.892.189.776.737.994/figura-definizione-t-skew-b-clock-tree-sincronizzato.webp)

![Figura 1.4 Errori dovuti alla temperatura, al carico, all’alimentazione e al processo [10]](https://thumb-eu.123doks.com/thumbv2/123dokorg/5635861.69305/4.892.185.610.376.642/figura-errori-dovuti-temperatura-carico-alimentazione-processo.webp)

![Figura 1.14 Schema a blocchi di un PLL [10].](https://thumb-eu.123doks.com/thumbv2/123dokorg/5635861.69305/16.892.195.752.538.674/figura-schema-blocchi-pll.webp)