UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

81

CAPITOLO 4

Implementazione del Ricevitore digitale

4.1 Schema generale di progetto del ricevitore

Nel capitolo precedente abbiamo descritto il sistema di ricezione in tutte le sue parti. In particolare abbiamo approfondito la tecnica del sottocampionamento, in quanto vogliamo applicarla al segnale prelevato dalla nostra bobina RF.

Il seguente schema rappresenta in forma grafica lo schema a blocchi di progetto del ricevitore digitale per applicazioni di risonanza magnetica con tecnica di Undersampling comprensivo del filtro analogico antialiasing, realizzato in questo lavoro di tesi.

Figura 4.1 - Schema a Blocchi Ricevitore

Prima di passare alla descrizione del singolo blocco riassumiamo le caratteristiche del nostro segnale:

• frequenza centrale fC ≅ 7.66 MHz

• B = 50-55 KHz .

A questo punto è fondamentale scegliere una frequenza di campionamento che ci consenta di centrare il segnale in una zona di Nyquist.

A

A

D

D

C

C

D

D

D

D

C

C

Passivo Ellittico 6°ordine AD6620F

F

i

i

l

l

t

t

r

r

o

o

P

P

a

a

s

s

s

s

a

a

b

b

a

a

n

n

d

d

a

a

AD9245 14 Bit 80MSPSImplementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

82 Per sperimentare ed evidenziare gli effetti dell’oversampling, abbiamo deciso di campionare con due frequenze diverse sempre operando undersampling. La prima frequenza che abbiamo scelto è pari a 2.7648 MSPS, ottenuta tramite una divisione per quattro da una frequenza di 11.0592 MHZ relativa ad un oscillatore commerciale.

Tale frequenza ci consente di centrare il nostro segnale nella sesta zona di Nyquist, come risulta dalla (4.2) (la fC per tali valori è pari a 7.603 MHz, molto

vicino comunque a 7.66 MHz) e come rappresentato in fig 4.1.

Figura 4.2 - Rappresentazione del segnale nello spettro di Nyquist

A questo punto, vediamo dove va a cadere la replica del segnale in seguito al campionamento. Riprendendo la (3.12), si ha che

MHz . MHz . MHz .66 mod27648 21304 7 =

tale valore è relativo alla seconda zona di Nyquist, perciò per ottenere l’esatta posizione nella prima zona di Nyquist, dobbiamo effettuare un’ulteriore operazione, come riportato nella tabella 3.2 del capitolo precedente:

KHz input fS 634.4 3 − = fS 3fS 1.3824 2.7648 7.66 MHz 5a 6a 50-55 KHz 1a 2a 3a 4a

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

83 al centro cioè della prima zona di Nyquist ( 1/2 * fS/2 = 691.2 KHz ).

Quanto detto è rappresentato in fig 4.2.

Figura 4.3 - Rappresentazione dell’alias del segnale nello spettro di Nyquist in seguito al sottocampionamento.

La scelta di questa frequenza di campionamento consente di rilassare le caratteristiche del filtro anti-aliasing a monte del convertitore analogico digitale, nonché di ottenere un processing gain pari almeno a

dB B fS 14 2 log 10 ≅

Tale fattore di oversampling deriva dall’aver considerato, come riferimento per la velocità dei dati in uscita, la banda massima B = 50-55 KHz del segnale “captato” dalla nostra bobina.

La seconda frequenza che abbiamo scelto è pari alla massima fornita dall’oscillatore da noi acquistato, cioè 11.0592 MSPS. Il segnale in questo caso viene centrato nella seconda zona di Nyquist . Come abbiamo fatto in precedenza vediamo ora dove va a cadere la replica del segnale in seguito al campionamento. Riprendendo la (3.12) si ha che:

7.66MHz mod 11.0592MHz = 7.66MHz

(4.1)

fS 3fS

0.6912 2.7648 7.66 MHz

alias in seguito al sottocampionamento

• • •

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

84 tale valore è relativo alla seconda zona di Nyquist perciò per ottenere l’esatta posizione nella prima, anche in questo caso dobbiamo effettuare un’ulteriore operazione, come riportato nella tabella 3.2 del capitolo precedente:

fs-input=3.3992MHz

al centro cioè (in questo caso in maniera approssimativa) della prima zona di Nyquist (1/2*fs=5.5296MHz).

In questo caso il process gain è pari a

dB B fS 20 2 log 10 ≅

quindi ci aspettiamo un rapporto segnale rumore maggiore rispetto al campionamento a 2.7648MHz.

In realtà, poi, la velocità di campionamento dei dati in uscita è strettamente legata, oltre che, evidentemente, alla banda caratteristica della bobina di ricezione del segnale RF, anche alla risoluzione che si vuole ottenere e, quindi, al FOV che si desidera perseguire.

Quando abbiamo parlato delle tecniche di imaging, abbiamo visto come, in presenza di un gradiente di campo magnetico, si abbia

relativamente alla frequenza di Larmor si ottiene che

x xG f f = 0 +γ . 0 f xGx f f − =∆ =γ ⇒

Per rilevare un range di frequenze ∆f è necessaria una certa frequenza di campionamento in uscita fSout; in particolare, in presenza di un gradiente, questo

(

B0 xGx)

;f =γ + (4.3)

(4.4) (4.5) (4.2)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

85 range corrisponde alla distanza attraverso l’immagine lungo la direzione di codifica in frequenza, vale a dire proprio al FOV [7] .

Quindi, f Sout FOVG f =γ . f Sout G f FOV γ = ⇒

Ciò significa che, volendo ottenere un certo FOV, ed avendo a disposizione un determinato Gf, fSout deriva direttamente dalla (4.6); c’è da dire che, diminuendo la

fSout, aumenta proporzionalmente la finestra di campionamento del FID o

dell’echo.

Il vantaggio di una fSout più bassa è quello di ottenere un SNR maggiore, mentre

gli svantaggi sono un aumento degli artefatti dovuti allo shift chimico, una perdita del contrasto nell’immagine e un ristretto intervallo di tempi di echo TE.

Facciamo un esempio: supponiamo di avere a disposizione un Gf = 5 G/cm (tipico di un applicazione di microimaging) e di voler ottenere un FOV di 1cm; sostituendo tali valori nella (4.5), otteniamo fSout = 21.29 KHz.

Nella nostra applicazione, quindi, considereremo la possibilità di ottenere diverse frequenze di campionamento dei dati in uscita; cioè, partendo dalla fSout massima

(50-55 KHz) legata alla banda della bobina RF, scaleremo la velocità dei dati in uscita rispetto al valore massimo, fino a raggiungere 4-5 KHz, contemplando in questo modo alcuni dei possibili casi relazionati a varie combinazioni di FOV e Gf. In conclusione, questo significa poter raggiungere fattori di

sovracampionamento maggiori e, di conseguenza, un processing gain migliore di quanto calcolato nella (4.1).

4.2 Realizzazione Filtro Passabanda

La realizzazione del filtro è di primaria importanza per una linea di ricezione con undersampling.

(4.6)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

86 Prima di passare alla descrizione del progetto facciamo una necessaria introduzione sulle varie categorie di filtri.

Nei circuiti elettronici i filtri sono elementi selettivi che consentono il passaggio di segnali elettrici a frequenze o campi di frequenze determinati mentre bloccano il passaggio di segnali indesiderati in campi frequenziali diversi.

I filtri possono essere utilizzati per ridurre segnali indesiderati, facilitare il recupero di segnali voluti, limitare la larghezza di banda, minimizzare aliasing in sistemi a dati campionati, etc. etc.

Nel nostro caso è necessario l’uso di un filtro passabanda cioé dedicato alla reiezione di segnali al di fuori della banda passante.

Si definiscono Attivi , quei filtri realizzati con l’uso di resistenze ,capacità ed elementi attivi ( amplificatori operazionali ) e Passivi quelli realizzati con l’uso di induttanze, capacità e resistenze.

I filtri attivi hanno lo svantaggio di introdurre rumore aggiuntivo, per la presenza degli

Op-Amp,e inoltre, fino a poco tempo fa, alle alte frequenze ( > 1MHz ) a causa delle performance dinamiche degli stessi Op-Amp ne era interdetto l’ utilizzo. Grazie però alle evoluzioni tecnologiche in questo campo, proprio nel laboratorio Iteni ,presso l’Istituto di Fisiologia Clinica, si sta realizzando

un filtro attivo passa banda del secondo ordine per Figura 4.4 - Ex. Filtro 2°

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

87 Il grosso punto debole invece dei filtri passivi risiede nel fatto che si usano induttanze, che introducono svantaggi legati alle dimensioni elevate, alla resistenza di perdita, all’accoppiamento magnetico ed alla dispersione di flusso. Va detto però che nel campo frequenziale di lavoro le induttanze in gioco come dimostrano le simulazioni seguenti, sono previste induttanze di valori al massimo dell’ordine della decina di µH, cioè ragionevolmente bassi da poter essere utilizzati senza grossi problemi.

In definitiva i filtri passivi alle radio frequenze mostrano davvero pochi effetti secondari e altrettanto pochi problemi di stabilità associati, invece, alle relative controparti attive.

Nella figura a pagina precedente è rappresentato un esempio molto semplice di filtro passabanda passivo del secondo ordine con indicata la funzione di trasferimento nel dominio di s. In a) è riportata la risposta in frequenza dell’ ampiezza

e in b) della fase :

L’ordine del filtro è rappresentato dal massimo grado del denominatore della funzione di trasferimento.

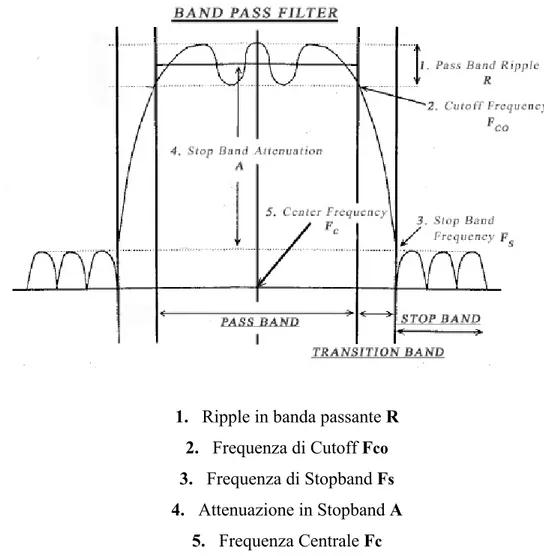

La risposta in frequenza di un filtro passabanda e i suoi parametri fondamentali sono riportati di seguito.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

88 (4.8)

1. Ripple in banda passante R

2. Frequenza di Cutoff Fco

3. Frequenza di Stopband Fs

4. Attenuazione in Stopband A

5. Frequenza Centrale Fc

Figura 4.5 - Risposta in ampiezza di un filtro passabanda generico e parametri fondamentali

Un parametro di merito del filtro è rappresentato dal fattore di Qualità definito come: l h c f f f Q − =

Cioè il rapporto tra la frequenza centrale e la banda passante del segnale. Esistono varie tipologie di filtri.

I filtri di Butterworth mostrano il migliore compromesso tra attenuazione e risposta in fase, non presentano ripple nella passband e nella stopband. Appartengono alla categoria di filtri a risposta massimamente piatta.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

89 I filtri di Chebyshev presentano, chiaramente rispetto al filtro dello stesso ordine di Butterworth, una regione di transizione minore, pagando nella presenza di un certo ripple in passband e in stopband.

La riduzione della regione di transizione implica la possibilità estremamente importante in un filtraggio passabanda, a parità di ordine del filtro, di ottenere una campana quanto più possibile stretta e vicina alla risposta ideale ( rettangolare ). Per raggiungere questo target allora si preferisce utilizzare un filtro di tipo

Ellittico il quale evidenzia una zona di transizione ancora più ridotta rispetto al corrispondente di Chebyshev.

Lo scotto da pagare, come già accennato sopra, è la presenza di un certo ripple che, se al di sotto della soglia critica di 0.1 dB, non compromette la qualità dell’immagine finale.

4.2.1 Progetto Filtro

Questa tesi propone un metodologia di progetto che parte dall’ utilizzo di un simulatore scaricabile gratuitamente dalla rete.

Il simulatore utilizzato è il seguente: FilterMaster v.1.0 ( Omicron Electronic

1991 ).

Per un primo prototipo si è deciso di partire da un filtro almeno del 6° ordine Ellittico per poter avere una attenuazione accettabile nella zona di Nyquist corrispondente al segnale di interesse.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

90

Elliptic - Bandpass filter 6

thOrder

Lower passband limit frequency : 7.500 000 MHz

Upper passband limit frequency : 7.800 000 MHz

Lower stopband limit frequency : 6.900 000 MHz

Upper stopband limit frequency : 8.478 261 MHz

Passband attenuation : 0.100 000 dB

Return loss : 16.43 dB

Stopband attenuation : 50.78 dB

Degree : 6

Il simulatore restituisce la configurazione circuitale e i corrispondenti valori dei componenti. ----R---- 50.000 000 Ω | | | L 26.878 030 µH | | | C 16.109 682 pF | |

--L---C-- 1.463 090 µH Resonance frequency Pole-No.1

| | 375.158 743 pF 6.793 243 MHz

| |

--L---C-- 1.154 169 µH Resonance frequency Pole-No.2

| | 295.946 676 pF 8.611 499 MHz | | | L 26. 878 030 µH | | | C 16. 109 682 pF | | -- R --- 50.000 000 Ω

Come si evince dalla tabella di cui sopra, i valori restituiti dal simulatore sono ben lontani dall’essere valori commerciali.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

91 (4.9) Figura 4.6 - Risposta in ampiezza filtro simulato

4.2.2 Scelte implementative

In un circuito sì fatto è necessario scegliere opportunamente i condensatori e gli induttori per l’implementazione del filtro.

Per ciò che concerne i primi è necessario impiegare capacità ad alto fattore di bontà Q definito come:

p CR

Q=ω

Dove Rp è la resistenza parallela che rappresenta le perdite, C è il valore della

capacità e ω è la pulsazione di lavoro.

A tale scopo abbiamo utilizzato condensatori forniti dalla ATC ( American Technical Ceramics, USA ) , che presentano un fattore di qualità Q > 10.000

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

92 (4.10) Figura 4.7 - Datasheet Atc 100 E series.

Per il tuning fine della risposta in frequenza del filtro sono stati impiegati, inoltre, dei trimmer capacitivi anch’essi ad alta qualità.

Per quanto riguarda gli induttori, per rispondere all’esigenza di ottenere dei valori di induttanza prossimi a quelli ottenuti con il simulatore, quindi chiaramente non presenti commercialmente, si è ritenuto di procedere con l’avvolgimento in aria, o su supporto ferromagnetico, di filo di rame dimensionando l’induttore così ottenuto attraverso l’impiego di una formula empirica :

B A A N L 10 9 ) ( 10 2 + ⋅ = πµ con:

N = numero d’avvolgimenti B = lunghezza solenoide µ = permeabilità magnetica del mezzo A = raggio solenoide

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

93 La verifica degli induttori così realizzati è stata fatta ponendo gli stessi in parallelo a capacità note e successivamente misurando la frequenza di risonanza del circuito mediante un Dual Loop Probe [ 21 ] collegato ad un Network Analyzer HP3577A ( 5 Hz - 200 Mhz ).

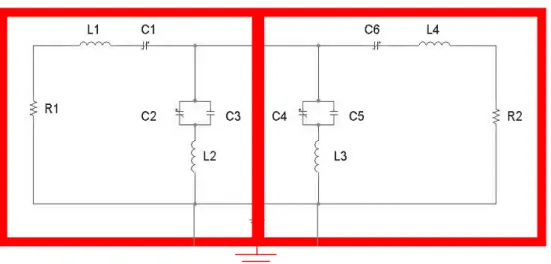

Figura 4.8 - Circuito Filtro Passabanda

La figura di sopra rappresenta il circuito nella sua realizzazione finale.

In ogni ramo è presente un’induttanza in serie ad un parallelo di capacità composto da un condensatore fisso ed uno variabile per ottenere valori quanto più possibili vicini a quelli forniti dal simulatore.

La resistenza in uscita e quella in ingresso rappresentano la resistenza del cavo coassiale per inserire e prelevare il segnale dalla bobina.

Particolare attenzione è stata posta in fase di progetto alla disposizione delle induttanze all’interno del dispositivo.

Il circuito è stato diviso idealmente in due parti da uno schermo metallico completamente separate induttivamente, e successivamente è stato inserito in una scatola di rame ( in rosso in figura 4.8 ).

Nella singola sezione poi è stato necessario predisporre le induttanze ortogonalmente per eliminare il più possibile eventuali interazioni mutue.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

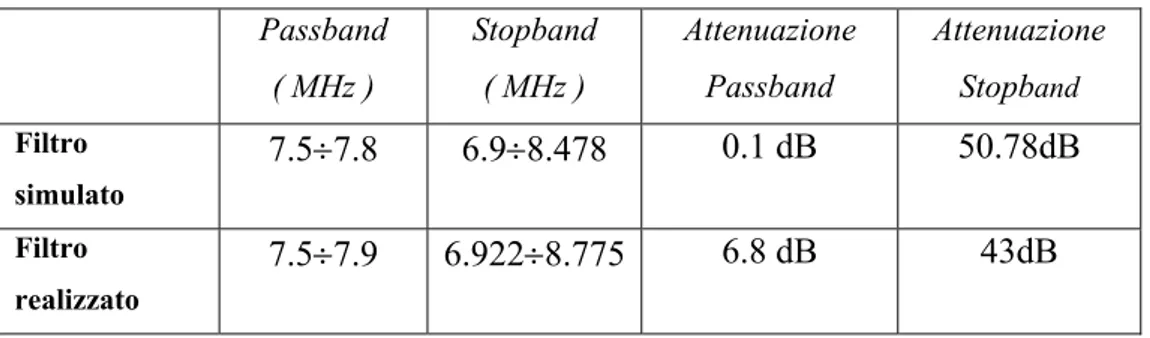

94 I risultati ottenuti sono riportati nella tabella di cui sotto:

Tab.4.1 - Confronto filtro realizzato e filtro simulato

Passband ( MHz ) Stopband ( MHz ) Attenuazione Passband Attenuazione Stopband Filtro simulato 7.5÷7.8 6.9÷8.478 0.1 dB 50.78dB Filtro realizzato 7.5÷7.9 6.922÷8.775 6.8 dB 43dB

La tabella mette in evidenza un risultato molto soddisfacente.

La tecnica utilizzata è dunque molto efficiente e può essere riproposta per filtri di ordine superiore al 6° , cioè filtri più selettivi e sempre più vicini alla idealità.

(a) (b)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

95 Figura 4.10 -Risposta in frequenza misurata con Network Analyzer

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

96

4.3 Individuazione del convertitore analogico-digitale

4.3.1 Convertitore con Sample and Hold anteposto

In una prima ricerca non abbiamo trovato un convertitore che avesse basso aperture jitter, risoluzione pari a 14 bit e velocità adeguata alla nostra applicazione. Ci eravamo quindi orientati su un ADC che soddisfacesse gli ultimi due requisiti, pensando di anteporvi un SHA su cui far ricadere le problematiche relative all’incertezza sull’istante di campionamento. Il convertitore analogico-digitale che avremmo scelto per sottocampionare il segnale prelevato dalla bobina RF è l’ AD9243 dell’Analog Device [12] .

Questo ADC è caratterizzato da una velocità di campionamento massima di 3 MSPS (quindi in questo caso l’unico campionamento possibile sarebbe stato quello a 2.7648 MHz) e da una dinamica fino a 14 bit.

Un diagramma a blocchi dell’ADC è riportato in fig 4.2.

Figura 4.11 - Diagramma a blocchi dell’AD9243

Il dispositivo utilizza una architettura a 4 stadi in pipeline con in ingresso un amplificatore sample-and-hold (SHA) ad ampia banda.

Ogni stadio del pipeline, escluso l’ultimo, consiste di un flash A/D a bassa risoluzione connesso ad un DAC e ad un amplificatore di residuo; il compito di quest’ultimo è quello di amplificare la differenza tra l’uscita del DAC e l’ingresso del flash per il successivo stadio in pipeline.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

97 Un bit di ridondanza è utilizzato in ogni stadio per facilitare la correzione digitale degli errori di ogni flash.

L’ultimo stadio, infine, consiste di un flash A/D.

L’uscita digitale è portata in un buffer che pilota i pin d’uscita; i drivers d’uscita possono essere configurati in modo tale da interfacciarsi con famiglie logiche a +5V e a +3.3V. L’ADC può essere inoltre configurato per trattare segnali in ingresso con span di 5 V o di 2 V.

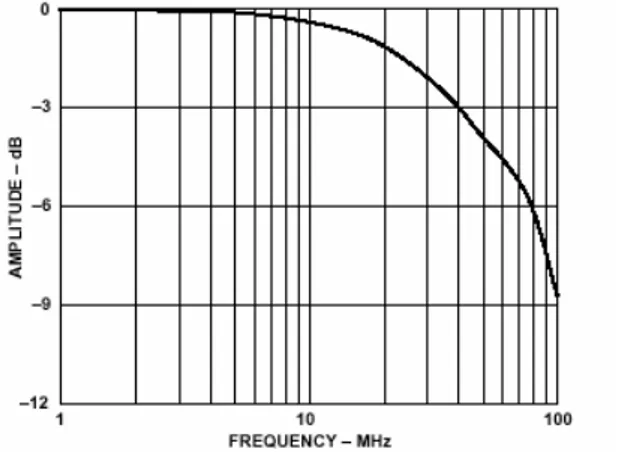

Riportiamo ora alcune curve significative ai fini della nostra applicazione.

Figura 4.12 - SINAD in funzione della frequenza di ingresso (input span = 2V, VCM = 2.5V)

I datasheet del componente dichiarano, come è evidente anche dal grafico di fig 4.12, un SINAD pari a 75dB e un SNR di 80dB anche alla nostra frequenza di interesse (7.66 MHz circa), dove per SINAD si intende il rapporto del valore rms del segnale d’ingresso con il valore rms della somma di tutte le altre componenti spettrali sotto la frequenza di Nyquist, incluse tutte le armoniche esclusa la dc, mentre nell’ SNR il raffronto è fatto con tutte le componenti spettrali eccetto le prime sei armoniche e la dc.

In fig 4.13 è riportata la banda a piena potenza del convertitore, che si spinge fino a 40 MHz, ben al di sopra della nostra frequenza di interesse.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

98 Figura 4.13 - Banda a piena potenza del convertitore

Figura 4.14 - (a) THD in funzione della frequenza di ingresso (b) THD in funzione della velocità di campionamento e per diversi span

La fig 4.14, invece, rappresenta la Total Harmonic Distorsion (definita come il rapporto tra il valore rms della somma delle prime sei armoniche e il valore rms del segnale d’ingresso misurato) in funzione della frequenza d’ingresso (a) e della velocità di campionamento (b) .

Altre due curve importanti da analizzare sono riportate in fig 4.15, dove si fa riferimento all’ SFDR caratteristico del dispositivo, parametro che abbiamo indicato come fondamentale ai fini di un sottocampionamento. In entrambe le rappresentazioni l’ SFDR è riportato in dBc (riferito al valore massimo del segnale) e in dBFS (riferito al valore di fondo scala); in particolare, nelle due

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

99 figure, la frequenza di ingresso è pari 1.5 MHz, e le curve evidenziano un SFDR di almeno 90 dBFS.

Ancora più significative sono le curve riportate in fig 4.16, dove è rappresentata una tipica performance di sottocampionamento dell’AD9243, in cui cioè un segnale a 10.7 MHz è digitalizzato ad una frequenza di campionamento di 2.5 MHz; in seguito al campionamento la frequenza risultante del segnale è di 700 KHz (vedi fig 4.16(b)).

Il grafico di fig 4.16(b) conferma che l’AD9243 si presta ottimamente alla nostra applicazione, in quanto il dispositivo dovrebbe garantire un alto grado di linearità e di SFDR su un vasto range di ampiezze.

Figura 4.15: (a) Single Tone SFDR ( fIN = 1.5 MHz , VCM = 2.5 V )

(b) Dual Tone SFDR ( f1 = 0.95 MHz , f2 = 1.04 MHz , VCM = 2.5 V )

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

100 Figura 4.16: (a)Sottocampionamento alla frequenza di 10.7 MHz mediante AD9243 ( VCM

= 2.5V , span d’ingresso 2 VP-P )

(b) SNR/SFDR relativamente ad un ingresso differenziale dell’ AD9243 in funzione della Ampiezza d’Ingresso (AIN) @ 10.7 MHz

L’AD9243 però presenta un aperture jitter piuttosto elevato, pari a 4 ps rms e l’effetto di tale fenomeno, secondo noi, rischierebbe di diventare preponderante e di portare a risultati molto peggiori di quelli attesi. La soluzione più interessante a questo problema, sarebbe stata quella ,già accennata nel capitolo precedente, di anteporre all’ADC un circuito di Sample and Hold che presentasse un’incertezza più bassa. Il SHA da noi scelto sarebbe stato l’AD9100 dell’Analog Devices [23]. Esso è caratterizzato da aperture jitter<1ps, da una banda a meno 3dB pari a 250 MHz e da buone prestazioni dinamiche a frequenze molto maggiori di quelle da noi previste in questo lavoro. In figura 4.17 è rappresentato uno schema a blocchi del dispositivo.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

101 Figura 4.17: schema a blocchi dell’AD9100

Tale dispositivo è consigliato per applicazioni relative a convertitori con risoluzione da 8 a 16 bit. In figura 4.18 e 4.19 è rappresentato l’andamento del rapporto segnale rumore ,per due diverse frequenze di campionamento, in funzione della frequenza del segnale d’ingresso di un convertitore (l’AD9060) e dello stesso ADC con l’AD9100 anteposto. Sono evidenti i miglioramenti dovuti alla presenza del SHA.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

102 Figura 4.19: SNR vs frequenza di ingresso campionando a 20 MSPS

Nelle figure 4.20 e 4.21 mostriamo invece rispettivamente le buone prestazioni del SHA in termini di SFDR anche per la frequenza del segnale da noi trattato (a 7.66 MHz si può arrivare a -82 dB circa) e la banda del dispositivo.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

103 Figura 4.21: guadagno vs frequenza di ingresso

L’idea di anteporre questo circuito di Sample and Hold davanti all’AD9243 ci sembrava quindi allettante ed interessante. Purtroppo però l’AD9100 ,anche se diversamente dichiarato sul sito dell’Analog Devices, non è disponibile in commercio se non presso rivenditori di materiale obsoleto che però ci hanno richiesto una cifra spropositata.

4.3.2 Convertitore con basso aperture jitter

Dato che la specifica relativa alla bassa incertezza sull’istante di campionamento ci sembrava di fondamentale importanza, prima di abbandonarla ,accontentandoci quindi del valore di 4ps rms dell’AD9243, abbiamo deciso di ripetere le ricerche in rete. E , proprio sul sito dell’Analog Devices, abbiamo scoperto un convertitore appena uscito con ottime prestazioni da questo punto di vista. Si tratta dell’AD9245 che presenta un aperture jitter pari 0.3 ps rms [27]. In figura 4.22 è rappresentato lo schema a blocchi del dispositivo.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

104 Figura 4.22: schema a blocchi dell’AD9245

Il convertitore presenta una struttura molto simile a quella dell’AD9243: un’architettura pipeline con un amplificatore Sample and Hold in ingresso. Il circuito in pipeline è diviso in tre sezioni che consistono in un primo stadio a 4 bit, seguito da 8 blocchi a 2 bit ed infine un flash a 3 bit. Le uscite da ogni singolo ADC sono combinate nella parte di correzione logica digitale per ottenere il risultato finale a 14 bit. L’architettura pipeline permette al primo stadio di elaborare un nuovo campione, mentre i rimanenti blocchi operano sui precedenti dati.

Il campionamento avviene sul fronte in salita del segnale di clock.

Ogni stadio dello schema, eccetto l’ultimo, è costituito da ADC flash con bassa risoluzione, collegati con blocchi DAC a capacità commutate e amplificatori di residuo interstadio (MDAC). Questi ultimi hanno il compito, nella struttura pipeline, di magnificare la differenza tra l’uscita ricostruita dal DAC e l’ingresso del flash per lo stadio successivo. Viene utilizzato un bit di ridondanza in ogni blocco per facilitare la correzione digitale dell’errore nei convertitori flash. L’ultimo stadio è un semplice convertitore flash.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

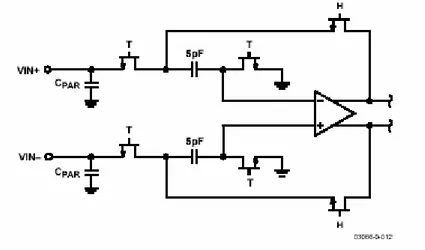

105 In ingresso al dispositivo, come abbiamo già detto, troviamo un SHA che può essere accoppiato in continua o alternata con ingresso singolo o differenziale. Lo schema è riportato nella figura seguente.

Figura 4.23: SHA in ingresso (switched capacitor)

Lo stadio di output invece allinea i dati tenendo conto anche della correzione dell’errore e passa i dati ai buffers di uscita. Questi ultimi sono alimentati separatamente dal resto del circuito e quando non alimentati si portano in uno stato di alta impedenza.

L’AD9245 è alimentato a 3V (2.7-3.6V) e i drivers d’uscita possono essere configurati in modo tale da interfacciarsi con famiglie logiche a +2.5V e a +3.3V. Questo ADC può lavorare con frequenze di campionamento comprese tra 1 MSPS e 80 MSPS; presenta una potenza consumata pari a solo 366 mW ed una banda a piena potenza di 500 MHz. Nei datasheet si dichiara SNR pari a 72.5 dBc e un SFDR di 87.6 dBc anche per la frequenza di nostro interesse (circa 7.66 MHz), possiamo notarlo nelle figure seguenti.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

106 Figura 4.24: SNR e SFDR vs ampiezza del segnale d’[email protected]

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

107 Figura 4.26: SNR e SFDR vs frequenza di campionamento@40MHz

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

108 Figura 4.28: SFDR vs frequenza del segnale d’ingresso

La differenza sostanziale rispetto all’AD9243 sta nel fatto che il SHA in ingresso è stato curato particolarmente in modo da avere ottime performance dal punto di vista dell’aperture jitter. Possiamo vedere nella figura seguente le previsioni riguardo a tale fenomeno.

Figura 4.29: SNR vs frequenza del segnale d’ingresso

Quindi, anche se i valori di SNR ed SFDR alla frequenza del nostro segnale (7.66 MHz) risultano più bassi rispetto a quelli dichiarati per il convertitore precedente, l’AD9245 ci è sembrato il dispositivo più adeguato perché si presume che l’errore

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

109 dovuto all’incertezza sull’istante di campionamento sia minimizzato e di conseguenza i risultati siano il più vicino possibili a quelli attesi. Inoltre, con questo convertitore possiamo operare con due diverse frequenze di campionamento (2.7648MSPS e 11.5692MSPS) come ci eravamo proposti all’inizio di questo capitolo e in futuro fare un confronto, in termini di SNR in uscita dall’ADC, tra la tecnica di Nyquist e quella di SuperNyquist.

Ultima nota da aggiungere, per un eventuale progetto futuro di un sistema non a singolo, ma a doppio canale (come necessario per una applicazione in NMR), è quella relativa ad un altro parametro del convertitore: l’aperture delay. Come già accennato nel capitolo precedente, questo è il ritardo tra il fronte in salita del segnale di clock e l’effettivo istante di campionamento. Avere un valore basso significa avere la possibilità di multiplexare l’ingresso all’ADC a frequenze piuttosto elevate e quindi poter passare alternativamente al DDC a valle del convertitore, due segnali da lui elaborabili in modalità dual channel. La specifica infatti da soddisfare in questo caso, è che l’ADC campioni sempre quando il dato fornitogli dal multiplexer è stabile. Con un aperture delay pari ad 1 ns, come quello dell’AD9245, potremmo alternare il segnale d’ingresso al convertitore con frequenze dell’ordine del MHz.

4.4 Scelta del Digital Down Converter

Il Digital Down-Converter (DDC) che abbiamo scelto per effettuare le operazioni descritte in precedenza, vale a dire traslazione in frequenza, decimazione e filtro digitale dei campioni in uscita dall’ ADC, è il dispositivo dell’ Analog Device indicato con il nome di AD6620 [13] .

Uno schema a blocchi dell’AD6620 è riportato in fig 4.30.

L’AD6620 è un digital down-converter caratterizzato da quattro stadi in cascata: • un traslatore di frequenza

• due filtri decimatori a coefficienti fissi

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

110 L’AD6620 può accettare in ingresso dati con velocità fino a 67 MSPS.

Sono previste tre modalità d’ingresso dei dati:

Single Channel Real, Diversity Channel Real o Single Channel Complex; la prima è utilizzata nel caso in cui si abbia un solo ADC che piloti il DDC, la seconda con due canali d’ingresso; infine, la modalità Single Channel Complex accetta dati complessi in ingresso (generalmente si utilizza con più AD6620 in cascata). Analizziamo in dettaglio, ora, i diversi stadi del dispositivo.

Il primo stadio è, dunque, un traslatore di frequenza, che consiste di due moltiplicatori e di un oscillatore complesso a 32 bit controllato numericamente (NCO).

L’ NCO è utilizzato come un oscillatore locale in quadratura ed è in grado di produrre ogni frequenza tra –fS/2 e +fS/2 con una risoluzione pari a fS/232. Inoltre,

tale NCO presenta delle componenti spurie nel caso peggiore sotto i 100 dBc per tutte le frequenze di uscita.

Figura 4.30 - Schema a blocchi dell’AD6620

CIC Filter Decimator FIR Filter Complex NCO Rate Control Coefficient RAM Control Interfaccia di programmazione Dati ADC Dati complessi Output Format

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

111 La parola di controllo di tale oscillatore, NCO_FREQ è interpretata come un intero (unsigned) a 32 bit; quindi, per traslare un segnale dalla frequenza fC alla

continua, NCO_FREQ va calcolato secondo l’equazione

. mod 2 _ 32 S C f f FREQ NCO = ×

La funzione mod che compare nell’espressione, e che avevamo già introdotto in precedenza, è utilizzata proprio per consentire un campionamento di tipo Super-Nyquist.

Il secondo stadio è costituito da un filtro decimatore a coefficienti fissi. Tale filtro è rappresentato da un filtro CIC (Cascade Integrator Comb) del

secondo ordine. Chiariamo, innanzitutto, cosa si intende per filtro CIC esaminandone la struttura riportata, proprio per un filtro del secondo ordine, in fig 4.31.

Figura 4.31: Diagramma a blocchi di un filtro CIC del secondo ordine

Il filtro è costituito da due integratori in cascata seguiti da una decimazione per r e da due derivatori.

La funzione di trasferimento di un generico filtro CIC di ordine n caratterizzato da una decimazione per r è dunque

. z 1 z 1 ) z ( H n 1 r − − = −−

Il grosso vantaggio di questo tipo di filtri è la semplicità, in quanto sono necessari soltanto dei sommatori e dei registri.

Analizziamo ora, in particolare, il filtro dell’AD6620.

Tale filtro, come già detto, è un CIC del secondo ordine (CIC2); può processare segnali fino a 67 MHz e la velocità dei dati in uscita è pari a

z -1 z-1 z-r z-r Input Output fS fS/r (4.12) (4.11)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

112 2 2 CIC S S M f f =

dove MCIC2 è un intero compreso tra 1 e 16.

In particolare la risposta in frequenza del CIC2 è data dalla seguente equazione: 2 1 2 1 1 2 1 ) ( 2 2 − − × = + − − z z z H CIC CIC M S

dove SCIC2 è un fattore di scala programmabile con valore compreso tra 0 e 6.

La tabella 4.2 riassume i valori di attenuazione in banda passante del CIC2, in funzione di MCIC2, per diversi valori della stessa banda in percentuale rispetto alla

velocità dei dati in ingresso.

Tabella 4.2 - Reiezione di CIC2 per diversi valori di banda in percentuale rispetto a fS

(4.13)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

113 La tabella può essere usata come strumento per decidere come distribuire la decimazione tra i diversi stadi [13].

Il terzo stadio prevede l’altro filtro CIC del quinto ordine.

La velocità dei dati in ingresso a questo filtro è, evidentemente, fS2, mentre la sua

risposta in frequenza è data dall’equazione seguente

, z 1 z 1 2 1 ) z ( H 5 1 M 5 S 5 CIC 5 CIC − − × = + − −

dove il fattore di decimazione MCIC5 può essere programmato tra 1 e 32, mentre il

fattore di scala SCIC2 è un intero compreso tra 0 e 20.

Analogamente a quanto visto per il filtro CIC2, la tabella 4.3 indica i valori di attenuazione in banda passante del CIC5, in funzione di MCIC5, per diversi valori

della stessa banda in percentuale rispetto alla velocità dei dati in ingresso.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

114

Tabella 4.3 – Reiezione di CIC5 per diversi valori di banda in percentuale rispetto a fS

Infine, la velocità dei dati in uscita è data da

. M f f 5 CIC 2 S 5 S ≤

Il compito di questi primi due filtri è quello di ridurre la velocità dei dati in ingresso in modo tale che l’ultimo stadio, un filtro FIR del tipo somma di prodotti

con coefficienti programmabili (RCF), possa calcolare più “prese” per uscita.

Uno schema semplificato del filtro è riportato in fig 4.32.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

115 Figura 4.32 - Schema a blocchi del filtro FIR a coefficienti RAM

Le memorie dei dati, I-RAM e Q-RAM, immagazzinano i 256 campioni complessi più recenti. La memoria dei coefficienti, C-RAM, immagazzina fino a 256 coefficienti. Il massimo numero di prese relativamente a questo filtro FIR è pari a 256. Il fattore di decimazione MRCF di questo filtro può essere programmato

tra 1 e 32 e la velocità dei dati in uscita è dunque pari a

. M f f RCF 5 S SR =

La risposta complessiva dell’AD6620 è data dalla composizione delle risposte dei tre filtri decimatori in cascata CIC2, CIC5 e RCF; ogni stadio consente di ottenere bande di transizione sempre più strette, con l’RCF, in particolare, che permette di conferire una maggiore “piattezza” alla risposta totale (vedi fig 4.33).

Figura 4.33 - Il segnale, dopo la traslazione in banda base tramite NCO, è decimato e filtrato tramite i filtri CIC2, CIC5 e RCF

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

116 Facciamo ora alcune considerazioni sulla sincronizzazione dei segnali in ingresso all’AD6620; il segnale di clock è, evidentemente, utilizzato per campionare la porta d’ingresso del dispositivo e per sincronizzare gli stadi di processing successivi. Tipicamente, in applicazioni con ADC ad alta velocità di campionamento, il clock dello stesso ADC è impiegato come clock dell’AD6620. Il dispositivo, però, prevede anche la possibilità di impiegare un clock di processing più veloce e diverso da quello del relativo ADC; ciò consente di ottenere delle performance migliori relativamente ai filtri digitali. [13] :

Nella nostra applicazione utilizzeremo lo stesso clock ( 2.7648 MHz nel primo caso e 11.0592 MHz nel secondo) sia per l’ADC (AD9245) che per l’AD6620. Una volta descritto il funzionamento dell’AD6620, affrontiamo il problema relativo all’implementazione del filtro digitale in funzione delle specifiche da noi desiderate, e, quindi, all’impostazione delle caratteristiche dei filtri nei diversi stadi. Questa procedura può essere effettuata utilizzando un software di simulazione dell’AD6620, messo a disposizione dall’Analog Device, e che andiamo ad esaminare nel prossimo sottoparagrafo.

4.4.1 Software di simulazione dell’AD6620

Il software di simulazione dell’AD6620 [14] consente, mediante una procedura guidata, di impostare tutte le specifiche dei filtri digitali da noi richieste in termini di pass-band, stop-band e di relative attenuazioni. Inoltre, ci permette di impostare la decimazione dei dati in uscita rispetto alla velocità dei dati in ingresso, vale a dire la fSout nella (4.7).

Il software permette, poi, di prendere in considerazione anche le caratteristiche del filtro passa-banda anti-aliasing, il quale, evidentemente, agevola il perseguimento delle specifiche richieste. Le specifiche del nostro primo prototipo di filtro anti-aliasing sono, considerando come limite di stop-band la banda di Nyquist relativa al campionamento a 2.7648 MHz.

• pass-band = 300 KHz • pass-band rejection = 0 dB • stop-band = 1.25 MHz

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

117 • stop-band rejection = 36 dB ;

questo filtro ci consente di ridurre l’aliasing dovuto alle repliche di segnali presenti nelle altre zone di Nyquist .

Stabiliamo che la risposta in frequenza del filtro digitale complessivo debba avere, possibilmente, le seguenti caratteristiche:

• pass-band = 21.6 KHz • pass-band rejection = 0 dB • stop-band = 35 KHz

• stop-band rejection = 75 dB .

Dobbiamo a questo punto distinguere le due diverse condizioni di lavoro campionando rispettivamente a 2.7648MSPS e 11.0592MSPS.

fs=2.7648MSPS Supponiamo di voler ottenere, come preso in esempio in

precedenza, una fSout = 21.6 KHz circa. Ciò significa che il fattore di decimazione

complessivo deve essere pari a 64

KHz 6 . 21 * 2 MHz 7648 . 2 cioè .

Una volta impostati questi valori, il software riassume le specifiche in una finestra, come rappresentato in fig 4.34.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

118 Figura 4.34 - Finestra di riassunto delle specifiche del filtro digitale da implementare

sull’AD6620

Evidenziamo, inoltre, come è possibile indicare anche la velocità di campionamento dei dati (2.7648 MHz), la velocità di processing dell’AD6620 in rapporto alla stessa velocità di campionamento dei dati al suo ingresso (nel nostro caso RCF Clock Multiplier = 1), e, infine, in base a questi valori, il numero di prese del filtro FIR relativo allo stadio finale (nel nostro caso si ha un filtro a 64 prese).

A questo punto, il software calcola le possibili configurazioni dei tre filtri CIC2, CIC5 e RCF, in termini di fattori di decimazione MCIC2, MCIC5 e MRCF, per

ottenere le specifiche richieste, come rappresentato in fig 4.35. 300000 0

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

119 Figura 4.35 - Possibili configurazioni di MCIC2, MCIC5 e MRCF per un fattore di decimazione

complessivo di 64

Infine, scelta una tra le possibili configurazioni, il software rappresenta la risposta in frequenza complessiva dei tre filtri (vedi fig 4.36 – finestra in alto), nonché la risposta impulsiva del filtro FIR RCF (vedi fig 4.36 – finestra in basso).

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

120 Figura 4.36 - Risposta in frequenza complessiva dei filtri implementati sull’AD6620 (CLKAD6620 = CLKAD9243) con fattori di decimazione rispettivamente di 2,8,4 e risposta impulsiva

di RCF con 64 prese secondo il software di simulazione dell’Analog Device.

Nella tabella 4.4, infine, sono riportati i valori di stop-band rejection per alcune frequenze significative, determinati sempre tramite il software di simulazione; il risultato evidente è che, diminuendo fSout, aumenta il corrispondente fattore di

decimazione, di conseguenza aumenta il numero di prese del filtro RCF, e, dunque, le relative performance migliorano.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

121

Tabella 4.4 - Performance dell’AD6620 in termini di stop-band rejection per alcune frequenze di

uscita (i valori sottolineati corrispondono all’esempio illustrato in precedenza)

Stop-Band Rejection (dB)

f

Sout(KHz)

N

DEC Pass-band (KHz) Stop-band (KHz) CLKCLKDDCADC = CLKDDC = 2*CLKADC ∼31 45 31 45 -60 -80 21.6 64 22 35 -75 -100 ∼10 135 11 15 -90 -105 ∼5 273 5.2 7.5 -105 -105fs=11.0592MSPS Anche in questo caso fissiamo una fSout = 21.6 KHz circa . Ciò

significa che il fattore di decimazione complessivo deve essere pari a 256

KHz MHz cioè 6 . 21 * 2 0592 . 11 .

Riportiamo anche per questo caso la finestra di riassunto delle specifiche del filtro digitale e la risposta in frequenza complessiva e quella del filtro RCF.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

122 Figura 4.37 - Finestra di riassunto delle specifiche del filtro digitale da implementare

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

123 Figura 4.38 - Risposta in frequenza complessiva dei filtri implementati sull’AD6620 (CLKAD6620 = CLKAD9245) con fattori di decimazione rispettivamente di 2,8,16 e risposta impulsiva

di RCF con 256 prese secondo il software di simulazione dell’Analog Device.

In conclusione, la simulazione dell’AD6620 mette in risalto le notevoli qualità di questo demodulatore digitale, in quanto ci consentirebbe di ottenere, se confermato dalle prove sperimentali, oltre ad una rivelazione fase-quadratura del segnale molto “pulita” mediante l’NCO, anche delle notevoli prestazioni in termini di filtro digitale.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

124

4.5 Circuito per il clock

Come abbiamo indicato in precedenza, vogliamo testare le prestazioni del nostro sistema sia nel caso che la velocità di campionamento dell’AD9245 sia pari a 2.7648 MHz che a 11.0592MHz. Nel capitolo precedente, quando abbiamo parlato dell’applicazione del sottocampionamento, abbiamo visto come uno dei principali problemi di cui bisogna tener conto è il jitter (o rumore di fase), il cui effetto sul rapporto segnale rumore è prevedibile secondo la seguente formula.

(

)

[

2 f t]

.log 20

SNR =− π analog jitter−rms

Le possibili sorgenti di jitter sono [15] :

• il convertitore analogico-digitale e il suo SHA • il clock di campionamento

• il routing del segnale dal generatore di clock al convertitore .

Per quanto riguarda il primo punto abbiamo scelto il convertitore ponendo tale specifica al primo posto, per cui ci sentiamo abbastanza rassicurati dalle prestazioni dichiarate nei datasheet dell’AD9245.

Analizziamo ora il secondo punto, cioè il problema della scelta di un oscillatore a basso rumore. Abbiamo pensato di utilizzare un oscillatore ibrido commerciale, con una configurazione, quella a porte logiche, che abbiamo indicato come poco adatta per applicazioni a basso jitter, ma supportata da un PLL (Phase-Locked Loop), il quale consente di rimuovere, o, quanto meno, di ridurre il rumore di fase mediante una ricostruzione del segnale.

Prima di descrivere in dettaglio la realizzazione del circuito per il clock, concludiamo il discorso sulle possibili sorgenti di rumore di fase.

L’ultima possibile causa di jitter riguarda il modo in cui il segnale di clock è portato al sistema digitale. Due sono le possibili fonti di rumore:

• l’accoppiamento con gli altri segnali digitali

• il rumore di modo comune tra massa analogica e digitale .

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

125 Nel primo caso, linee di diversi segnali digitali possono accoppiarsi capacitivamente o induttivamente nel caso in cui siano parallele; questo non è un problema serio per la maggior parte dei sistemi digitali, ma lo diventa nel caso di segnali analogici, e quindi per il segnale di clock. La soluzione migliore è di far correre le piste relative al segnale di clock lontane dagli altri segnali digitali; nella nostra applicazione, il circuito per il clock è stato comunque implementato su una basetta separata dal resto del sistema.

Infine, è rimasto da analizzare il jitter dovuto al rumore di modo comune tra la massa analogica e la massa digitale del sistema. In fig 4.39 è rappresentato come questo crei dei problemi [15].

Figura 4.39 - Effetto del ground noise

Questa tensione di modo comune si sovrappone al segnale di clock in ingresso all’ADC, modulandolo e, quindi, provocando un jitter interno al convertitore stesso. Il modo migliore per eliminare tale sorgente di jitter è quello di utilizzare come riferimento per il clock la massa analogica del sistema (vedi fig 4.40).

Senza ground noise Livelli di soglia per il clock dell’ADC Con ground noise Clock Ground noise Clock+Ground noise

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

126 Figura 4.40 - Il ground noise si può eliminare collegando il clock al riferimento di massa

analogica del sistema

4.5.1 Implementazione del circuito per il clock tramite PLL

Descriviamo, quindi, in dettaglio, la configurazione circuitale del circuito per il clock del convertitore analogico digitale e del DDC.

Il semplice schema a blocchi del circuito è riportato in fig 4.41.

Figura 4.41 - Schema a blocchi del circuito per il clock dell’AD9245 e dell’AD6620

Per ottenere il clock alla nostre frequenza di interesse (2.7648 MHz e 11.0592 MHz), abbiamo utilizzato un oscillatore ibrido commerciale, l’ SCO-020, della

Sunny Electronics [16], il quale fornisce una frequenza di oscillazione pari a 11.0592 MHz. I valori da noi richiesti, sono stati quindi ricavati tramite il PLL, l’

MC88915, della Motorola [17], che fornisce più uscite con rapporti di frequenza

rispetto all’ingresso di 1:2, 1:1, 2:1, tutte “agganciate” in fase.

In particolare, la configurazione scelta per la nostra applicazione è riportata in fig 4.42. In questa applicazione, l’uscita 2x_Q è connessa all’ingresso FEEDBACK, cosicché il PLL interno allineerà i fronti positivi di 2x_Q e del segnale dall’oscillatore; in questo modo, 2x_Q sarà pari proprio alla frequenza

CLOCK ADC Oscillatore ibrido

PLL

clock ripulito dal rumore di fase clock con jitterImplementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

127 dell’oscillatore (11.0592 MHz), mentre Q/2 = 1/4 * 2x_Q = 2.7648 MHz e le rimanenti uscite Q avranno valore 1/2 * 2x_Q = 5.5296 MHz.

Chiaramente, a seconda della frequenza di campionamento con cui vogliamo operare, andremo a prelevare il segnale di clock da passare all’AD9245 da un piedino piuttosto che da un altro. E con questo intendo dire che abbiamo proprio saldato e dissaldato fisicamente il collegamento al clock del convertitore a seconda delle misure che volevamo fare.

Analizziamo, ora, la funzione del filtro esterno (vedi fig 4.43).

I resistori da 47 Ω, i capacitori di bypass a bassa frequenza da 10 µF e i capacitori di bypass ad alta frequenza da 0.1 µF costituiscono un filtro a larga banda che minimizza la sensibilità del dispositivo alle oscillazioni dell’alimentazione tipiche di un sistema digitale ad alta frequenza.

Il resistore da 1 MΩ inietta corrente nel PLL interno, provocando un offset fisso tra le uscite e il segnale d’ingresso.

In aggiunta ai capacitori di bypass utilizzati nel filtro analogico appena descritto, abbiamo utilizzato un capacitore di bypass da 0.1 µF tra ognuno degli altri quattro pin (digitali) di alimentazione dell’ MC88915 e la massa della scheda; ciò dovrebbe contribuire a ridurre il rumore di switching causato dalle uscite dello stesso dispositivo. Infine, tutti i componenti relativi al filtro e i capacitori di bypass sono stati montati quanto più possibile vicini all’MC88915, in modo tale da evitare i possibili effetti parassiti dovuti a tracce troppo lunghe.

Figura 4.42 - Configurazione del circuito per il clock

11.0592 MHz 2.7648 MHz

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

128 Figura 4.43- Loop filter esterno all’ MC88915

4.6 Implementazione del ricevitore digitale

I componenti principali del nostro ricevitore digitale (AD9245 e AD6620) sono disponibili come moduli di valutazione (evaluation board); l’enorme esperienza maturata negli anni da parte dell’Analog Devices con la realizzazione di dispositivi sempre più sofisticati, ha portato allo sviluppo di moduli di valutazione altamente funzionali, utili per l’implementazione di sistemi sperimentali come il nostro.

Quindi, la nostra catena prevede l’utilizzo dell’evaluation board dell’AD9245 ( che ci è stata gentilmente regalata dall’Analog Devices in forma prototipale, in quanto all’inizio del lavoro non era ancora disponibile sul mercato), dell’evaluation board dell’AD6620, oltre che, naturalmente, del circuito per il clock descritto in precedenza e del filtro passabanda descritto nel paragrafo 4.2.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

129 In fig 4.44 è riportata una foto del sistema.

Figura 4.44 - Foto del sistema implementato

Riportiamo lo schema completo dell’evaluation board dell’ADC, giusto per dare un’idea della complessità della scheda.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

130 a))Sezione di ingresso e AD9245

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

131 b) Latch e connettore d’uscita

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

132 c) timing circuit

Notiamo in figura a) che l’ingresso, prima di essere passato all’ADC, viene reso differenziale tramite un trasformatore, perché in questo modo le prestazioni del convertitore migliorano. Nello schema c) è incluso il circuito di elaborazione del segnale di clock. In esso abbiamo inserito un jumper (tra E52 e E53) che ci ha permesso di invertire il CLK come richiesto per il corretto funzionamento del sistema. Nella figura sottostante invece possiamo osservare una foto della scheda AD9245

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

133 .

Figura 4.46 – AD9245

Soffermiamoci adesso, sulla descrizione dell’evaluation board relativa all’AD6620 [18]. Le due evaluation board non prevedono un collegamento diretto tra uscite ed ingressi, quindi è stato necessario effettuare un opportuno adattamento. In particolare l’uscita dell’AD6620 è a 16 bit, mentre l’AD9245 lavora su 14 bit: è stato quindi necessario un allineamento verso l’alto, nel senso che i bit di output meno significativi del DDC sono stati collegati a massa. Nella figura seguente possiamo vedere il connettore in ingresso al DDC tramite il quale giungono i dati dall’ADC [18].

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

134 figura 4.47- connettore di ingresso dell’AD6620

Il segnale di clock , prelevato dal circuito realizzato su una basetta separata dal resto del sistema, è stato portato in ingresso alla scheda dell’AD9245, mentre come clock per l’AD6620 ( corrispondente al piedino 10, ICLK in figura 4.47) è stato utilizzato il segnale disponibile all’uscita del convertitore analogico-digitale (sottolineiamo ancora che l’ADC ha una logica digitale a 3.3V e può quindi interfacciarsi senza problemi con altri dispositivi con logica a 3.3V, qual è appunto l’AD6620).

Altro segnale in ingresso al DDC che merita di essere ricordato è quello che esso riceve tramite il piedino 27 (I A\B) .Tale input indica all’AD6620 se si sta

lavorando in modalità dual o single channel. Nella nostra applicazione lo abbiamo collegato all’alimentazione ,come suggerito nei datasheet, così da poter operare con un solo canale. Ciò è evidenziato dalla temporizzazione consigliata che riportiamo di seguito.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

135 figura 4.48: temporizzazione in modalità single channel

Per semplicità non riportiamo l’intero circuito, ma solo uno schema a blocchi della scheda del DDC che è rappresentato in fig 4.49.

Figura 4.49 - Schema a blocchi dell’evaluation board dell’AD6620

Come mostrato nello schema, i dati provenienti dall’AD9245 passano attraverso dei latch d’ingresso (74LCX574) e, quindi, sono portati direttamente in ingresso all’AD6620. A questo punto, il DDC permette di effettuare il processing dei dati come descritto in precedenza, dopodiché vi sono due possibilità: infatti, i dati sono disponibili real –time (connessione Header) in modo tale che possano essere

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

136 elaborati tramite DSP o microprocessore (i dati possono uscire in modalità seriale o parallela), oppure gli stessi dati possono essere posti nella memoria FIFO (First-in, First-out, IDT 72265, può memorizzare fino a 16K) presente sulla scheda, per poi essere scaricati sul PC, attraverso la porta parallela della stampante, per una successiva elaborazione.

Una seconda modalità della scheda è la modalità di Bypass; in questa configurazione, l’AD6620 è escluso; i dati, infatti, dopo essere passati attraverso una seconda serie di latch, sono condotti direttamente nella FIFO e, quindi, possono essere scaricati e analizzati sul PC.

Questa modalità consente, dunque, di effettuare una verifica del funzionamento dell’ADC; naturalmente, la modalità AD6620 e quella di Bypass non possono essere impostate simultaneamente. In entrambi i casi, comunque, i dati elaborati dall’AD6620 sono disponibili sulla connessione header.

Inoltre, sulla scheda di valutazione sono presenti alcuni jumper che consentono di introdurre opportuni ritardi tra i dati provenienti dall’evaluation board dell’AD9245 e i latch d’ingresso della scheda stessa, questo per assicurare la giusta temporizzazione del dispositivo.

Riportiamo di seguito una foto del dispositivo.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

137 Attraverso la porta della stampante è possibile effettuare, oltre al download dei dati, anche il controllo dell’AD6620, questo grazie al software messo a disposizione dall’Analog Devices a supporto della scheda.

L’interfaccia grafica del sofware si presenta come in fig 4.51 e 4.52; sono presenti due finestre, l’AD6620 Monitor (fig 4.51) e l’AD6620 Controller (fig 4.52), le quali consentono di impostare i parametri per il controllo dell’AD6620, nonché di scaricare i dati dalla FIFO sul PC e di analizzarli.

Descriviamo alcune funzioni che si possono impostare tramite i due programmi, rimandando al manuale di riferimento [18] per una più approfondita descrizione dei comandi.

L’AD6620 Controller ci consente di impostare tutti i parametri di funzionamento dell’AD6620, vale a dire la modalità d’ingresso dei dati (nel nostro caso Single Channel Real), la velocità di campionamento degli stessi dati, il valore dello shift di frequenza dell’ NCO (viene impostato automaticamente), e, inoltre, ci permette di configurare i filtri digitali (CIC2, CIC5 e RCF) caricando direttamente i risultati del software di simulazione (fattori di decimazione e risposta impulsiva). In figura riportiamo la pagina di controllo nel caso si campioni a 2.7648 MSPS.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

138 Figura 4.51 - Programma di controllo dell’AD6620

L’AD6620 Monitor, invece, ci consente di controllare e di elaborare i dati prelevati dalla FIFO della scheda (quindi, dall’AD9245 o dall’AD6620).

In particolare, ci permette di analizzare la FFT dei dati, il loro andamento nel dominio del tempo, il grafico di I vs Q (i due canali fase-quadratura dell’AD6620), nonché di rilevare in maniera immediata il valore del SINAD, dell’SNR, del livello della seconda e della terza armonica del segnale più ampio presente nello spettro (in dBc) e del livello del segnale spurio più ampio dopo questi tre misurato rispetto al fondo scala (dBFS).

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

139 Figura 4.52 - Programma di monitoraggio dell’AD6620

4.7 Prove sperimentali

I test sul sistema sono stati effettuati utilizzando come segnale d’ingresso una forma d’onda sinusoidale generata tramite il generatore di funzione HP3325A .La catena per i test include, inoltre, il filtro anti-aliasing, le cui caratteristiche sono state riportate in precedenza, e, infine, naturalmente, il demodulatore digitale costituito dalle evaluation board dei due dispositivi (AD9245 e AD6620). Uno schema a blocchi è riportato in fig 4.53.

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

140 Fig 4.53- Schema a blocchi della configurazione per i test

Prima di riportare i risultati delle verifiche effettuate, è opportuno fare una premessa.

Nel valutare le prestazioni effettive del sistema, occorrerebbe porsi nelle condizioni ideali di misura, il che presupporrebbe che il segnale d’ingresso fosse una sinusoide perfetta, vale a dire un tono perfettamente puro; ciò, chiaramente, non è possibile, in quanto la qualità del segnale è notevolmente diminuita da diversi fattori:

• il rumore derivante dalla strumentazione utilizzata, incluso quello derivante da un improprio interfacciamento tra i dispositivi, nonché limitazioni derivanti dal rumore termico della sorgente di segnale o da componenti spurie dovute allo stesso generatore di funzione

• le armoniche dello stesso segnale, dovute alla distorsione non lineare del generatore di funzione

• l’inevitabile contributo del jitter del clock, nonostante l’utilizzo del PLL per una sua attenuazione .

Il primo test che abbiamo fatto, dunque, riguarda proprio il segnale generato dall’HP3325A, e precisamente abbiamo osservato lo spettro del segnale tramite

Generatore di funzione HP3325A Filtro anti-aliasing AD9245 Evaluation Board AD6620 Evaluation Board PC (FFT del segnale)

Implementazione del ricevitore digitale

UNIVERSITA’DEGLISTUDIDIPISA

Corso di Laurea in Ingegneria Elettronica

141 l’analizzatore di spettro (HP8557A).

L’analisi è stata fatta sul segnale in uscita direttamente dal generatore, e sullo stesso segnale, ma dopo essere stato filtrato dal filtro anti-aliasing.

Lo spettro del segnale nei due casi è stato rappresentato in fig 4.54.

(a)

(b)

Figura 4.54- (a) Spettro del segnale in uscita dal generatore di funzione (b) Spettro dello stesso segnale in uscita dal filtro

L’analisi effettuata ha messo in evidenza che il segnale fornito dal generatore presenta comunque delle armoniche intorno alla fondamentale di ampiezza consistente; inoltre, è presente una componente spuria ad una frequenza di circa 5 MHz.

Tali componenti sono attenuate relativamente poco dal filtro anti-aliasing (vedi fig 4.54)), quindi la prova del sistema ne è stata sicuramente condizionata.

7.66 MHz 15.32 MHz 22.98 MHz 30.64 MHz 38.3 MHz 45.96 MHz 7.66 MHz 15.32 MHz 22.98 MHz 30.64 MHz 38.3 MHz 45.96 MHz Livello della fondamentale -50 dBc -65 dBc -70 dBc Componente spuria (5.1 MHz) Componente spuria (5.1 MHz) 2a 3a 4a 5a 6a 2a 3a 4a 5a 6a Livello della fondamentale -30 dBc -35 dBc -40 dBc -45 dBc -50 dBc