CAPITOLO 3

Progetto di un deskewer con controllo

digitale

3.1 Introduzione

Il rapido e incalzante sviluppo dell’elettronica digitale, sostenuto dall’evoluzione tecnologica della microelettronica, dalla sempre maggiore diffusione di tecniche di progettazione automatica (CAD, CAE) e dalla rapida evoluzione dei processi tecnologici ha portato negli ultimi anni alla realizzazione di sistemi sempre più complessi e veloci. Un esempio sono le CPU che hanno frequenze di clock che stanno migrando verso valori sempre più elevati. Dunque la generazione e il controllo del segnale di sincronismo sta diventando uno dei problemi più critici nella progettazione di un sistema digitale. Al diminuire del periodo di clock, l’incertezza o skew nel sistema di distribuzione del segnale di sincronizzazione diventa sempre più un problema non trascurabile. Progettare un sistema di distribuzione del clock che minimizzi lo skew diventa quindi un’esigenza. Il termine clock skew è usato per descrivere una differenza di temporizzazione tra i segnali in una rete di distribuzione del clock.

Il clock skew è un parametro importante nel progetto di sistemi ad alta velocità. Per operazioni di successo e affidabili, il clock skew deve essere ridotto ad una frazione accettabile del periodo del clock di sistema. Il lavoro svolto in questa tesi ha avuto come obiettivo il progetto e la realizzazione di un prototipo di

circuito deskewer VLSI in tecnologia CMOS nel quale per la correzione dello skew vengono applicati due algoritmi (Bisezione e Differenziale al Nonio) per mezzo di un dispositivo controllore realizzato all’interno dello stesso chip in grado di regolare il ritardo introdotto da ogni singola cella, in modo indipendente dalle altre celle. Questa regolazione avviene tramite comandi costituiti da parole digitali. Ciò ci ha permesso l’uso di celle standard e quindi di strumenti di progettazione semicustom, per la realizzazione del controllore di fase. In questo capitolo descriveremo il progetto degli elementi essenziali che compongono il deskewer, cioè le linee di ritardo, il phase detector il controllore di fase e tutta la circuiteria di contorno necessaria alla realizzazione dell’architettura (vedi Figura 3.1) proposta in questo lavoro di tesi. Per la realizzazione di alcuni di essi ci siamo basati sui risultati ottenuti in precedenti progetti svolti all’interno del Dipartimento dell’Ingegneria dell’informazione dell’Universita di Pisa [1].

I progetti delle linee e del phase detector necessari per realizzare il circuito deskewer sono stati realizzati in modo interamente fullcustom utilizzando il processo tecnologico CSD a 0.35µm della AMS, che consente l’utilizzo di tre livelli di metal e due livelli di poly. Il software usato per il disegno fullcustom è stato il layout editor VIRTUOSO di CADENCE.

Per quanto riguarda, invece il controllore di fase, esso è stato realizzato in modo semicustom usando il linguaggio di descrizione dello hardware VHDL e il sintetizzatore DESIGN-ANALYZER di SYNOPSYS.

Cmd Cmd 1 1 0 0 Clk Sys B A

……

Cmd Path_2 Path_1 PD CONTROLLORE DELAY LINE 2 DELAYLINE1……

Clk A Clk BLinea di ritardo e suo utilizzo

La linea di ritardo costituisce l’elemento fondamentale nella realizzazione di un circuito per l’equalizzazione del segnale di sincronismo in quanto consente di creare con precisione e stabilità quei riferimenti temporali, anche molto piccoli necessari per ottenere una correzione ad alta risoluzione.

Una linea di ritardo è un sistema in grado di compiere un’operazione elementare sul segnale d’ingresso del tipo:

u(t) = i(t-∆t)

Le linee di ritardo quando vengono utilizzate all’interno di un sistema digitale aumentano notevolmente la loro potenzialità se sono realizzate in modo da essere interfacciate direttamente con esso, in quanto permettono la regolazione del ritardo introdotto attraverso una parola digitale di ingresso. Le tecniche di realizzazione sono molteplici ma si basano tutte sulla relazione approssimata che esprime il ritardo introdotto da una porta logica:

0 I V C K T l s d ⋅ =

dove: K è una costante, Cl è la capacità di carico, Vs è l’escursione dell’uscita e I0

è la corrente in uscita dalla porta. È possibile notare come per la regolazione del tempo di propagazione si può agire sia su I0 che su Cl. La linea di ritardo a

controllo digitale utilizzata nell’ambito di questo lavoro di tesi permette il controllo del ritardo introdotto da ogni singola cella in modo indipendente dalle altre. Le due linee di ritardo presenti nel deskewer sono costituite da 3 celle tutte diverse tra loro alle quali sono stati aggiunti agli estremi due buffer necessari per equalizzare sia il carico pilotato che il segnale ricevuto in ingresso. Le celle di ritardo che costituiscono la linea possono essere a controllo digitale o a controllo

analogico (ad esempio la cella Current-Starved Inverter). I vantaggi di una linea con un controllo totalmente digitale rispetto ad una analogica sono l’eliminazione della Charge-Pump (CP) usata come convertitore fase-tensione la quale risulta essere di difficile progettazione e l’introduzione di notevoli benefici in termine di rumore e disturbi sulla tensione di alimentazione riducendo molto la loro influenza sul ritardo introdotto poiché la grandezza di controllo è una parola ad N bit e non una tensione analogica. In letteratura esistono diverse tecniche per la realizzazione delle celle di ritardo a controllo digitale, quella adottata nel progetto di questo sistema è quella denominata Shunt-Capacitor (SC), il cui schema di principio è mostrato in Figura 3.2. In essa al posto di un normale condensatore viene usato un transistore NMOS con i terminali di source e drain cortocircuitati.

In Out

Bi Bi

Figura 3.2 Cella di ritardo a Shunt-Capacitor

Questa cella nasce dall’idea che per realizzare la regolazione del ritardo introdotto basta agire sul tempo di propagazione di un segnale che attraversa una porta logica, tempo di propagazione che può essere modificato variando il carico capacitivo presente sull’uscita. In questo modo possiamo connettere sull’uscita dell’inverter un certo numero di condensatori, ognuno controllato da un bit della parola di controllo. Se la tensione sul gate è bassa, le capacità che caricano l’inverter della cella sono quelle di giunzione e di overlap, mentre quando il gate è a livello logico alto viene inserita anche la capacità di canale che è predominante rispetto alle altre, di conseguenza il carico capacitivo aumenta notevolmente. Questa struttura permette di ottenere layout più compatti a parità di carico capacitivo in quanto viene sfruttata la capacità di gate (Cox) che è la più elevata

inverter della cella elimina l’effetto di un fenomeno indesiderato definito pulse-shrinking che, se il segnale di ingresso è un’onda quadra, si traduce in un aumento del duty-cicle δ (definito come il rapporto tra il semiperiodo positivo e il periodo totale) tra l’ingresso e l’uscita della cella. Ciò accade durante le commutazioni del segnale in quanto i fronti risultano caricati in modo non uniforme e l’intervallo fra l’istante di inizio della commutazione e il 50% della tensione di alimentazione (che costituisce la soglia logica teorica dell’inverter posto a valle) cambia nelle due situazioni di salita e discesa del segnale. Questa dissimmetria è tanto più pronunciata quanto maggiore è il numero di condensatori collegati alla cella di ritardo. Quindi la presenza delle capacità di carico su entrambe le uscite degli inverter elimina questo fastidioso fenomeno. In questo modo in corrispondenza di qualsiasi commutazione del segnale di ingresso il ritardo complessivo sarà dato dalla somma dei due ritardi introdotti dai due inverter i quali subiscono commutazioni opposte. Le linee realizzate con le celle sopra menzionate nel progetto del deskewer sono utilizzate per introdurre dei ritardi in modo controllato attraverso l’inserimento di capacità opportunamente dimensionate. Del dimensionamento di queste capacità (shunt-capacitor) parleremo in modo più approfondito nei paragrafi successivi.

3.1.1 Elemento di ritardo a controllo digitale: shunt-capacitor

Come è già stato accennato l’elemento di ritardo elementare che costituisce le nostre celle è lo shunt-capacitor. Vediamo di analizzare in modo più dettagliato il funzionamento dei carichi di tipo shunt-capacitor; per far ciò, bisogna subito notare che la capacità di gate di un transistore NMOS è non lineare e variabile a seconda che si lavori in zona triodo, in saturazione o in interdizione, quindi bisogna fare attenzione al fatto che la polarizzazione del transistore-condensatore cambia a seconda del livello logico dell’uscita dell’inverter. Questo comporta il fenomeno del pulse-shrinking.

Nell’ambito dell’analisi del funzionamento di questi dispositivi, vediamo quali sono le capacità che si vedono dal terminale D/S: le capacità dovute alle

giunzioni che i pozzetti di source e di drain formano con il substrato, le quali sono costituite da una parte proporzionale al perimetro e una proporzionale all’area dei pozzetti che non dipendono dalla zona della caratteristica in cui il transistore sta funzionando:

CBS = CJAS + CJSWPS

CBD = CJAD + CJSWPD

le capacità che si vedono verso il gate che sono a loro volta costituite da due parti. La prima è dovuta alla sovrapposizione geometrica tra il gate e i terminali di drain e source a causa della diffusione laterale, delle maschere e degli attacchi acidi. La seconda dipende invece dalla distribuzione della carica sotto il gate cioè dalla forma del canale e quindi dalla polarizzazione:

CGS = COVGS + CGSC(VG,VS,VD,VB)

CGD = COVGD + CGDC(VG,VS,VD,VB)

In prima approssimazione il secondo contributo è nullo quando il transistore è interdetto poiché il canale non è formato, mentre quando siamo in zona triodo si ha: CGSC = CGDC = 2 L W Cox⋅ ⋅

Quando questa capacità è presente, il suo valore è nettamente superiore agli altri contributi ed è proprio questo fenomeno che viene sfruttato con l’uso degli shunt capacitor in una cella di ritardo. In Figura 3.3 viene mostrata la sezione di un transistore-condensatore NMOS in cui vengono indicate le capacità sopra menzionate.

B D/S CC CBD CBS COVGS COVGD D S G P N N

Figura 3.3 Sezione di un transistore-condensatore NMOS

Durante il funzionamento della cella, la tensione VD/S è imposta dall’inverter e

può variare tra 0 e la tensione di alimentazione, che per il processo a 0.35µm della AMS è fissata a 3.3 V. La tensione VG, invece, può essere fissata a 0 o 3.3 V dal

sistema usato per controllare i condensatori. Nel primo caso (VG = 0 V) il canale

non può formarsi in quanto:

VGS = VG – VD/S = - VD/S < VT

Nel secondo caso (VG = 3.3 V), finchè risulta verificata la condizione:

0 < VD/S < VDD - VT

il transistore lavora in zona lineare, l’armatura inferiore del condensatore è completamente formata (il canale si è formato in maniera uniforme) e l’azione caricante dell’inverter viene perfettamente esercitata.

Quando la tensione VD/S > VDD – VT si verifica che:

VGS = VG – VD/S < VT

Il canale scompare e la capacità di carico dell’inverter si riduce fortemente.

3.2.2 Modello elettrico dello shunt-capacitor

Per simulare correttamente i transistori-capacitori che utilizziamo come carichi della cella non possiamo lasciare che il simulatore SPECTRE di CADENCE veda lo shunt-capacitor come un semplice transistore MOSFET con il

drain e source cortocircuitati, questo a causa della notevole influenza delle resistenze parassite di canale.

Durante le simulazioni transitorie un qualsiasi MOSFET viene trattato attraverso un modello equivalente i cui parametri dipendono dalla geometria e dalla tecnologia usata.

Nel caso di funzionamento in zona triodo nelle model usate da SPECTRE si tiene conto della resistenza globale di canale in quanto la corrente che scorre tra drain e source è fissata dalla differenza di potenziale presente tra essi. Se però questi due terminali sono cortocircuitati, la resistenza di canale scompare e la corrente risulta essere nulla. Il transistore diventa in pratica una pura capacità, con resistenza delle armature nulla; quindi questo modello risulta essere inesatto poiché la corrente scorre nelle armature e incontra sia la resistenza del gate che quella del canale. Quest’ultima è tutt’altro che trascurabile ed il suo valore dipende dalla differenza tra la tensione gate-source e la tensione di soglia la quale risente dell’effetto body.

Per tener conto della formazione o della scomparsa del canale durante la variazione di VD/S non possiamo rinunciare del tutto al modello classico del

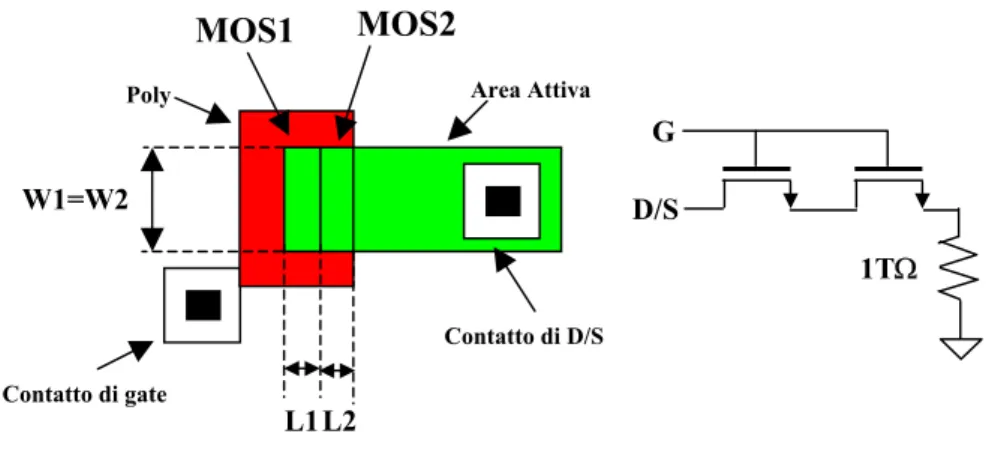

transistore MOSFET. Per simulare la distribuzione delle cariche sulle armature possiamo utilizzare un modello costituito da una catena di transistori ciascuno dei quali rappresenta una porzione di condensatore. Il modello di shunt-capacitor utilizzato nell’ambito di questa tesi è realizzato con una catena costituita da due soli transistori. La catena si sviluppa a partire dal contatto di D/S verso l’esterno del condensatore con l’ultimo terminale che dovrebbe essere flottante in quanto da esso non può uscire corrente. Per consentire la simulazione colleghiamo a questo terminale una resistenza molto alta. In Figura 3.4 è mostrato un esempio di shunt capacitor rettangolare con relativo circuito elettrico equivalente.

Poly Area Attiva D/S G 1TΩ Contatto di D/S Contatto di gate W1=W2 L2 L1 MOS1 MOS2

Figura 3.4 Esempio di shunt-capacitor rettangolare con circuito elettrico equivalente

Delle dimensioni geometriche di ciascun shunt-capacitor utilizzato (W1,W2, L1, L2) nel progetto del deskewer parleremo nel paragrafo relativo ai condensatori. Il modello è ulteriormente perfezionato per quanto riguarda i transistori intermedi. Per essi infatti la capacità introdotta deve essere solo quella di canale e quindi è necessario annullare l’area e il perimetro di drain e source, tutti i parametri che per i normali transistori tengono conto degli effetti capacitivi di bordo (capacità di overlap) e infine i fattori di correzione sulle dimensioni geometriche dovute alle maschere, alla diffusione laterale e agli attacchi acidi.

3.2 Progetto delle celle di ritardo

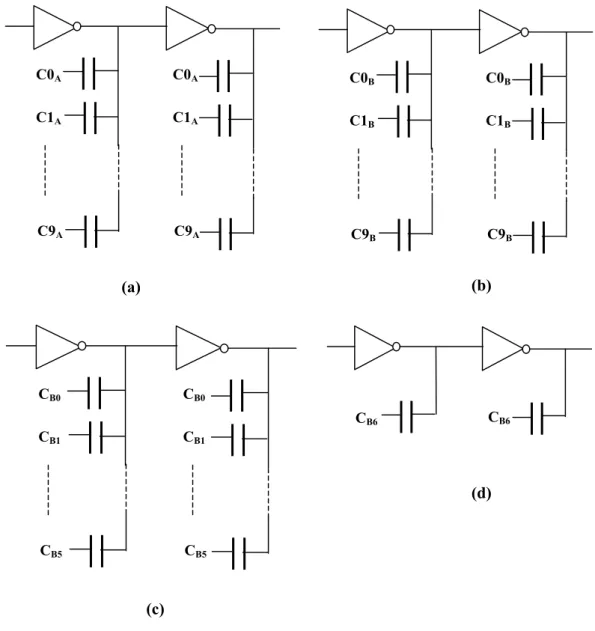

Definita la struttura e il tipo di carichi per le linee non ci resta che definire il numero di carichi per ogni cella e la loro dimensione, scelte in base alle specifiche di progetto. Ricordiamo che le 2 linee sono caratterizzate ognuna da 3 celle diverse tra loro. In Figura 3.5 riportiamo lo schema delle celle di ritardo in cui gli shunt-capacitor sono rappresentati con il simbolo di una semplice capacità. Le celle che contengono le capacità per la correzione che utilizza il metodo di bisezione sono perfettamente uguali per entrambe le linee, mentre le celle che

contengono le capacità per la correzione che utilizza il metodo differenziale al nonio sono diverse in quanto il ritardo introdotto dalla cella della linea di ritardo superiore è leggermente minore di quello introdotto dalla cella della linea di ritardo inferiore in modo tale da poter applicare il principio del nonio.

C0A C9A (d) (b) (a) CB6 CB6 CB5 CB1 CB0 CB5 CB1 CB0 C9B C1B C0B C9B C1B C0B C9A C1A C0A C1A (c)

Figura 3.5 Struttura delle celle di ritardo

Nella figura 3.5 (a) è riportato lo schema della cella di ritardo usata per il metodo del nonio della linea di ritardo superiore. Notiamo che i carichi in uscita ad ogni inverter sono costituiti da dieci condensatori (C0A-C9A) tutti uguali tra loro.

Questi condensatori sono stati progettati in modo tale che il ritardo introdotto da ognuno di essi sia pari approssimativamente a 1.5 ps. Nella figura 3.5 (b) è riportato lo schema della cella di ritardo usata per il metodo del nonio della linea di ritardo inferiore. La struttura di tale cella è uguale a quella della cella della linea superiore l’unica differenza è che i dieci condensatori (C0B-C9B) sono stati

progettati in modo tale che il ritardo introdotto da ognuno di loro sia approssimativamente pari a 1.7 ps rispetto al ritardo nominale introdotto dalla linea. Nella figura 3.5 (c), (d) sono riportate le strutture delle due celle contenenti le capacità di bisezione (CB0-CB6) relative ad entrambe le linee. I sette

condensatori di bisezione hanno grandezze crescenti secondo la potenza di due da CB0 a CB6 in modo tale che CB1 è grande il doppio di CB0, CB2 è grande 4 volte CB0

e così via fino a CB6 che è grande 64 volte CB0. Il condensatore CB0 è stato

progettato in modo da introdurre un ritardo approssimativamente uguale a 0.9 ps valutato sempre in condizioni nominali. Come è possibile notare dalla figura 3.5 (c), (d) le capacità di carico di bisezione sono state suddivise in due celle contenenti rispettivamente (CB0-CB5) e CB6. Questa scelta è stata fatta per limitare

il numero di condensatori per ogni cella, in quanto per ottenere ritardi crescenti come la potenza di due è necessario realizzare le capacità di carico più grandi come il parallelo di tante CB0. Ad esempio per ottenere un ritardo pari al doppio

del ritardo introdotto dalla sola CB0 la relativa capacità che introduce questo

ritardo (CB1) è realizzata collegando due capacità CB0 in parallelo e così via fino

alla CB6 ottenuta collegando 64 capacità CB0 in parallelo. Tutte queste capacità di

carico su una sola cella avrebbero introdotto non linearità inaccettabili nella caratteristica di ritardo. Questo perché ogni capacità di carico introduce come già detto delle capacità parassite che possono diventare dannose al crescere del numero delle CB. Infatti la presenza del ritardo dovuto a questi elementi parassiti

non garantisce più che i ritardi introdotti inserendo le varie CB siano quelli

desiderati in quanto all’aumentare della capacità e quindi del numero delle CB0 il

comportamento delle capacità diventa non lineare. Ci siamo accorti che separando la CB6 questa non linearità è notevolmente ridotta permettendoci di ottenere con

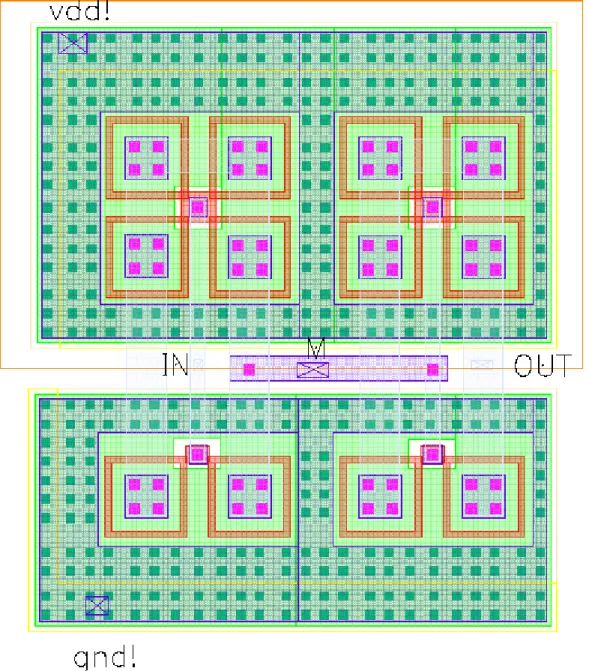

Nelle tavole I,II,III,IV sono rappresentati i layout completi delle celle di ritardo comprendenti gli inverter dei buffer di cella e le relative capacità di carico. Nei prossimi paragrafi approfondiremo i punti principali del progetto di tutti i componenti del deskewer del quale poi analizzeremo le prestazioni.

3.3 Gli

inverter

Per quanto concerne il progetto degli inverter della cella, essi devono essere identici per consentire la simmetria nella propagazione dei fronti e devono dare un basso ritardo a vuoto: ciò implica la minima capacità parassita in uscita e un rapporto W/L elevato.

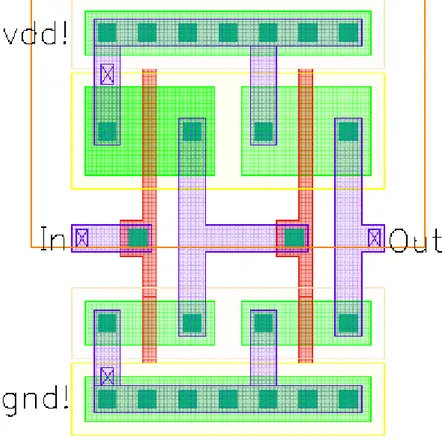

Poiché la diffusione di drain presente sull’uscita dell’inverter, può avere un valore capacitivo elevato, si è adottata per i transistori che costituiscono l’inverter la forma ad anello, come si può osservare dalla Figura 3.6 in cui è riportato il layout dei due inverter che formano una cella. In tal modo si è minimizzata la capacità di drain dei due transistori, soprattutto quella associata al perimetro di drain.

Anche utilizzando questa particolare forma, i parametri W e L valutati dall’estrattore (DIVA), ben rappresentano l’effettiva forza dei transitori. Infatti il layout di un qualsiasi transistore l’estrattore valuta sia l’area di gate (dall’intersezione della maschera del poly e dell’area attiva), sia la larghezza WTOT di gate intesa come il bordo affacciato verso la diffusione di source e drain.

I parametri W e L del transistore sono poi valutati nel seguente modo:

W Area L W W TOT = = 2

Quindi il transistore RETTANGOLARE equivalente a quello effettivamente disegnato ha una larghezza di canale pari alla media tra quelle viste tra drain e source e una lunghezza tale da rendere equivalenti le aree.

Nel nostro caso l’estrattore ha valutato una lunghezza di canale L= 0.3 µm, mentre la larghezza è risultata Wp = 52 µm per i transistori PMOS, e Wn = 26 µm

per i transistori NMOS.

Vediamo di seguito (Figura 3.7) come determinare le dimensioni dell’anello una volta note larghezza (W) e lunghezza (L) del transistore MOS.

min min min min 2 4 4 8 2 3 . 0 L l l P l L W P L P P P P W m L L i e i i i i e e i ⋅ + = = ⋅ − = ⋅ + = + = = = µ Anello di Poly W Lmin Lmin li le

Figura 3.7 Dimensionamento anello di poly

Dove Pi è il perimetro interno dell’anello e Pe è il perimetro esterno. L’anello è di

forma quadrata. Un’altra cosa che si può notare dalla figura 3.6 sono gli anelli di contatti di substrato che circondano gli inverter di cella. Tale accorgimento è stato adottato per prevenire i problemi di latch-up a cui possono dare luogo transistori di questa potenza e consente tra l’altro di aumentare la capacità parassita presente sull’alimentazione con un benefico effetto stabilizzante.

3.4 I

condensatori

Le precedenti realizzazioni di linee di ritardo che utilizzavano shunt capacitor [2], hanno dimostrato che il ritardo introdotto da un transistore capacitore non dipende solo dalla sua area, ma anche dalla sua forma e dalla distanza delle varie parti del canale dal contatto di D/S. Ciò avviene a causa dell’inevitabile presenza di resistenze parassite sia di canale che di gate di cui sia l’estrattore che il simulatore non tengono conto. Se per esempio si vuole realizzare un condensatore che introduce un ritardo pari al doppio di quello di un

altro, non si può semplicemente progettarlo mantenendo la stessa forma e allargare l’area di gate fino al doppio in quanto in questo modo ci saranno zone (quelle più lontane dal contatto di D/S) in cui il canale si formerà più tardi a causa della presenza delle resistenze parassite che ritardano la distribuzione delle cariche sulle armature. Come conseguenza il ritardo introdotto risulterà minore di quello che ci si aspettava. Conseguenze ancora peggiori e imprevedibili ci sarebbero se si progettasse il nuovo transistore cambiandone completamente la forma. Se vogliamo realizzare dei condensatori di grande capacità e vogliamo essere sicuri delle relazioni tra ritardi introdotti dobbiamo rispettare le relazioni tra le aree senza cambiare ne la forma del condensatore, ne i tempi di distribuzione delle cariche sulle armature. Quindi come già accennato precedentemente, il metodo migliore per realizzare per esempio condensatori che devono introdurre ritardo doppio è quello di mettere due condensatori uguali in parallelo. Nel nostro caso, i condensatori di bisezione (CB1 -CB5) sono costituiti rispettivamente da 2, 4,

8, 16, 32 condensatori CB0 posti in parallelo, mentre CB6 è costituito da 64

condensatori CB0’ in parallelo dove CB0’è leggermente diverso come dimensioni

rispetto a CB0 ma mantiene la stessa forma.

3.4.1 Layout e calibrazione dei condensatori

Passiamo ora ad analizzare le caratteristiche dei quattro condensatori da noi utilizzati. Nella tabella che segue ne sono riportate le dimensioni.

Tipo Area (µm2)

C0A 0.6

C0B 0.7

CB0 0.545

CB0’ 0.52

Visto che le dimensioni di ognuno di essi sono piccole non è stato necessario utilizzare nessuna forma particolare per la realizzazione del layout, infatti è stata utilizzata la semplice forma rettangolare.

Le dimensioni minime possibili, con la tecnologia utilizzata, sono lunghezza L = 0.3 µm e larghezza W = 0.3 µm. Da notare che nel layout di tutti i condensatori, per minimizzare il ritardo a vuoto della cella, i contatti di source/drain sono stati condivisi a coppie.

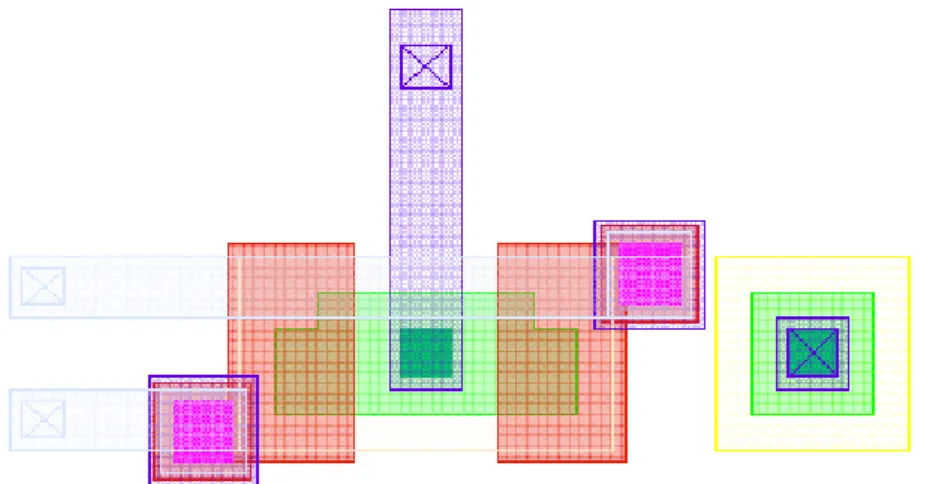

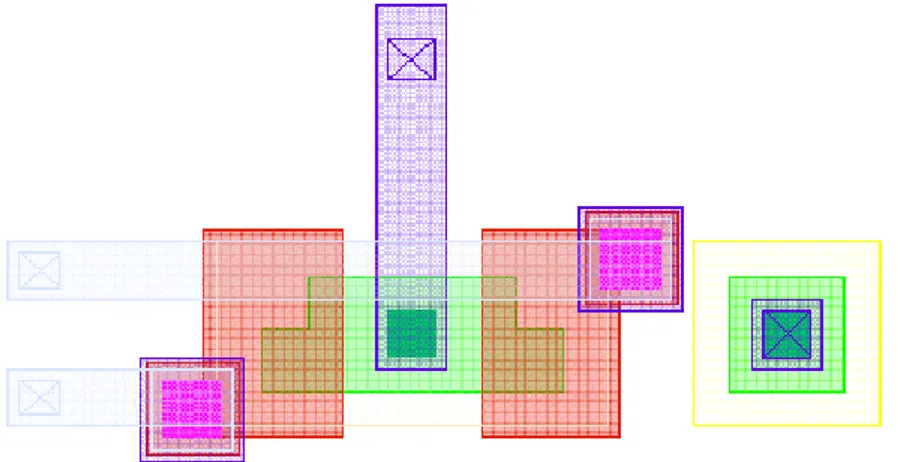

Cominciamo con la descrizione dei condensatori usati per il metodo del nonio (C0A e C0B) relativi alla linea di ritardo superiore e a quella inferiore i cui

layout sono mostrati rispettivamente nella Figura 3.8 e nella Figura 3.9.

Figura 3.8 Layout delle capacità differenziali della linea superiore

Per il dimensionamento di tali condensatori, più che del ritardo introdotto da ciascun condensatore relativo alla rispettiva linea, si è tenuto conto del ritardo introdotto inserendo i condensatori a coppie (uno della linea superiore e uno della linea inferiore). Questo perché lo scopo è quello di realizzare un ritardo differenziale molto piccolo.

Riportiamo nella tabella sottostante le dimensioni espresse in µm dei due transitori relative ai due condensatori differenziali: C0A e C0B.

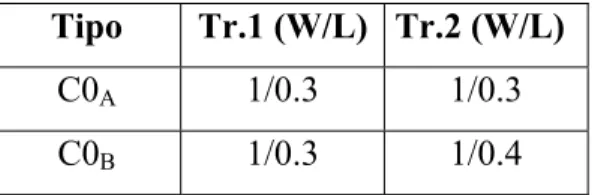

Tipo Tr.1 (W/L) Tr.2 (W/L)

C0A 1/0.3 1/0.3

C0B 1/0.3 1/0.4

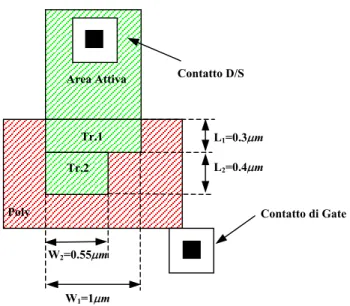

Come si nota dai valori della tabella e dalla Figura 3.10 abbiamo aumentato la lunghezza del secondo transistore della C0B, in modo tale che il mismatch tra i

due transistori (Tr.2 di C0A e Tr.2 di C0B) desse luogo alla piccola differenza di

ritardo introdotta dai due condensatori differenziali.

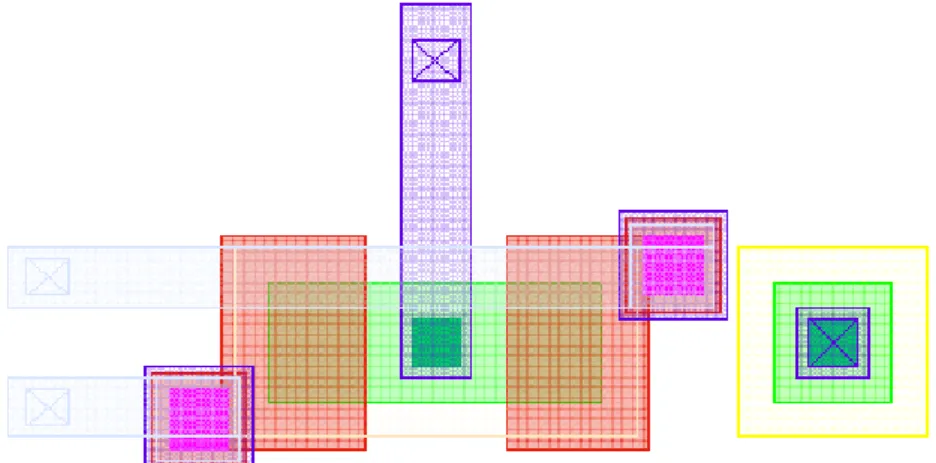

Contatto D/S Contatto di Gate Area Attiva Tr.2 Tr.1 W1=W2=1µm L2=0.4µm L1=0.3µm Poly Area Attiva Tr.2 Tr.1 W1=W2=1µm L2=0.3µm L1=0.3µm Poly (C0A) (C0B)

Passiamo ora alla descrizione del condensatore di bisezione CB0. Come è stato già

detto la sua forma è di tipo rettangolare come mostrato in Figura 3.11 in cui è rappresentato il layout.

Figura 3.11 Layout delle capacità di bisezione (CB0)

Le dimensioni di tale condensatore sono state scelte in modo tale da introdurre un ritardo pari a 0.9 ps. Nella tabella riportata di seguito sono espresse in µm la lunghezza e la larghezza dei 2 transistori che costituiscono il modello del condensatore. Tipo Tr.1 (W/L) Tr.2 (W/L) CB0 1/0.3 0.7/0.35 W1=1µm L1=0.3µm L2=0.35µm Tr.1 Tr.2

Area Attiva Contatto D/S

W2=0.7µm

Poly Contatto di Gate

Nella Figura 3.12 è mostrata la schematizzazione della capacità di bisezione CB0.

La capacità CB0’ è stata utilizzata per determinare la capacità CB6. Il suo

layout è rappresentato in Figura 3.13.

Figura 3.13 Layout delle capacità di bisezione (CB0’)

La scelta delle sue dimensioni è stata fatta in base al fatto che il ritardo che si desidera introdurre con la CB6, capacità ottenuta mettendo in parallelo 64 CB0’,

sia pari al doppio del ritardo introdotto dalla CB5. L’unica cosa che si è cercata di

rispettare è la forma di CB0’ la quale deve essere uguale a quella della CB0, in

modo da evitare i problemi di cui abbiamo precedentemente parlato. Le dimensioni espresse in µm dei due transistori che costituiscono la CB0’ sono

riportate nella tabella che segue e in Figura 3.14 è mostrata una sua schematizzazione.

Tipo Tr.1 (W/L) Tr.2 (W/L)

Contatto D/S W2=0.55µm Area Attiva Tr.2 Tr.1 W1=1µm L2=0.4µm L1=0.3µm

Poly Contatto di Gate

Figura 3.14 Schematizzazione della capacità di bisezione di CB0’

È stato quindi creato uno schematico equivalente della cella di ritardo nel quale al posto dei condensatori sono stati sostituiti i transistori secondo la scomposizione appena descritta e successivamente la cella sotto esame è stata inserita all’interno di una catena di tre celle. Nella Tabella 3.1 sono presentati i ritardi introdotti dalle capacità di bisezione, il valore ideale e l’errore percentuale che commettiamo nel caso typical, risultati dalle simulazioni typical, worst speed e worst power calcolati sulla simulazione dello schematico.

Ricordiamo che nelle condizioni typical, worst speed e worst power, vengono applicate una tensione di alimentazione pari rispettivamente a 3.3 V, 3 V, 3.6 V e una temperatura di 27, 85 e 0 gradi centigradi.

Dalla Tabella 3.1 è possibile notare che anche nei casi worst speed e worst power viene comunque mantenuta la proporzionalità dei ritardi introdotti secondo la potenza di due.

Capacità di Bisezione Worst Speed (ps) Typical (ps) Worst Power (ps) Valore ideale (ps) Errore (%) CB0 1.3 0.9 0.6 0.9 0 CB1 2.6 1.8 1.3 1.8 0 CB2 5.3 3.6 2.5 3.6 0 CB3 10.6 7.3 5 7.2 Err.Simulaz. CB4 21.2 14.6 10 14.4 1.38 CB5 42.4 29.3 20.2 28.8 1.73 CB6 81.5 57.4 40.2 57.6 0.35 Tabella 3.1

Nelle Tabelle 3.2 e 3.3 vengono presentati i valori dei ritardi introdotti dalle capacità C0A e C0B delle due linee (superiore ed inferiore) nelle tre

condizioni di funzionamento. Capacità Differenziali Worst Speed (ps) Typical (ps) Worst Power (ps) C0A 2.3 1.5 1 C1A 2.4 1.5 1 C2A 2.3 1.4 0.9 C3A 2.3 1.5 1 C4A 2.3 1.5 1 C5A 2.3 1.4 0.9 C6A 2.4 1.5 1 C7A 2.3 1.5 1 C8A 2.3 1.4 0.9 C9A 2.3 1.5 1 Tabella 3.2

Capacità Differenziali Worst Speed (ps) Typical (ps) Worst Power (ps) C0B 2.5 1.7 1.1 C1B 2.6 1.6 1.1 C2B 2.5 1.7 1.1 C3B 2.5 1.6 1.1 C4B 2.5 1.6 1.1 C5B 2.5 1.7 1.1 C6B 2.6 1.6 1.1 C7B 2.5 1.6 1.1 C8B 2.5 1.6 1.1 C9B 2.5 1.6 1 Tabella 3.3

Dalle Tabella 3.2 e 3.3, confrontando i dati per relativa colonna, si evince come il mismatch tra le due capacità differenziali produca quella piccola differenza tra i ritardi introdotti dalle due linee rispetto al valore nominale, tale da permettere la corretta applicazione del metodo del nonio per il recupero differenziale dello skew residuo. Nel capitolo successivo saranno presentati i dati prodotti dalle simulazioni post-layout per meglio apprezzare i risultati ottenuti.

3.5 I buffer di linea

A monte e a valle della catena di tre celle che caratterizzano le due linee di ritardo sono stati collocati due buffer le cui dimensioni dei transistori che costituiscono gli inverter sono Wn = 1 µm per gli NMOS, Wp = 2 µm per i PMOS

e lunghezza L = Lmin = 0.3 µm per entrambi. Ricordiamo che nella progettazione

di tipo digitale la scelta di realizzare i transistori di tipo PMOS con larghezza di canale pari al doppio rispetto a quella dei transistori NMOS è dovuta al fatto che la mobilità delle lacune è circa la metà rispetto a quella degli elettroni. Quindi

avere Wp ≈ 2Wn ci garantisce che i tempi di salita (trise) e i tempi di discesa (tfall)

del segnale di clock siano circa uguali. L’inserimento dei buffer è stato necessario per equalizzare sia il carico pilotato, che il segnale ricevuto in ingresso dalla catena di tre celle.

Nella Figura 3.15 è mostrata una schematizzazione a blocchi di una porzione di linea, il cui scopo è quello di evidenziare meglio i punti in cui sono stati inseriti i due buffer.

Buffer Buffer Cella di ritardo 1 Cella di ritardo 3 …… …… …… Cella di ritardo 2

Figura 3.15 Schema a blocchi di una porzione di linea

In Figura 3.16 è rappresentato il layout dei buffer.

Dalla Figura 3.16 si nota che il layout è stato realizzato rispettando alcune regole di matching, infatti i dispositivi hanno uguale forma e dimensioni quasi minime.

3.6 I

multiplexer

I multiplexer a due vie giocano un ruolo importante nell’applicazione della strategia di correzione dello skew tra i due segnali di sincronizzazione e nella distribuzione degli stessi ai diversi sistemi sincroni.

Nell’architettura del deskewer proposto in questo lavoro di tesi i multiplexer sono introdotti sia a monte del buffer di ingresso, per introdurre l’offset, di cui parleremo in modo più dettagliato nel prossimo paragrafo, che a valle del buffer di uscita. Vediamo più in dettaglio la funzione dei MUX posti a valle del buffer di uscita delle linee.

Quando le due linee sono scariche (in condizioni nominali) introducono lo stesso ritardo sul clock di sistema. I segnali di sincronismo in uscita dal deskewer percorrendo due piste di interconnessione di lunghezze diverse per giungere ai sistemi sincroni e avendo in generale da pilotare carichi diversi saranno soggetti a ritardi di propagazione diversi. Valutato il segno dello sfasamento tra i due segnali attraverso il phase-detector i multiplexer hanno il compito di far sì che la linea che ha capacità differenziali maggiori e in cui è presente l’offset diventi la linea di distribuzione del segnale di sincronismo che risulta essere in anticipo rispetto all’altro. Questa è una condizione necessaria per poter applicare con successo la correzione con il metodo del nonio. Particolare cura è stata dedicata alle due piste di interconnessione che permettono l’inversione di percorso tra i due segnali di sincronismo. Queste due piste devono avere uguale lunghezza per evitare di introdurre un ulteriore sfasamento tra i due segnali nelle condizioni di funzionamento nominali (cioè con linee scariche). In Figura 3.17 riportiamo una schematizzazione a blocchi del deskewer in cui vengono mostrati in maniera dettagliata i punti in cui i MUX sono inseriti.

B A Linea Superiore 1 1 1 1 0 0 0 0 S1 S2 E1 E2 E1 E2 Clk_sys Offset Buffer Buffer Buffer Buffer Mux_B Mux_A Mux Mux

Catena di tre celle di ritardo Catena di tre celle di ritardo

Linea Inferiore

Figura 3.17 Schematizzazione a blocchi deskewer

I multiplexer sono stati realizzati con una struttura a pass-gate, per minimizzare le dimensioni di ingombro su silicio come mostrato in Figura 3.18. Si è preferito utilizzare due segnali (S1(E1), S2(E2)) di controllo per selezionare le vie del multiplexer in quanto l’introduzione di un inverter se pur di dimensioni minime, introduceva delle dissimmetrie strutturali che si ripercuotevano sul tempo di attraversamento di ciascuna via non rendendoli uguali, andando quindi contro le specifiche di progetto richieste.

S1

( )

E1 =1 S2( )

E2 =0 U =B S1( )

E1 =0 S2( )

E2 =1 U= A A U Wn= 2µm Wp= 4µm B S2(E2) S1(E1)Il layout del multiplexer è mostrato in Figura 3.19.

Figura 3.19 Layout multiplexer a due vie

Per i transistori di ciascuna pass-gate si è scelta la forma a pettine per diminuirne le dimensioni di ingombro e per minimizzare le capacità parassite introdotte dal contatto di drain. Infatti osservando la Figura 3.20 notiamo che gli elettrodi D e S non sono tecnologicamente uguali, in quanto l’area occupata dalla giunzione di D è pari a metà di quella occupata dal S. Il fatto che l’area di D sia dimezzata determina una riduzione delle capacità di carico.

D

S S

3.7 L’offset

Per un corretto funzionamento dell’algoritmo di bisezione doppio è stato necessario introdurre un offset. Esso è stato inserito sulla linea di ritardo contenente le capacità differenziali maggiori. Cerchiamo di spiegare meglio perché l’offset è necessario.

L’algoritmo di bisezione sfrutta il metodo delle approssimazioni successive (SAR) il quale viene applicato in modo duale su entrambi i segnali di clock. Sul segnale in anticipo l’algoritmo permette di inserire ad ogni passo di correzione un ritardo, partendo da una situazione in cui tutte le capacità di bisezione sono spente. Sul segnale in ritardo invece l’algoritmo deve permettere di disinserire ad ogni passo di correzione un ritardo analogo a quello inserito sul segnale in anticipo, partendo da una situazione in cui tutte le capacità di bisezione sono accese. Questa strategia di correzione permette con numero di passi minore (quindi con un numero di capacità di bisezione minore) di recuperare un range di sfasamento più ampio rispetto al caso in cui l’algoritmo fosse applicato solo al segnale in anticipo. Il fatto di partire con tutte le capacità di bisezione accese sulla linea su cui si propaga il segnale in ritardo, comporta la necessità di aggiungere un offset pari al ritardo introdotto da tutte le capacità di bisezione sul segnale in anticipo, segnale che verrà deviato sulla linea in cui è presente tale offset (nel nostro caso sulla linea inferiore come mostrato in Figura 3.17). La Figura 3.21 descrive la soluzione circuitale che permette l’inserimento dell’offset.

Offset

1

0 E1 E2

L’offset è stato realizzato con un buffer in cui si è adottata per i transistori che costituiscono l’inverter la forma a pettine, (interallacciata) come si può osservare dalla Figura 3.22 in cui è riportato il layout degli inverter che costituiscono il buffer per l’offset. Noto il valore del ritardo introdotto quando tutte le capacità di bisezione sono inserite pari a 117.4 ps, attraverso una serie di simulazioni sono state determinate le necessarie dimensioni geometriche dei transistori, le quali hanno determinato un ritardo pari a 116.7 ps. Si nota che l’errore commesso rispetto al ritardo totale introdotto dalle capacità di bisezione è dello 0.6 %, valore che può essere considerato trascurabile. Le dimensioni sono: Wp= 9 µm per i

transistori PMOS e Wn= 4.5 µm per i transistori NMOS e lunghezza minima di

canale L= 0.3 µm.

3.8 Il

phase

detector

Il circuito phase detector (PD) è stato realizzato completamente in modo fullcustom, per poter ottenere la necessaria sensibilità richiesta dalle specifiche di progetto. Esso deve generare un segnale Trig in modo che valga 1 se la configurazione dello sfasamento è tale per cui il segnale Clk_A (come mostrato in

Figura 3.1 ) è in anticipo rispetto al segnale Clk_B e 0 in caso contrario.

Tale segnale verrà poi sincronizzato con il clock del controllore di fase, il quale utilizzerà l’informazione ricevuta per produrre la parola digitale utilizzata per cambiare opportunamente la configurazione delle capacità di carico di ogni cella costituente la linea di ritardo e realizzare così la retroazione negativa.

Inizialmente il deskewer è completamente scarico, cioè tutte le capacità adibite alla correzione dello skew del clock sono disattivate e il ritardo introdotto dalle due linee è identico per entrambe (ritardo nominale delle linee).

Ricevendo il segnale di Trig, il controllore di fase avrà il compito di inserire i condensatori per la correzione dello skew secondo i due algoritmi in esso implementati (Bisezione doppia, Differenziale al Nonio). Per comprendere al meglio la descrizione che segue precisiamo che la soluzione adottata in questo progetto discrimina la fase dei fronti di discesa dei due segnali di sincronismo.

Molti phase detector presentano una regione a guadagno molto basso o nullo vicino la zona in cui la differenza di fase tra i segnali di ingresso è prossima allo zero. Questa regione di basso guadagno [3] come mostrato in Figura 3.23 è comunemente definita “dead-zone”. L’origine della dead-zone nei phase detector di tipo digitale è data dall’incapacità di generare impulsi infinitamente corti (proporzionali allo sfasamento tra i segnali) che indichino la presenza di piccoli sfasamenti tra i due segnali. La presenza di questa zona morta deteriora le prestazioni del rilevatore di fase in quanto ne diminuisce la sensibilità. phase detector accurati devono avere dead-zone nulla o comunque la più piccola possibile e devono risultare il più possibile insensibili ad un certo numero di

imperfezioni, come ad esempio il mismatch circuitale dovuto al processo tecnologico [4]. Differenza di Fase Tensione di uscita del PD+CP Dead-Zone 0

Figura 3.23 Caratteristica di trasferimento PD

3.8.1 Phase detector basato sul sense amplifier

Il phase detector proposto nell’ambito di questa tesi si basa sull’utilizzo di un circuito bistabile quale il Sense Amplifier. Flip-flop basati sul sense amplifier (SAFF) sono presentati ad esempio in [5]. Questa soluzione riduce il fenomeno della dead-zone a valori piccolissimi e permette di ottenere risoluzioni sufficienti ai nostri scopi. Lo schema a blocchi dell’architettura adottata è mostrata in

Figura 3.24. Buffer Buffer /Trig Trig Clk_B Clk_A FF_SR (Nor) Sense Amplifier

Figura 3.24 Architettura phase detector

Come mostrato in Figura 3.24 il phase detector è costituito da due stadi, il primo è un sense amplifier mentre il secondo è un flip-flop SR realizzato a porte nor in

quanto questo rilevatore di fase è sensibile ai fronti in discesa del segnale di clock. Vediamo più in dettaglio la struttura del circuito phase detector in Figura 3.25.

Clk_A Clk_B Trig /Q Q R S M7 M5 M6 M8 M4 M3 M2 M1 Gnd Out_1 Out_2 Vdd S R Q

Figura 3.25 Schema elettrico del phase detector

Se gli ingressi, Clk_A e Clk_B sono entrambi alti abbiamo una situazione di precarica a 0, cioè tutti i nodi del circuito sono portati a tensione nulla. Se il fronte in discesa di Clk_A arriva prima del fronte in discesa di Clk_B allora il pull-down di precarica viene rilasciato prima nella parte di sinistra (M7) quindi il circuito si porta nello stato stabile in cui:

Out_1 = 1 Out_2 = 0

Configurazione che setta il flip-flop SR (ingressi attivi alti). Viceversa, se arriva prima il fronte in discesa di Clk_B rispetto a quello di Clk_A il sense amplifier si porta nello stato stabile in cui:

Out_1 = 0 Out_2 = 1

Configurazione che resetta il flip-flop SR. Quindi se Trig è alto significa che il fronte in discesa di Clk_A è arrivato in anticipo rispetto a quello di Clk_B, mentre se Trig è basso è il fronte in discesa di Clk_B che è arrivato in anticipo rispetto a quello di Clk_A, come mostrato dalla temporizzazione di Figura 3.26.

0 0 1 1 1 0 0 1 1 0 0 1 PRECARICA CONSERVAZIONE Out_1 Out_2 Clk_A Clk_B Out_2 Out_1 Clk_B Clk_A Conserv. Sbilanciamento Precarica Trig

Figura 3.26 Temporizzazione del sense amplifier con Clk_A in anticipo su Clk_B e tabella di verità

Quando si riaccende la prima precarica per evitare che questa provochi la commutazione del circuito è necessario realizzare i transistori di precarica (M7, M8) in modo da essere più deboli rispetto ai PMOS interni del bistabile (M3, M4). Il limite inferiore sulle dimensioni dei transistori di precarica è determinato dalla loro capacità di precaricare i nodi in un tempo pari alla metà del periodo di clock. Le dimensioni geometriche scelte sono riportate in Tabella 3.4

Tr. W L M1 12 µm 0.3 µm M2 12 µm 0.3 µm M3 10 µm 0.3 µm M4 10 µm 0.3 µm M5 2 µm 0.3 µm M6 2 µm 0.3 µm M7 0.6 µm 0.3 µm M8 0.6 µm 0.3 µm Tabella 3.4 3.8.2 Sense Amplifier

Il sense amplifier costituisce il cuore del phase detector proposto determinandone le sue caratteristiche di funzionamento. Nelle memorie DRAM il circuito fondamentale su cui si basa il sense amplifier è costituito da una coppia di inverter CMOS chiusi ad anello come si nota dalla Figura 3.27, per cui il circuito è intrinsecamente instabile.

Figura 3.27 Elemento bistabile

Avendo un comportamento bistabile quando si trova in uno dei suoi stati stabili, la corrente assorbita staticamente è nulla e quindi il consumo di potenza è nullo. Nelle DRAM la fase di lettura è un’operazione distruttiva per il contenuto informativo della cella di memoria. Per risolvere questo grave inconveniente si usa un sense amplifier in grado di discriminare la piccola d.d.p determinata dalla lettura della cella, di amplificarla e di riportare il segnale della bit-line ad un livello logico pieno. In pratica quando il sense amplifier rivela la piccola variazione di tensione sbilancia completamente la sua tensione di uscita verso un valore alto o basso di tensione in base al segno della variazione rilevata.

Sullo stesso principio di funzionamento si basa il rilevamento dello sfasamento tra i due segnali di sincronismo. In questa applicazione il sense

amplifier si sbilancia verso uno dei due stati stabili secondo il segno dello sfasamento rilevato cioè se Clk_A è in anticipo su Clk_B o viceversa. La sua simmetria circuitale riduce gli errori dovuti al mismatch circuitale introdotti dal processo tecnologico e aumenta la sensibilità dello sfasamento rilevato. In

Figura 3.28 viene mostrato il layout del sense amplifier. I transistori (M1, M2, M3, M4), viste le loro dimensioni (vedi Tabella 3.4), sono stati realizzati con la forma a pettine per ridurre l’ingombro su silicio.

Figura 3.28 Layout del sense amplifier

a) Determinazione del Sense Time

Il sense time del phase detector è il tempo che il circuito impiega per decidere quali dei due segnali in ingresso è in anticipo rispetto all’altro e per

presentare l’uscita relativa. Come è lecito aspettarsi il tempo di decisione aumenta al diminuire dello sfasamento in ingresso [6]. Quindi, quando il sense time è graficato in funzione dello sfasamento iniziale esistente tra i due segnali, un picco pronunciato è osservabile in corrispondenza dello sfasamento nullo. Essendo il rilevatore di fase proposto in questo progetto sensibile al fronte in discesa del segnale di clock il sense time è definito più precisamente come il ritardo che intercorre dall’istante in cui il fronte in discesa del segnale in anticipo supera la soglia di VDD/2 al momento in cui le tensioni di uscita del sense amplifier

differiscono di 2 V (circa pari a 2/3 VDD), al variare dello sfasamento presente tra i

due segnali. La Figura 3.29 mostra un esempio grafico della definizione del sense time e la relativa funzione utilizzata per la sua determinazione mediante il tool CALCULATOR di CADENCE. SENSE TIME (ps) (V) 0 1.65 2 V 3.3 Clk_A Clk_B Out_2 Out_1 SKEW

(

)

(

VT("/Clk_A"),1.65,4,"either"abs((VT("/Out_1") VT("/Out_2"))),2,4,"either";)

Delay f skew f time sense − = = − Figura 3.29

È stata effettuata un’analisi parametrica facendo variare lo skew del clock in un range compreso tra 0 e 200 ps in modo simmetrico per ogni segnale. Il sense time misurato dalle simulazioni elettriche è mostrato in Figura 3.30 in cui è possibile osservare come in corrispondenza di uno sfasamento nullo si ha la presenza di un valore di picco.

0.0 70.0 140.0 210.0 280.0 350.0 420.0 490.0 560.0 630.0 700.0 770.0 840.0 910.0 -200 -150 -100 -50 0 49 99 149 199 Skew (ps) Se nse T im e (ps)

Figura 3.30 Sense time in funzione dello skew del clock

b) Determinazione del Sense Time in presenza di mismatch

Come già accennato, il progetto del layout del sense amplifier è stato realizzato rispettando il più possibile le simmetrie sulla disposizione dei transistori che lo costituiscono, in quanto il mismatch circuitale dovuto al processo tecnologico influenza negativamente la sensibilità del dispositivo.

Per verificare come la sensibilità sul rilevamento dello sfasamento dei segnali d’ingresso dipenda in maniera considerevole dagli errori dovuti al processo tecnologico, si è condotta un’analisi parametrica sul sense time variando la larghezza di canale della coppia di transistori NMOS (M5, M6) e dei PMOS (M3, M4) del bistabile con una tolleranza che varia in un range del ± 5% rispetto al loro valore nominale (vedi Tabella 3.4).

Nell’analisi parametrica è stata introdotta una variabile δ la quale tiene conto del valore della tolleranza ad ogni step di simulazione. Ad ogni passo di simulazione le larghezze di canale della coppia di transistori NMOS (M5, M6) viene variata nel seguente modo:

δ δ − = + = nom nom W W W W 6 6 5 5 con 2 mismatch = δ

lo stesso tipo di analisi è stata condotta per la coppia di transistori PMOS (M3, M4): δ δ − = + = nom nom W W W W 4 4 3 3

Il δ è stato fatto variare nell’intervallo ±5%, con un numero di step pari a cinque, ottenendo così una famiglia di cinque curve sense time/sfasamento per ogni coppia di transistori. Così facendo abbiamo garantito che il mismatch totale introdotto ad ogni passo sia quello desiderato e che la famiglia di curve sia perfettamente simmetrica rispetto al valore ideale. In Figura 3.31 e Figura 3.32 viene rappresentato il sense time in presenza di mismatch al variare dello skew presente tra i due segnali di sincronismo rispettivamente per la coppia di transistori NMOS e per la coppia di transistori PMOS.

0 40 80 120 160 200 240 280 320 360 400 440 480 520 560 600 640 -11 -10 -9 -8 -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7 8 9 10 11 Skew (ps) Se nse _T im e (ps) Delta_wn 0nm Delta_wn 25nm Delta_wn 50nm Delta_wn -25nm Delta_wn -50nm

0 40 80 120 160 200 240 280 320 360 400 440 480 520 560 -50 -45 -40 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30 35 40 45 50 Skew (ps) Se nse _Tim e ( p s) Delta_wp -250nm Delta_wp -125nm Delta_wp 0nm Delta_wp 125nm Delta_wp 250nm

Figura 3.32 Sense time con mismatch su M3, M4

Dalle Figure 3.31 e 3.32 si nota che per un mismatch del 5% il picco si sposta nel caso peggiore di circa 12 ps. Osserviamo inoltre che il valore massimo sense time raggiunto dalle curve in figura non ha grande significato fisico in quanto dipende da quanto vicino si trovano i campioni allo sfasamento per il quale si ha il picco vero e proprio. In corrispondenza di esso infatti il sense time tende teoricamente all’infinito. Per evidenziare il comportamento della sensibilità del sense amplifier intorno a valori di sfasamento nullo lo skew è stato fatto variare in un range di valori più piccolo rispetto all’intervallo preso in analisi nello studio del deskewer.

I risultati delle due simulazioni parametriche mettono in evidenza come la sensibilità del sense amplifier dipenda anche di quale coppia di transistori del bistabile si stia facendo variare la larghezza di canale. Infatti si nota che il phase detector risente maggiormente degli errori di processo che agiscono sulla coppia di transistori PMOS rispetto alla coppia di transistori NMOS.

3.8.3 Flip-flop SR a porte NOR

Come mostrato in Figura 3.25 quando gli ingressi ai transistori di precarica (M7, M8) sono entrambi alti danno luogo ad una fase di precarica a ‘0’, ciò comporta che il circuito è sensibile alla fase dei fronti in discesa di Clk_A e Clk_B. Nella situazione in cui Clk_A è in anticipo rispetto a Clk_B la configurazione delle uscite del sense amplifier è Out_1 = 1 e Out_2 = 0, quindi set (S) va alto e reset (R) va basso; quando, invece, Clk_B è in anticipo rispetto a Clk_A allora la configurazione delle uscite è Out_1 = 0 e Out_2 = 1, quindi R va alto e S va basso. Per avere Trig alto nella prima configurazione di sfasamento e basso nella seconda gli ingressi al flip-flop SR devono essere attivi alti dunque la sua architettura può essere quella tradizionale a porte NOR. In Figura 3.33 è rappresentato il layout del flip-flop SR a porte NOR.

Come gli altri layout anche in questo caso è stata rispettata la simmetria circuitale nel disegno del dispositivo. Le dimensioni dei transistori che costituiscono le due porte nor sono le seguenti: Wn = 0.6 µm per gli NMOS e Wp = 1.2 µm per i

PMOS e lunghezza di canale minima L = 0.3 µm.

3.8.4 I buffer

I buffer presenti nell’architettura del phase detector mostrata in

Figura 3.24 sono stati realizzati con forme diverse ma grandezze identiche. Questo ha permesso di poter realizzare il layout del phase detector in maniera più compatta possibile in modo tale da ridurre l’area di silicio da processare e garantire un fattore di forma più unitario possibile (layout di forma quadrata). In particolare i buffer a monte del sense amplifier hanno una forma verticale mentre quelli a monte del flip-flop SR hanno forma orizzontale. Le dimensioni dei transistori che costituiscono gli inverter dei due buffer sono le seguenti: Wn = 0.6 µm per gli NMOS e Wp = 1.2 µm per i PMOS e lunghezza di canale

minima.

(b) (a)

3.8.5 Layout e simulazioni elettriche

Il layout del rivelatore di fase è stato realizzato in modo più possibile compatto ed è stato posizionato a destra delle linee di ritardo. Esso è presentato nella tavola IV. Particolare cura è posta nel posizionamento e nel collegamento dei segnali Clk_A e Clk_B in quanto è necessario che non introducano una differenza di fase che andrebbe ad alterare il funzionamento del rivelatore. Le dimensioni finali del circuito sono risultate di (29.2 x 26.75 µm2).

Per verificare la funzionalità del circuito sono state infine effettuate alcune simulazioni elettriche le quali hanno consentito di controllare la corretta generazione del segnale di Trig e il corretto funzionamento del rivelatore. In particolare ci siamo assicurati che la sensibilità del circuito fosse sufficiente a sentire il minimo cambiamento di fase in grado di produrre il segnale di Trig per il corretto funzionamento del controllore. Per far questo abbiamo fatto due simulazioni in cui abbiamo fatto arrivare al phase detector il segnale Clk_A in anticipo e in ritardo rispetto a Clk_B di 0.1 ps. In Figura 3.35 riportiamo le forme d’onda più significative risultanti dalla simulazione in cui Clk_A è posto in anticipo rispetto a Clk_B esattamente di 0.1 ps. Come si vede l’uscita Trig che inizialmente è bassa, diventa alta in corrispondenza del fronte di discesa di Clk_A, indicando correttamente al controllore di fase il segno dello sfasamento. Per la simulazione elettrica le uscite Trig e /Trig (nella waveform prodotta da CADENCE /Trig è indicato con Trig_) sono state chiuse su due capacità di carico del valore di 10 fF. In figura è riportato anche l’andamento dei segnali in uscita al sense amplifier (Out_1, Out_2), dove si nota come a partire da una situazione di precarica, quando viene rilevato lo sfasamento il sense amplifier si sbilancia portando il segnale Out_1 alto e il segnale Out_2 basso. La simulazione della situazione duale (Clk_B in anticipo su Clk_A) non viene riportata in quanto produce risultati del tutto analoghi: Trig inizialmente alto va basso, e il sense amplier sbilancia le uscite in modo da portare Out_1 basso e Out_2 alto.

/Clk_A

/Clk_B

Figura 3.35 Simulazione del phase detector

3.9 Progetto semicustom del controllore di fase

Il controllore di fase, come già detto, ha il compito di pilotare secondo una opportuna strategia di correzione, i condensatori di bisezione e differenziale , sulla base dell’indicazione fornitagli dal phase detector attraverso i segnali Trig e /Trig. Vista la non criticità delle temporizzazioni in questo dispositivo (che utilizza il clock di sistema ad una frequenza di 50 Mhz) è stato scelto per esso un approccio standard cell. La quantità di area utilizzata è stata resa minima con l’aiuto del tool di sintesi e di ottimizzazione logica Design Analizer di SYNOPSYS.

Prima di descrivere la strategia di correzione che abbiamo scelto di utilizzare, ricordiamo che le capacità per la correzione al nonio sono organizzate con una codifica termometrica, in modo da poter essere attivate da uno shift register, mentre i condensatori per la correzione con il metodo di bisezione sono raggruppati in modo tale che ogni gruppo ha un peso crescente come la potenza di

due e sono attivati o disattivati attraverso un registro di tipo SAR (registro ad approssimazioni successive) a sette bit.

3.9.1 Implementazione strategia di correzione

La nostra strategia è quella di utilizzare i condensatori di bisezione per ridurre lo skew del clock iniziale a valori inferiori o al limite uguali a 2 ps, per poi affinare la correzione attraverso il controllo dei condensatori differenziali con il metodo del nonio. La scelta di ridurre lo skew del clock iniziale a valori inferiori o al limite uguali a 2 ps ci ha portato a fissare il numero dei condensatori differenziali a dieci poiché ogni coppia di condensatori differenziali (una coppia è costituita da un condensatore della linea superiore e un condensatore della linea inferiore) inserita introduce un ritardo pari a 0.2 ps. Una volta rilevato il segno dello sfasamento attraverso i due segnali Trig e /Trig prodotti dal rivelatore di fase e deviati opportunamente i segnali sulle due linee, accendiamo e spegniamo i condensatori di bisezione più significativi rispettivamente sulla linea inferiore e su quella superiore. Se al successivo periodo di clock il segno dello sfasamento e quindi la configurazione dei segnali Trig e /Trig non è cambiata rispetto alla situazione precedente allora si procede ad accendere e spegnere i condensatori che introducono un ritardo pari alla metà del precedente e così via fino a quando non si verifica un’inversione di segno nello sfasamento che cambia la configurazione di Trig e /Trig. In questo caso si procede allo spegnimento e accensione dei condensatori che hanno prodotto l’inversione di segno e contemporaneamente all’accensione e spegnimento dei condensatori che introducono un ritardo pari a metà del precedente. Questa strategia ci garantisce che al termine della correzione di bisezione il segno dello sfasamento tra i due segnali sia identico a quello iniziale mentre la sua ampiezza risulta essersi ridotta a valori molto piccoli. La durata della correzione iniziale dello skew, sfruttando l’algoritmo SAR, è pari ad un numero di cicli di clock corrispondenti al numero di condensatori utilizzati per la bisezione. La garanzia che il segno dello sfasamento iniziale si conservi al termine di tale correzione ci permette di applicare correttamente la correzione fine

con il metodo differenziale al nonio. Con riferimento al segno dello sfasamento che ci ritroviamo al termine della correzione grossolana inseriamo una coppia di condensatori differenziali e controlliamo se la configurazione dei segnali Trig e /Trig non sia cambiata. Se non cambia procediamo all’inserzione della successiva coppia di condensatori differenziali in maniera termometrica fin tanto che il segno dello sfasamento si conserva. Nel momento in cui si verifica un’inversione di segno invece di oscillare intorno a questo valore ci fermiamo alla configurazione che produce l’inversione di segno, in quanto, essendo il passo di correzione molto piccolo, non è necessario tornare indietro spegnendo la coppia di condensatori poichè il valore dello sfasamento ottenuto nei due casi si discosta di poco. Nella tabella seguente riportiamo un esempio che riassume la strategia adottata riportando i valori dei segnali di controllo nei due tipi di correzione.

SEGNO SFASAMENTO COND. BISEZIONE

LINEA SUP. COND. BISEZIONE LINEA INF. COPPIA COND. DIFFERENZIALI POSITIVO POSITIVO NEGATIVO NEGATIVO POSITIVO POSITIVO NEGATIVO POSITIVO POSITIVO POSITIVO POSITIVO NEGATIVO 1111111 0111111 1011111 1101111 1100111 1100011 1100101 1100100 ⇓ ⇓ 1100100 0000000 1000000 0100000 0010000 0011000 0011100 0011010 0011011 ⇓ ⇓ 0011011 0000000000 0000000000 ⇓ ⇓ 0000000000 0000000001 0000000011 0000000111 0000000111

3.9.2 Descrizione del circuito

Il controllore di fase, il cui schema a blocchi è rappresentato in

Figura 3.36, è composto essenzialmente da due unità: un blocco di bisezione che sfrutta due registri SAR a sette bit dal quale escono i segnali di controllo per i condensatori di bisezione di ciascuna linea (CB0-CB6) e un blocco differenziale

costituito da uno shift-register a dieci bit dal quale escono i segnali di controllo per i condensatori (C0A-C9A) e (C0B-C9B) per il metodo del nonio.

c0-c9 e-nonio Clk Reset /Trig Trig 10 S2 E1 S1 E2 e1 s1 e2 s2 7 7 B0′-B6′ b′0-b′6 b0-b6 B0-B6 E-NONIO TRIG /TRIG CLK DIFFERENZIALE AL NONIO C0-C9 TRIG /TRIG RESET CLK E-NONIO BISEZIONE DOPPIA

Figura 3.36 Schema a blocchi del controllore di fase

Entrambi questi due dispositivi ricevono in ingresso i segnali di Trig e /Trig provenienti dal rivelatore di fase; il segnale di reset va in ingresso solo al blocco di bisezione. I due blocchi sono collegati tra loro attraverso un segnale denominato e-nonio, di uscita per il blocco di bisezione e d’ingresso per quello differenziale al nonio. E-nonio è un segnale di abilitazione attivo alto che ha la funzione di segnalare al blocco differenziale che la correzione con l’algoritmo di bisezione doppio è terminata dando così inizio alla correzione differenziale.

L’introduzione di questo segnale di abilitazione è stata necessaria in modo tale che il blocco differenziale non fosse sensibile ai segnali provenienti dal phase detector (Trig, /Trig) e quindi garantire che nessuna capacità usata per il metodo del nonio (C0A(B)-C9A(B)) fosse inserita durante la correzione grossolana. Un

impulso sull’ingresso di reset sincrono ha l’effetto di disattivare tutte le uscite di controllo dei condensatori di bisezione e del nonio come deve essere assicurato all’inizio della correzione. In qualsiasi istante del funzionamento del deskewer fornendo un impulso sul segnale di reset il controllore si porta in una condizione di funzionamento iniziale in cui tutti i registri di uscita vengono inizializzati al valore nullo.

I due blocchi del controllore sopra descritti sono stati realizzati come due state-machine, descritte con il linguaggio VHDL di SYNOPSYS. Per la sua progettazione semicustom si è utilizzata la struttura di tipo gerarchico.

Per ulteriori dettagli riguardo il circuito del controllore di fase e in particolare la struttura interna dei blocchi di bisezione e differenziale al nonio rimandiamo all’appendice B, in cui abbiamo riportato la descrizione VHDL di tutte le parti del prototipo progettate in modo semicustom.

3.9.3 Verifica della funzionalità degli algoritmi

Una volta terminata la descrizione in VHDL del controllore di fase i passi successivi, prima di effettuare la sintesi attraverso il tool Design Analyzer di SYNOPSYS e la simulazione post-sintesi, sono i seguenti: compilazione del codice VHDL per verificare che non ci siano errori di sintassi, e simulazione pre-sintesi per verificare la corrispondenza della descrizione alle specifiche richieste. La simulazione è resa possibile da un’entità ausiliaria, testbench, tramite la quale vengono generati i segnali di ingresso al sistema completo e prelevati i segnali di uscita.

Una volta che la descrizione risulta essere funzionalmente corretta si passa alla sua sintesi. Per realizzarla è necessario avere a disposizione una libreria in cui sono descritte le funzionalità e le caratteristiche elettriche e geometriche delle

standard cell utilizzate fornite dalla fonderia. Il processo di sintesi restituisce un’architettura a livello di dispositivo, ossia costituito da un insieme di standard cell collegate opportunamente. Il sistema sintetizzato viene nuovamente simulato, utilizzando lo stesso testbench della presintesi e le entità con le loro rispettive architetture a livello di dispositivo, al fine di verificare la funzionalità e di valutare il rispetto delle specifiche. In questa simulazione vengono valutati anche i tempi di attraversamento delle celle utilizzate. Il flusso progettuale del componente semicustom termina con la fase di back-end e la simulazione post layout. Il back-end, caratterizzato dai passi di floorplannig, placement e routing, porta alla realizzazione del layout del dispositivo e alla crezione del file per la produzione del set di maschere necessario alla realizzazione del chip.

La simulazione post-sintesi relativa al nostro controllore ha verificato la corretta funzionalità dei due algoritmi utilizzati. Infatti, in base al testbench realizzato in modo da testarne la funzionalità, i risultati ottenuti dalla simulazione post-sintesi sono gli stessi di quelli ottenuti con la simulazione pre-sintesi. In

Figura 3.37 (a), (b) e (c) viene riportata la temporizzazione di un esempio di correzione effettuata dal controllore di fase.

(b)

(c)

Figura 3.37 Temporizzazione di una fase di correzione

3.10 Il blocco fullcustom

La parte fullcustom del nostro progetto che comprende le due linee di ritardo, il phase detector, i multiplexer in uscita e in ingresso alle linee, i buffer di linea e l’offset, è stata organizzata in modo da formare un unico modulo che si potesse istanziare nelle fasi successive (in particolare durante il floorplanning).

Dopo aver posizionato una accanto all’altra le tre celle che formano le linee, aggiunto le istanze di tutti gli altri componenti sopra citati ed effettuati i

collegamenti, è stato necessario portare sul bordo esterno con delle piste di metal, tutti i segnali che rendono possibile la comunicazione con gli altri componenti del prototipo e con l’esterno. Al fine di agevolare le operazioni di routing del chip, tutti i segnali per la comunicazione con il controllore di fase e quelli di controllo delle capacità si trovano sul lato sinistro mentre i segnali che rendono possibile la comunicazione con l’esterno sono situati sul lato destro. Infine i segnali di alimentazione e ground sono posti sui lati superiore e inferiore rispettivamente in posizione simmetrica.

Il layout del blocco fullcustom è presentato nella tavola V. Osservandolo possiamo notare la presenza di due vaste aree esterne in cui i segnali di vdd e gnd, realizzati rispettivamente in metal2 e metal1 sono sovrapposti. Queste aree hanno il preciso scopo di aumentare la capacità esistente tra alimentazione e massa che serve a limitare il più possibile le nocive variazioni di questi segnali.

Bibliografia

[1] F. Baronti, D. Lunardini, “Non linearità dei TDC: analisi, tecniche di correzione e progetto di

linea di ritardo a calibrazione digitale”, Tesi di Laurea, Corso di Laurea in Ing. Elettronica,

Università degli Studi di Pisa, A.A. 2000/2001.

[2] L. Mazzoni, “Collaudo e progetto di una linea di ritardo CMOS a controllo digitale con

risoluzione inferiore a ns, applicata ad un trasmettitore PWM”, Tesi di Laurea, Corso di

Laurea in Ing. Elettronica, Università degli Studi di Pisa, A.A. 1995/1996.

[3] Rami Ahola, Jarkko Routama, Saska Lindforce, Kari Halonen, “A Phase-Detector with no

dead-zone and a very wide output voltage range chargepump”, IEEE 1998, p.p 155-158.

[4] Mathieu Renaud, Yvon Savaria, “A linear phase detector for arbitrary clock signals”, IEEE

2002, p.p. 775-778.

[5] B.Nikolic, Member, IEEE, W. G. Oklobdzija, Fellow, IEEE, V. Stojanovic, W. Jia, Member,

IEEE, James Kar-Shing Chiu, and Michael Ming-Tak Leung, “Improved Sene-Amplifier-based

Flip-Flop: design and measurements”, IEEE Journal of Solid State Circuits, vol. 35, no. 6, june 2000.

[6] Duane G. Laurent, Senior Member, IEEE, “Sense Ampliefier Signal Margins and Process

Sensitivities”, IEEE Transactions on Circuits and Systems—I:Fundamental Theory and