93

CAPITOLO 5

ARCHITETTURA IMPLEMENTATA E RISULTATI OTTENUTI

________________________________________________________________________________

In questo capitolo illustreremo il funzionamento dei modelli implementati in SIMULINK e i risultati delle simulazioni. Il capitolo si divide in due sezioni: nella prima sono presentati i modelli usati per la generazione dei tre segnali GALILEO, E ,6 E , 5 L , la simulazione del 1 canale rumoroso e il front-end del ricevitore; nella seconda sono mostrati i modelli per la simulazione degli anelli di recupero dei sincronismi cioè DLL, FLL e PLL.

5.1 Segnali GALILEO

Prima di illustrare i modelli dei tre segnali è opportuno fare la seguente premessa.

All’inizio del nostro lavoro ci eravamo prefissati l’obbiettivo di costruire i modelli allontanandoci il meno possibile dall’architettura implementata nella realtà; l’ ” idea “ che avevamo era quella mostrata di seguito:

RX

Figura 5.1 Schema a blocchi del sistema da simulare

COSTRUZIONE DEI SEGNALI (tempo continuo) FILTRAGGIO ANALOGICO MODULAZIONE A IF (70MHz) CON PORTANTI ANALOGICHE

RUMORE GAUSSIANO BIANCO FILTRAGGIO ANALOGICO ANTI-ALIASING CAMPIONAMENTO A IF 93.333 camp F = MHz DEMODULAZIONE IN BANDA BASE CON

PORTANTI NUMERICHE

FILTRAGGIO NUMERICO

Un modello di questo tipo, sebbene corretto (spettri, costellazioni, ecc.), a causa della presenza dei blocchi continui, necessari per l'elaborazione della parte "analogica", come già affermato nel Capitolo 4, rallentava notevolmente la simulazione. Questo fatto ha reso il modello così concepito non utilizzabile nel momento in cui implementavamo gli anelli del recupero dei sincronismi. E’ stato, quindi, necessario modificare l’architettura usata: abbiamo scelto di lavorare interamente in “digitale”, cioè sui campioni, partendo già con i segnali campionati a 93.333 MHz e utilizzando solo blocchi numerici, con il risultato di una diminuzione notevole dei tempi di simulazione.

Tale modifica è stata effettuata solo sul segnale E , poiché esclusivamente su di esso 6 sono stati simulati gli anelli di sincronizzazione.

I modelli per la generazione dei segnali L e 1 E vengono, invece, presentati con 5 l’architettura mostrata in fig. 5.1, la quale, come già detto, non può essere usata per effettuare successive elaborazioni sui segnali, a causa dei lunghi tempi di simulazione, ma sicuramente è adatta per fini didattici come l’illustrazione degli spettri, delle costellazioni, degli effetti dei filtraggi e dell’inserimento del rumore ecc.

Adesso illustriamo i modelli con cui si è simulato il trasmettitore, il canale ed i primi stadi del ricevitore per i tre segnali GALILEO, soffermandoci sulla descrizione dei blocchi utilizzati e sui risultati ottenuti.

95

5.1.1 Segnale L

1In fig.5.2 riportiamo lo schema di principio utilizzato per la generazione del segnale L . 1

Figura 5.2 Prima parte del modello per il segnale L1

Partiamo dal blocco che genera il codice di gold.

Cliccando sul blocco in alto a sinistra si apre il seguente subsystem

(mostrato in fig. 5.3 ).

Generatore di Gold

Figura 5.3 Contenuto del subsystem che genera il codice di Gold

Possiamo individuare il blocco Gold Sequence Generator già implementato in SIMULINK; cliccando sul blocco si apre il seguente dialog box:

97 Bisogna settare i parametri tenendo conto di quanto detto nelle tabelle 2.2.2 e 2.2.3 (stiamo valutando il codice di Gold per il canale L1 C− ).

• Preferred polynomial (1) : rappresenta il vettore delle prese del registro numero 1. Si ottiene riportando la notazione da ottale a binaria e poi ribaltando tale espressione.

• Initial states (1): rappresenta il vettore delle condizioni iniziali del primo registro a scorrimento che, come affermato nelle specifiche, è costituito da tutti 1. Da notare il fatto che, come evidenziato in fig.2.2.2, il numero delle prese è più grande di uno rispetto al numero degli stati iniziali.

• Preferred polynomial (2): rappresenta il vettore delle prese del registro numero 2. • Initilal states (2): rappresenta il vettore delle condizioni iniziali del secondo registro

a scorrimento, che viene scelto all’interno di una tabella dove sono presenti 100 possibili valori espressi in ottale.

• Sample time: è la velocità di emissioni dei simboli, cioè la chip-rate del codice, che come si evince dalla tabella 2.1.2, è pari a Rc = 1.023 Mch/sec.

• Reset on nonzero input: se selezionato, un ingresso diverso da zero resetta i registri ai valori iniziali, facendo di fatto ripartire la sequenza di codice. Facendo riferimento alla fig.5.3 possiamo notare all’ingresso del blocco Gold Sequence Generator il segnale Rst (Reset) generato dai blocchi alla sua sinistra. Questo segnale resetta il codice ogni 8184 chip, che è proprio il periodo del codice primario.

Esaminiamo adesso il blocco sottostante; è il blocco che genera il codice secondario.

Figura 5.5 Contenuto del subsystem che genera il codice secondario

Analizziamo il funzionamento del blocco Direct Look-Up Table:

Figura 5.6 Dialog box del blocco Look-Up Table

Inseriamo nel campo Table data i valori della sequenza del codice secondo la tabella 2.2.4, dopo aver riportato i valori in linguaggio binario.

99 I blocchi alla sua sinistra generano un segnale che svolge questi compiti:

1) Fissa la durata del chip del codice secondario pari 1/125 sec.; questo, come già detto nel capitolo 2, dura un’intera sequenza del codice primario; infatti 1/125 = (1/1023000) * 8184

2) Ad ogni passo (T= 1/125) seleziona e mette in uscita (out1) un valore della Direct Look-Up Table. Questa operazione viene fatta partendo dal primo valore fino all’ultimo e proseguendo in maniera ciclica.

Analizziamo adesso il blocco :

Il canale L1 C− presenta una modulazione BOC(1,1); questo significa che il segnale prodotto tra il codice primario e quello secondario viene moltiplicato per sign⎡⎣sin 2

(

πf ts)

⎤⎦ , il quale corrisponde ad un’onda quadra con frequenza pari a f = 1.023 MHz. sQuesto blocco si occupa della generazione di tale onda quadra; cliccando sul blocco si apre il subsystem mostrato in fig.5.7 che contiene il blocco Pulse Generator, nel quale possiamo settare i parametri : in definitiva questo blocco genera ogni 1/1023000 sec. un impulso rettangolare di ampiezza unitaria di durata 1/2046000 sec.; il successivo blocco Unipolar to Bipolar Converter è un mappatore che crea la definitiva onda quadra a valori

± 1.

durata chip codice

secondario durata chip codice

Figura 5.7 Contenuto del subsystem che genera l'onda quadra

101 Il canale L1−B a differenza di quello L1−C non è un canale pilota; cioè in L1−B sono presenti dei dati che vengono generati dal blocco Generatore Dati D_L1-B. Per fare questo abbiamo scelto il blocco PN Sequenze Generator, il quale genera una sequenza pseudo-casuale utilizzando uno shift register. E' necessario settare alcuni parametri tra cui le prese e gli stati iniziali del registro a scorrimento ma soprattutto la velocità di emissione dei simboli cioè la data-rate (per il canale L1−B in accordo alla Tab.2.1.2 è pari a 0.004 sec).

Per quanto riguarda il canale L1−A dobbiamo dire che le informazioni riguardanti il codice primario e secondario sono criptate. Per il blocco CLASSIFIED DATA abbiamo usato dei codici scelti del tutto arbitrariamente.

Dopo aver generato i segnali 1I L

S e 1Q L

S , li abbiamo inviati in un filtro passa-basso analogico con banda pari a 20 MHz; tale filtraggio è necessario prima che il segnale venga portato a Frequenza Intermedia (IF).

Il blocco che abbiamo utilizzato, con il rispettivo dialog box, sono mostrati in fig.5.10:

Figura 5.10 Blocco Analog FILTER LP e suo dialog box

Riportiamo in fig.5.11 il proseguimento del modello di fig.5.2.

Adesso le componenti in fase ed in quadratura dopo essere state filtrate vengono portate a IF mediante moltiplicazione con due portanti analogiche (rispettivamente coseno e seno) con frequenza pari a 70 MHz.

103

Figura 5.12 Blocco Cosine e suo dialog box

Figura 5.11 Continuazione del modello di fig.5.2 per il segnale L1

Il blocco che abbiamo utilizzato è mostrato in fig.5.12.

Da notare che abbiamo settato il campo Sample time a 0, proprio perché l’onda sinusoidale viene generata a tempo continuo.

Introduciamo adesso il rumore gaussiano bianco; abbiamo utilizzato il blocco Continous White Noise. Teoricamente il rumore gaussiano bianco ha una un intervallo di correlazione pari a zero e una densità spettrale a banda infinita; in realtà nei sistemi fisici il rumore sarà bianco solo all’interno della banda del nostro segnale, cioè il tempo di correlazione non sarà zero ma molto più piccolo dell’inverso della frequenza massima usata nel modello. Il blocco genera, quindi, dei numeri casuali distribuiti normalmente ad uno specifico sample time, che corrisponde all’intervallo di correlazione; quest’ultimo, affinché la simulazione sia accurata, deve essere scelto secondo la (5.1):

max

1

1

100

ct

f

≈

Nel nostro caso dobbiamo considerare il fatto di essere a IF;

f

max è pari a 90MHz, come possiamo capire dalla fig.5.13, quindi abbiamo assegnato at

c il valore di9 10 sec

⋅

−9 ..40 MHz

70 MHz

Figura 5.13 Banda occupata dal segnale a IF

105

Figura5.14 Blocco Band-Limited White Noise e suo dialog box

Oltre il tempo di correlazione dobbiamo settare il parametro Noise power, che corrisponde al valore di No/2.

Abbiamo scelto per il nostro modello un rapporto C/No pari a 40dB; vediamo cosa significa:

40

C

dB

No

=

10000

C

No

=

Essendo C = 1 (si veda il Capitolo 2) si evince che

1

2

20000

No =

.La potenza di rumore a IF vale 4000; essa si ottiene calcolando l'integrale della densità spettrale di potenza sulla banda del nostro segnale.

Figura 5.15 Rumore che entra nel ricevitore

No/2 =1/20000

40MHz 40MHz

70 MHz -70 MHz

La potenza di rumore è molto elevata rispetto a quella del segnale ed è per questo che lo spettro del segnale scompare al di sotto del rumore.

Da notare che il filtro anti-aliasing del ricevitore non ha alcun effetto sul segnale utile; serve esclusivamente a limitare il rumore sulla banda del segnale.

Di seguito mostriamo l'effetto dell'inserimento del rumore sullo spettro del segnale utile. Gli spettri sono valutati sul segnale in uscita al filtro anti-aliasing.

107 A questo punto, dopo il filtraggio anti-aliasing, inizia la fase "digitale": il ricevitore campiona il segnale ricevuto con una frequenza pari a

93,333

MHz.Il blocco utilizzato per il campionamento è mostrato in fig 5.17.

Figura 5.17 Blocco Zero-Order Hold e suo Dialog box

Gli stadi successivi del ricevitore sono costituiti da blocchi interamente numerici.

La conversione del segnale in banda base avviene utilizzando un seno ed un coseno che, in accordo con quanto detto sopra, sono differenti da quelli utilizzati in trasmissione e mostrati in fig.5.12: si tratta di segnali non più analogici ma campionati, cioè, andremo ad inserire nel campo Sample time il valore 1/93333333.

Il segnale è, quindi, stato convertito in banda base; dobbiamo effettuare un ultimo filtraggio passa-basso prima di avere a disposizione le due componenti.

Tale filtraggio numerico viene effettuato usando il blocco filter_LP_8 da noi implementato tramite una S - Function e già illustrato nel Capitolo 4.

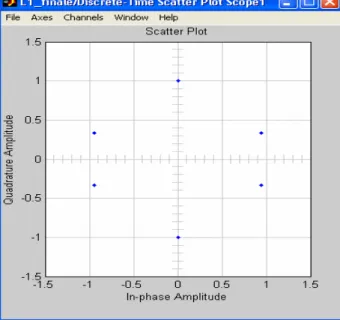

Avendo già commentato gli spettri delle varie componenti nel Capitolo 2, mostriamo soltanto due scatter plot del segnale. La fig.5.19 mostra la costellazione del segnale in trasmissione prima di entrare nei filtri passa-basso, mentre la fig.5.20 rappresenta la costellazione del segnale in ricezione (in assenza di rumore); si vedono chiaramente su quest'ultimo gli effetti dei filtraggi.

Figura 5.19 Scatter Plot del segnale L1 in trasmissione

109 SE5_a Numerico a IF SE5_b Numerico a IF

5.1.2 Segnale E

5In fig.5.21 è riportato lo schema SIMULINK del trasmettitore, canale e ricevitore per il segnale E . 5

Figura 5.21 Il modello per il segnale E5

Questo modello risulta essere sicuramente più complicato rispetto al precedente, non tanto per la costruzione dei quattro canali,

e

E a I5 − ,e

E a Q5 − ,e

E b I5 − ,e

E b Q5 − , per i quali abbiamo utilizzato gli stessi blocchi del modello precedente con le opportune modifiche, ma per la presenza della modulazione AltBOC (15,10).Abbiamo già visto nel Capitolo 2 quanto fossero complicate le formule per la costruzione del segnale

S

E5( )

t

; riportiamo di seguito l'espressione (2.4.3) da cui poi ricavare le componenti in fase ed in quadratura SE5−I( )t ed SE5−Q( )t ., 5 5 5 5 5 5 1 ( ) ( ( ) ( )) ( ) ( 4) 2 2 S E E E a I E a Q E S E S T s t = ⋅ e − t + ⋅j e − t ⋅⎢⎡sc − t − ⋅j sc − t− ⎤⎥+ ⎣ ⎦ , 5 5 5 5 5 1 ( ( ) ( )) ( ) ( 4) 2 2 S E E b I E b Q E S E S T e − t j e − t ⎡sc − t j sc − t ⎤ ⋅ + ⋅ ⋅⎢ + ⋅ − ⎥+ ⎣ ⎦ (2.4.3) , 5 5 5 5 5 1 ( ( ) ( )) ( ) ( 4) 2 2 S E E a I E a Q E P E P T e − t j e − t ⎡sc − t j sc − t ⎤ ⋅ + ⋅ ⋅⎢ + ⋅ − ⎥+ ⎣ ⎦ , 5 5 5 5 5 1 ( ( ) ( )) ( ) ( 4) 2 2 S E E b I E b Q E P E P T e − t j e − t ⎡sc − t j sc − t ⎤ ⋅ + ⋅ ⋅⎢ + ⋅ − ⎥ ⎣ ⎦

Cliccando sul sottosistema sottostante si apre il modello di fig.5.21, che genera la componente in fase del segnale.

111

Figura 5.22 Contenuto del subsystem S_E5-I

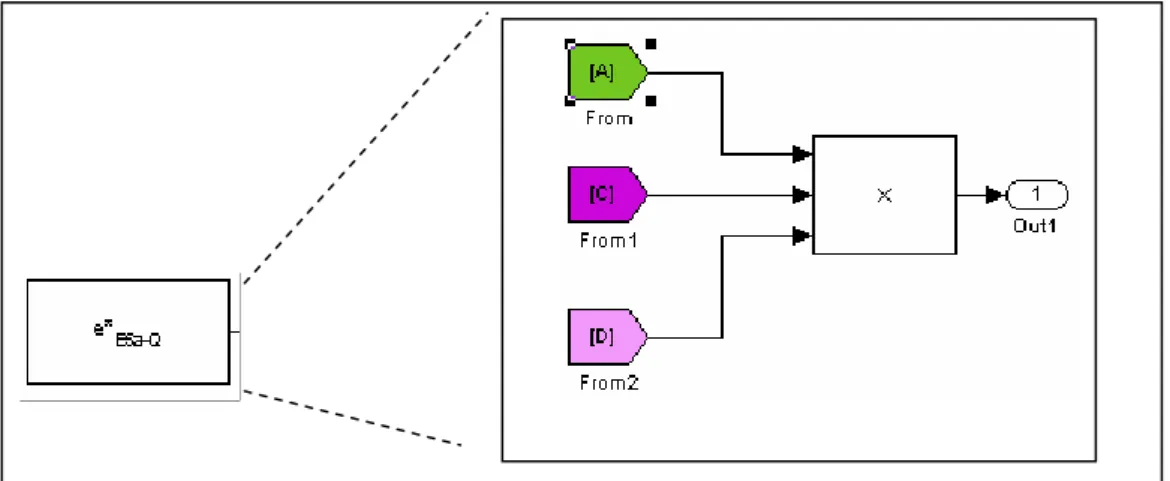

E' possibile individuare ulteriori sottoblocchi; alcuni, come quello mostrato in fig.5.23, servono per la generazione dei segnali eE a I5 − ( )t , eE a Q5 − ( )t , eE a Q5 − ( )t , eE a Q5 − ( )t , altri, come in fig.5.24, generano le forme d'onda scE5−S( )t e scE5−P( )t .

Figura 5.24 Contenuto del subsystem SC_E5-S

Il segnale scE5−S( )t è descritto dalla equazione (2.4.4); per la sua generazione abbiamo utilizzato la stessa tecnica vista per la creazione dei codici secondari. Abbiamo, cioè, inserito nella Direct Look-Up Table i valori dei coefficienti AS ; il segnale che pilota questo i blocco fa in modo che, ad ogni 1/122760000 sec (questo intervallo corrisponde a , 5

8

S E

T

con TS E, 5 = 1/15345000 il periodo della sottoportante) ci sia in uscita al sistema (Out1) un segnale rettangolare con ampiezza pari ad uno dei coefficienti AS . i

In definitiva l'andamento del segnale è mostrato in fig. 5.25 che coincide con l'andamento della curva rossa di fig.2.4.2.

113 Le due componenti in fase ed in quadratura prima della moltiplicazione con il seno e con il coseno vengono filtrate da un filtro passa basso analogico di banda 45 MHz.

A questo punto, a causa della presenza della modulazione AltBOC (15,10), non è più possibile moltiplicare le due componenti con le due sinusoidi a frequenza 70 MHz, utilizzando lo schema per il segnale L . Da quanto affermato nel Capitolo 2, sappiamo che 1 ci sono due sottoportanti, una a 15.345 MHz e l'altra a -15.345 MHz, dove sono centrati gli spettri rispettivamente del segnale E5 B− e di E5 A− (fig.2.2.5 e fig.2.2.6). In ricezione vogliamo campionare a frequenza intermedia, non le componenti in fase ed in quadratura di E , ma proprio i canali 5 E5 A− ed E5 B− . Questa "architettura" di ricezione corrisponde a quella di un ricevitore che demodula separatamente le due sottobande E5 A− ed E5 B− .

Per realizzare ciò abbiamo convertito il segnale E ad una frequenza pari a 140 MHz, ed 5 in ricezione abbiamo riconvertito verso il basso tramite moltiplicazione con due portanti a frequenza opportuna, in modo tale da ottenere due diversi canali entrambi aventi gli spettri dei segnali E5 A− ed E5 B− centrati su 70 MHz; abbiamo, successivamente, effettuato un filtraggio passa-banda che facesse "passare" solo 20 MHz, cioè principalmente il lobo principale, e di seguito abbiamo inserito il campionatore con frequenza

93,333

MHz. Nelle fig.5.26 è illustrato lo spettro che arriva al ricevitore dopo il filtro anti-aliasing. Da notare che le figure seguenti sono state ottenute in assenza di rumore.Figura 5.26 Spettro del segnale in ingresso al ricevitore

Attraverso la conversione con due portanti a frequenza opportuna riusciamo a centrare all'interno del filtro passa banda i due lobi principali appartenenti a E5 A− e ad E5 B− .

Prendiamo il canale E5 A− . Il lobo principale si trova ad una frequenza di 124.655 MHz; questo valore si ottiene facendo 140 MHz - 15.345 MHz.

A questo punto basta convertire il segnale per un' oscillazione a frequenza 54.655 MHz per traslare lo spettro a frequenza IF. Infatti in seguito alla moltiplicazione lo spettro viene traslato a frequenze fs± flo: nel nostro caso ci interessa solo il termine fs− flo poiché 124.655 MHz - 54.655 MHz è proprio uguale a 70 MHz.

Figura 5.27 Demodulazione del canale E5_a

Portante in trasmissione

115 Per quanto riguarda il canale E5 B− si procede nello stesso modo, soltanto che adesso la frequenza di conversione è uguale a 85.345 MHz. Infatti il lobo principale si trova ad una frequenza pari a 155.345 MHz (140 MHz + 15.345 MHz); dopo la moltiplicazione il termine fs− flo (155.345 MHz - 85.345 MHz) è proprio pari a 70 MHz.

Figura 5.28 Demodulazione del canale E5_b

In fig. 5.29 è mostrato lo spettro in uscita dal filtro passa banda; avendo una banda di 20 MHz si può verificare il fatto che passa esclusivamente il lobo principale.

Figura 5.29 Spettro del segnale in uscita al filtro passa-banda

In conclusione mostriamo in fig. 5.30 lo scatter plot, cioè la costellazione del segnale E . 5

117

5.1.3 Segnale E

6Il modello per la generazione del segnale E , come precedentemente detto, è stato 6 "pensato" in modo differente rispetto a quelli per la generazione di E ed 5 L . Non abbiamo 1 utilizzato blocchi tempo-continui ma solo blocchi numerici e siamo partiti direttamente con i segnali già campionati a 93,333 MHz; sebbene tale scelta abbia reso questo modello più distante dalla descrizione reale del sistema, è stata necessaria per aumentare notevolmente la velocità della simulazione e per rendere i risultati compatibili con l'architettura usata nei modelli per il recupero dei sincronismi (vedi la generazione dei segnali early, late e prompt).

Abbiamo detto che il modello lavora direttamente sui campioni; cerchiamo di approfondire tale aspetto che è sicuramente il più interessante, illustrando il blocco generatore dei campioni del codice di Gold del canale

e

E6−C.Clicchiamo sul blocco:

Figura 5.32 Contenuto del subsystem Generatore di Gold

Vediamo adesso il funzionamento dei due blocchi; partiamo con:

119 Per capire come funziona questo elemento è necessaria fare una breve premessa.

Abbiamo precedentemente salvato in un file di MATLAB un'intera sequenza del codice di Gold (10230 chip) e lo abbiamo caricato sul workspace; questa procedura ci ha permesso di avere a disposizione la variabile gold_E6_C prima dell'avvio della simulazione.

Figura 5.34 Il workspace di MATLAB

Ritorniamo alla fig.5.33; il blocco Signal From Workspace non fa altro che prelevare il contenuto della variabile ad intervalli di tempo multipli interi del Sample Time (in cui abbiamo inserito proprio il valore 1/93333333 sec.). In definitiva, ad ogni passo di simulazione, abbiamo in uscita un vettore di dimensione 10230x1 contenente l'intera sequenza di chip del codice di Gold per il canale

e

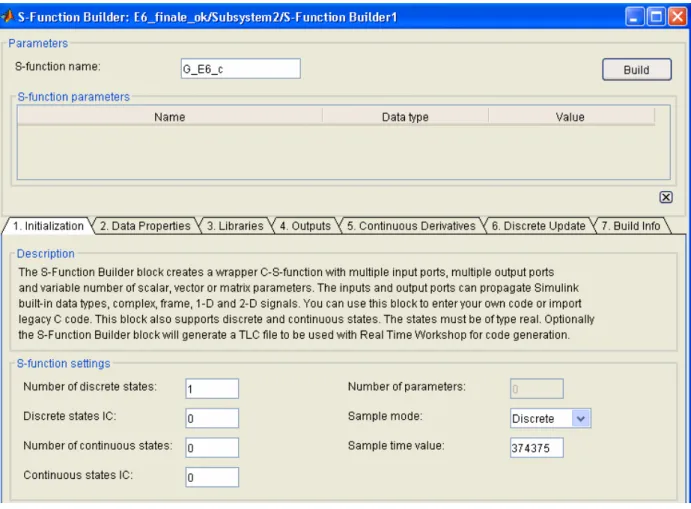

E6−C.Questo vettore entra nel blocco G_E6_c ; si tratta di una S-Function, da noi implementata attraverso un Builder, che ha il compito di effettuare il campionamento a 93,333 MHz del codice.

Ricordando quanto detto nel Capitolo 4, mostriamo di seguito il contenuto dei vari pannelli del S-Function Builder.

Figura 5.35 Dialog box del S-Function Builder G_E6_c

Dal pannello Initialization possiamo notare la presenza di uno stato discreto il cui valore iniziale è pari a zero, ed il campo Sample mode settato su Discrete con intervallo di campionamento pari a 1/93333333 sec.

Passiamo al Data Properties Panel

121

Figura 5.37 Data Properties Panel - Outputs ports

Possiamo individuare l'ingresso, chiamato gold, che come già detto è costituito da 10230 chip, ed un'uscita chiamata out che ha dimensione pari ad uno e che rappresenta il campione che esce dal blocco ogni 1/93333333 sec.

Mostriamo di seguito Outputs Panel e Discrete Update Panel.

Out[0]=gold[0] Figura 5.39 Discrete Update Panel

Spieghiamo adesso come lavora la nostra S -Function.

Ad ogni passo di simulazione il blocco svolge le seguenti azioni:

1. Assegna alla variabile r il valore di xD[0].

2. Assegna alla variabile t la parte intera del rapporto tra r e la durata del chip. 3. Assegna alla variabile u il valore di

t

mod_10230.4. Assegna all'uscita out[0] il valore del chip che si trova all' u-esimo posto del vettore d'ingresso gold[].

5. Aggiorna il valore di xD[0] sommando al precedente una quantità pari ad un intervallo di campionamento.

Durata di un chip = 0.000001955.. sec

_ _ _

Sample Time

Figura 5.40 Come lavora la S-Function

Out[0]=gold[0] Out[0]=gold[0] Out[0]=gold[1] Out[0]=gold[1]

123 Poiché la durata di un chip non è un multiplo intero del tempo di campionamento troveremo mediamente tra 18 e 19 campioni per chip come risulta dalla (5.1).

93333333

18, 246..

5115000 =

In fig. 5.41 mostriamo la parte conclusiva del modello (continua da figura 5.31).

Si può notare anche qui la presenza di blocchi interamente numerici e l'assenza in ricezione del campionatore.

Figura 5.41 Continuazione del modello di fig.5.31 per il segnale E6

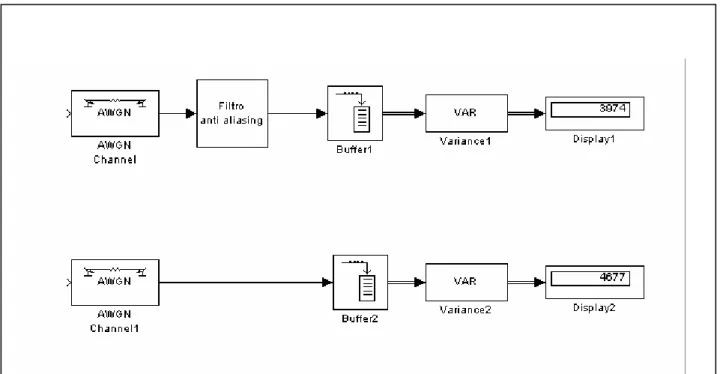

Per la simulazione del rumore abbiamo utilizzato un blocco più adatto ai sistemi interamenti discreti, diverso, quindi, da quello descritto nei modelli dei segnali E ed 5 L . 1

Figura 5.42 Il blocco AWGN Channel e il suo Dialog box

Questo blocco inserisce del rumore bianco con potenza (Variance) pari a

1

2

camp

No

T

⋅

.Nel nostro caso

1

93333333

camp

T

=

e1

2

20000

No =

; quindi settiamo il campo Variance, con il valore dato da 93333333 466720000 ≈ .

Inseriamo come verifica la fig.5.43 che descrive un modello che calcola la potenza di un segnale in ingresso.

Notiamo che aggiungendo il filtro anti-aliasing la potenza di rumore diminuisce avvicinandosi a 4000, cioè al valore che dovrebbe avere sulla banda del segnale e che avevamo già calcolato a pag.13.

125

Figura 5.43 Calcolo della potenza di rumore con e senza filtraggio anti-aliasing

In conclusione mostriamo la costellazione del segnale E in trasmissione, prima dei filtri 6 passa-basso, ed in ricezione in assenza di rumore e dopo i filtraggi.

.

127

5.2 Il ricevitore e le sue componenti in SIMULINK

5.2.1 Recupero del timing

Per quanto concerne il ricevitore, ci siamo interessati agli anelli di sincronizzazione per il recupero del timing e della fase e frequenza della portante.

Lo studio è stato effettuato, come già detto, sulla portante canale B di GALILEO e quindi i risultati ottenuti dalle simulazioni fanno riferimento a tale segnale.

Per approfondimenti suE rimandiamo al capitolo 2. 6B

Analizzeremo passo dopo passo ogni blocco di rilievo del nostro programma svolto in SIMULINK andando a spiegare le scelte dei parametri che hanno condizionato il dimensionamento del sistema.

Nella figura 5.2.1 viene visualizzata la generazione del canale E fornito in ingresso agli 6B anelli di recupero dei sincronismi in accordo con la trattazione riportata nel capitolo 3.

Figura 5.2.1 Generazione e prima parte dello stadio di ricezione per E6b

Nel paragrafo precedente è già stato illustrato come produrre in SIMULINK l’intero segnale E di cui 6 E fa parte e quindi non ci dilungheremo sugli elementi che 6B costituiscono il trasmettitore ed il canale in fig. 5.2.1, ma focalizzeremo la nostra

attenzione sul segnale ricevuto.

Nel programma, il ricevitore effettua una demodulazione tramite i blocchi riportati in figura 5.2.2 (già spiegati in precedenza), ottenendo la parte in fase e quella in quadratura che unite danno luogo all’inviluppo complesso del segnale ricevuto.

Trascurando il rumore questo segnale in banda base differisce da quello trasmesso a causa della non perfetta congruenza tra parametri di sincronizzazione della portante e quelli dell’oscillatore locale in accordo con l’espressione 3.1.5.

L’offset sulla fase e sulla frequenza, è controllato manualmente tramite l’interfaccia dei blocchi sin

( )

⋅ e cos( )

⋅ come si può notare dalla maschera visualizzata in figura 5.2.2Figura 5.2.2 Maschera del blocco se(.)

Infatti per avere una demodulazione coerente avremmo dovuto fissare nel campo frequency del sin

( )

⋅ un valore di 70MHz e nel campo phase offset un valore nullo.129 Nell’esempio di figura 5.2.2, simulando un errore sull’oscillatore locale, abbiamo scelto invece gli offset pari a υ =200Hz ed a θ =0.087 rad.

Proseguendo con le componenti del ricevitore, il segnale demodulato incontra per primo il DLL di tipo non coerente come mostrato in fig. 5.2.3

Figura 5.2.3 DLL non coerente

Cercheremo di dare un’idea di come è stato possibile implementare l’anello chiuso per il tracking del codice utilizzando il linguaggio di SIMULINK.

Il blocco in fig. 5.2.3 denominato DLL è un sottosistema mascherato il cui schema circuitale è riportato in fig. 5.2.4

Figura 5.2.4 Contenuto del blocco DLL

Lo switch serve solo per dare l’avvio, per mezzo di un valore iniziale del ritardo

τ

, al circuito chiuso che in seguito produrrà le stime sul ritardo di propagazione.Esso è pilotato da tre ingressi e produce una sola uscita ad una velocità pari al passo di campionamento del sistema GALILEO dato da 1 93333333 sec.

Numerando gli ingressi dal basso verso l’alto lo switch assegna alla sua uscita il valore del primo o del terzo input in base alla condizione selezionata nel campo criteria for passing first input, che è pilotata dal secondo ingresso.

Nel nostro caso, come si nota in figura 5.2.4 , viene fatto passare al primo istante il valore costante contenuto nel blocco tau iniziale, mentre, per il resto della simulazione, viene interdetto questo blocco a favore delle stime ˆτk.

131

Figura 5.2.5 Maschera del blocco Switch

Il cuore del sottosistema sono però le due S-function che sono adibite alla generazione dei codici locali e delle stime temporali.

La prima ha in ingresso la stima aggiornata ˆτk e permette la generazione dei codici di Gold campionati e ritardati opportunamente dando vita ai tre rami denominati prompt code, early code e late code.

La seconda, invece, ha in ingresso il segnale errore e , creato in accordo a quanto k specificato nel paragrafo 3.4, ed utilizza l’espressione 3.4.1 per aggiornare la stima sul timing.

Come si nota dalla figura 5.2.4, l’uscita dello switch va ad alimentare a sua volta il sottosistema riportato in fig. 5.2.6

Figura 5.2.6 Contenuto sottosistema prompt, early, late code

Il blocco di figura denominato gold_E6_ritardo è un S-function builder, il cui ruolo è quello di campionare e traslare il codice in base alle stime effettuate dal DLL.

Il funzionamento è simile a quello del Builder g_E6_c illustrato nel paragrafo precedente, con la differenza che ora bisogna tenere di conto di uno shift della sequenza di spreading ad ogni aggiornamento della stima del timing.

Facciamo riferimento all’interfaccia grafica del Builder per illustrare i vari parametri utilizzati per la creazione della S-function.

133

Figura 5.2.8 S-function inizialization

Nel pannello Inizialization è presente un solo discrete state inizializzato a 0 che conta i passi di campionamento mentre il campo Sample mode è settato con un passo discreto pari a 1/93333333 sec che regola la velocità delle uscite.

Il Data properties panel contiene gli ingressi e le uscite ed è visualizzato di seguito (fig. 5.2.9)

Figura 5.2.10 S-function data properties

In ingresso abbiamo due variabili ritardo e gold, indipendentemente dal fatto di essere sul ramo early, late o prompt, che rappresentano rispettivamente il ritardo temporale di cui va ruotato il codice locale e l’intero periodo della sequenza di spreading uguale a quello del segnale trasmesso.

Abbiamo, inoltre, un’ uscita chiamata out che ha dimensione pari ad uno e che rappresenta il campione che esce dal blocco ogni 1/93333333 sec.

Le stime di ˆτk si presentano, invece, in ingresso al sottosistema con una velocità diversa e dipendente dalla dimensione dei buffer.

Questo permette di simulare il campionamento e significa che nel tempo occorrente per aggiornare la stima avrò più volte un’ uscita costante e quindi un valore costante.

Di seguito vengono esposte le righe di programma scritte nei campi outputs e discrete update e ne daremo una breve spiegazione.

135

Figura 5.2.12 S-function discrete update

L’idea è quella di capire ad ogni aggiornamento della stima del ritardo di propagazione quale campione del codice trasmettere per avere un perfetto allineamento con quello del segnale ricevuto.

Sappiamo che per E la lunghezza temporale di un periodo della sequenza di Gold è 6B 10−3

sec mentre quella di un chip è 1 5115000 1.955 10= ∗ −7 sec.

Ad ogni passo di campionamento la S-function esegue le seguenti operazioni:

1. Valuta il segno della quantità ˆτk± ∆ e si costruisce la variabile r che tiene conto di tutti i ritardi e di quanto è passato dall’inizio della simulazione

2. Assegna alla variabile t la parte intera di r 1.955 10∗ −7

3. Assegna alla variabile u la quantità t mod 5115

4. Assegna all'uscita out[0] il valore del chip che si trova all' u-esimo posto del vettore d'ingresso gold[].

5. Aggiorna il valore di xD[0] sommando al precedente una quantità pari ad un intervallo di campionamento.

E’ bene ricordare che al punto 1, se il segno dell’ingresso è negativo, viene aggiunta ad r un’ulteriore quantità pari ad un periodo di codice poichè questa aggiunta ai fini della traslazione non ha conseguenze, ma permette di mantenere r come una quantità positiva, condizione essenziale per il funzionamento.

Quindi in base a semplici constatazioni di tipo temporale siamo in grado, ad ogni passo di campionamento, di individuare il chip da cui andare ad attingere il campione e di generare un codice di Gold campionato e ruotato in maniera corretta in base alla stima ˆτk.

Ritornando alla fig. 5.2.4, le due uscite denominate early e late vengono utilizzate per creare il segnale errore e in accordo con quanto detto nel capitolo 3, il quale a sua volta k va in ingresso al secondo S-function builder, chiamato update1, adibito al calcolo delle stime temporali.

I buffer che sono stati presi di dimensione 43000 hanno il compito di memorizzare i campioni e di metterli in un vettore di tale lunghezza.

Si ha un’uscita dal buffer solo quando esso si è totalmente riempito, quindi con una velocità di 1 43000 sec, e poi si ha il calcolo del segnale e in base a quanto detto per un k DLL di tipo non coerente.

Figura 5.2.13 Maschera buffer

Prima di mostrare il programma scritto nell’output della S-function, è interessante visualizzare la curva ad S del DLL ottenuta con il circuito aperto di fig. 5.2.14, facendo attenzione nel notare che quando si inserisce il rumore AWGN si deve effettuare per un ritardo fissato τ non solo la media su 43000 campioni, ma anche su qualche centinaio di realizzazioni di rumore.

137

Figura 5.2.14 Circuito per il calcolo della curva ad S

Con una media su 250 realizzazioni ed un canale AWGN in cui C N è 40 dB si ottiene la 0 curva ad S di fig. 5.2.15 in cui si può notare che il campo d’aggancio è ⎡⎣−T Tc, c⎤⎦ dove

7

1.955 10

c

T = ∗ − sec è la durarta di un chip.

Ritornando al blocco update1, la stima ˆτk è rinnovata con passo pari alla velocità d’aggiornamento del segnale e e viene calcolata semplicemente mettendo nei campi k output e discrete states le seguenti istruzioni

Figura 5.2.16 S-function outputs

Figura 5.2.17 S-function discrete update

Anche ora abbiamo un solo stato discreto xD[0] che rappresenta la stima del ritardo al passo precedente e che viene inizializzato con lo stesso valore iniziale messo nello switch del sottosistema di fig. 5.2.4.

La variabile in[0] è il segnale errore e, quindi, l’uscita dalla S-function indicata con out[0] non fa altro che rispettare l’equazione 3.4.1.

Nelle figure 5.2.18 – 5.2.20 vengono riportati i risultati ottenuti con il programma finora presentato in relazione ai parametri usati per la stima del timing.

139 Banda d’anello = 1Hz Tupdate =43000 93333333

γ =1.04 10∗ −9 0 40 Hz C N = dB offset timing = 2 9.775 108 c T = ∗ − sec

Banda d’anello = 1Hz Tupdate =43000 93333333 γ =1.04 10∗ −9 0 40 Hz C N = dB offset timing = - 2 9.775 10 8 c T = − ∗ − sec

141 Banda d’anello = 1Hz Tupdate =43000 93333333

γ =1.04 10∗ −9 0 40 Hz C N = dB offset timing = 10 1.955 10 8 c T = ∗ − sec

5.2.2 Recupero dei parametri della portante

Come esposto in fig. 5.2.21 il ramo che fuoriesce dal sottosistema CTRLL (Code Timing

Recovery Unit) è il prompt code il quale è mediato sui soliti 43000 campioni e va ad

alimentare le altre parti del ricevitore composto dagli anelli di sincronismo dei parametri della portante.

Figura 5.2.21 Schema collegamento dei tre circuiti di sincronizzazione

Prima di continuare con la spiegazione del programma si rende necessario esporre le motivazioni che ci inducono ad una certa scelta della dimensione dei buffer piuttosto che un’altra. [10]

Il segnale campionato, che entra nel filtro a media mobile, subisce una rotazione dovuta alla presenza di un residuo frequenziale che possiamo avere ad esempio per effetto Doppler.

143 Infatti ogni campione rispetto all’altro ruota di una quantità pari a 2π∆ con fTs T tempo di s campionamento, comportando una perdita di potenza che può rivelarsi pesante ai fini della ricezione se i termini che vengono accumulati e mediati sono elevati.

Si può dimostrare ([10]) che una maggiorazione della perdita di potenza all’interno di una media mobile è ben stimata dall’espressione seguente

(

)

10 sin 20 log fT SNR fT π π ∆ ⎛ ⎞ ∆ = ⎜ ⎟ ∆ ⎝ ⎠ (5.2.1)dove T è il periodo di integrazione della media mobile e f∆ è espresso in Hz.

E’ bene segnalare che, nonostante l’equazione 5.2.1 ci induca a non usare accumulatori di dimensioni troppo grandi, esistono controindicazioni anche nell’adoperare buffer di dimensioni troppo ridotte.

Infatti, se la media viene effettuata con un periodo ristretto, si ha un filtraggio meno efficiente nei confronti del rumore e, quindi, un peggioramento nelle prestazioni degli anelli di sincronizzazione che può essere eliminato solo stringendo la banda di anello e dunque aumentando il transitorio.

E’ evidente che la scelta degli accumulatori deve tener di conto di quanto esposto fino ad ora e che, quindi, si deve trovare una soluzione di equilibrio che non comporti una elevata perdita di potenza sul segnale in uscita al filtro a media mobile, ma che anche limiti l’effetto del rumore.

Nel nostro caso l’intenzione iniziale era quella di avere dei buffer che contenessero un numero di campioni pari a quelli relativi ad un singolo dato e, quindi

dimensione accumulatore = 93333333 1000 93333, 3=

Questa scelta comporta però una perdita di potenza eccessiva data da ∆SNR≈2.5dBdove si è scelto ∆ =f 400Hz e T =93333, 3 93333333 0,001sec= .Il dato ∆ =f 400Hz è un valore di riferimento pari al massimo errore residuo sul Doppler Shift dopo la fase di coarse acquisition.

frequenza

Un buon compromesso tra perdita di potenza e filtraggio del rumore è dato da una dimensione del buffer pari a 43000 per la quale abbiamo ∆SNR≈0.5dB.

Torniamo adesso alla spiegazione dei blocchi del programma analizzando i sottosistemi PLL ed FLL che sono a loro volta mostrati nelle fig. 5.2.22 - 5.2.23

Figura 5.2.22 PLL

145 Cercheremo adesso di entrare nel dettaglio della costruzione in SIMULINK degli anelli chiusi d’aggancio di frequenza e fase, rimandando sempre al capitolo 3 per eventuali chiarimenti di tipo teorico.

Partiamo con l’illustrare i blocchi di fig. 5.2.23 (FLL)

Cliccando sul blocco chiamato FED si ha lo schema in fig. 5.2.24

Figura 5.2.24 Contenuto blocco FED

Esso è in grado di calcolarsi il segnale errore conforme alla 3.2.5 tramite un circuito come quello di fig. 5.2.24 in cui il blocco z−1 ritarda la sua uscita di un passo rispetto all’ingresso

ed u valuta il complesso coniugato. H

L’ultimo blocco contiene una S-function per il calcolo della parte immaginaria del quadrato dell’ingresso.

E’ interessante notare che se in ingresso ad un S-function builder si dichiara un ingresso o un’uscita complessa, come in questo caso, i comandi da immettere nel campo output sono diversi dal caso in cui le variabili siano di tipo reale, come visto finora.

Figura 5.2.25 S-function outputs

Adesso per gli ingressi e per le uscite va specificata la parte ℜ e quella ℑ tramite il comando .re o .im come si vede in figura.

Riferendoci nuovamente alla figura 5.2.23 il segnale errore e viene immesso in una k seconda S-function che elabora la stima aggiornata dell’offset di frequenza come in 3.2.1 tramite il codice riportato nelle fig. 5.2.26 – 5.2.27

147

Figura 5.2.27 S-fuction discrete update

Possiamo notare che le variabili che interessano l’output ed il discrete panel hanno questo significato

• In[0] rappresenta il segnale errore e k

• Out[0] rappresenta la stima dell’offset di frequenza al passo corrente νˆk+1

• XD[0] rappresenta la stima dell’offset di frequenza al passo precedente ˆνk

Infine si crea il segnale e−jθk per la correzione dell’offset in frequenza tramite NCO il cui

schema circuitale è esposto in figura 5.2.28

Anche stavolta si nota la presenza di uno switch che ha il solo scopo di dare l’avvio all’anello chiuso con un valore iniziale inseribile manualmente ed in seguito si procede, con riferimento alla 3.2.2, alla generazione di θk.

E’ possibile inoltre mostrare la curva ad S ottenuta ad anello aperto per visualizzare il campo d’aggancio dell’FLL che va da

(

−500Hz,500Hz)

Figura 5.2.29 Curva S FLL

In questa fase il programma implementato non richiede particolari spiegazioni e, quindi, possiamo immediatamente passare alla visualizzazione dei risultati ottenuti con le scelte dei parametri visualizzate di seguito.

E’ inoltre opportuno notare che le prestazioni ottenute in fig. 5.2.30 - 5.2.31 sono state ottenute supponendo il DLL già agganciato, un offset di fase nullo ed il PLL non collegato.

149 Banda d’anello = 1Hz Tupdate =43000 93333333

γ =7.756 C N0 =40dBHz

offset frequenza = ∆ =f 200Hz

Banda d’anello = 1Hz Tupdate =43000 93333333 γ =7.756 C N0 =40dBHz

offset frequenza = ∆ = −f 100Hz

Figura 5.2.31 Stima offset fase

Per quanto riguarda il PLL, come possiamo notare in figura 5.2.22, la struttura del programma non subisce grandi variazioni rispetto a quella degli altri sincronizzatori e quindi è possibile analizzare subito i contenuti dei blocchi principali.

Ancora una volta con la presenza dello switch si immette un valore iniziale dell’offset di fase per inizializzare il circuito chiuso.

Ricordandoci la 3.3.1 per il calcolo del segnale errore, è evidente la necessità di estrarre dal segnale ricevuto la stima del simbolo d’informazione trasmesso per mezzo di un decisore hard che nel programma è implementato dalla S-function decisore.

151 Ciò è possibile inserendo nel campo output dell’S-function builder i comandi mostrati in fig. 5.2.32

Figura 5.2.32 S-function outputs

Il segnale e entra alla cadenza di 1/43000 sec in ingresso ad una nuova S-function k chiamata update_PLL che elabora le stime dell’offset di fase in accordo con le espressioni 3.3.2 e 3.3.3.

Andiamo ad analizzare i pannelli del seguente blocco (fig. 5.2.33)

Figura 5.2.34 S-function initialization

Figura 5.2.35 S-function outputs

153 In questo caso si hanno tre stati iniziali, tutti con valore di partenza nullo, che rappresentano i valori dei parametri µk, e e k θk e che sono raffigurate rispettivamente dalle variabili xD[0], xD[1], xD[2].

Il programma nel campo output e discrete update si limita ad interpretare fedelmente la 3.3.2 e la 3.3.3.

Infatti la S-function ad ogni passo di simulazione svolge le seguenti azioni:

1. assegna all’uscita il valore di xD[2] che rappresenta θˆk+1 2. aggiorna µk assegnando tale valore alla variabile xD[0] 3. aggiorna e assegnando tale valore alla variabile xD[1] k 4. aggiorna θˆk assegnando tale valore alla variabile xD[2]

E’ interessante vedere i risultati ottenuti in cui abbiamo supposto il DLL già a regime, l’ FLL staccato ed una curva ad S del PLL come quella in figura 5.2.37.

Si ricorda, inoltre, che con la scelta dei parametri visualizzata in seguito, il PLL, essendo del 2° ordine, è in grado di recuperare anche un offset frequenziale del’ordine di 20Hz La banda d’anello è infatti pari a 20Hz.

Figura 5.2.37 Curva S del PLL

π

−

2 10 anello update B T = − 43000 93333333 update T = γ =0.06544 ς = 2 2 ρ =0.013 C N0 =40dBHz

offset frequenza = 0 offset fase = 5° = 0.087rad

155 2 10 anello update B T = − 43000 93333333 update T = γ =0.06544 ς = 2 2 ρ =0.013 C N0 =40dBHz offset frequenza = 10Hz offset fase = 0

Figura 5.2.39 Differenza tra fase vera e quella stimata

A conclusione vengono proposte le prestazioni dell’intero sistema che si ottengono collegando assieme i tre anelli di recupero dei sincronismi come già illustrato in fig.5.2.21 facendoli partire tutti da una situazione di non regime.

Figura 5.2.40 Recupero offset frequenziale in assenza di rumore DLL FLL PLL Bl = 1Hz Bl=1Hz 10 2 anello update B T = − 43000 93333333 update T = γ =7.756 γ =0.06544 9 1.04 10 γ = ∗ − offset freq = 200Hz ρ =0.013

offset timing = 1.955 10∗ −8sec ς = 2 2

157

Figura 5.2.41 Recupero timing in assenza di rumore

Figura 5.2.43 Recupero offset fase in assenza di rumore

0.35 rad

Come si può dedurre dalla fig. 5.2.43 il PLL si aggancia alla fase da stimare, a regime, con un errore dato da un multiplo di π e, quindi, al ricevitore i simboli d’informazione stimati saranno tutti di segno opposto (vedere fig. 5.2.44 – 5.2.45)

Infatti se la retta rossa di fig. 5.2.43 rappresenta l’asintoto a regime della curva data dalla stima di fase e la retta verde rappresenta la parallela che ha valore, per t=0sec, pari alla fase iniziale messa nello switch, si ottiene una differenza di quota tra le due rette data da

0.35-(-9) = 9.35

Il valore trovato è un multiplo di π essendo 9.35 π ≈3 e questo sta a significare proprio che a regime la fase stimata si aggancia a quella reale a meno di un multiplo di π . A conferma di quanto detto si possono confrontare i dati trasmessi con quelli presenti al ricevitore, dopo il decisore hard usato dal PLL (vedere fig. 5.2.22).

Figura 5.2.44 Esempio di 19 dati al trasmettitore a regime

Fase di partenza Retta verde per t=0 sec

Retta rossa per t=0 sec

159

Figura 5.2.45 Esempio di 19 dati al ricevitore a regime

Per maggiore completezza vengono esposte le fig. 5.2.46 – 5.2.48 che rappresentano i recuperi dei sincronismi in presenza di rumore con C N0 =40dBHz

Figura 5.2.46 Recupero offset frequenziale con e senza rumore

161